100661:2

нительного коммутатора объединен сподключен к треть&лу входу второго

третьим входе блока выбора опорногоключа, выход которого подключен к друсигнала, соответствующий выход которого гому входу второго режектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска шумоподобных сигналов | 1977 |

|

SU674224A1 |

| УСТРОЙСТВО ПОИСКА СИГНАЛА СИНХРОНИЗАЦИИ СПУТНИКОВОЙ СИСТЕМЫ СВЯЗИ | 1995 |

|

RU2093963C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1990 |

|

RU2007044C1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840115A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1980 |

|

SU1840563A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1985 |

|

SU1840080A1 |

| Устройство синхронизации сигнала с -образной частотной модуляцией | 1976 |

|

SU743207A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1979 |

|

SU1840071A1 |

| Устройство поиска шумоподобного сигнала | 1982 |

|

SU1095433A2 |

| Устройство поиска шумоподобных сигналов | 1989 |

|

SU1653170A1 |

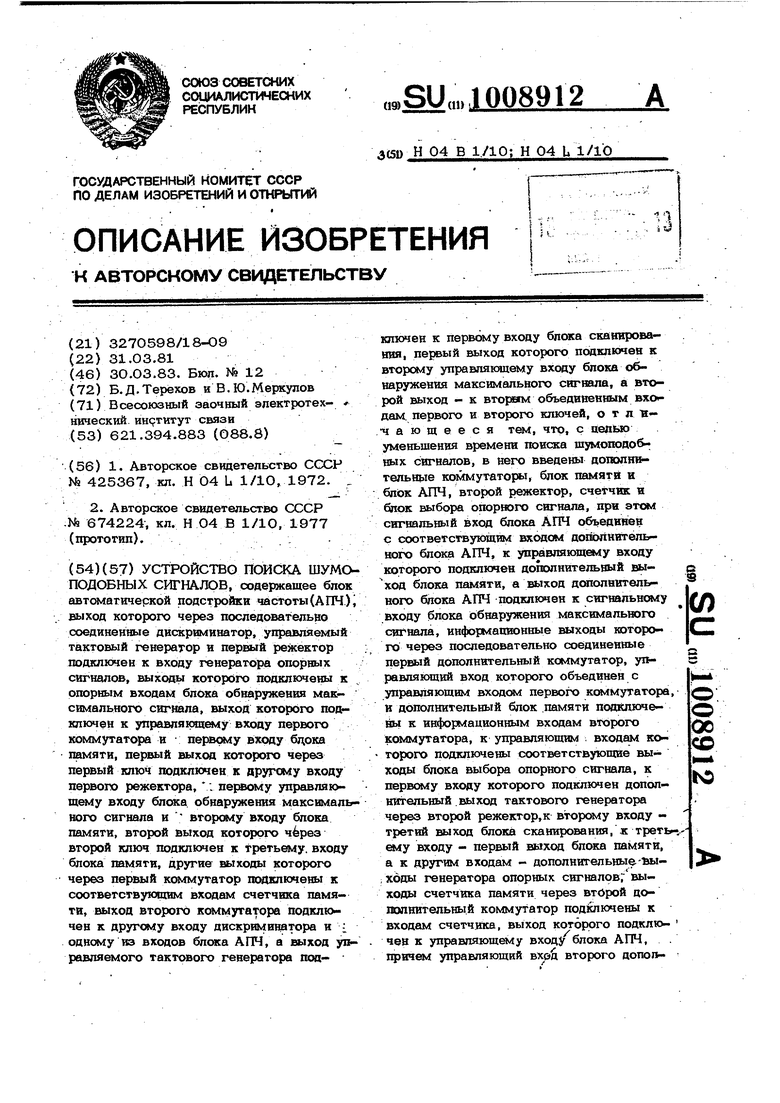

УСТРОЙСТВО ПОИСЖА ШУМОПОДОБНЫХ СИГНАЛОВ, содержащее блок автоматичеркой подстройки частоты (А ПЧ)| выход которого через последовательно соединенные дискриминатор, управляемый тактовый генератор и первый режёктор подключен к входу генератора опорных сигналов, выходы которого подключены к опорным входам блока обнаружения максимального сигнала, выход которого поен ключен к управляющему входу первого коммутатора и первому В1ходу бдока памяти, первый выход которого через первый ключ подключен к другому входу первого режектора, : первому управляк щему входу бл(жа обнаружения максимального сигнала и второму входу блока памяти, второй выход которого ч4рез второй ключ подключен к третьему, входу блока 1ШМЯТИ, другие выходы которого через первый коммутатор подключены к соответствующим входам счетчика памяти, выход второго коммутатора подключен к другому входу дискриминатора и ; одному из входов блока АПЧ, а выход управляемого тактового генератора подключен к первому входу блока сканирования, первый выход которого подключен к вторсму управляющему входу блока обнаружения максимального сигнала, а второй выход - к BTopEiM объединенным . первого и второго ключей, о т л ичающееся тем, что, с аепыо уменьшения времени поиска ш оподобных сигналов, в него введены дополни тельные коммутаторы, блок памяти к блок АПЧ, второй режёктор, счетчик и блок выбора опорного сигнала, при этом сигнальный вход блока АПЧ объединен с соответствующим входом догажннтельного блока АПЧ, к управляющему входу которого подключен дополнительный выS ход блока памяти, а выход дополнитель(Л С ного блока АПЧ подключен к сигнальному .входу блока обнаружения максимального сигнала, информатаюнные выходы которого через последовательно соединенные первый дополнительный коммутатор, управляющий вход которого объединен с управляющим входом первого коммутатора, U дополнительный блок .памяти подключео ны к информационным входам второго 00 С коммутатора, к упрЕШляющим входш ко торого подключены соответствующие выходы блока выбора опорного сигнала, к ю первому входу которого подключен дополШггельный .выход тактового генератора через второй режёктор, к второму входу третий выход блока сканирования, ж треть-,.ему входу - первый выход блока памяти, а к другим входам - дополнительные-ьы;Х:6ды генератора опорных сигналов выходы счетчика памяти через второй дополнительный коммутатор подключены к входам счетчика, выход которого подклк чен к управляющему входублока АПЧ, причем управляющий вход второго дотюп

Изобретение относится к устройствам обнаружения, распознавания и приема шумоподобных сигналов и может быть использовано, например, в рад1юлокац1 онных и связных системах. Известно устройство поиска широкопо лоскых сигналов, содержащее приемник с гетеродином в цепи автоматической подстройки частоты и - блоком слежения за задержкой, содержащим, в свою очередь дискриминатор и регистр сдвига с обратной связью, выход каждого из т разрядовкоторого соединен с входом соответствующего коррелятора, а через соответствующий вентиль и общую схему ИЛИ - с входом дискриминатора, другой вход которого соединен с информационными входами корреляторов, а также блок сканирования, управляющий регистром сдвига и гетеродином, при этом BbJxoa каждого корреляторачерез соответствующий вычитающий блок подключен к детектору максимального сигнала (МС), причем выходы детектора МС подключены к управляющим входам соответствующих .упомянутых вентилей непосредственно, а к входам сброса корреляторов и : управляющему входу блока сканирования - через дополнительную схему ИЛИ и ключ, к сигнальному входу входу которого подключен тактовый выход блока сканирования через линию задержки рЗ Недостатке этого устройства является, то, что в-процессе сканирования проверяется каждое превыщение порогово го уровня, вследствие чего возрастает время поиска сигнала. Наиболее близким к предлагаемому я& ляется устройство поиска щумоподобных сигналов, содержащее блок авт {атичеокой подстройки частоты, выход которого через последовательно соединенные дискриминатор, управляемый тактовы генератор и первый режектор подключён к входу генератора опорных сигналов, выходы которого подключены к опорным входам блока обнаружения максимального сигнала, выход которого подключен к управляющему входу первого коммутатора и у первому входу блока памяти, первый выход которого через первый ключ подключен к другому входу первого режектора, , первому управляющему входу блока обнаружения максимального сигнала и второму входу блока памяти, второй выход которого через второй ключ подключен к третьему входу блока памяти, другие выходы которого через первый коммутатор подключены к соответствующим входам счетчика памяти, выход второго коммутатора подключен к другому входу дискриминатора и одному из входов блока АПЧ,а выход управляемого тактового генератора подключен к первому входу блока сканирования, первый выход которого подключен к второму управляк щ®v y входу блока обнаружения максимального сигнала, а второй выход - к вторым Объединенным входам первого и второго ключей 2. Отличительной особенностью известного устройства является максимальная величина отклика на выходе корреляционного обнаружителя, но отождествление искомого сигнала с опорным, обеспечивающим этот отклик, производится лищь после просмотра всей области поиска, в резул тате чего известное устройство имеет больщое время поиска сигнала. Цель изобретения - уменьшение времени поиска щумоподобных сигналов. .Поставленная цель достигается тем, что в устройство поиска щумоподобных сигналов, содержащее блок автоматичеокой подстройки частоты, выход которого через последовательно соединенные дискриминатор, управляемый тактовый генератор и первый режектор подклк чен к входу генератора опорных сигналов, выходы которого подключены к onopiibiM входам блока обнаружения максимального сигнала, выход которого подключен к управляющему входу первого 3100 каммутаторй. и первому входу блока памяти, первый выход которого через пер вый ключ подключен к другому входу первого режектора, первому управляк ЩЙ4У входу блока обнаружения максималь иого сигнала и второму входу блока памяти, второй выход которого через второй ключ подключен к третьему входу блока памяти, другие выходы которого через первый коммутатор подключены к соответствующим входам счегчика памяти выход второго коммутатора подключен к другому входу дискриминатора и одному Из входов блока А ПЧ, а выход управляемого тактового генератора подключен к первому входу блсяса сканирования, первы выход которого подключен к управляющему входу блока обнаружения максимального сигнала, а второй выход к вторым объединенным входам первого и второго ключей, введены дополнительные кcяvfмyтaтopы, блок памяти и блок АПЧ, режектор, счетчик и блок выбора опорного сигнала, при этом сиг. нальный вход блока АПЧ объединен с соответствующим входом дополнительного блока АПЧ, к управляющему входу которого (подключен дополнительный выход блока памяти, а выход дополнительного блока АПЧ подключен к сигнальному входу блок(а обнаружения максимального сиг нала, информационные выходы которого через последовательно соединенные дополнительный коммутатор, управляющий вход которого объединен с управляющим входом первого коммутатора, и дополнительный блок памяти подключены к информационным входам второго коммутатора, к управляющим входам которого подключены соответствующие выходы блока выбора опорного сигнала, к первому входу которого подключен дополнительный выход тактового генератора через второй режектор, к второму входу третий выход блока сканирования, к третьему входу - первый выход блока памяти, а к другим входам - дополнитель ные выходы генератора опорных сигналов выходы счетчика памяти через второй до полнительный коммутатор подключены к входам счетчика, выход которого годключен к управляющему входу блока ХПЧ, причем управляющий вход второго дополнительного коммутатора объединен с третьим входом блока выбора опорного сигнала, соответствующий выход которого подключен к третьему входу клк ча, выход которого подключен к другому входу второго режектора. 24 Отождествление искомого сигнала с опорным, обеспечивающим максимальный отклик корреляционной свертки, проиаводится после просмотра части области поиска при одновременнс сканировании оставшейся части области поиска, за счет чего уменьшается время поиска сигнала. На чертеже представлена фу1|кциональная схема предлагаемого устройства, где для простоты показаны только три кана-ла обнаружения. Устройство содержит блок автоматической подстройки частоты 1, состоящий из смесителя 2, демодулятора 3 я управляемого гетеродина 4, дискриминатор 5, управляемый тактовый генератор 6, первый режектор 7, генератор 8 опорных сигналов, блок 9 обнаружения максимального сигнала, состоящий из канальных корреляторов 1О-12, детектора максимального сигнала 13, блока 14 сравнения, ключей 15 и 16, элементов 17 и 18 памяти, второй коммутатор 19, блок 2О сканирования, первый кпуп 21, второй ключ 22, блок 23 памяти, состоящий из элементов 24 и 25 памяти, счётчиков 26 - 28, коммутатора 29, дешифратора ЗО, первый коммутатор 31, счеч чик 32 памяти, второй дополнительный коммутатор 33, счетчик 34, дополнительный блок АПЧ 35, состоящий из смесителя 36, демодзшятора 37 и управляемого гете одина 38, второй режектор 39, блок 4О выбора опорного сигнала; первый дополнительный коммутатор 41, дополнительный блок 42 памяти. Устройство работает следующим образом. Приходящий сигнал с неизвестной частотой и запаздыванием и шум через дополнительный блок АПЧ 35 поступают на входы канальных корреляторов 10-12 блока 9 обнаружения максимального си1 нала. В канальных корреляторах происходит свертка принимаемой смеси сигнала и шума и опорных сигналов, поступающих с генератора 8 опорных сигналов. Детектор максимального сигнала 13 подключает канальный коррелятор 10-12 с максимальным напряжением свертки к первому входу блока 14 сравнения / К второму входу блока 14 сравнения подгключен 18 памяти, который в исходном состоянии (в начале поиска) вы- дает нулевой уровень. Если напряжение кадильного корреля- тора 10-12 больше, ч напряжение с элемента 18 памяти, то блок 14 сравн ния закрывает ключ 15 и устанавливает элемент 17 памяти в такое положение, при котором коммутатор 29 блока 23 памяти и первый коммутатор 31 записы вают информацию из счетчиков 28 и 27 блока 23 памяти в счетчик 26 блока 2 памяти и счетчик 32 памяти соответственно. При этом первый дополнительный коммутатор 41 открыт и детектор максимального сигнала 13 устанавливает дополнительный блок 42 памяти в поло жение, соответствующее номеру канал ного коррелятора с максимальным напря жением свертки (записывается номер ка Нального коррелятора), а в элемент 18 памяти через открытый ключ 16 поступают импульсы с блока 20 сканирования (например, тактовой частоты), увеличивая записанный в нем уровень. Как только этот уровень достигнет величины напряжения на первом входе блока 14 сравнения, т.е. максимального напряжения свертки, открывается ключ 15 и , определяющий время анализа . данной группы опорных сигналов, с выхода блока 20 сканирования поступает на счетчик 27 блока 23 памяти через открытый первый ключ 21 в первый режектор 7, осуществляя временной сдвиг опорных сигналов на элемент 17 памяти блока обнаружения максимальног сигнала 9, возвращая его в исходное состояние, и на сбросовые входы канальных корреляторов 10-12, разряжая содержащиеся в них интеграторы. Счетчик 29 блока 23 памяти, воздействуя на управляемый гетеродин 38 дополн№тельного блока АПЧ 35, управляет поиском по частоте. Если при анализе группы опорных сигналов напряжение свертки на первом входе блока 14 сравнения меньше уровня, записанного в элементе 18 памяти,то переход к анализу следующей группы onopHbix сигналов происходит как.и ранее, но без записи Информации из счеть чика 27 в счетчик 26 и из счетчика 28 в счетчик 32 памяти. После анализа всех временных положений опорных сигналов, что фиксируется счетчиком 27 блока 23 памяти, де шифратор 30 блока 23 памяти выдает команду на переход устройства в режим проверки группы опорных сигналов, обеспечившей максимальный отклик. К этому моменту в счетчиках 27 и 28 блока 23 памяти записаны координаты запаздывания и частоты той группы опорных сигналов, ввпряжеиие свертки KOTopiix было максимально в процессе сканирования (анализа), а дополиитель.ный блок 42 памяти установлен в положение, соответствующее номеру канал ного ко|эрелятора с максимальным напряжением свертки и помнит этот (юмер. Следовательно, в памяти устройства есть координаты нужной группы опорных сиг- налов (запаздывание и частота) и нсмер опорного сигнала (канального коррелятора), обеспечившего максимальный отклик. Для перехода в режим проверки необходимо выдать координаты опорного, сигнала, обеспечившего максимальный отклик в блок АПЧ 1. Это происходит следующим образом. Импульс с выхода дешифратора 30 блока 23 памяти закрывает первый ключ 21, воздействует на блок 40 выбора опорного сигнала и через второй дополнительный ксымутатор 33 воздействует на счетчик 34. В результате в блоке АПЧ 1 через второй коммутатор 19 выдается исксмый опорный сигнал (искомый по временному положению), а счетчик 34 устанавливает нужную частоту управляемого гетеродина 4, т.е. обеспечивает согласование опорного сигнала по частоте. При этом через открытый второй ключ 22 блок 20 сканирования воздействует на второй режектор 39 и счетчик 26 блока 23 памяти, списывая имек щуюся в нем инфор«гацию и осуществляя временной сдвиг опорного сигнала, подаваемого на блок АПЧ 1. После обработки необходимого временного рассогласования счетчик 26 блока 23 памяти устанавливает второй ключ 22 в положение Закрыт. Опорный сигнал, подаваемый на блок АПЧ 1, имеет нужные запаздывание и частоту. В то же время счетчики 26 и 27 блока 23 памяти обнуляются (эти цепи для простоты, не показаны), испульс с блока 2О сканирования через открытый первый ключ 21 поступает в первый режектор 7, в блок 23 памяти и в блок 9 обнаружения максимального сигнала и т.д. Одновременно с анализом опорного сигнала, обеспечившего максимальный отклик, продолжается сканирование оставшейся части области поиска. Таким образом предлагаемое устройство Чзбеспечивает меньшее время поиска сигнала без ухудшения остальных пара-, метров.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО ПОИСКА ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1972 |

|

SU425367A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство поиска шумоподобных сигналов | 1977 |

|

SU674224A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-03-30—Публикация

1981-03-31—Подача