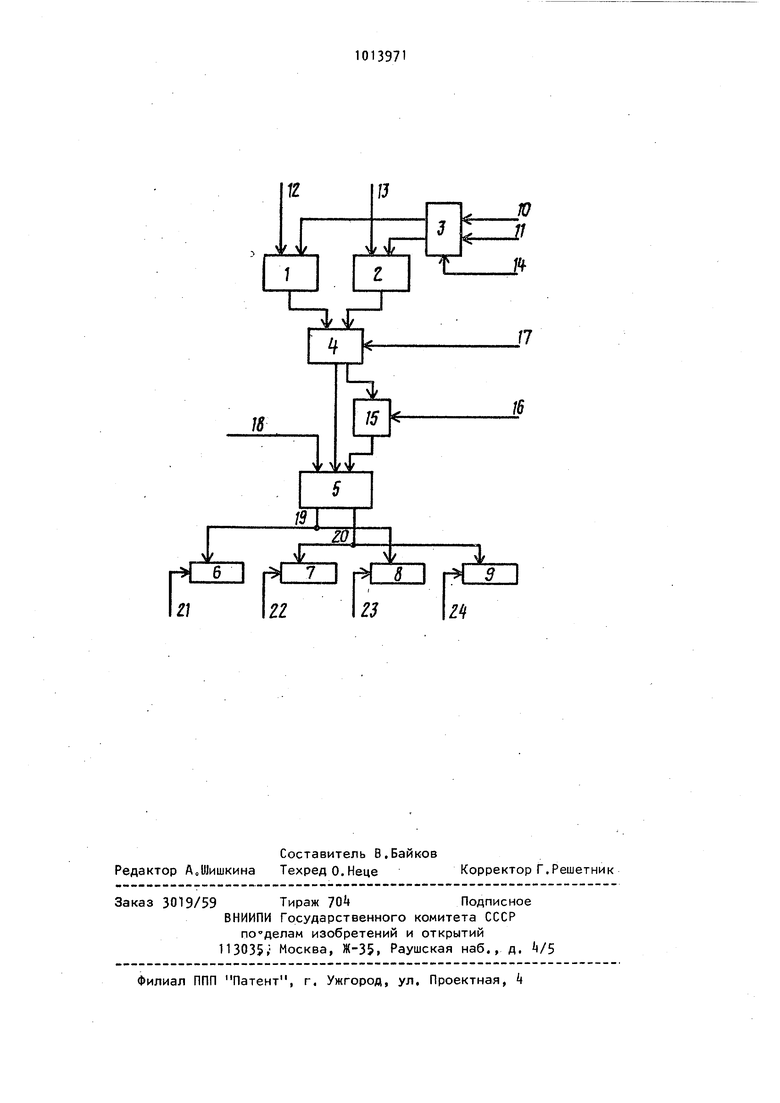

Изобретение относится к автоматике и вычислительной технике и может быть использовано в процессорах для спектрально-корреляционного анализа сигналов. При осуществлении тэкого анализа в реальном масштабе времени появляется необходимость добиваться большого быстродействия арифметических устройств (АУ), реализующих базовую операцию алгоритма быстрого преобразования Фурье (БПФ). Быстродействие таких устройств находится в прямой зависимости от частотного диапазона входных сигналов. Задачу получения большого быстродействия решают построением ДУ в виде матричных систем. Однако пру анализе виброакустических сигналов при диагностировании мехайичес кого состояния машин и механизмов, частота входных сигналов обычно не превышает и быстродействие мат ричных систем оказывается избыточным Встает вопрос построения аппаратуры с оптимальным соотношением быстродей ctвия и объеме применяемого оборудования, . Известно устройство для БПФ, выполняющее базовую операцию с максимальиым распараллеливанием арифметических дей(твий и содержащее всего три блока умножения f 1 3. Однако устройство громоздки и име ет малый коэффициент использования операционных узлов, а также избыточ ность быстродействия. Наиболее близким техническим реше нием к изобретению является устройс во для быстрого преобразования Фурь 21, содержащее два умножителя, сумматор, сумматор-вычитатель, четыре регистра, а также инвертор, дополнительный сумматор-вычитатель и блоки масштабирования. Известное устройство реализует основные соотношения Ai A... , (1) Re В.М. ReB-- ReW. - JinB.OrnW. -, 3rn 5-XMj JrnB..-ReB,OmWj , где Re, Im - вещественная и мнимая часть соответственно. Недостатком известного устройств является большая сложность, обуслов ленная, прежде всего, блоками масштабирования. Целью изобретения является упрощение устройства. .Поставленная цель достигается тем, что устройство для быстрого преобразования Фурье, содержащее два умножителя, сумматор, сумматор-вычитатель и четыре регистра, причем первые входы первого и второго умножителей являются входами соответственно мнимой и действительной частей первого операнда устройства, выходы умножителей подключены к входам сумматора, управляющий вход которого является входом задания режима устройства, информационный выход сумматора подключен к первому входу сумматора-вы читателя, второй вход которого является входом эторого операнда устройства, выход суммы сумматора-вычитателя подключен к входам первого и второго регистров, выход разности сумматора-вычитателя подключен к входам третьего и четвертого регистров, входы синхронизации регистров являются тактовыми входами устройства, содержит коммутатор и сумматор по модулю два, причем входы коммутагора являютей входами мнимой и действительной частей коэффициента устройства, выходы коммутатора подключены к вторым входам умножителей, первый вход сумматора по модулю два подключен к выходу знакового разряда сумматора, выход сумматора по модулю два подключен к входу знакового разряда первого слагаемого сумматора-вычитателя, управляющий вход коммутатора и второй вход сумматора по модулю два являются первым и вторым управляющими входами устройства. На чертеже.приведена схема предлагаемого устройства. Устройство содержит умножители 1 и 2, коммутатор 3, сумматор А, сумматор-вычитатель 5, регистры 6-9, входы 10 и 11 мнимой-И действительной частей (задания) коэффициента устройства, вход 12 (шину) мнимой части первого операнда (комплексного числа) устройства, вход 13 (шину) вещественной части первого операнда (комплексного числа) устройства, управляющий вход 1 (шину управления коммутатором), сумматор 15 по модулю два, управляющий вход 16 (шину управления), вход 17 (шину) задания режима, вход 18 (шину) второго операнда (комплексного числа) устройства, (суммирующий) выход 19 суммы сумматора-вычитателя, ( вычитающий ) выход 20 разности сумматора-вычитателя, шины 21-24 синхронизации. Устройство работает следующим образом. Базовая операция алгоритма БПФ выполняется (как и в известном устройстве) за время основного тактового импульса. Знамение времени такта определяется временем считывания операнда из оперативного запоминающего устройства (ОЗУ). Время срабаты вания АУ в два с лишним раза меньше времени основного такта, поэтому для АУ такт представлен двумя полута товыми Импульсами. При выполнении прямого БПФ на вторые входы умножителей 1 и 2 по ши нам 12 и 13 поступают соответственно мнимая ImB и вещественная ReB части первого комплексного числа со знаками. На шину 16 управления подается сигнал Нуль и знак пропускается прямым. На входы 10 и 11 задания коэффициентов поступают соответственно ReW- и IrftWj. В течение первого полутакта на ши ну Н управления коммутатором 3 пода ется управляющий сигнал, под деиствием которого коэффициент с вхо да 10 через коммутатор 3 поступает н первый вход блока 2 умножения, а коэффициент ImW с входа 11 - на первый вход умножителя 1. Результат операции умножения с выходов умножителей 1 и 2 поступает соответственно на первый и второй входы сумматора Ц, который под действием нулевого сигнала на шине 17 выполняет операцию сложения, в результате чего на входе сумматора t получают число, соответствующее выражению (3 модуль которого поступает на первый числовой вход, а знак, проходя через сумматор 15 по модулю два без изменения - на знаковый вход сумматора-вычитателя 5, на второй вход ко торого поступает вещественная часть (ReAl) со знаком с шины 18 второго комплексного числа (ReAi+ mA.). На шины 21 и 22 синхронизации подается сигнал разрешения записи ин формации в регистры 6 и 7, при этом на шинах 23 и 2 существует сигнал запрета; Таким образом, результаты. 71 полученные на суммирующем выходе 19 (ReA и вычитающем выходе 20 (ReB| сумматора-вычитателя 5 в соответствии с выражением (1) и (2), записываются в регистры 6 и 7 соответственно, В течение второго полутакта на шине Н управления коммутатором 3 устанавливается сигнал Единица, в результате чего на первый вход умножителя 1 поступает ReW,-, а на первый i вход умножителя 2 - lmW|, Под действием сигнала Единица на шине 17 сумматор l выполняет операцию вычитания, в результатечего на его выходе получают число, соответствующее выражению (А), модуль и прямой знак которого поступает на первый числовойизнаковый входы сумматоравычитателя 5, на вторые которого подается мнимая часть (ImA.) со знаком второго комплексного числа (ReA +lmA-). На шины 23 и 2 синхронизации подается сигнал разрешения записи информации в регистры 8 и 9, при этом на шинах 21 и 22 существует сигнал запрета. Таким образом, результаты полученные на суммирующем выходе 19 (i M.i) и вычитающем выходе 20 (imB. ) сумматора-вычитателя 5 в соответствии с выражениями (l) и (2)« записываются В регистры 8 и 9 соответственно. При выполнении обратного БПФ работа устройства аналогична работе при выполнении прямого БПФ за исключением того, что в первом полутакте устанавливается сигнал Единица на шине 17 (.сумматор Ц выполняет операцию вычитания )и на шине 16 управления сумматором 15 по модулю два (знак инвертируется), а в течение второго полутакта устанавливается нулевой сигнал на шине 17 и шине 16 сумматором 15 по модулю два. Таким образом, предложенное устройство позволяет сократить количество используемого оборудования (за счёт исключения из состава устройства сумматора-вычитателя и одного инвертора знака) при тех же функциональных возможностях устройст-ва, 3 также исключить необходимость введения схем масштабирования, реализация которых требует значительных аппаратурных затрат.

Н

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразованияфуРьЕ | 1978 |

|

SU794637A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Вычислительное устройство для цифровой обработки сигналов | 1985 |

|

SU1295414A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Арифметическое устройство для вычисления коэффициентов Фурье | 1986 |

|

SU1388893A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1989 |

|

SU1631555A1 |

Г

1л

п

т

Авторы

Даты

1983-04-23—Публикация

1981-12-16—Подача