1 12

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении ЭВМ, в частности процессоров цифровой обработки сигналов.

Цель изобретения - расширение функциональных возможностей устройства за счет реализации функций вида

X 1::А;В;, Xj А, в. -ь с. , X. 4ZA,.

1 icO -°

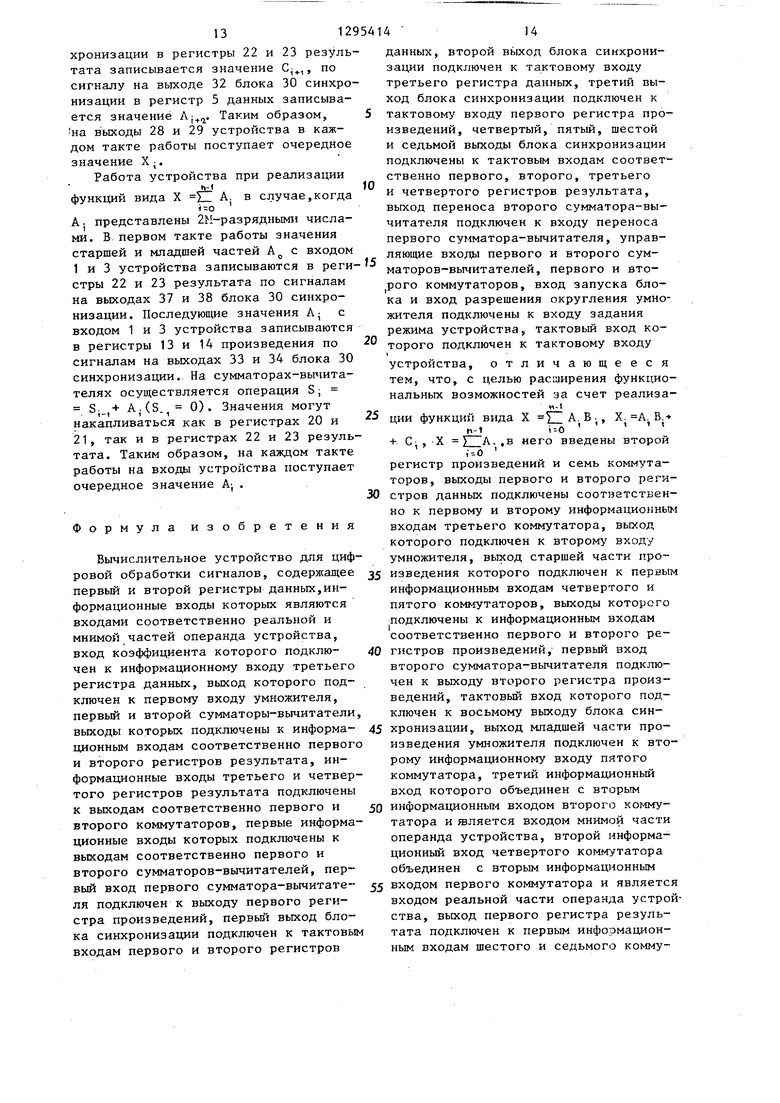

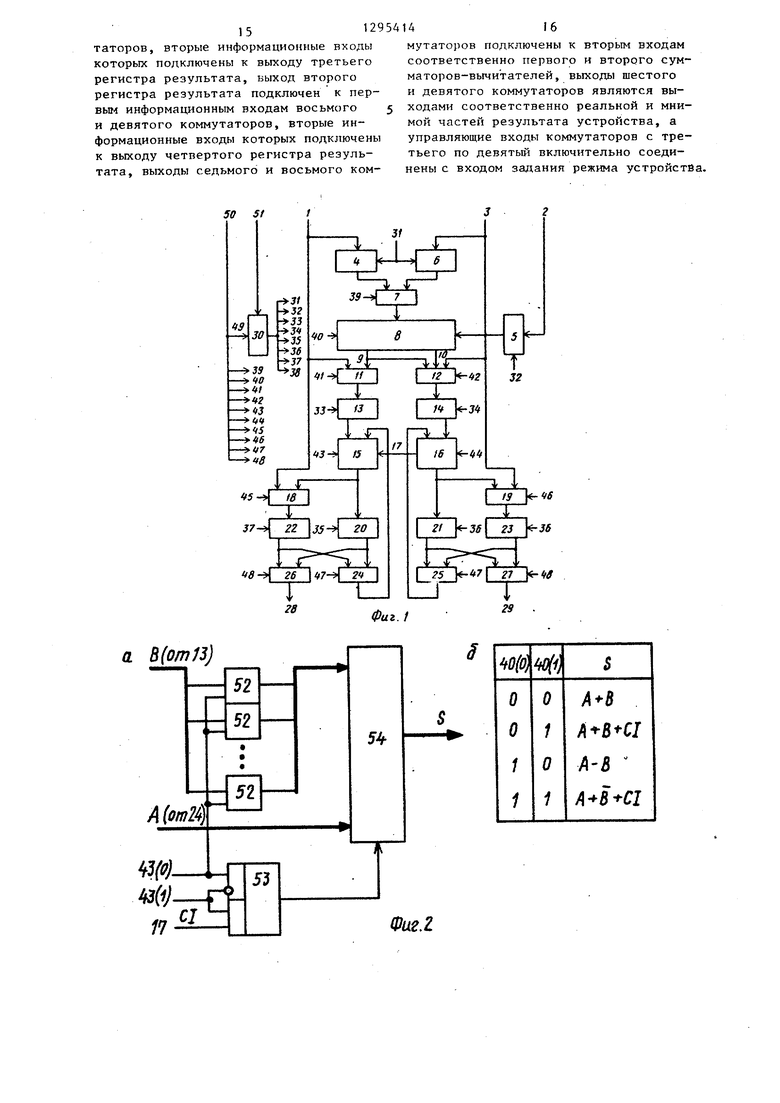

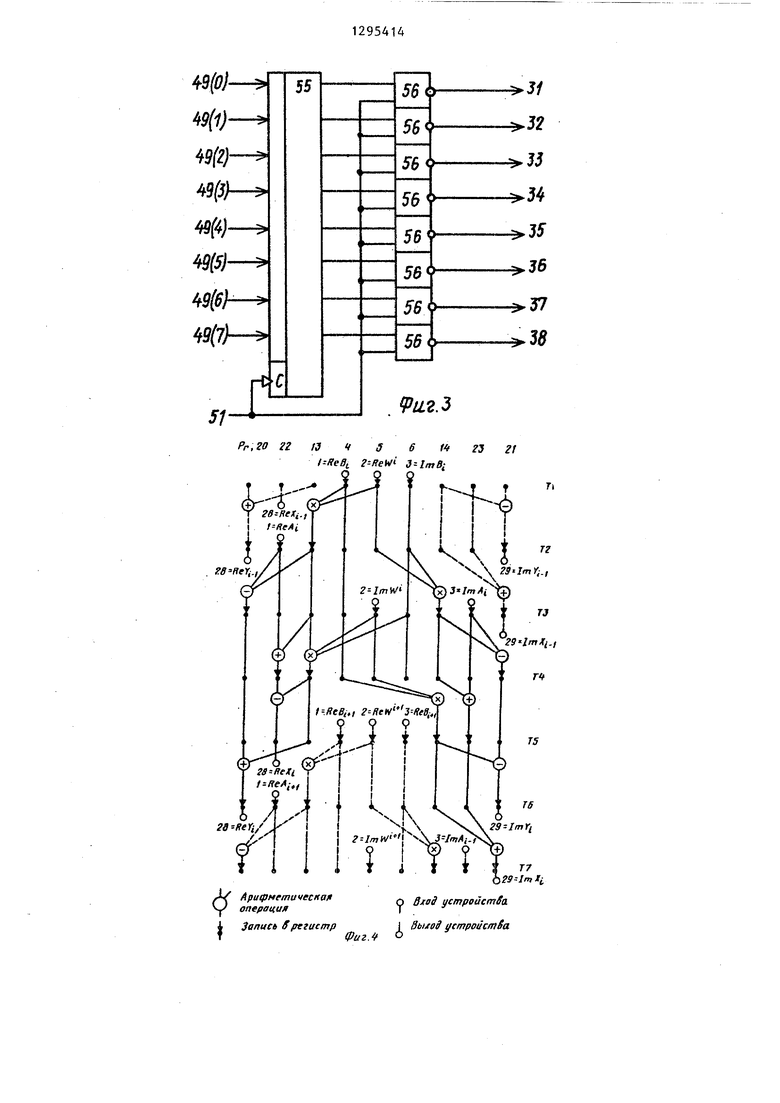

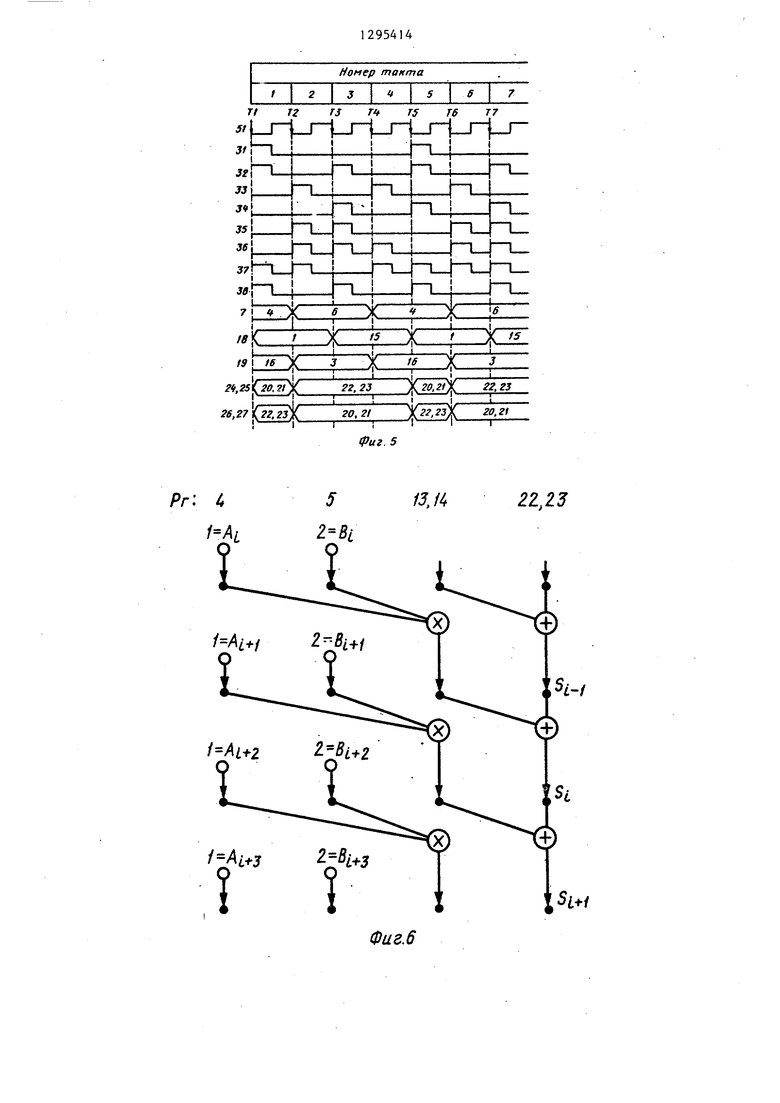

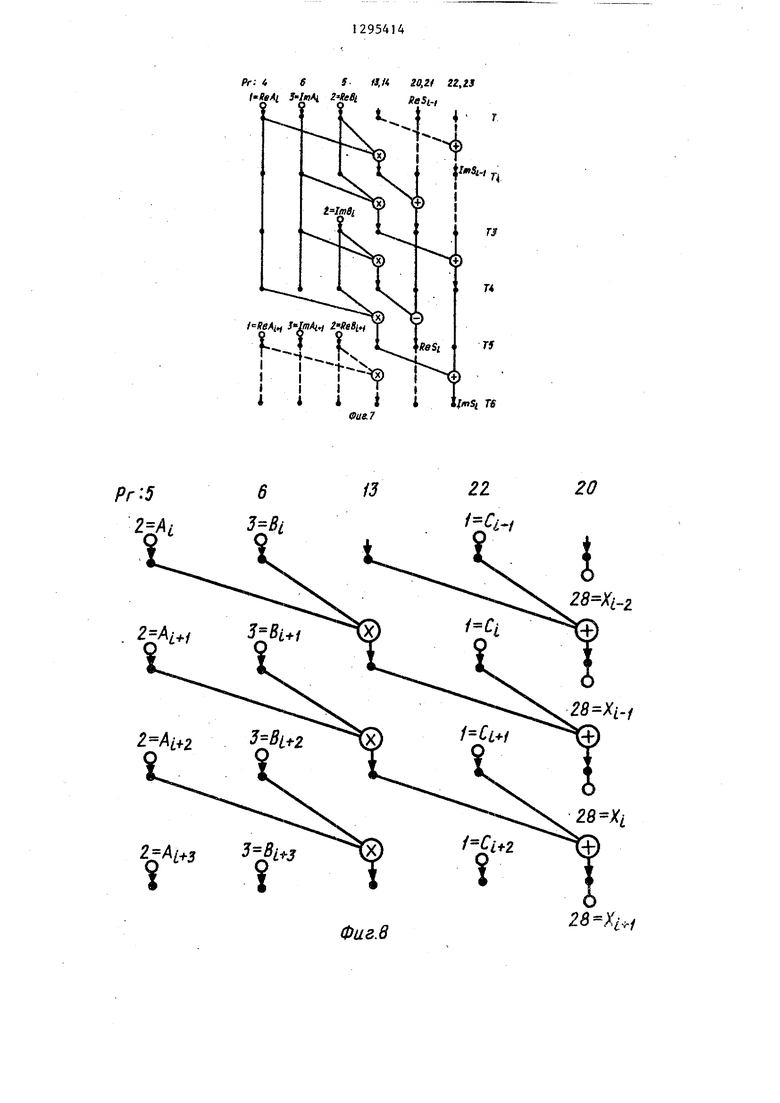

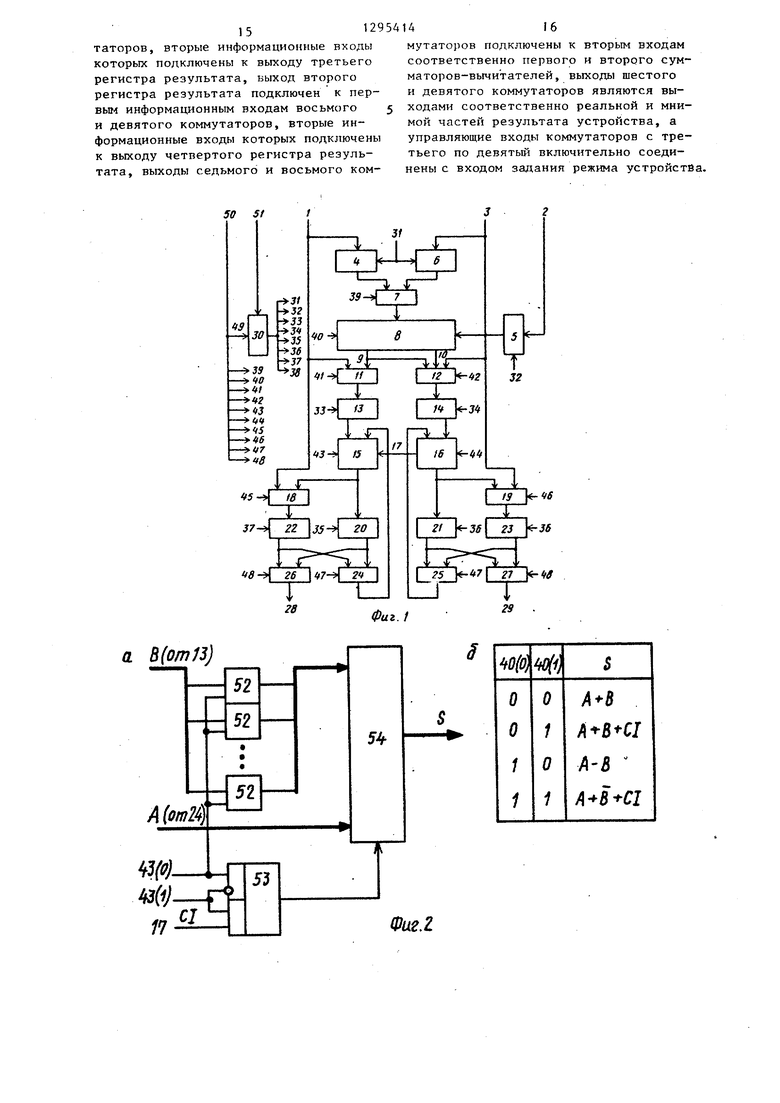

На фиг, 1 представлена структурная схема специализированного вьиис- лительного устройства; на фиг.2 вариант построения сумматора-вычита- теля и его таблица функционирования; на фиг. 3 - вариант построения блока синхронизации; на фиг. 4 -- граф функционирования вычислительного устройства при выполнении быстрого преоб- разования Фурье (ВПФ); на фиг. 5 - временная диаграмма управляющих сигналов при выполнении ВПФ; на фиг.6 - граф функционирования устройства при

h-T

вычислении функций вида X А.В:

: л

--0

при действительных А. и В- ; на фиг.7- граф функционирования устройства при

п-1

вычислении функций вида X 511 А. В

1-О

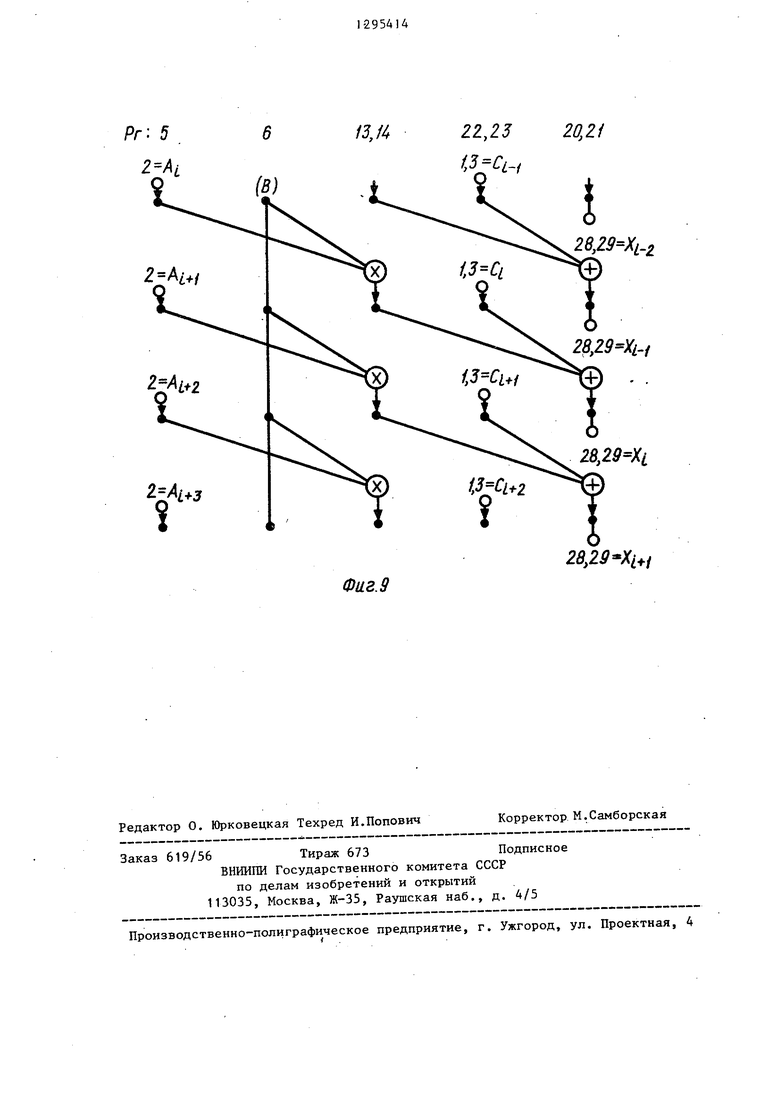

при комплексных Aj и В. ; на фиг.8 - граф функционирования устройства при вычислении функций вида X AJ В- +С; на фиг. 9 - граф функционирования устройства при вычислении функций вида X. A.BJ+CJ при постоянном В.

Вычислительное устройство содержит (фиг. 1) входы 1-3 реальной и мнимой частей операнда и коэффициента устройства, первый, второй и третий регистры 4-6 данных, коммутатор 7, умножитель 8, вьгход 9 старшей части произведения умножителя 8, выход 10 младшей части произведения умножителя 8, коммутаторы 11 и 12 произведения, . первый и второй регистры 13 и 14 произведения, первый и второй сумматоры- вычитатели 15 и 16, выход 17 переноса, коммутаторы 18 и 19 результата, первьш, второй, третий и четвертьв регистры 20-23 результата, коммутаторы 24 и 25 операнда, выходные коммутаторы 26 и 27, выходы 28 и 29 реальной и мнимой частей результата устройства, блок 30 синхронизации, вы- ходы 31-38 блока 30 синхронизации, вход 39 управления коммутатора 7, вход 40 разрешения округления результата умножителя 8 до старшей части

14 2

произведения, входы 41 и 42 управления коммутаторами 11 и 12 произведения, входы 43 и 44 управления сумматорами-вычитателями 15 и 16, входы 45 и 46 управления коммутаторами 18 и 19 результата, вход 47 управления коммутаторами 24 и 25 операнда, вход 48 управления выходными коммутаторами 26 и 27, вход 49 запуска блока 30 синхронизации, вход 50 задания режима состояний из управляющих полей 39-48 и тактовый вход 51 устройства.

Сумматор-вычитатель 15 (фиг. 2а) содержит информационные входы А и В, на которые поступают числа, представленные в дополнительном коде, вход переноса CI, уровень логической единицы на котором соответствует наличию входного переноса, злементы НЕРАВНОЗНАЧНОСТЬ 52 (по одному на каждый разряд входа В),, элемент 2И-ШТИ 53, сумматор 54 и информационный выход.

Операции сумматора-вычитателя осуществляются под управлением входов 43(0) и 43(1) в соответствии с таблицей (фиг.2Б).

Влок 30 синхронизации (фиг. 3) содержит восьмиразрядный управляющий вход 49(0)-49(7), регистр 55, срабатывающий по положительному фронту (переходу из уровня логического нуля в уровень логической единицы) синхросигнала, и элементы ИШ1-НЕ 56.

Работа устройства при выполнении ВПФ.

Устройство реализует базовую операцию БПФ по основанию 2.

X, А. + В.

V7

Y, А, - В1 W ; ReXj ReAj +ReBj Rew +ImB. ImW ; ImX, ImA. +ReB. ImW +lmB; ReW ; ReY; ReA.-ReB. ReW +ImB; ImW ; ImY. IroAj-ReB. ImW -ImB. ReW , де Aj и Bj - исходные отсчеты;

e

2У

N N

X ; и Yj - преобразованные отсчеты;весовой коэффициент;

количество отсчетов в исходном массиве;

действительная часть числа; Im - мнимая часть числа.

j ГТ, Re

31

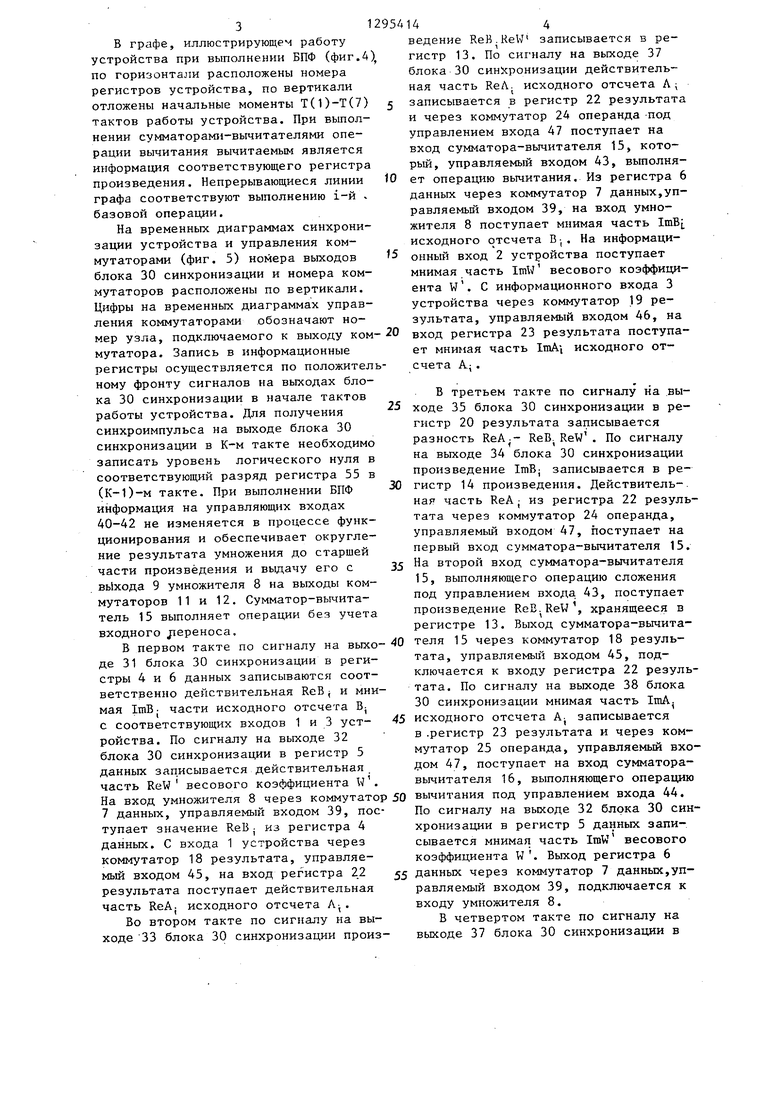

В графе, иллюстрирующем работу устройства при выполнении БПФ (фиг.4 по горизонтали расположены номера регистров устройства, по вертикали отложены начальные моменты Т(1)-Т(7) тактов работы устройства. При выполнении сумматорамя-вычитателями операции вычитания вычитаемым является информация соответствующего регистра произведения. Непрерывающиеся линии графа соответствуют выполнению i-й . базовой операции.

На временных диаграммах синхронизации устройства и управления коммутаторами (фиг. 5) номера выходов блока 30 синхронизации и номера коммутаторов расположены по вертикали. Цифры на временных диаграммах управления коммутаторами обозначают номер узла, подключаемого к выходу ком мутатора. Запись в информационные регистры осуществляется по положителному фронту сигналов на выходах блока 30 синхронизации в начале тактов работы устройства. Для получения синхроимпульса на выходе блока 30 синхронизации в К-м такте необходимо записать уровень логического нуля в соответствующий разряд регистра 55 в (К-1)-м такте. При выполнении БПФ информация на управляющих входах 40-42 не изменяется в процессе функционирования и обеспечивает округление результата умножения до старшей части произведения и выдачу его с вь1хода 9 умножителя 8 на выходы коммутаторов 11 и 12, Сумматор-вычита- тель 15 выполняет операции без учета входного jiepeHoca.

В первом такте по сигналу на выхо де 31 блока 30 синхронизации в регистры 4 и 6 данных записываются соответственно действительная ReB j и мнимая ImB части исходного отсчета В; с соответствующих входов 1 и 3 уст- ройства. По сигналу на выходе 32 блока 30 синхронизации в регистр 5 данных зацисывается действительная часть ReW весового коэффициента W . На вход умножителя 8 через коммутато 7 данных, управляемый входом 39, поступает значение ReB j из регистра 4 данных. С входа 1 устройства через коммутатор 18 результата, управляемый входом 45, на вход регистра 2,2 результата поступает действительная часть ReAj исходного отсчета Л-, .

Во втором такте по сигналу на выходе 33 блока 30 синхронизации произ5

54

5

5 0 35

0 45 0 55

144

ведение ReB.ReW записывается в регистр 13. По сигналу на выходе 37 блока 30 синхронизации действительная часть ReA. исходного отсчета Л записывается в регистр 22 результата и через коммутатор 24 операнда -под управлением входа 47 поступает на вход сумматора-вычитателя 15, который, управляемый входом 43, выполняет операцию вычитания. Из регистра 6 данных через коммутатор 7 данных,уп- равляемьш входом 39, на вход умножителя 8 поступает мнимая часть 1тВ исходного отсчета В;. На информаци- онныГ вход 2 устройства поступает мнимая часть ImW весового коэффициента W . С информационного входа 3 устройства через коммутатор 19 результата, управляемый входом 46, на вход регистра 23 результата поступает мнимая часть ImA , исходного отсчета А;.

В третьем такте по сигналу на выходе 35 блока 30 синхронизации в регистр 20 результата записывается разность ReA.- ReB. ReW . По сигналу на выходе 34 блока 30 синхронизации произведение ImB; записывается в регистр 14 произведения. Действитель-. ная часть ReA; из регистра 22 результата через коммутатор 24 операнда, управляемый входом 47, поступает на первый вход сумматора-вычитателя 15. На второй вход сумматора-вычитателя 15, выполняющего операцию сложения под управлением входа. 43, поступает произведение ReB.ReW хранящееся в регистре 13. Выход сумматора-вычитателя 15 через коммутатор 18 результата, управляемьш входом 45, подключается к входу регистра 22 результата. По сигналу на выходе 38 блока 30 синхронизации мнимая часть ImA. исходного отсчета А записывается в .регистр 23 результата и через коммутатор 25 операнда, управляемый входом 47, поступает на вход сумматора- вычитателя 16, выполняющего операцию вычитания под управлением входа 44. По сигналу на выходе 32 блока 30 синхронизации в регистр 5 данных записывается мнимая часть ImW весового коэффициента W . Выход регистра 6 данных через коммутатор 7 данных,управляемый входом 39, подключается к входу умножителя 8.

В четвертом такте по сигналу на выходе 37 блока 30 синхронизации в

JO

51295414

регистр 22 результата записываетсй сумма . По сигналу на выходе 36 блока 30 синхронизации в. регистр 21 результата записывается разность ImAj- ImBjReW . По сигналу на выходе 33 блока 30 синхронизации в регистр 13 записывается произведение ImB. ImW . Действительная часть исходного отсчета В., хранящаяся в регистре 4 данных, через коммутатор 7 данных, управляемый входом 39, поступает на вход умножителя 8. Регистр 22 результата через коммутатор 24 операнда, управляемый входом 47, подключается к входу сумматора-вычи- тателя 15, выполняющего операцию вычитания под управлейием входа 43.Выход сумматора-вычитателя 15 через коммутатор 18 результата, управляемый входом 45, подключается к входу регистра 22 результата. Мнимая часть IrnAj исходного отсчета А. из регистра 23 результата через коммутатор 23 операнда, управляемый входом 47,поматоре-вычитател е 16 под управлением входа 44 вычитается из значения ImAj-ImB. ReW , хранящегося в регистре 21 результата и поступающего на 5 .выход коммутатора 25 операнда под управлением входа 47. Аналогично работе устройства в первом такте в регистры 4 и 6 данных записываются соответственно действительная ,, и мнимая ImB, части исходного отсчета Bi

Vl f г

1+, в регистр 5 данных - действительная часть весового коэффициента W . Выход регистра 4 данных через коммутатор 7 данных, уп15 равляемый входом 39, подключается к входу умножителя 8. Вход 1 устройства, на который поступает действительная часть ReAj, исходного отсчета А,, , через коммутатор 18 результата,

20 |управляемый входом 45, подключается к входу регистра 22 результата.

В шестом такте по сигналу на выходе 35 блока 30 синхронизации вычисступает на вход сумматора-вычитателя ленное значение действительной части

ReYj ReAj-ReBj ReW +ImB, ImW преобразованного отсчета Y записывается в регистр 20 результата. По сигналу на выходе 36 блока 30 синхронизации

16, где суммируется с произведением ImB) под управлением входа 44. Выход сумматора-вычитателя 16 через коммутатор 19 результата, управляемый входом 46, подключается к входу регист- 30 вычисленное значение мнимой части m i t -. т TmV , TmA;-TmR. RpW -RpR.TmlJ nnprifi -

pa 23 результата. Ha входы 1 и 3 устройства поступают соответственно действительная ReB; и мнимая ImB части исходного отсчета В,, на вход 2 устройства поступает действительная часть ReW весового коэффициента W .

ImY ; ImA;-ImB. ReW преобразованного отсчета Yj записывается в регистр 21 результата. Через выходные коммутаторы 26 и 27, управ- 2 ляемые входом 48, действительная ReY и мнимая IY части преобразованного отсчета Y поступают соответственно

на выходы 28 и 29 устройства. Значение ImAj+ImBjReW , хранящееся в реВ пятом такте по сигналу с выхода 37 блока 30 синхронизации в регистр 22 результата записывается вычислен- :40 гистре 23 результата, через коммута- ное значение действительной, части ReXj ReAj +ReB. ReW -ImBj ImW преобразованного отсчета X., которое поступает на выход 28 устройства через

тор 25 операнда, управляемый входом 47, поступает на вход сумматора-вычитателя 16, где под управлением входа 44 суммируется с произведением

выходной коммутатор 26, управляемый 45 ReBjImW , хранящимся в регистре 14

входом 48. Значение , произведения. Аналогично работе устхранящееся в регистре 20 результата,

через коммутатор 24 операнда, управляемый входом 47, поступает на вход

ройства во втором такте в регистр 13 записывается произведение , в регистр 22 результата - действи- сумматора-вычитателя 15, где под уп- 50 тельная часть ReA, исходного отсче- равлением входа 43 суммируется с та А,. Сумматор-вычитатель 15 осу- произведением ImB/ ImW , хранящимся ществляет операцию ReAj,-ReBi,ReW в регистре 13 произведения. По сиг- регистр 6 данных через коммутатор 7 налу на выходе 38 блока 30 синхрони- данных подклншается к входу умножи- зации сумма ImA-+ImB. ReW записывает-55 теля 8, на вход 2 устройства посту- ся в регистр 23 результата. По сиг- пает мнимая часть весового коэффициента , на вход регистра 23 результата через коммутатор 19 результата с входа 3 устройства постуналу на выходе 34 блока 30 синхронизации в регистр 14 записывается произведение ReBjItiw , которое на сум

маторе-вычитател е 16 под управлением входа 44 вычитается из значения ImAj-ImB. ReW , хранящегося в регистре 21 результата и поступающего на .выход коммутатора 25 операнда под управлением входа 47. Аналогично работе устройства в первом такте в регистры 4 и 6 данных записываются соответственно действительная ,, и мнимая ImB, части исходного отсчета Bi

Vl f г

1+, в регистр 5 данных - действительная часть весового коэффициента W . Выход регистра 4 данных через коммутатор 7 данных, управляемый входом 39, подключается к входу умножителя 8. Вход 1 устройства, на который поступает действительная часть ReAj, исходного отсчета А,, , через коммутатор 18 результата,

|управляемый входом 45, подключается к входу регистра 22 результата.

вычисленное значение мнимой части TmV , TmA;-TmR. RpW -RpR.TmlJ nnprifi -

ImY ; ImA;-ImB. ReW преобразованного отсчета Yj записывается в регистр 21 результата. Через выходные коммутаторы 26 и 27, управ- ляемые входом 48, действительная ReY и мнимая IY части преобразованного отсчета Y поступают соответственно

на выходы 28 и 29 устройства. Значение ImAj+ImBjReW , хранящееся в регистре 23 результата, через коммута-

эффициента , на вход регистра 23 результата через коммутатор 19 результата с входа 3 устройства посту7 IraA.

пает мнимая часть IraA. хходного отсчета А..,

В седьмом такте по сигналу на выходе 36 блока 30 синхронизации вычисленное значение мнимой части ImX ; 1тпА;-«- ImB. ReU + ReB ImW преобразованного отсчета Х записывается в регистр 21 результата и через выходной коммутатор 27, управляемый входом

12954148

меняется в процессе функционирования и обеспечивает подключение выхода регистра 4 данных через коммутатор 7 данных к входу умножителя 8, отсутствие округления результата умножите ля 8 до старшей части произведения, подключение выхода 9 старшей части произведения умножителя 8 через коммутатор 11 произведения к входу ре48, поступает на выход 29 устройства. гистра 13 произведения, подключение

15

20

25

30

Вычисление последующих преобразовательных отсчетов производится аналогично вычислению X , и Y .

Таким образом, каждые четыре такта на выходы устройства поступают значения очередной пары преобразованных отсчетов.

При дальнейшем описании функционирования устройства предполагаем, что разрядность информационных узлов и шин равна М.

Работа устройства при вычислении

п-1

)ункций вида X

i:0

Устройство обеспечивает вычисление подобных функций, когда числа А ,- и В являются действительными, комплексными, либо одно из них является действительным, другое - комплексным. В устройствах обработки данных, представленных в формате с фиксированной запятой, часто возникает необходимость в снижении погрешности вычисления подобных функций, особенно при большом значении п. В предлагаемом устройстве эта задача решается за счет увеличения разрядности накапливаемой суммы. Если М - разрядно сть чисел, поступающих на вход умножителя, то промежуточные и конечный результаты вычислений могут быть получены в виде чисел разрядностью 2М. При этом быстродействие предлагаемого устройства не снижается, так как время умножения двух М-разряднык чисел, как правило, преБьш1ает время сложения двух 2М-раз- рядных чисел.

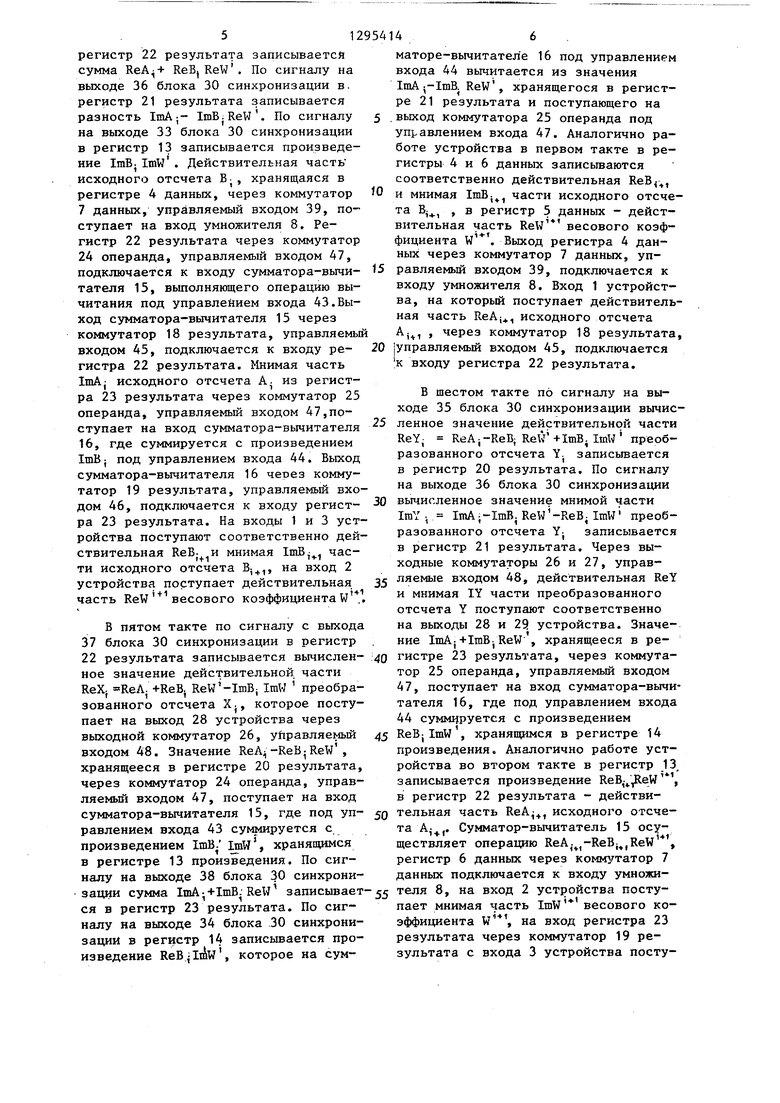

На -фиг. 6 представлен граф вычис- 50 ления предлагаемым устройством функций

h-1 X IZ А В. с использованием 2М-разьорядных произведений действительных

чисел А j и В. . Предполагаем, что значения А- и В. поступают соответст венно на информационные входы 1 и 2 устройства,.состояние управляющих входов 39-44,47 и 48 устройства не из35

40

45

выхода 10 младшей части произведения умножителя 8 через кся 1мутатор 12 про изведения к входу регистра 14 произведения , выполнение операции суммиро вания сумматорами-вычитателями 15 и 16 с учетом выходного переноса (выход 17). Выход регистра 22 результат через коммутатор 24 операнда подключается к входу сумматора-вычитателя 15, а через выходной коммутатор 26 - к выходу 28 устройства. Выход регист ра 23 результата через коммутатор 25 операнда подключается к входу сумма- тбра-вычитателя 16, а через выходной коммутатор 27 - к выходу 29 устройст ва. Перед началом накопления произведений в регистры 22 и 23 записывается нулевое значение, получаемое, например, на выходах сумматоров 18 и 19 результата под управлением вхо- доь 45 и 46, затем входы регистров 22 и 23 результата подключаются к выходам соответственно сумматоров- вычитателей 15 и 16.

В каждом такте работы устройства по сигналам на выходах 37 и 38 блок 30 синхронизации в регистры 22 и 23 результата записывается сумма Sj S- +А.В, по сигналам на выходах 33 и 34 блока 30 синхронизации в ре гистры 13 и 14 записываются значени соответственно старшей и младшей ча тей произведения А.В,, по сигнала на выходах 31 и 32 блока 30 синхрон зации в регистры 4 и 5 данных записываются значения соответственно А; и В.. Подобнььм образом устройство .функционирует до получения результата

-Vi-1

Вычисление функций вида ..X 111 А j

i-o при комплексных А. и В сводится к

вычислению выражений

55

1 I

ReX У (ReA; ReB -ImA; Хпш;;;

ImX (ReAjImB, +ImAiReB, ) ,

i 0

которые можно представить в виде ре курентных соотношений

4148

меняется в процессе функционирования и обеспечивает подключение выхода регистра 4 данных через коммутатор 7 данных к входу умножителя 8, отсутствие округления результата умножителя 8 до старшей части произведения, подключение выхода 9 старшей части произведения умножителя 8 через коммутатор 11 произведения к входу ре гистра 13 произведения, подключение

0

5

0

0

5

0

5

выхода 10 младшей части произведения умножителя 8 через кся 1мутатор 12 произведения к входу регистра 14 произведения , выполнение операции суммирования сумматорами-вычитателями 15 и 16 с учетом выходного переноса (выход 17). Выход регистра 22 результата через коммутатор 24 операнда подключается к входу сумматора-вычитателя 15, а через выходной коммутатор 26 - к выходу 28 устройства. Выход регистра 23 результата через коммутатор 25 операнда подключается к входу сумма- тбра-вычитателя 16, а через выходной коммутатор 27 - к выходу 29 устройства. Перед началом накопления произведений в регистры 22 и 23 записывается нулевое значение, получаемое, например, на выходах сумматоров 18 и 19 результата под управлением вхо- доь 45 и 46, затем входы регистров 22 и 23 результата подключаются к выходам соответственно сумматоров- вычитателей 15 и 16.

В каждом такте работы устройства по сигналам на выходах 37 и 38 блока 30 синхронизации в регистры 22 и 23 результата записывается сумма Sj S- +А.В, по сигналам на выходах 33 и 34 блока 30 синхронизации в регистры 13 и 14 записываются значения соответственно старшей и младшей частей произведения А.В,, по сигналам на выходах 31 и 32 блока 30 синхронизации в регистры 4 и 5 данных записываются значения соответственно А;, и В.. Подобнььм образом устройство .функционирует до получения результата X.

-Vi-1

Вычисление функций вида ..X 111 А j В/

i-o при комплексных А. и В сводится к

вычислению выражений

1 I

ReX У (ReA; ReB -ImA; Хпш;;;

ImX (ReAjImB, +ImAiReB, ) ,

i 0

которые можно представить в виде ре- курентных соотношений

9 12954

ReS| ReS. +ReA ReB; -ImAj ImB. ; ImSj IinS.+ReA. ImB. H-ImAjReBj ,

где i 0,1,...,n-1; ReS., 0; ImS., 0.

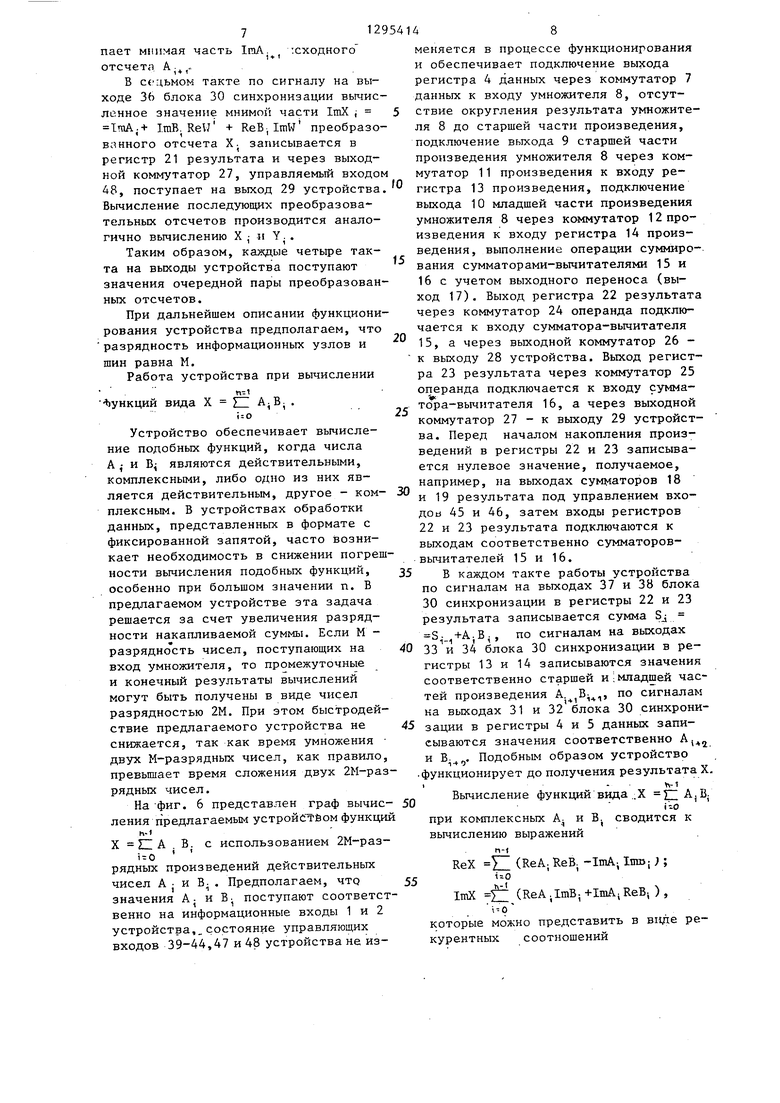

Граф (фиг. 7) иллюстрирует функционирование устройства при вычислении этих выражений при 2М-разрядных промежуточных результатах. Перед на- }0 чалом вычислений в регистры 22 и 23 результата записывается нулевое значение, затем состояние управляющих входов 40-42, 45 и 46 устройства не изменяется и обеспечивает отсутствие 15 округления результата умножителя 8 до старшей части произведения, подключение выходов 9 и 10 старшей и младшей частей произведения к входам соответственно регистров 13 и 14, 20 подключение выходов сумматоров-вычи- тателей 15 и 16 к входам соответственно регистров 22 и 23 результата. Значения ImB- поступаю соответственно на входы 1 и 3 устройст- 25 ва, значения ReSj и ImSj поочередно поступают на вход 2 устройства.Операции сумматоров-вычитателей 15 и 16 осуществляются с учетом выходного переноса (выход 17).Значения ReS; накап-30 ливаются в регистрах 20 и 21 результата, значения ImS; - в регистрах 22 и 23 результата.

В первом такте по сигналу на выходе 31 блока 30 синхронизации в 35 регистры 4 и 6 данных записываются соответственно значения ReAj и IraA., по сигналу на выходе 32 блока 30 синхронизации в регистр 5 данных записывается значение ReB j. Выход регистра 40 4 данных через коммутатор 7 данных, управляемый входом 39, подключается к входу умножителя 8.

Во втором такте по сигналам на выходах 33 и 34 блока 30 синхронизации 5 старшая и младшая части произведения ReA. ReBj умножителя 8 записываются соответственно в регистры 13 и 14. Значение ReS;, хранящееся в регистрах 20 и 21 результата, суммируется JQ с.произведением на суммато- рах вычитателях 15 и 16. На вход умножителя 8 через коммутатор 7 данных, управляемый входом 39, поступает значение ImA- из регистра 6 данных. На вход 2 устройства поступает значение ImB. .

В третьем такте по сигналам на вы ходах 35 и 36 блока 30 синхронизации

1410

в регистры 20 и 21 результата записывается значение ReSj,+ReA. ReB. .По сигналам на выходах 33 и 34 блока 30 синхронизации в регистры 13 и 14 записывается произведение ImA-ReB и суммируется на сумматорах-вычитате- лях 15 и 16 со значением ImSj., , которое поступает на выходы коммутаторов 24 и 25 операнда с выходов регистров 22 и 23 результата под управлением входа 47. Выход сумматора-вычи- тателя 15 через коммутатор 18 результата, управляемый входом 45, подключается к входу регистра 22 результата. Выход сумматора-вычитателя 16 через коммутатор 19 результата, управляемый входом 46, подключается к входу регистра 23 результата. По сиг- налу с выхода 32 блока 30 синхронизации в регистр 5 данных записывается значение 1иВ., На вход умножителя 8 через коммутатор 7 данных, управляемый входом 39, поступает значение ImA; из регистра 6 данных.

В четвертом такте по сигналам на вьпходах 37 и 38 блока 30 синхрочиза- ции в регистры 22 и 23 результата за пи-сывается значение ImS;.,+IraA)ReB . По сигналам на выходах 33 и 34 блока 30 синхронизации в регистры 13 и 14 записывается произведение 1т/ь1шВ, которое вычитается на сумматорах- вычитателях t5 и 16 из значения ReS.,-«-ReAj ReB| , поступающего на выходы коммутаторов 24 и 25 операнда с выходов регистров 20 и 21 результата под управлением входа 47. На вход умножителя 8 через коммутатор 7 данных, управляемый входом 39, поступает значение ReAj из регистра 4 данных. На входы 1 - 3 устройства поступают соответственно значения ReA, ,ReB;, .и ImA, .

В пятом такте по сигналам на вы-, ходах 35 и 36 блока 30 синхронизации в регистры 20 и 21 результата записы- вается значение ReSj ReS,..,+ReAj ReB - -ImA; ImB .По сигналам на выходах 33 и 34 блока 30 синхронизации в регистры 13 и 14 записывается произведение ReAj ImBj , которое суммируется на сум- маторах-вычитателях 15 и 16 со значением ImSj.,+ ImA-ReBj, поступакицим на выходы коммутаторов 24 и 25 операнда с выходов регистров 22 и 23 результата под управлением входа 47. Выход суьжатора-вычитателя 15 подключается к входу регистра 22 результата с помощью коммутатора 18 результата, упрашшемого входом 45. Выход сумматора-вычитателя 16 подключается к входу регистра 23 результата с помощью коммутатора 19 результата, управляемого входом 46. Аналогично работе устройства в первом такте в регистры 4-6 записываются значения соответственно ReAj.ReB и ImA. , на вход умножителя 8 через коммутатор 7 данных поступает значение ReA,.

В шестом такте по сигналам на выходах 37 и 38 блока 30 синхронизации в регистры 22 и 23 результата записывается значение 1тЗ| lmS. +1тА. КеВ + ReAjImBj. Дальнейшие этапы вычислений аналогичны описанным.

Таким образом, каждые четыре такта устройство начинает обработку очередной пары комплексных значений А и Bj

При использовании М-разрядных промежуточных значений при вычислении

j функций вида X . достаточно

использования одного из сумматоров- вычитателей и соответствующих регистров в каждом такте работы устройства Результат умножения в этом случае может быть получен как усеченным,так и округленным до старшей части произведения.

Работа устройства при вычислении

функций вида X

Л,В.

+ С;

где все

переменные представлены М-разрядными числами.

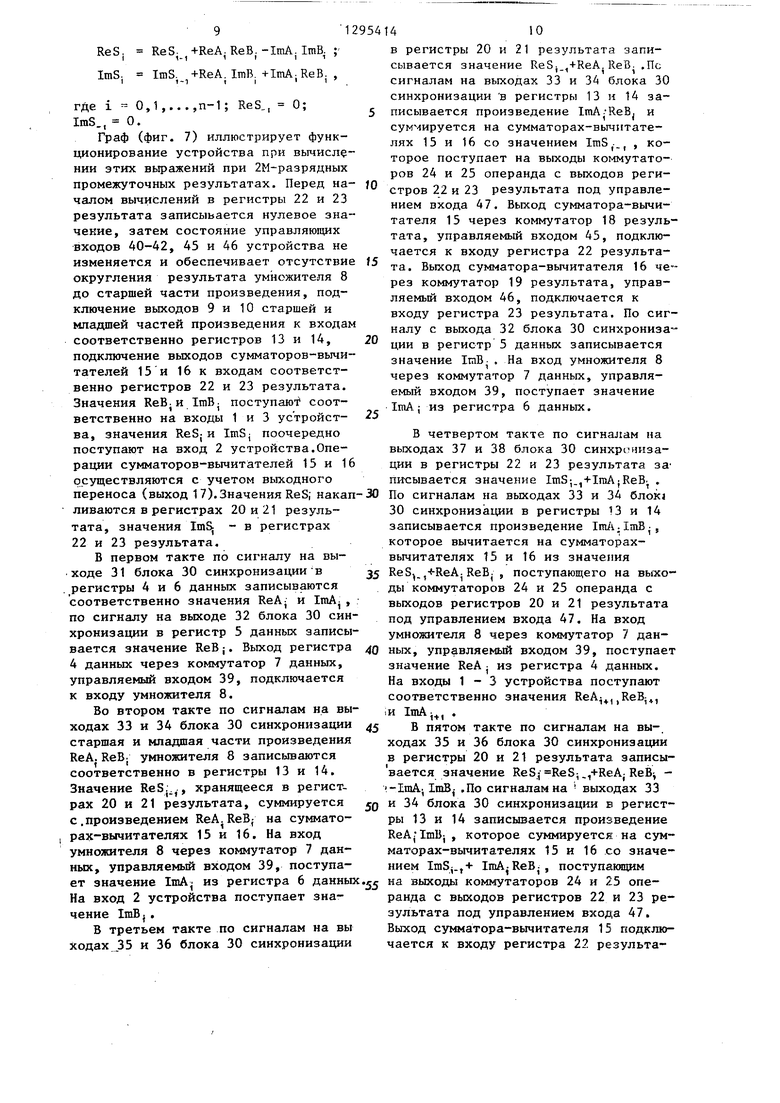

В этом случае функционирование устройства может быть проиллюстрировано графом, представленным на

30 на фиг. 9. Значения А; поступают на вхоп, 2 устройства, старшая и младшая части С; поступают соответственно на входы 1 и 3 устройства. Состояние управляющих входов 39-48 устройства

35 не изменяется и обеспечивает подключение выхода регистра 6 данных через коммутатор 7 данных к входу умножителя В, выхода 9 старшей части произведения умножителя 8 через коммуфиг. 8. Значения А|, В- и С; поступа- 40 татор 11 произведения к входу региют соответственно на входы Z, 3 и 1 устройства. Состояние управляющих входов 39, 41, 43, 45, 47 и 48 устройства не изменяется и обеспечивает

стра 13 произведения, выхода 10 младшей части произведения умножителя 8 через коммутатор 12 произведения к входу регистра 14 произведения,входа

подключение выхода регистра 6 данных 45 1 устройства через коммутатор 18 результата к входу регистра 22 результата, входа 3 устройства через коммутатор 19 результата к входу регистра 23 результата, выходов регистзультата к входу регистра 22 результата, входа 3 устройства через коммутатор 19 результата к входу регистра 23 результата, выходов регистчерез коммутатор 7 данных к входу умнохмтеля 8, выхода 9 старшей части произведения умножителя 8 через коммутатор 11 произведения к входу регистра 13 произведения, входа 1 устрой- 50 Ров 22 и 23 результата к входам соот- ства через коммутатор 18 результата ветственно коммутаторов 2А и 25 опе- к входу регистра 22 результата, выхода регистра 22 результата через коммутатор 24 операнда к входу сумматора-вычитателя 15, выхода регис.тра 55 20 результата через выходной коммутатор 26 к выходу 28 устройства. Сум- матор-вычитатель 15 выполняет операранда, выходов регистров 20 и 21 результата к входам коммутаторов 26 и 27. Производится запись значения X . А В + Cj в регистр. По сигналам на выходах 33 и 34 блока 30 синхронизации в регистры 13 и 14 записывается произведение А.,В , по сигналам на выходах 37 и 38 блока 30 сш

цию суммирования без учета входного

переноса (выход 17). Результат умножителя 8 может использоваться как округленным, так и усеченным до старшей части произведения.

В каждом такте работы устройства по сигналу на выходе 35 блока 30 синхронизации производится запись значения X . , + Ci в регистр 20 результата, по сигналу на выходе 33 блока 30 синхронизации в регистр 13 записывается произведение А.В,-, по сигналу на выходе 37 блока 30 синхронизации в регистр 22 результата записывается значение С,, по сигналу на выходе 31 блока 30 синхронизации

в регистр 6 данных - значение по сигналу на выходе 32 блока 30 синхронизации в регистр 5 данных - значение Л.. Таким образом, в каждом такте работы на выход 28 устройства поступает очередное значение X .

В некоторых задачах требуется вычисление функций вида X , А--В + С,

5 где В является М-разрядной константой, А; представлено М-разрядным числом, а X; и Q - 2М-разрядными числами. Граф, иллюстрирующий работу устройства в данном случае, представлен

0 на фиг. 9. Значения А; поступают на вхоп, 2 устройства, старшая и младшая части С; поступают соответственно на входы 1 и 3 устройства. Состояние управляющих входов 39-48 устройства

5 не изменяется и обеспечивает подключение выхода регистра 6 данных через коммутатор 7 данных к входу умножителя В, выхода 9 старшей части произведения умножителя 8 через коммутатор 11 произведения к входу регистра 13 произведения, выхода 10 младшей части произведения умножителя 8 через коммутатор 12 произведения к входу регистра 14 произведения,входа

1 устройства через коммутатор 18 результата к входу регистра 22 результата, входа 3 устройства через коммутатор 19 результата к входу регистра 23 результата, выходов регистРов 22 и 23 результата к входам соот- ветственно коммутаторов 2А и 25 опе-

Ров 22 и 23 результата к входам соот- ветственно коммутаторов 2А и 25 опе-

ранда, выходов регистров 20 и 21 результата к входам коммутаторов 26 и 27. Производится запись значения X . А В + Cj в регистр. По сигналам на выходах 33 и 34 блока 30 синхронизации в регистры 13 и 14 записывается произведение А.,В , по сигналам на выходах 37 и 38 блока 30 сш

хронизации в регистры 22 и 23 результата записывается значение С,, по сигналу на выходе 32 блока 30 синхронизации в регистр 5 данных записывается значение Л,. Таким образом, на в ыходы 28 и 29 устройства в каждом такте работы поступает очередное значение X;.

Работа устройства при реализации

функций вида X L- А. в случае,когда

А. представлены 2М-разрядными числами. В первом такте работы значения

данных, второй вькод блока синхронизации подключен к тактовому входу третьего регистра данных, третий выход блока синхронизации подключен к тактовому входу первого регистра произведений, четвертый, пятый, шестой и седьмой выходы блока синхронизации подключены к тактовым входам соответ ственно первого, второго, третьего и четвертого регистров результата, выход переноса второго сумматора-вы- читателя подключен к входу переноса первого сумматора-вычитателя, управляющие входы первого и второго сумстаршей и младшей частей А с входом

4 f ч- xi tJiv JJ - l J - У i T.

1 и 3 устройства записываются в реги- 5 маторов-вычитателей, первого и вто- стры 22 и 23 результата по сигналам аго коммутаторов, вход запуска бло- на выходах 37 и 38 блока 30 синхронизации. Последующие значения А; с входом 1 и 3 устройства записываются в регистры 13 и 14 произведения по сигналам на выходах 33 и 34 блока 30 синхронизации. На сумматорах-вьпшта- телях осуществляется операция S; S + A.(S. 0). Значения могут накапливаться как в регистрах 20 и 21, так и в регистрах 22 и 23 результата. Таким образом, на каждом такте

20

25

ка и вход разрешения округления умножителя подключены к входу задания режима устройства, тактовый вход которого подключен к тактовому входу

устройства, отличающееся тем, что, с ц€;лью расширения функциональных возможностей за счет реализаH-t

+ с

1

ции функций вида X ЩА. Б-, X. А. В.

h-t1 0 t

X ЩА.,В него введены второй

i--0

регистр произведений и семь коммутаторов, выходы первого и второго реги- 30 стров данных подключены соответственно к первому и второму информационным входам третьего коммутатора, выход которого подключен к втором входу умножителя, выход старшей части про- ровой обработки сигналов, содержап1ее 35 изведения которого подключен к первым

работы на входы устройства поступает очередное значение Aj .

Формула изобретения Вычислительное устройство для цифпервый и второй регистры данных,информационные входы которых являются входами соответственно реальной и мнимой частей операнда устройства, вход коэффициента которого подключен к информационному входу третьего регистра данных, выход которого подключен к первому входу умножителя.

информационным входам четвертого и цятого коммутаторов, выходы которого подключены к информационным входам соответственно первого и второго ре- 40 гистров произведений, первый вход второго сумматора-вычитателя подключен к выходу второго регистра произведений, тактовый вход которого подключен к восьмому выходу блока синпервый и второй сумматоры-вычитатели, выходы которых подключены к информа- 45 хронизации, выход младшей части про- ционным входам соответственно первого изведения умножителя подключен к вто- и второго регистров результата, ин- рому информационному входу пятого формационные входы третьего и четвер- коммутатора, третий информационный того регистров результата подключены вход которого объединен с вторым к вькодам соответственно первого и 50 информационным входом второго комму- второго коммутаторов, первые информа- татора и является входом мнимой части

ционные входы которых подключены к выходам соответственно первого и второго сумматоров-вычитателей, первый вход первого сумматора-вычитате- 55 входом первого коммутатора и является ля подключен к выходу первого реги- входом реальной части операнда устрой- стра произведений, первьй выход бло- ства, выход первого регистра резуль- ка синхронизации подключен к тактовым тата подключен к первьм инфо}эмацион- входам первого и второго регистров ным входам шестого и седьмого коммуданных, второй вькод блока синхронизации подключен к тактовому входу третьего регистра данных, третий выход блока синхронизации подключен к тактовому входу первого регистра произведений, четвертый, пятый, шестой и седьмой выходы блока синхронизации подключены к тактовым входам соответ ственно первого, второго, третьего и четвертого регистров результата, выход переноса второго сумматора-вы- читателя подключен к входу переноса первого сумматора-вычитателя, управляющие входы первого и второго сум ч- xi tJiv JJ - l J - У i T.

маторов-вычитателей, первого и вто- аго коммутаторов, вход запуска бло-

маторов-вычитателей, первого и вто- аго коммутаторов, вход запуска бло-

ка и вход разрешения округления умножителя подключены к входу задания режима устройства, тактовый вход которого подключен к тактовому входу

устройства, отличающееся тем, что, с ц€;лью расширения функциональных возможностей за счет реализа 5 маторов-вычитателей, пер аго коммутаторов, вход

25

H-t

ции функций вида X Щ

маторо аго к

+ с

1

информационным входам четвертого и цятого коммутаторов, выходы которого подключены к информационным входам соответственно первого и второго ре- 40 гистров произведений, первый вход второго сумматора-вычитателя подключен к выходу второго регистра произведений, тактовый вход которого подключен к восьмому выходу блока син45 хронизации, выход младшей части про- изведения умножителя подключен к вто- рому информационному входу пятого коммутатора, третий информационный вход которого объединен с вторым 50 информационным входом второго комму- татора и является входом мнимой части

операнда устройства, второй информационный вход четвертого коммутатора объединен с вторым информационным

15129

таторов, вторые информацион ые входы которых подключены к выходу третьего регистра результата, выход второго регистра результата подключен к первым информационным входам восьмого и девятого коммутаторов, вторые информационные входы которых подключены к выходу четвертого регистра результата, выходы седьмого и восьмого ком1416

мутаторов подключены к вторым входам соответственно первого и второго сум- маторов-вычитателей, выходы шестого и девятого коммутаторов являются выходами соответственно реальной и мнимой частей результата устройства, а управляющие входы коммутаторов с третьего по девятый включительно соединены с входом задания режима устройст

50 St

а В(о/п13)

/7

Фи22

49(

9(1)-

9{2)- 49fJb

{4}- {5}- 9(6)- 9(7h

5Г

566

J/

56

56

35

56

J6j

5

Рг.го гг 13 ч g # r« /j

.

о о Арифнети ческам операция

Запись Sрегистр

--//77rt JVw/ -

М 1 ГТ.

b; i --/ 4/i О Влад ycmpoucmSa

Фиг.

I 8bifo3 i/cmpoticmSa

л I

I 8bifo3 i/cmpoticmSa

г/

гг

n,2S l20.l

ГТ

26,27 |(ггз

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1327120A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Устройство для вычисления быстрого преобразования Фурье | 1989 |

|

SU1619300A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1984 |

|

SU1242986A1 |

| Устройство для быстрого преобразования Фурье | 1981 |

|

SU1013971A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Арифметическое устройство для быстрого преобразования Фурье | 1986 |

|

SU1383394A2 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1267431A1 |

| Процессор быстрого преобразования Фурье | 1988 |

|

SU1667101A1 |

| Устройство для цифровой фильтрации | 1988 |

|

SU1647592A1 |

Изобретение относится к автоматике и вычислительной технике и может / быть использовано при построении ЭВМ, в частности процессоров цифровой обработки сигналов. Устройство обеспечивает реализацию быстрого преобраэоh-1 вания Фурье функций вида Х .,Х., А.В. +с. 1 отличается М-1 X C:AJ и 1.0 повышенной контролепригодностью. Ин- формация с входных шин поступает в регистры данных. Произведение с выхода умножителя поступает в регистры и подвергается обработке на суммато- рах-вычитателях совместно с информацией, хранящейся в регистрах результата. Операции сумматора-вычитателя могут осуществляться как с учетом, так и без учета выхода переноса второго сумматора-вычитателя . Мультиплексирование информации осуществляется коммутаторами. Управление работой осуществляется входом задания ре- :жима и блоком синхронизации. 9 ил i СЛ

Д/4

Фиг. 6

6

S liaAi Z geSi ОО

5 «,« zo,n гг,гз

eeSi-i

Z fsSin

--Ц

1 i 1 1

Фае.7

rjr

W

ТУ

llmSi rs

Фиг.8

20,Zi

28,.2

28,.

2B,

Редактор 0. Юрковецкая Техред И.Попович

Заказ 619/56 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

Фиг.9

2a,29-Xi f

Корректор М.Самборская

| УСТРОЙСТВО ДЛЯ ОГЛУШЕНИЯ ЖИВОТНЫХ ПЕРЕД ИХ УБОЕМ | 1972 |

|

SU424552A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1981 |

|

SU1020833A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-07—Публикация

1985-07-02—Подача