и вт-орои входы триггера подключены соответственно к первому и второму выходам блока, а первый и второй выходы - соответственно к первым входам первого и второго элементов И, вторые входы которых соединены соответственно с пятым и четвертым Е;ходами ; блока5 а выходы - соответственно с 103 72 первым входом элемента ИЛИ и первым выходом блока, первый и второй входы третьего элемента И соединены соответственно с третьим входом блока и вторым выходом триггера, а выход с вторым входом элемента ИЛИ, подключенного выходом через формирователь аналогового сигнала к выходу блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с кассетным магнитофоном звукозаписи | 1983 |

|

SU1101811A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1985 |

|

SU1291989A1 |

| Устройство для сопряжения цифровой вычислительной машины с кассетным магнитофоном звукозаписи | 1982 |

|

SU1075249A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1986 |

|

SU1416992A1 |

| Устройство для сопряжения цифровойВычиСлиТЕльНОй МАшиНы C КАССЕТНыММАгНиТОфОНОМ зВуКОзАпиСи | 1979 |

|

SU798787A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1980 |

|

SU903854A1 |

| Устройство для сопряжения магнитофона с ЦВМ | 1987 |

|

SU1427374A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном звукозаписи | 1985 |

|

SU1260969A2 |

| Устройство для связи цифровой вычислительной машины с магнитофоном | 1982 |

|

SU1065853A1 |

1. УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАССЕТНЫМ МАГНИТОФОНОМ ЗВУКОЗАПИСИ, .содержащее блок синхронизации, канал ввода, блок модуляции, выход которого является аналоговым информационным выходом устройства, фильтр низких частот и канал вывода, включающий компаратор, делитель напряжения, формирователь импульса и цифровойанализатор частот, причем первый и второй выходы блока синхронизации соединены соответственно с первым и вторым входами канала ввода, а выход - с входом опорной частоты устройства и первым входом цифрового анализатора частот, второй вход которого соединен с шиной питающего напряжения,а третий вход через формирователь импульса - с выходом компаратора, первый вход которого соединен через фильтр низких частот с аналоговым информационным входом устройства, второй вход и выход компаратора соединены соответственно с выходом и входом делителя напряжения, отличающееся тем, что, с целью повышения достоверности обмена, в него введены преобразователь параллельного кода в последовательный, преобразователь последовательного кода в параллельный и селектор импульса, причем информационный вход преобразователя параллельного кода в последовательный соединен с цифровым информационным входом устройства, первый и второй управляющие входы соответственно с первыми выходом и входом блока модуляции, а выход с третьим входом канала ввода, первый и второй входы которого подклюсл чены соответственно к второму и третьему входам блока модуляции, соединенного соответственно четвертым, пятым и первым входами с первым и третьим выходами блока синхронизации и управляющим входом устройства, первый аход и выход селектора импульса подключен соответственно к аналогосо ю вому информационному входу устройства и управляющему выходу устройства, а 4 второй вход - к первому выходу преvj образователя последовательного кода 1чЭ в параллельный, первый и -второй входы которого соединены соответственно с третьим входом и выходом цифрового анализатора частот, а второй выход с цифровым информационным выходом устройства. 2. Устройство по п. 1, отличающееся тем, что блок модуляции содержит триггер, три элемента И, элемент ИЛИ и формирователь аналогового сигнала, причем первый

1

Изобретение относится к вычислительной технике и может быть исполь. зовано для сопряжения кассетного магнитофона с цифровой вычислительной машиной.

Известно устройство сопряжения, содержащее канал вывода, соединенный первыми входами и выходом соответственно с цифровым входом и аналоговым выходом устройства, а вторым и третьим входами - с соответствующими выходами блока синхронизации, и канал вывода, включающий делитель напряжения, компаратор, формирова.тель импульса и цифровой анализатор частот, выход которого является цифровым выходом устройства СОНедостаток данного устройства состоит в низкой достоверности обмена.

Наиболее близким к предлагаемому, по технической сущности является устройство сопряжения ЦВМ с магнитофоном, содержащее канал вывода, состоящий из элемента НЕ, триггера синхронизации, формирователя аналогового сигнала и блока модуляции, блок синхронизации и канал вывода, состоящий из полосового фильтра, делителя напряжения, компаратора, формирователя, импульса и цифрового анализатора частот, блок модуляции канала ввода содержит два элемента И, элемент ИЛИ и триггер, а цифровой анализатор частот канала вывода состоит из пяти триггеров, двух элементов И, счетчика и элемента ИЛИ 2.

Недостаток данного устройства состоит в низкой достоверности обмена информацией, так как в нем отсутствует побайторая синхронизация и обмен с ЦВМ ведется последовательным кодом

Цель изобретения - повышение достоверности обмена информацией.

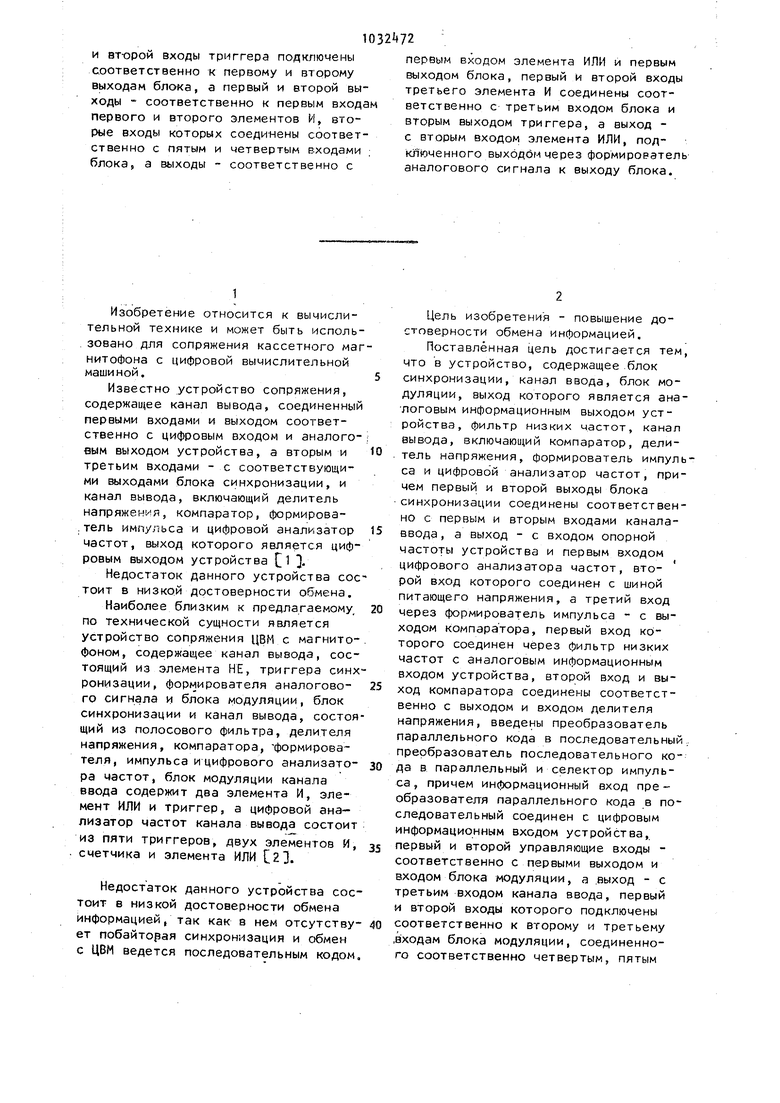

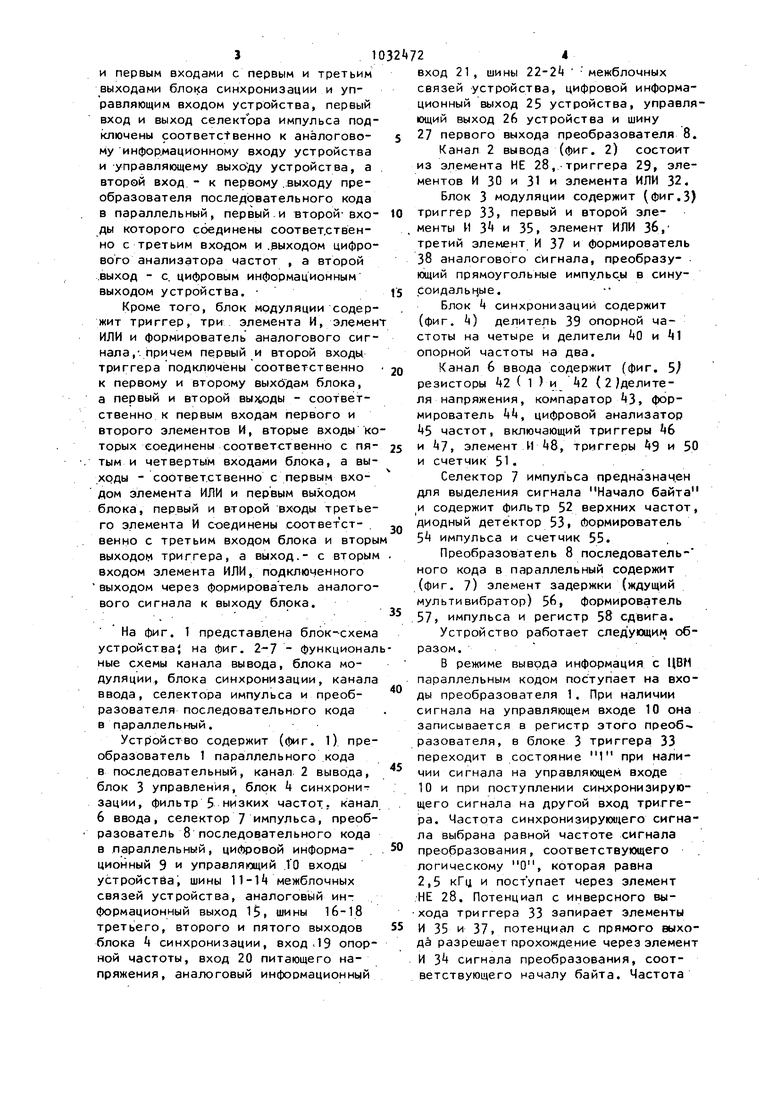

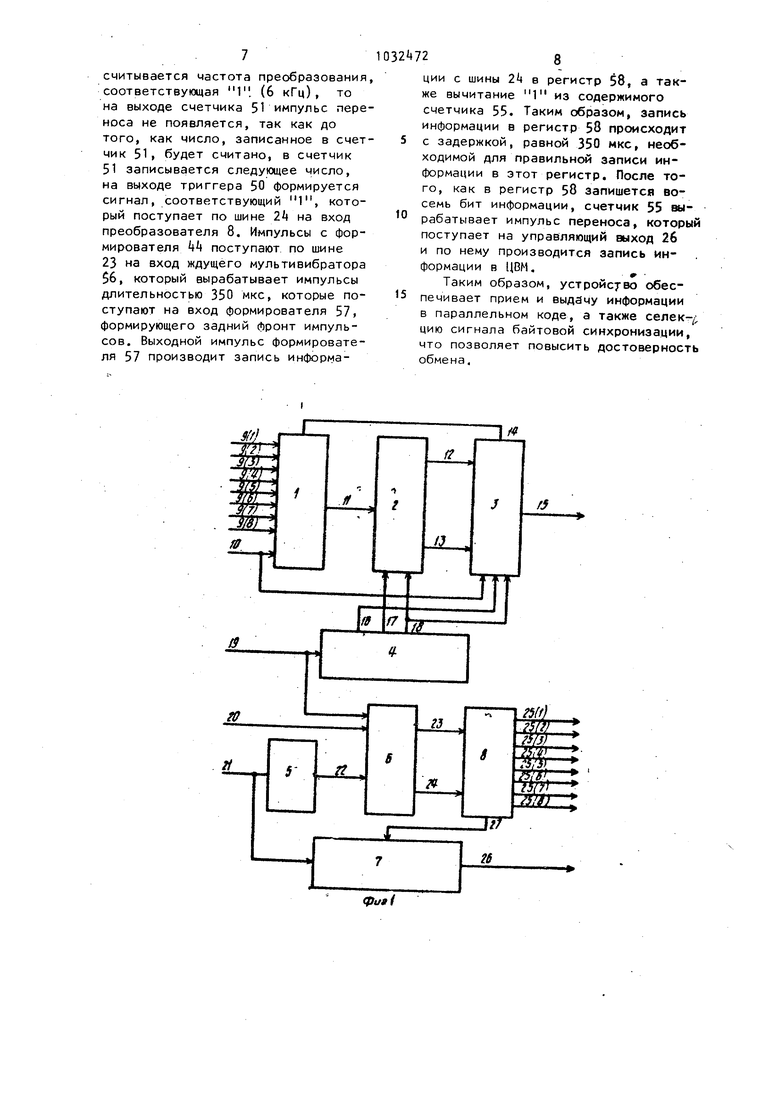

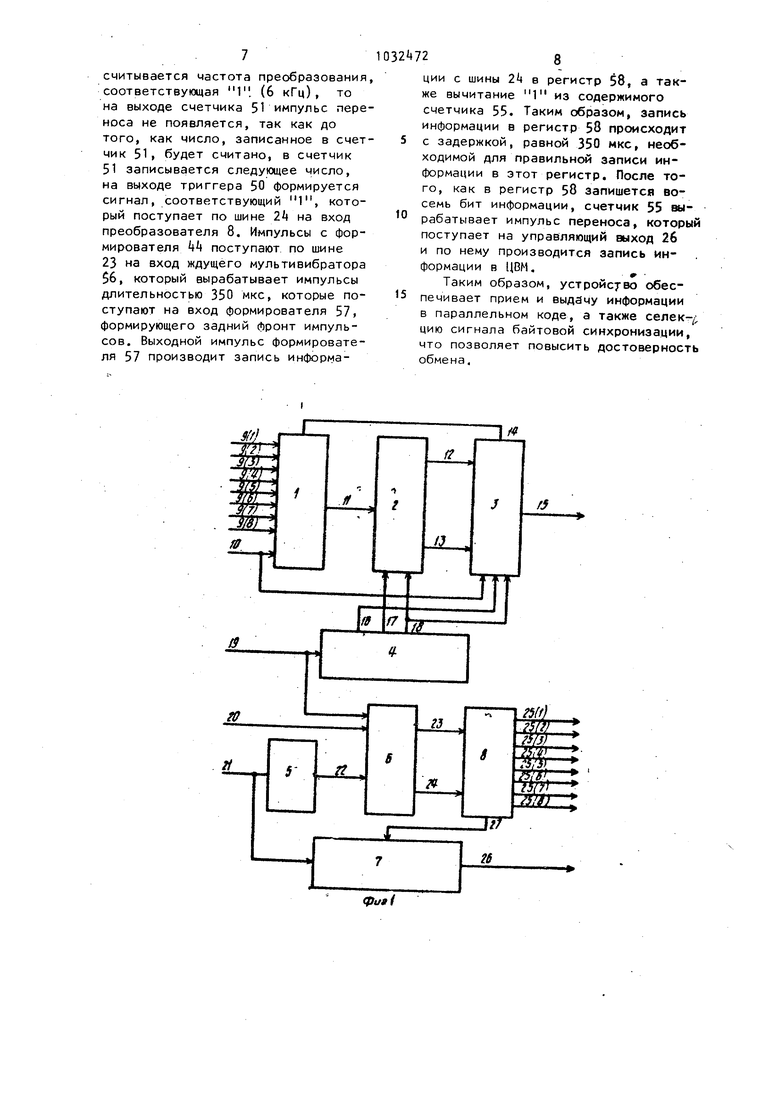

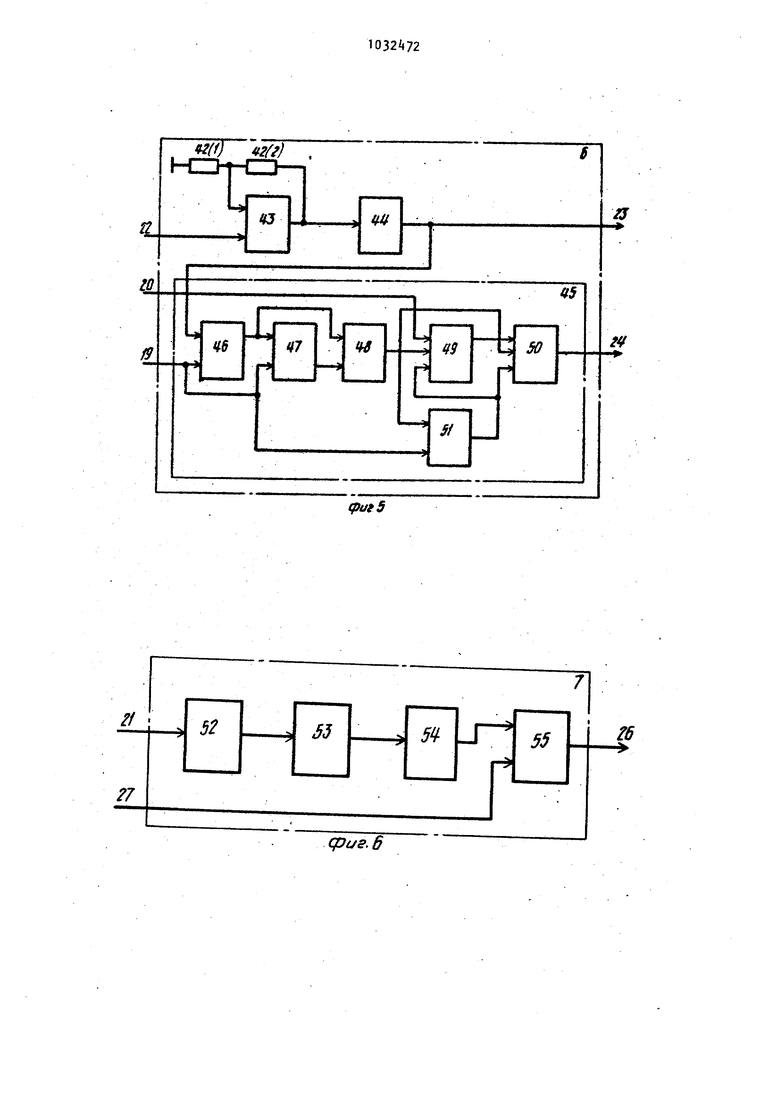

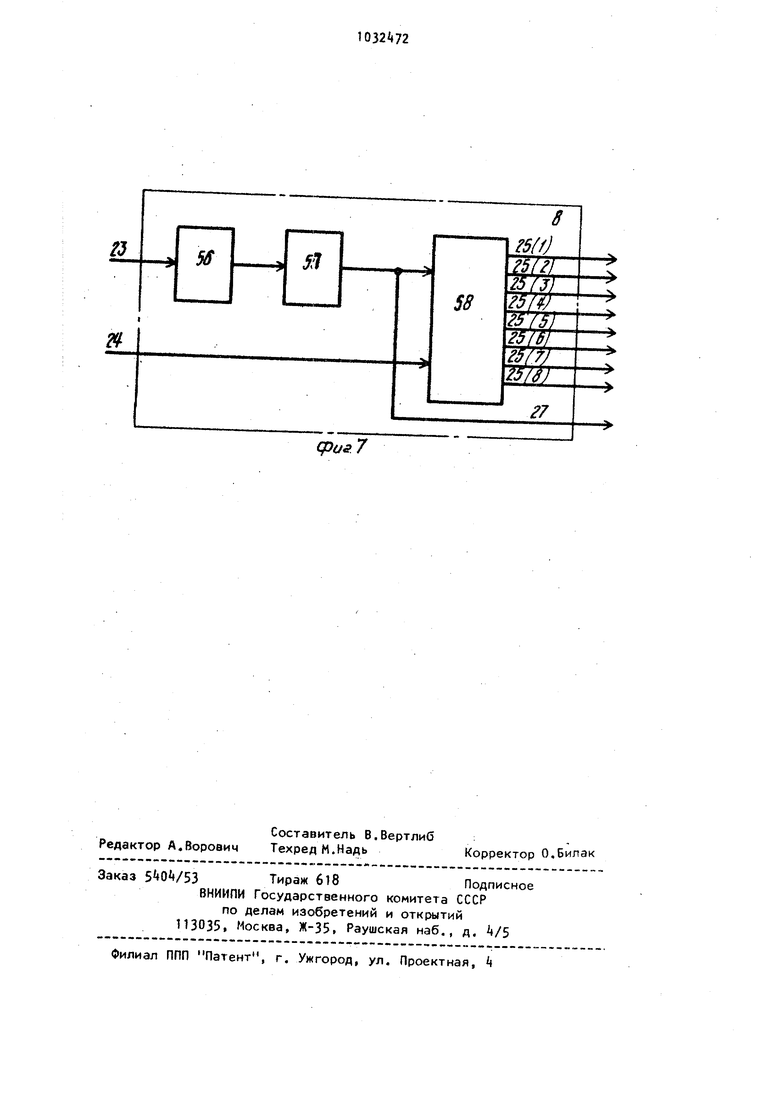

Поставленная цель достигается тем что в устройство, содержащее .блок синхронизации, канал ввода, блок модуляции, выход которого является аналоговым информационным выходом устройства, фильтр низких частот, канал вывода, включающий компаратор, делитель напряжения, формирователь импулса и цифровой анализатор частот, причем первый и второй выходы блока синхронизации соединены соответственно с первым и вторым входами каналаввода , а выход - с входом опорной частоты устройства и первым входом цифрового анализатора частот, второй вход которого соединен с шиной питающего напряжения, а третий вход через формирователь импульса - с выходом компаратора, первый вход которого соединен через фильтр низких частот с аналоговым информационным входом устройства, второй вход и выход компаратора соединены соответственно с выходом и входом делителя напряжения, введены преобразователь параллельного кода в последовательны преобразователь последовательного кода в параллельный и селектор импульса , причем информационный вход пре образователя параллельного кода в последовательный соединен с цифровым информационным входом устройства, первый и второй управляющие входы соответственно с первыми выходом и входом блока модуляции, а выход - с третьим входом канала ввода, первый и второй входы которого подключены соответственно к второму и третьему .входам блока модуляции, соединенного соответственно четвертым, пятым и первым входами с первым и третьим выходами блока синхронизации и управляющим входом устройства, первый вход и выход селектЪра импульса подключены cooTBeTcteeHHO к аналоговому инфор.мационному входу устройства и управляющему устройства, а второй вход - к первому .выходу преобразователя последовательного кода в параллельный, первый.и второй- входы которого соединены соответ.ственно с третьим входом и .выходом цифрового анализатора частот , а второй .выход - с, цифровым информационным выходом устройства. Кроме того, блок модуляции содержит триггер, три элемента И, элемен ИЛИ и формирователь аналогового сигнала,-, причем первый и второй входы триггера подключены соответственно к первому и второму выходам блока, а первый и второй вых,оды - соответственно к первым входам первого и второго элементов И, вторые входы ко торых соединены соответственно с пятым и четвертым входами блока, а выходы - соответственно с первым входом элемента ИЛИ и первым выходом блока, первый и второй входы третьего элемента И соединены с-оответст- . венно с третьим входом блока и вторы выходом триггера, а выход.- с вторым входом элемента ИЛИ, подключенного выходом через формирователь аналогового сигнала к выходу блока. На фиг. 1 представлена блок- схема устройства на фиг. 2-7 - функционал ные схемы канала вывода, блока модуляции, блока синхронизации, канала ввода, селектора импульса и преобразователя последовательного кода в параллельный. Устройство содержит (фиг. 1). преобразователь 1 параллельного кода в последовательный, канал 2 вывода. блок 3 управления, блок k синхронизации, фильтр 5 низких частот, канал 6 ввода, селектор 7 импульса, преобразователь 8 последовательного кода в .параллельный, цифровой информа- . ционный 9 и управляющий .ТО входы устройства, шины 11-Т межблочных связей устройства, аналоговый информационный выход 15, шины 16-18 третьего, второго и пятого выходов блока k синхронизации, вход .19 опорной частоты, вход 20 питающего напряжения, ана.логовый информационный вход 21 , шины межблочных связей устройства, цифровой информационный выход 25 устройства, управляющий выход 26 устройства и шину 27 первого выхода преобразователя 8. Канал 2 вывода (фиг. 2) состоит из элемента НЕ 28,.-триггера 2Э, элементов И 30 и 31 и элемента ИЛИ 32. Блок 3 модуляции содержит (фиг.З) триггер 33| первый и второй элементы И З и 35, элемент ИЛИ Зб, третий элемент И 37 и формирователь 38 аналогового сигнала, преобразу- ющий прямоугольные импульсы в синусоидалы ые. Блок 4 синхронизации содержит (фиг. 4) делитель 39 опорной частоты на четыре и делители 40 и опорной частоты на два. Канал 6 ввода содержит (фиг. S) резисторы 42 ( 1 и А2 ( 2 делителя напряжения, компаратор 3, формирователь 4, цифровой анализатор 5 частот, включающий триггеры 46 и k7, элемент И 48, триггеры 49 и 50 и счетчик 51. Селектор 7 импульса предназначен для выделения сигнала Начало байта и содержит фильтр 52 верхних частот, диодный детектор 53 Формирователь 5 импульса и счетчик 55. Преобразователь 8 последователь- ного кода в параллельный содержит (фиг. 7) элемент задержки (ждущий мультивибратор) 5б, формирователь 57, импульса и регистр 58 сдвига. Устройство работает следующим образом. В режиме вывода информация с ЦВН параллельным кодом поступает на входы преобразователя 1. При наличии сигнала на управляющем входе 10 она записывается в регистр этого преобразователя, в блоке 3 триггера 33 переходит в состояние 1 при наличии сигнала на управляющем входе 10 и при поступлении синхронизирующего сигнала на другой вход триггера. Частота синхронизируюв1его сигнала выбрана равной частоте сигнала преобразования, соответствующего логическому О, которая равна 2,5 кГц и поступает через элемент .НЕ 28. Потенциал с инверсного выхода триггера 33 запирает элементы И 35 и 37, потенциал с прямого выхода разрешает прохождение через элемент И сигнала преобразования, соответствующего началу байта. Частота сигйала преобразований, соответству кхцего началу байта, выбрана равной 10. кГц, Таким образом, сигнал преоб разования j соотр.етствующий началу байта, поступает через элемент . ИЛИ 36 и формирователь 38 на аналоговый инйормационный выход 15 который подключен к входу магнитофона. Длительность этой посылки равна длительности периода синхронизируюи(его сигнала, так как с приходом . следующего синхронизирунощего сигнала на вход триггера 33 сигнала на управляющем входе 10 нет и потенциал с прямого выхода этого триггера закрывает элемент И З, а потенциап с инверсного выхода открывает элементы И 35 и 37. Информа ция, находящаяся в старшем разряде регистра преобразователя 1, переписывается в триггер 29 только при поступлении синхронизирующего сигнала на триггер 29 через элемент НЕ 28. В зависимости от состояния триггера 29 на выходе элемента ИЛИ 32 появляются импульсы с частотой 2,5 кГц, соответствующие частот преобразования логического О, или частотой 5 кГц, соответствующие частоте преобразования логической 1 Эти сигналы при открытом элементе И 37 через элемент ИЛИ 36 и формиро ватель 38 поступают на вход кассет™ ного магнитофона звукозаписи, Импул сы частотой 2,5 кГц поступают с бло ка на вход элемента И 35 и при на личии разрешающего потенциала на другом его входе попадают в преобразователь 15 где по каждому импуль су информация, на ходя|щаяся в регист этого преобразователя, сдвигается на один разряд впрадо. Таким образом на вход магнитофона гоступает сигнал преобразования, соответствующий началу байта, а затем поступают сигналы преобразования, соответствующие логическому О или логической 1 в- зависимости от информации, поступившей на вход. После того, как вся информация, находящаяся в регистре преобразователя. 1, поступает на вход магнитофона, происходит запись новой информации, поступившей с ЦВМ на цифровые информационные входы 9 и в преобразовател)з I при условии, что имеется сигнал науправляющем входе 10 устройства, Сигналы преобразования, соответствующие началу байта, логической 1 и логическому О формируются в блоке k путем деления опорной частоты делителем 39 на четыре, делителем 0 на два и делителем 1 на два. , В режиме ввода обрабатываемая информация с выхода магнитофона через вход 21 поступает на фильтр 5 и на вход селектора 7. Фильтр 5 не пропускает сигналы с частотой выше 6 кГц, Обрабатываемая информация в селекторе поступает на вход фильтра 52, не пропускающий сигналы с частотой ниже 6 кГц, Сигнал, соответствующий началу байта, имеет частоту 10 кГц и через фильтр 52 поступает на вход диодного детектора 53, где преобразуется в постоянное напряжение, которое запускает формирователь 5, выходной импульс которого записывает в счетчик-;55 число восемь в двоичном-коде. Таким образом, перед обработкой каждого байта информации в счетчике 55 находится число восемь в двоичном коде, С выхода филБтра 5 информация поступает на компаратор 43, с выхода которого последовательность импульсов с частотой 2,5 или 5 кГц поступает на вход формирователя k, который формирует импульсы с крутыми фронтами. Эти импульсы поступают по шине 23 на вход преобразователя 8 и на вход триггера 6, который служит для синхронизации обрабатываемой информации,, поступающей с магнитофона с опорной частотой цифровой вычислительной машина,, Триггеры k6, kj и элемент И 48 формируют импульсы запуска для счетчика 51 и триггеров 49 и 50,. По импульсу запуска, сформированному на выходе элемента И 8, производится запись числа двенадцать в счетчик 51, триггер 9 устанавливается в 1, триггер 50 устанавливается в О, Число, записанное s счетчик 51, ачинает считываться импульсами порной частоты. Если с кассетого магнитофона звукозаписи считыается частота преобразования, сответствующая О (2,5 кГц), то а выходе счетчика 51 появляется мпульс переноса/ который устанавивает триггер 50 в исходное поожение и на шине 2 формируется игнал, соответствующий О, коорый поступает на вход преобраователя 8. Если с магнитофона считывается частота преобразования соответствующая Г (6 кГц), то на выходе счетчика 51 импульс пере носа не появляется, так как до того, как число, записанное в счет чик 51, будет считано, в счетчик 51 записывается следующее число, на выходе триггера 50 формируется сигнал, соответствующий 1, который поступает по шине 2 на вход преобразователя 8. Импульсы с формирователя поступают по шине 23 на вход ждущего мультивибратора 56, который вырабатывает импульсы длительностью 350 мкс, которые поступают на вход формирователя 57, формирующего задний фронт импульсов. Выходной импульс формирователя 57 производит запись информа2с шины в регистр 58, а также вычитание 1 из содержимого счетчика 55. Таким образом, запись информации в регистр 58 происходит с задержкой, равной 350 мкс, необходимой для правильной записи информации в этот регистр. После того, как в регистр 58 запишется восемь бит информации, счетчик 55 вырабатывает импульс переноса, который поступает на управляющий выход 2б и по нему производится запись информации в ЦВМ. . Таким образом, устройство обеспечивает прием и выдачу информации в параллельном коде, а также селек- ; цию сигнала байтовой синхронизации, что позволяет повысить достоверность обмена.

29

f/

18

17

Сриг.1

физ.З

I

16

iS

39

30

/J

J2 J/

v

v/

«/

фигЛ

Cpu8.6

Г6

55

pus7

Авторы

Даты

1983-07-30—Публикация

1982-04-07—Подача