блок модуляции устройства введены второй триггер, четвертый элемент И и элемент И-HEj причем первые вхол. элемента И-НЕ и четвертого элемента И блока модуляции соединены с вторым выходом кана,па Бывода, вьколь; - со--ответственно с счетным входом зтпрог-триггера и вторым входом первого трит

но с первым выходом первого триг-йра VI выходом второго триггера.,

2, Устройство по п. 1, о т Г к чающееся тем,, что канал зы-вода содержит триггер, два элеьгента

про Г

i-a о л

пед : рез

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения цифровой вычислительной машины с кассетным магнитофоном звукозаписи | 1982 |

|

SU1032472A1 |

| Устройство для сопряжения цифровой вычислительной машины с кассетным магнитофоном звукозаписи | 1982 |

|

SU1075249A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1985 |

|

SU1291989A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1986 |

|

SU1416992A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1985 |

|

SU1280641A1 |

| Устройство для сопряжения цифровойВычиСлиТЕльНОй МАшиНы C КАССЕТНыММАгНиТОфОНОМ зВуКОзАпиСи | 1979 |

|

SU798787A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1980 |

|

SU903854A1 |

| Устройство для сопряжения ЭВМ с магнитофоном | 1987 |

|

SU1474660A1 |

| Устройство для связи цифровой вычислительной машины с магнитофоном | 1982 |

|

SU1065853A1 |

| Устройство для сопряжения цифровой вычислительной машины с магнитофоном | 1984 |

|

SU1188745A1 |

Р1зобретение относится к вычис.г.к тельной технике и может быть испо.пьзовано для сопряжения кассеч-кого магнитофона С- цифровой вычислительной машиной (ЦВМ)

Известно устройство для сопряжения ЦВМ с магнитофоном, содержащее канал вывода,, состоящий из формирователя синусоидального импульса фаэскодированного модулятораj триггера и элемента НЕ, блок синхронизации я канал ввода, состоящий из полосового фильтра, делителя напряжения, компаратора и цифрового анализатора -астот Cl ,

Недостаток этого устройства состоит в низкой -достоверности обмена информацией .

Наиболее близким к изобретению является устройство для сопряжения ЦВМ с кассетным магнитофоном звуксааписи, содержащее блок синхронизацЗШ; канал вывода, преобразователь пар 1Ллельного кода в последовательный, преобразователь последовательного кода в параллельный, селектор импульса блок модуляции, выход которого является аналоговым информаи,ионным вькодом устройства, фильтр низкик частот и канал ввода, включающий компаратор делитель напряжения, формирователь импульса и цифровой анализатор часто причем первый и второй выходы блока синхронизации соединены соответственно с первьтм и вторым входами канала вывода, а вход - с входом опорной

частоты угтройсгил ,i iie:)i)::iM (ч u ia ;ioHo iL) а нализ аго;,);; ча(..:;;,.. ;;г;ч:1 ;

вход KUiyporo :Ое/ ННен ( ii:-- таюцегч) напряжения а реч-ии KX V;4ept:3 формирователь импзльса пых - дом компаратора I первый ,;: с.оедияен через юильтр /пизклх - ; ТО; с аналоговым И:;формац 1и.иыл «.: дом устройстза,, Всорок вхоп л комг:аратора соединены coejjBe г; , с выходом и входом делител;- игифял;;. ниЯд а информацг-ючаый тгход (;Гп) на-ешя параллельного o;ia з at;c.:i€:../ эаГ ;лы1ь;Я t; Д 1фаовым HKUJOpMaLU-iohi.::: входом устрсйсГва первый : 1Л :;n)0i-- ; ра1зляюш 1е сооТЕетс j-ieHrio первыми зык од ом к ыходим б.г;ока :-:;д :;;-; ции, а выход - с третьи -) зхидс 1 канапа вьтодв; первый и второй :;ых;;;;,: которого полключень соотBerrCTiitiiiHi; к второму и третьему вхсл,ам ojiOKa мод ляциИр соединенного четвертым, пятым и лерЕЫм входами ;: ггервыь; к третьим выходами блока синхронизации и упргвляюш,им входом устройства,, пер ВЬ1Й вход и выход селектора импульса подключен соответственно к аналоговому информационному входу устройства к управляющему выходу устройства, а второй вход - к nepaoi-ry выходу преобразователя -последовательного кода в параллельный, первый и второй входь которого соединены соответственно с первым и вторым выходами цифрового анализатора частот, а второй выход - с цифровым инфopмaциoннь: выхо дом ycTpoiiCTBa, причем блок модуляци содержит триггер, три .элемента И, элемент ИЛИ и формирователь аналогового сигнала, причем лервый и второй входы триггера подключены соответственно к лервому и второму выходам блока, а лервьт и второй выходы - со ответственно к лервым входам лервого и второго элементов И, вторые входы которых соединены соответственно с пятым и четвертым входами блока, а выходы - соответственно с первым вхо аом элемента ИЛИ и лервым выходом блока, лервый и второй входы третьего элемента И - соответственно с третьим входом блока и вторым входом триггера, а пыхо/ - с вторым входом элемента ИЛИ. по.дключенног.о выходом через формироватс.гь аналогового сигнала к вькоду блока 21. Недостатком известного устройства является низкая достоверность обмена информацией, так как имеется возможность появления на выходе селектора имлульса ложного сигнала Начало байта, обусловленного высокочастотными шумами магнитнорЧ и короткой длительностью сигнала Начало байта. Целью изобретения является повыше ние достоверности обмена информацией Поставленная цель достигается тем, что в устройство, содержащее блок синхронизации, канал вывода, первый и второй входы которого соеди нены соответственно с первым и вторым выходами блока синхронизации, преобразователь параллельного кода в лоследователы ый, и формационный вход которого является цифровым информационным входом устройства, а выход соединен с третьим входом канала вывода, блок модуляции, рключаюпщй пер вый триггер, три элемен1а И, элемент ИЛИ и формирователь синусоидальных импульсов, выход которого является аналоговым информационным выходом устройства, а вход соединен с выходом элемента ИЛИ блока модуляции, ка нал ввода, состоящий из компаратора формирователя импульса, делителя нап ряжения и цифрового анализатора частот, фильтр низких частот, селектор импульса и преобразователь последов тельного кода в параллельный, причем первый вход селектора импульса соединен с аналоговым информационным входом устройства и через фильтр ни ких частот с первым входом компарат 114 ра, выход, является управляющим выходом устройства, а второй вход подключен к первому выходу преобразователя последовательного кода в параллельHhrfi, второй выход которого является цифровым информационным выходом устройства, а первый и второй входы соответственно соединены с выходом формирователя импульса и выходом цифрового анализатора частот, первый вход которого подключен к входу опорной частоты устройства и входу блока синхронизации, второй вход - к входу питающего напряжения устройства, а третий вход - через формирователь импульса к выходу компаратора и входу д,е. напряжеггия, выходом соединен}юго с вторым заходом компаратора, в блоке мол,уля1Ц1И пг.рвые и выход первого триггера подключеи.ы соответственно к управляющему входу устройства и первому входу первого элемента И, а второй выход - к первым входам второго и третье-о элементов И, выходы первого и третьего элементов И соединены соответственно с первым и вторым входами элемента иГЙ, вторые входы - соответственно с третьим выходом блока синхронизагли и первым выходом канала вывода, второй вход и второго элемента И блока модуляции подключены соответственно к первому выходу блока синхронизации и первому управляющему входу преобразователя параллельного кода в последэвателььый, второй управляющий вход которого соединен с управляющим входом устройства, в блок модуляции введе1Ы второй триггер, четвертый элемент И и элемент li-HE, причем первые входы элемента И-НЕ и четвертого элемента И блока модуляции сосдииешп с BTopoiM выходом канала вывода, вьлходы - соотвстстзенно со счетным входом второго триггера и вторым входом первого триггера, а вторые входы соответственно с первым выходом первого триггера и выходом второго триггера. При этом канал вывода содержит триггер, два элемента И, элемент ИЛИ и элемент НЕ, причем информационный вход триггера является третьим входом канала, прямой и инверсный выходы соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к первому и второму входам канала, а выходы - соответственно к первому и ачпрому элемента ИЛИ, ВЕ.КОД которси., ся первым выхолим канала, riirxpoi; зируюнуш Х()д тригтера riu .чпнги, : вторым выходом канала и чепе: :-:км-, НЕ с riepBbfbi входом кан,-1 in,

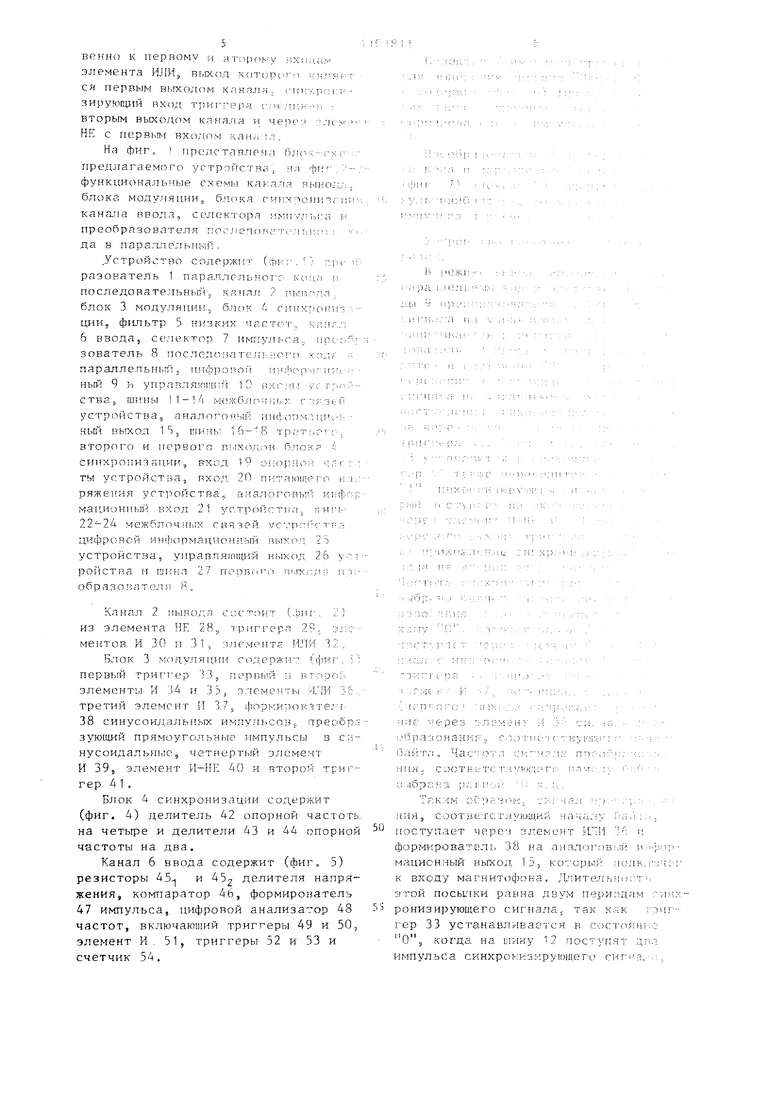

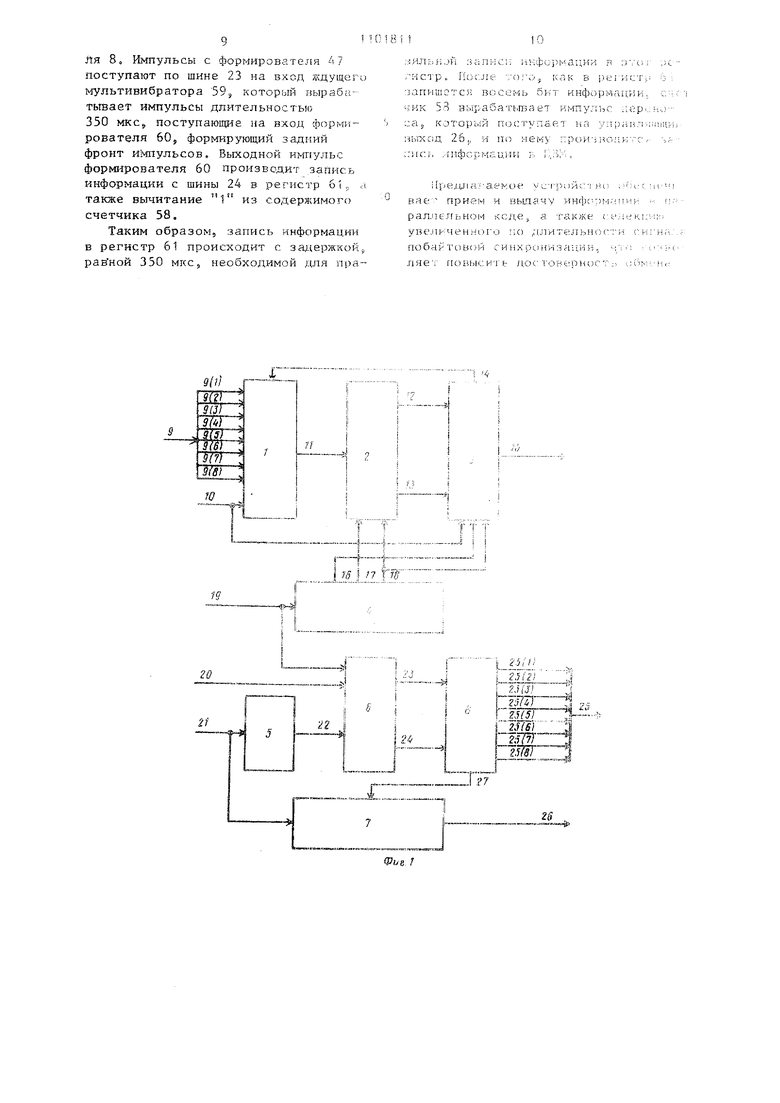

На фиг. i тии дстлплема блоч--;-х (-: предлагаемого устрэйства. на фг;-./-.фуЕ1Кционалы- ые схемы каг:а7гл Fii iBOur,, блока модуляции, блока cHfixnonHT;: ии. канала ввода, селектора я -л- -ъсз iпреобразователя послелоп; ч/л fjn-i ; да в параллельнь:й-:

.Устройство содержит (. гч- раэователь 1 параллсльзюгт ко;и п последовательны;, кянял пьпог,

блок 3 модуляции, блок 4 СИ(Х)СМиЗ ции. фяпьтр 5 низких частот,, кан;-.-; 6 ввода, селектор 7 импульса,. (OL-;, зователь 8 посдодо; ате. кпл;

ПараЛЛе.ПЬНЫЙ 5 HHUpOT Off

ный 9 ь уг равля1-г11-пп1 10 ,ы уггг::- CTEBj шнны 11-14 межблоч ; ; : cri.-ritil устройства, аналоговык (I:ODM;U;-OI- ный вьход IS, 11И; ь: трет:, второго и ггервого пмхо.п.ов б.лоь-я -. сипхрошзадии, вход 19 опорном чп(: : ты устройства, вход. 20 пи-акпцегч и;, ряжения устройства аналоговь:и мационны11 вход 21 устройсти;, пип22-24 межблоч:Л11х связей ус-:рслт т-т,-: цифровой ин{}к1рмацион ый iif,ivoj; 2т устройстза, управ.пя П|ций вых()д 26 ройства и шина 27 пеового ;р,гхо.пп пт: образопателтп 8.

Канал 2 выво;;я (,biir, 2; из элемента НЕ 28„ триггера .. эл:: ментов И 30 и 31, :;лемеитй ИЛи 32,

Блок 3 модуляди - (фиг, ; перВР)ГЙ триггер 33 j первьй и Fropo;i элементы И н 35 племепты И-ЧИ 3с, третий элемент П 37. фор1чипо1-;гте:г38 синусоидальпых имдулвсов,, преобр.;; зующий прямстугольные импульсы в с;;нусоидальн1,е 5 четвертый элемент И 39, элемент И-НЕ 40 и второй триггер 4 1 ,

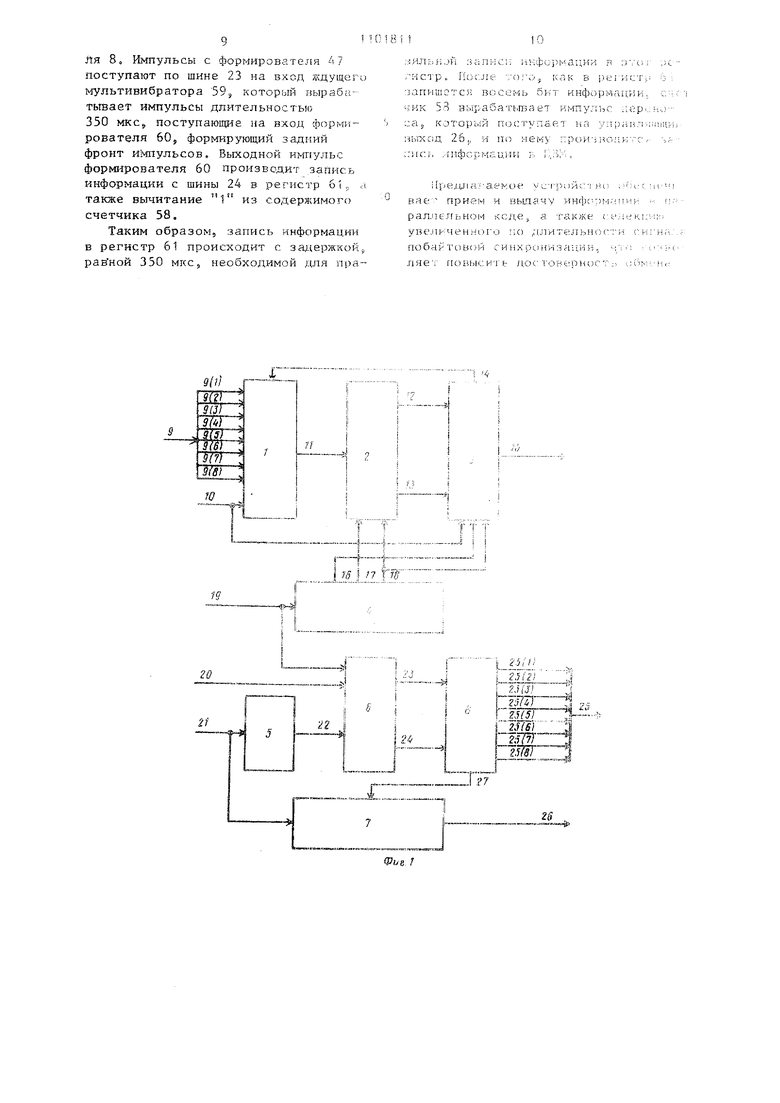

Блок 4 синхронизации содержит (фиг. 4) делитель 42 опорной частоть. на четыре и делители 43 и 44 опорной частоты на два.

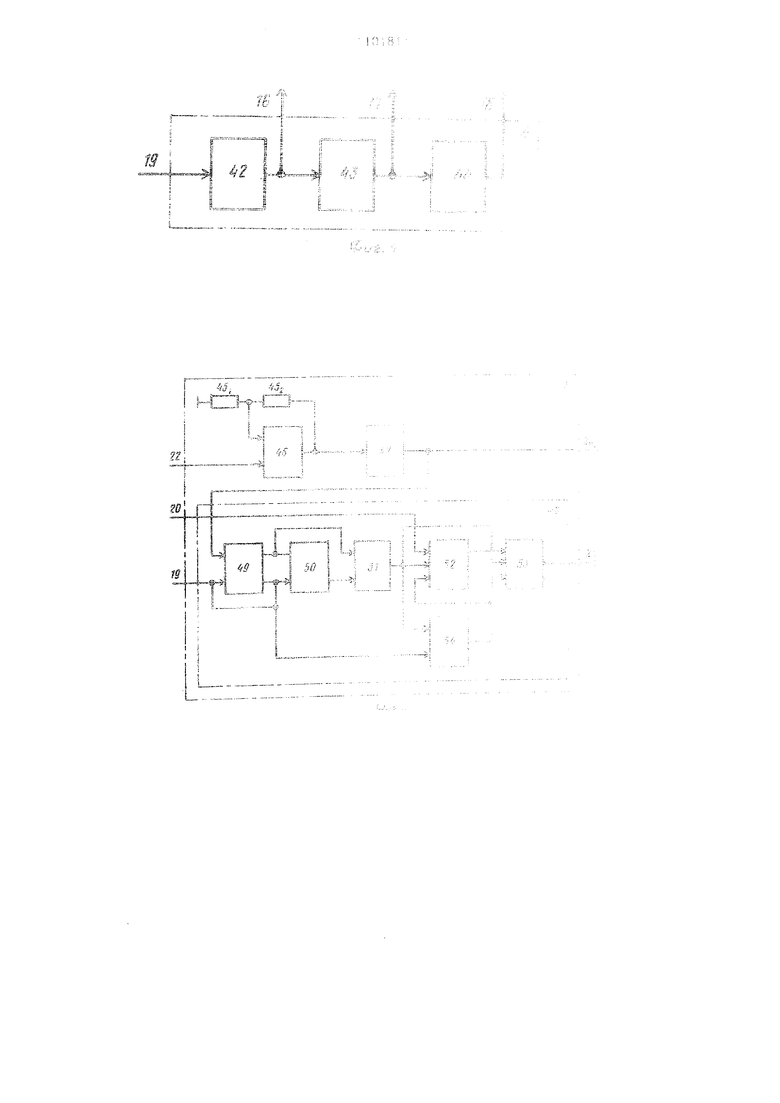

Канал 6 ввода содержит (фиг, 5) резисторы 45 и 452 делителя напряжения, компаратор 46, формирователь 47 импульса, цифровой анализатор 48 частот, вклнзчающий триггер1э1 49 и 50. элемент И . 51, триггеры 52 и 53 и счетчик 54,

.хгт

;к:лм ОС;),, j; ; иия, соотнетст ующий нпча.г

поступает мере: элемент -П

3 и формирователь 38 на аналог

ОВ|ЛЙ мационный выход 15. ко-орьп ис-дк 1 ;ч к входу магнитоф{П1а. дрпеэтой посылки равна двум пе

риодам си

р о ни 3 и г о с и г нала, та к к,як гои гер 33 устанавлггвается в с ОС той Hi-; о когда на 12 пост у пят дп,1 импульса синхро ;изирующег(, сиг1-а. ; 7. 1 при этом триггер -ч ус танп rijisiiiaoTCH опять в согт(5я:;ие О, и пртени.иа.ч с его ииперсного ныхола разрешает прохождение г.нпхроничирутщего сипчала через элемент И 39 на BTOJIOH вход трип-ера 33. Так как сигнала на управляющем входе 10 не будет, подача его прекращается после установки триппера 33 в состояние 1, то триг гер 33 устанавливается в состояние О и потенциалом с прямсичт выхода тапрегдаот прохождение импчлт.сон чере элемент I-HK 4П и эчехрнт И 34, а потенциал с инверсногч sijxcva сткры:-ае: э.пемент И и -.пемеит i 37. Ин формация, Haxojuii;; я с я is CTapiiiCM разряде perncTjia rnfriCiiailMiai еля 1, пе 1ен1К ;раетгл ,-. Tpiirr j 2: .(лт.ко при lioci ( HiiXfi ,;pvK.i:ici4 сигнала ча г ти1Мор -М Ч-гчЗ ;i ПК 28. В зачигимос П от (ччмччния тригге 5 , соотвстстну|0 :1ие частоте прсобразонани5; чогическ:Ч| . Эти сиг нл. ич О элемсп i4- и 3 / чс- рё элемеи Г lUlH 36 и формирователь 38 постучиот на пход магчп тофона, Имг1у/1,сь.1 часпч-.той 2,5 кГц поступают с блока 4 г:а Rxo:i элемента И 35 и п ячглкчии разре; :аю;:1его потеьии1ала на информация, нахг1Г;я;паяся Г регистре этого преобразователя, сдв1;гается на один разряд вправо. -Таким чбразом, на ВХОД; маг ;ИТ01Т}О1;а поступает сигнал преобразования,, соответствующий нача лу байта, а затем - сигналы преобразования, соответст уюцие логическому О или логической 1 в зависимости от информации, поступившей на вход 9. После того, как вся } нформаиия, находящаяся в регистре преобразоватедя 1, поступит на вход магнитофона, происходит запись новой информации, поступивикч: с ЦВМ на цифровые информационные пхолы 9 и в преобразо ватель 1 при услгч И, что будет сигнал на упрар,ляю;п,ем входе 10 устройст ва. Сигнал. преобразования, соответствую 11ие -тачалу байта, логической на , х елитетоты делито.тг-м лем 0 на дв;;, делителем 41 на два, Б 11ежимс: ввода обрабат 1 р аемая информация с магнитофона через вх(1д 21 постчтаЕ т-на фильтр 5 и на вхо.д селектс ра 7, Фильтр 5 не пропускает сиг:аль с частотой вьпие 6 кГц, Обрабатываемая информация поступает на вход фильтра 55, не пропускающий сигналы с частотой ниже 6 кГц. Сигнал, соответствующий началу байта, имеет кГц и через фильтр 55 частоту поступает на вход диодного детектора 5, ггч преобразуется в постоян |1-е ч;::рчже};ио, лоторое запхскает ф р И1Ч1Ват- Ч ) т, ИМП :1ЬС которого зачис т в счет;ик 58 число вчсе--, } ;1во;чпч-м коле так. что :ч-реч ii6pa;4VT-v(ifi каж;ипч oaf-Ta В СЧ1ГЧИКе 58 аХ;Ч.ИТСЯ ЧИСЧ ДНОЧЧ ОМ Чт;;С . с ..-ч:; 1:)и.л-тра 3 инфор-кшия ia чар а14.4) J., с н 1гходч к (1 т 04014 ч CJ ч/ ч v4 а те: i Р-. н с с т ь ii п у л i, с о с ча -тчтой 2, чГч 5 поступает па ixo4 т(ч;ч . которкй :И . ЗУЧ И ПУЧ}ГЬ 1ОСТу :а-|Т ЧО 23 пч чреобрлзо1 атечя 8 и ч: :-ч(ч; --Q. когор1,;й сложит цля С1: ч-чччч13.. обраблт чваемой ии.,4li, ОСТучаСПОЧ с .аГН1ГГОфо;1а с пульсу сформированному на B -Txc4ie эчсмента 1 51, производится зап1Ч . 4:ic.ia д ч малдатъ в счетчик а :ч; Чер 53 - в О. , записанное в счетчик :. начинает считываться им ; ьсчэми опорной частоты. Если с ;aгнитoфoнa считыгчяется частота преобрлзова}Г)я. соотвс ств ю;иая О (2,5 кГц), ь BMXLVie счетчика 54 появляется импул,с переноса, который уста; авливг-ет триппер 53 в исходдюе положение, а ;ia тине 24 формируется сигнал, соответствую :ц:й О, кОТорый поступает на вход преобразователя 8. Если с магнитофона считывается частота преобразования, соответствующая логичческой 1 (5 кГц), на выходе счетчика 54 1мпульс переноса не появляется, так как до того, как число будет считано, в счетчшк 54 записывается следукщее число, на выходе триггера 53 формируется сигнал, соответствующий I, KOTopbifi поступает по иине 24 на вход гчтеобразоватеЛя 8, ИмпульсьЕ с формирователя 4/ поступают по шине 23 на вход ждущего мультивибратора 59 который вырабмтывает импульсы длительностью 350 MKCj поступающие на вход формг,рователя 60, формирующий фронт импульсов. Выходной импульс формирователя 60 производит запись информации с шины 24 в регистр 6i,, а также вычитание 1 из содержимого счетчика 58. Таким образом, запись информации в регистр 61 происходит с задержкой« равной 350 МКС 5 необходимой для iiiyanJHJIiiiHJH ; ;:П|-;С;: гнстр. iUi;ле ;, :iani-iii:eTCJ; восем1з ot чик 53 вьц;-а5ать.гог5ет ::а, который П.)(;тулает на иьжод 26,, и по иему ::рои :;ис:г, . лфсрмги ЛР; ; i ipejjJiH a.eKOt VCTP;)H;:I lui вае прием и выдачу инфо-гмрал.1«;г(ьном кеде, а также ct увеличенного :;с) длителbHiii : rio6a{-TOB iM синхронизации 5 ЛЯеТ riOBhiCHlt ДОС TOBt-ptUJCT :

fS I n fW

29

16

28

-9

П

JO

13

32

31

(Pus. 2

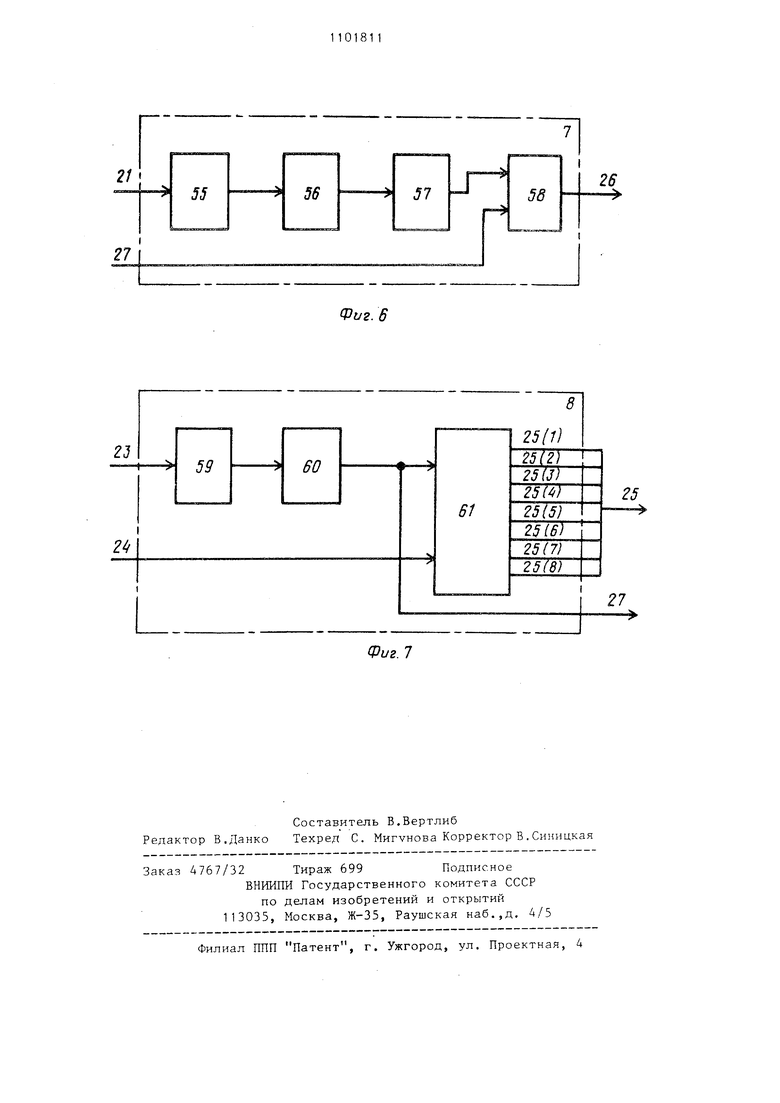

Фиг. 6

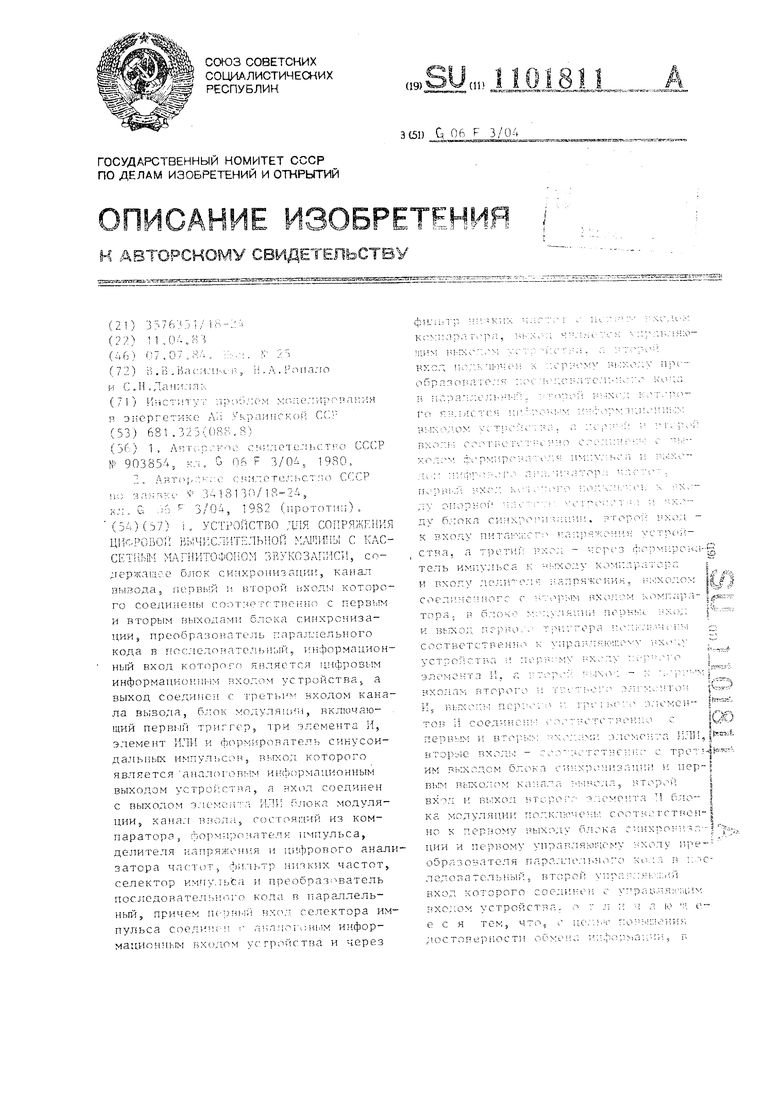

Фиг. 7

Авторы

Даты

1984-07-07—Публикация

1983-04-11—Подача