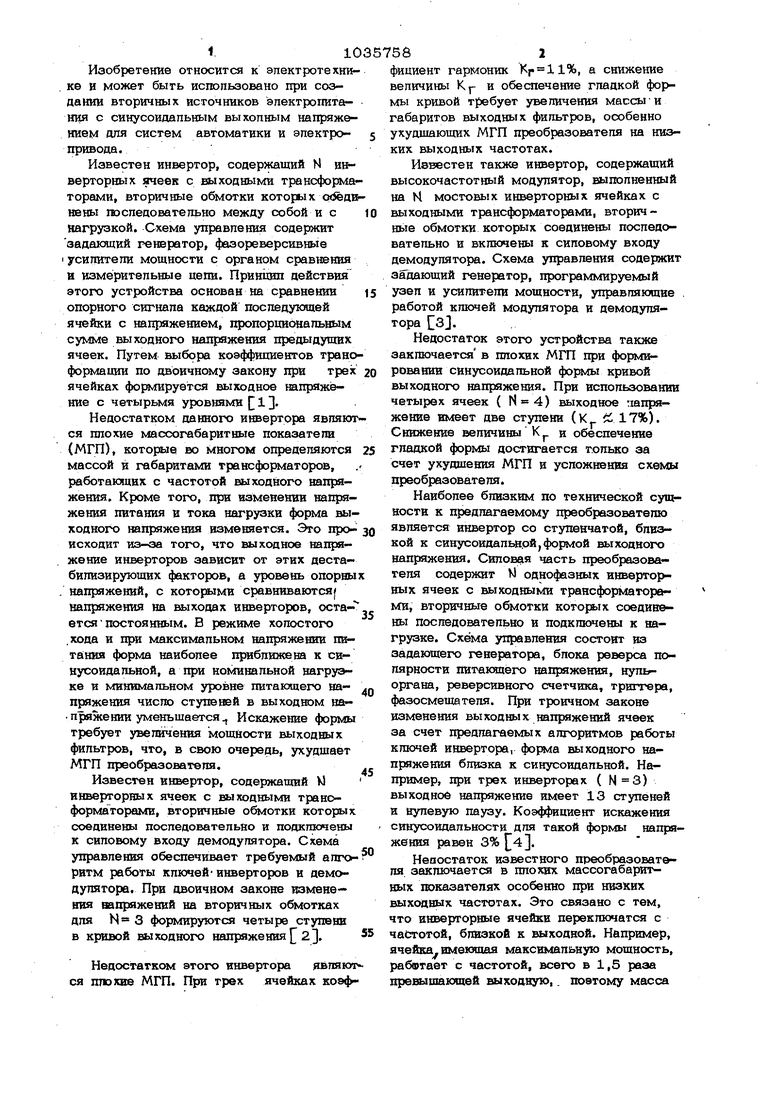

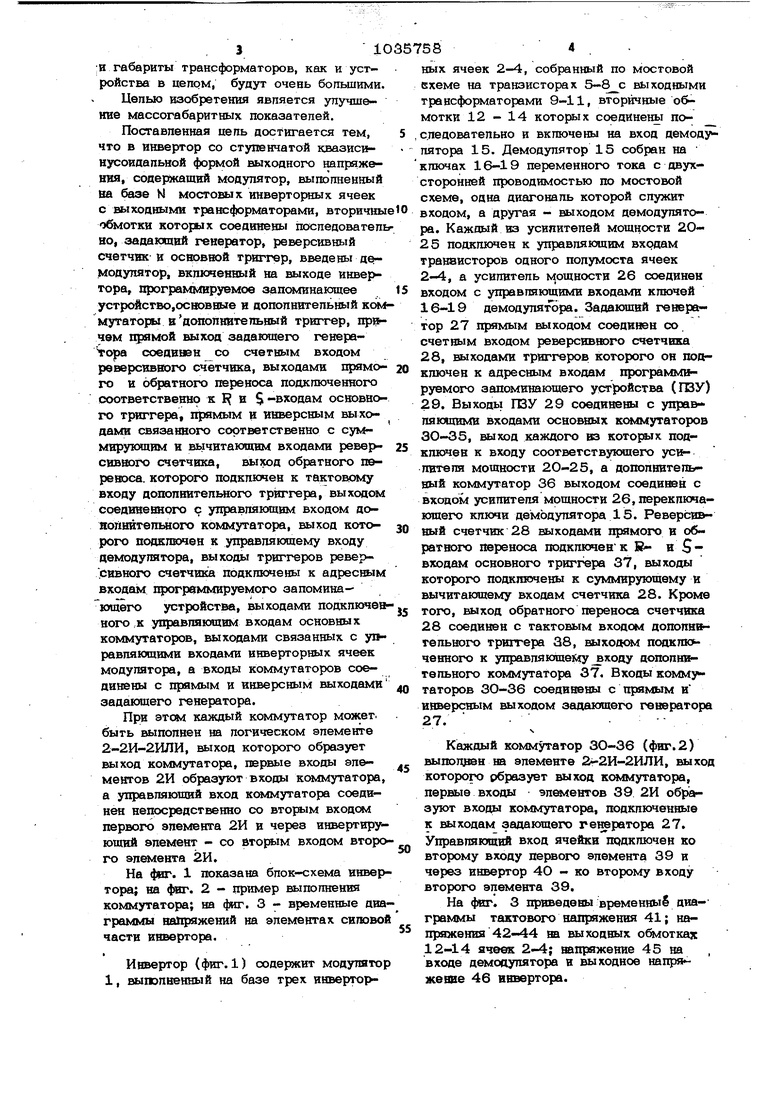

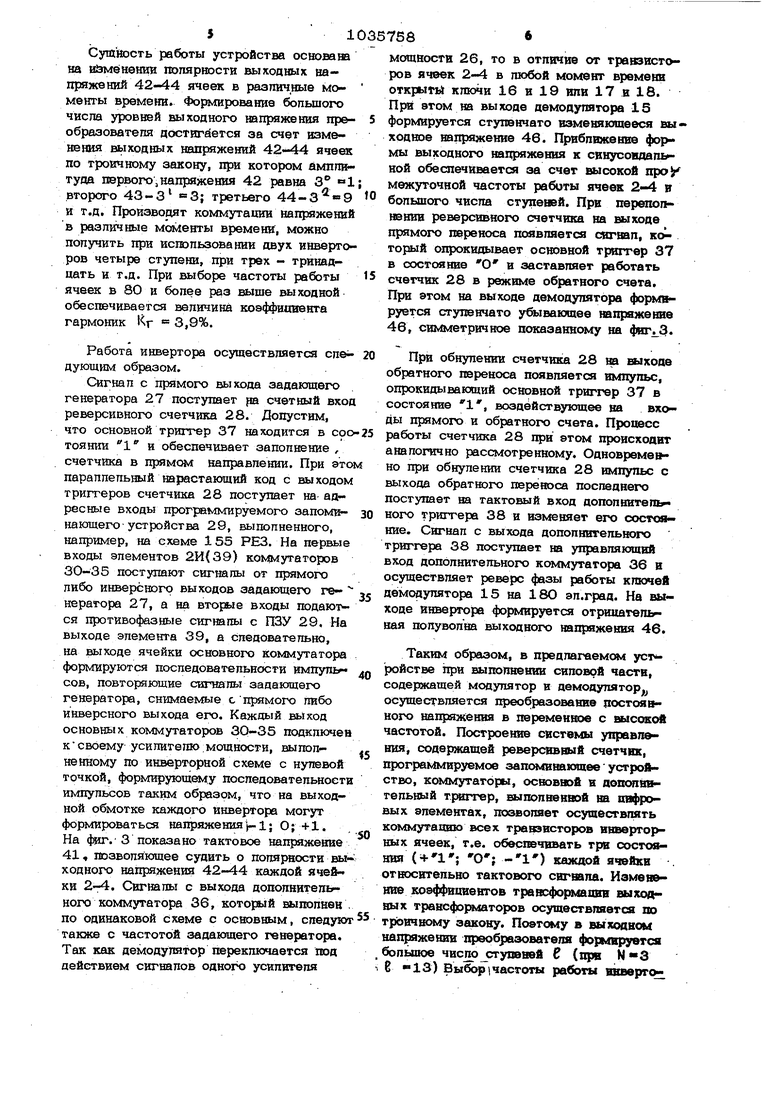

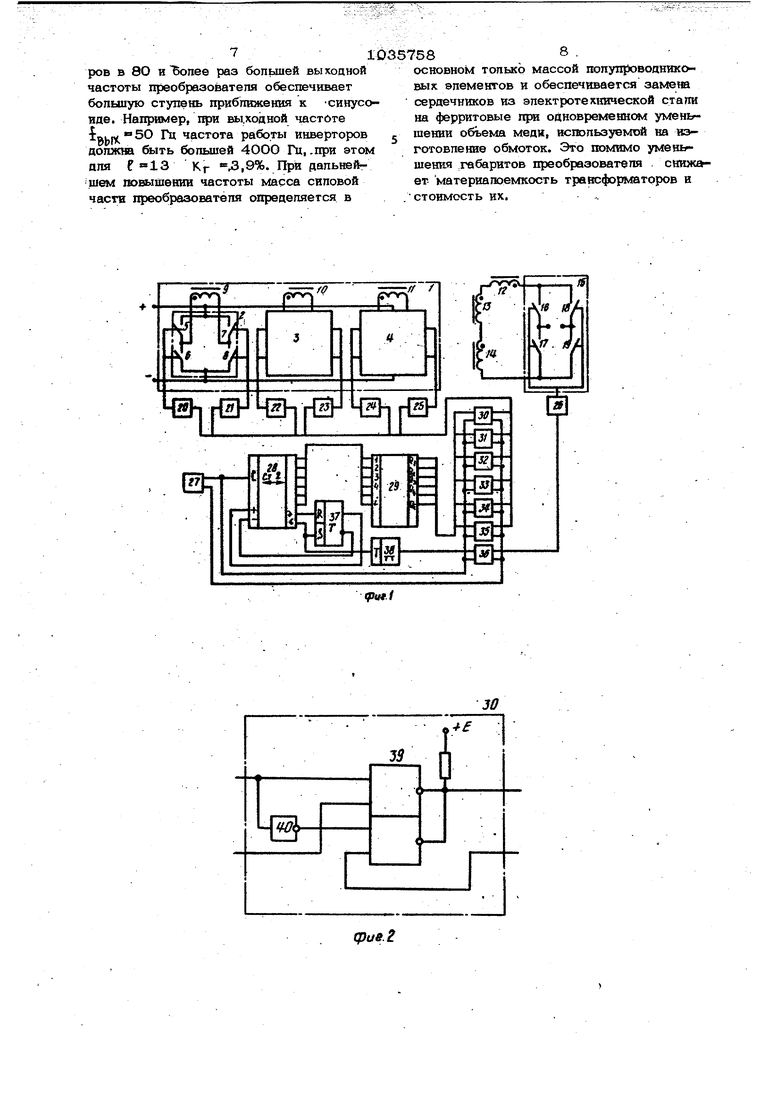

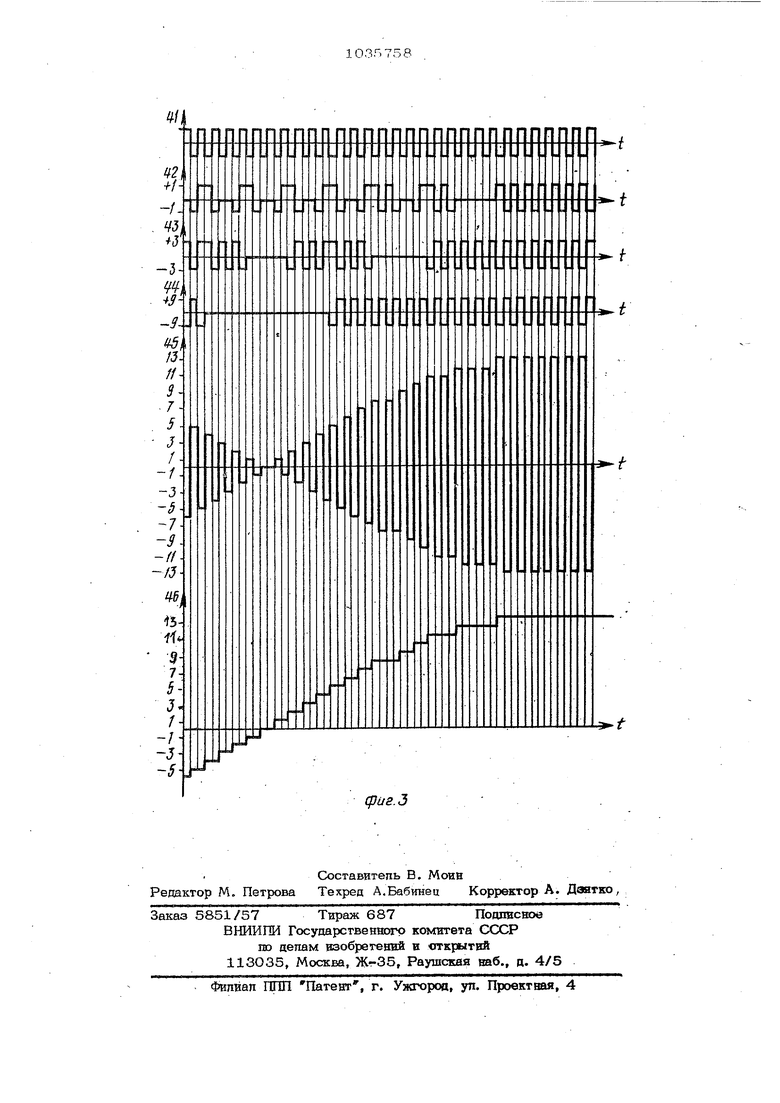

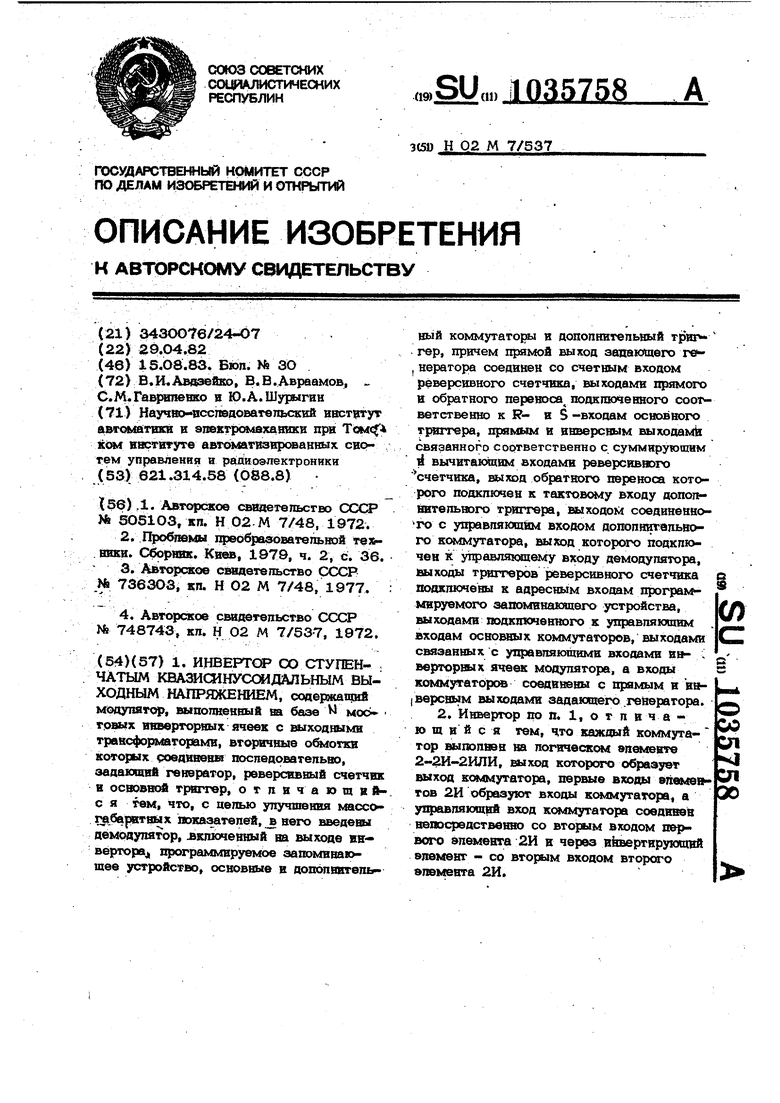

Изобретение отнсхзится к электротехнике и может быть использовано при создании вторичных источников электропитания с синусоидальным выхопным напряжением для систем автоматики и эпектропривода. Известен инвертор, содержащий М инверторных ячеек с выходными трансформа торами, вторичные обмотки которых рдёдк нены последовательно между собой и с нагрузкой. Схема управления содержит задающий геивратор, фазореверсивные I уситггели мощности с органом сравнения И измерительные цепи. Принцип действия этого устройства основан на сравнении опорного сигнала каждой последующей ячейки с напряжением, пропорциональным сумме выходного напряжения предыдущих ячеек. Путем выбора коэффициентов трано формашга по двоичному закону при трех ячейках фо{жшруется вызюдное напряжение с четырьмя уровнями | 13Недостатком данного инвертора являют ся плохие массогабаритные показатели (МГП), которые во многом определяются массой и габаритами трансформаторов, работаю цих с частотой выходного напряжения. Кроме того, при изменении напряжения питания и тока нагрузки форма выходного напряжения изменяется. Это происходит из-за того, что выходное нащм- жение инверторов зависит от этих дестабилизирующих факторов, а уровень опорны . напряжений, с которыми сравниваются напряжения на выходах инверторов, остается-постоянным. В режиме холостого .хода и при максимальном напряжении пита:ния форма наиболее 11риблихюна к синусоидальной, а при номинальной нагрузке и минимальном уровне питающего напряжения число ступеней в выходном на- пряжении уменьщается Искажение формы требует увеличения мощности выходных фильтров, что, в свою очередь, ухудшает МГП преобразователя. Известен инвертор, содержащий W инверторных ячеек с выходными трансформаторами, вторичные обмотки которых соединены поспедовательво и подктпочены к силовому входу демодулятора. Схема управления обеспечивает требуемый алго ритм работы ключей- инверторов и демодулятора. При двоичном законе изменения вапряжений на вторичных обмотках для формируются четыре ступени в кривой выходного напряжения 23. Недостатком этого инвертора ябляют ся шюхие МГП. При трех ячейках коэф фиииент гармоник Кр 11%, а снижение величины Кр и обеспечение гладкой форн мы кривой требует увеличения массы и габаритов выходных фильтров, особенно ухудшающих МГП преобразователя на низких выходных частотах. Иввестен также инвертор, содержащий высокочастотный модулятор, выполненный на N мостовых инверторных ячейках с выходными трансформаторами, вторичные обмотки которых соединены последовательно и включены к силовому входу демодулятора. Схема управления содержит задающий генератор, программируемый узел и усилители мощности, управляющие . работой ключей модулятора и демодулятора 3. Недостаток этого устройства также заключается в плохих МГП при формировании синусоидальной формы кривой выходного напряжения. При использовании четырех ячеек ( N 4) выходное напряжение имеет две ступени (К Л 7%). Снижение величины К . и обеспечение гладкой формы достигается только за счет ухудшения МГП и усложгония схемы преобразовате ля. Наиболее близким по технической сущности к предлагаемому преобразователю является инвертор со ступенчатой, близкой к синусоидапы1рй,фо1Яу{ой выходного напряжения. Силов(ая часть преобразователя содержит М однофазных инверто хных ячеек с выходными трансформаторами, вторичные обмотки которых соединены последовательно и подключены к нагрузке. Схема управления состоит из задающего генератора, блока реверса полярности питающего напряжения, нульоргана, реверсивного счетчика, триггера, фазосмещателя. При троичном законе изменения выходных напряжений ячеек за счет предлагаемых алгоритмов работы ключей инвертора, фо1ыа выходного напряжения близка к синусоидальной. Например, при трех инверторах ( N 3) выходное напряжение имеет 13 ступеней и нулевую паузу. Коэффициент искажения синусоидальности для такой формы напряжения равен 3% 4. Непостаток известного преобразователя закгаочается в плохих массогабаритных показателях особенно при низких выходных частотах. Это связано с тем, что инверторные ячейки переключатся с ча&готой, близкой к выходной. Например, ячейка имеющая максимальную мощность, работает с частотой, всего в 1,5 раза превышающей выходную,. поэтому масса :и габариты трансформаторов, как и устройства в цепом, будут очень бопъшкмк. Цепью изобретения явпяется улучшение массогабаритных показатепей. Посягавпенная цепь достигается тем, что в инвертор со ступенчатой квазис нусоипапьной формой выходного напряжения, содерисащкй модупятор, выпопненный ва базе Ы мостовых инверторных ячеек с выходными трансформаторами, вторичны обмотки которых соединены поспедоватеп но, задающий генератор, реверсивный счетчик и освювной триггер, введены демодупятор, вкпючеяный на исходе инвертора, програко«{ируемое запсжганающее устройство,основшле и допопнитепьный ком мутаторы Едополните пьный триггер, щяиой выход задающего генера тс а соеднвэн со счетным входом реверсивного счетчика, выходами прямого и обратного переноса подкпюченного соответственно к I и $ -входам основно го триггера, прямым и инверсным выходами связанного соответственно с суммвруюшим и вычитающим входами реве1 сиввого счетчика, выход обратного переноса, которого подкшочен к тактовому входу допопнитепьного триггера, выходом соеднневкого с управпяюшим входом дояоднитепьного коммутатора, выход которого подкшочен к управляющему входу демодупятора, выходы триггеров реверЪивного счетчика подключены к адресшлм входам программируемого за помина ютаего устройства, выходами подкпючеа ного к управляющим входам основных коммутаторов, выходами связанных с управляющими входами инверторных ячеек модулятора, а входы коммутаторов соединены с прямым и инверсным выходами задающего генератора. При этом каждый коммутатор может, быть ылполнен на логическом элементе 2-2И-2ИЛИ, выход которого образует выход коммутатора, первые входы эле- ментов 2И образуют входы коммутатора, а управляющий вход коммутатора соединен непосредственно со вторым входом первого элемента 2И и через инвертирующий влеменг - со вторым входом второ го элемента 2И. На фиг. 1 показана блок-схема инвер тора; на 4яяг. 2 - пример выполнения коммутатора; на фиг. 3 - временные диа граммы напряжений на элементах ситово части иювертора. Инвертор (фиг.) содержит модулято 1, выполненный на базе трех инверторных ячеек 2-4, собранный по мостовой вхеме на транзисторах выходными трансформаторами 9-11, вторичные обмотки 12-14 которых соединены последовательно и включены на вход демоду лятора 15. Демодулятор 15 собран на ключах 16-19 переменного тока с двухсторонней проводимостью по мостовой схеме, одна диагональ которой служит входом, а другая - выходом демодулятора. Каждый из уснпнтелей мощности 2О- 25 подключен к управляющим входам транзисторов одного полумоста ячеек 2-4, а усилитель мощности 26 соединен входом с управляющими входами ключей 16-19 демодулятора. Задающий генератор 27 прямым выходом соединен со счетным входом реверсивного счетчика 28,выходами триггеров которого он подгключей к адресным входам программируемого запоминающего устройства (ПЗУ) 29.Выходы геУ 29 соединены с управляющими входами основных (утаторов ЗО-35, выход каждого вз которых подключен к входу соответствующего ус лителя мощности 20-25, а дополните Л1уЕый коммутатор 36 выходом соединен с входом усилителя мощности 26, переключающего ключи демодулятора 15. Реверсивный счетчик 28 выходами прямого и обратного переноса подключенк В- н Sвходам основного триггера 37, выходы которого подключены к суммирующему и вычитающему входам счетчика 28. Кроме того, выход обратного переноса счетчика 28 соединен с тактовым входом дополнительного триггера 38, выходом подкпюьченного к управляющему входу дополнительного коьшутатора 37. Входы коммутаторов ЗО-36 соединешл с прямым и инверсным выходом задающего генератора 27. ,ч Каждый коммутатор ЗО-36 (фиг. 2) выполнен ш элементе 2 2И-2ИЛИ, выход которого образует выход коммутатора, первые входы 9л««1ентов 39 2И образуют вхо№1 коммутатора, подключенные к выходам задающего гедаратора 27. Управляющий вход ячейки прдключен ко второму входу первого элемента 39 и через инвертор 40 - ко второму входу второго элемента 39. На фиг. 3 приведены временные диаграммы тактового напряжения 41; напряжения 42-44 ва выходных обмотках 12-14 ячеек 2-4; вапрвпкение 45 на входе демодулятора и выходное напря жавве 46 вввертора. 510 Сушйость работы устройства основана на и мёнешш попярности выходных напряжений 42-44 ячеек в раэпичше моменты времени. Формирование большого числа уровней выходного напряжения пр&образоватепя достигается за счет изменения вь1ходных напряжеш1й ячеек по троичному закону, при котором амплитуда первогх,напряжения 42 равна 3 «1 второго 43-3 З; третьего 9 и т.д. Производят коммутации напряжений в различные моменты времени, можно получить при использовании двух иН рторов четыре ступени, при трех - тринадцать и т.д. При выборе частоты работы ячеек в 80 и более раз выше вы ходной обеспечивается величина коэ4Фициента гармоник Кг 3,9%. Работа инвертора осуществляется сле дующим образом. Сигнал с прямого выхода задающего генератора 27 поступает ра счетный вход реверсивного счетчика 28. Допустим, что основной триггер 37 находится в сро тоянии 1 и обеспечивает заполнение, счетчика в прямом направлении. При это параллельный нарастающий код с выходом триггеров счетчика 28 поступает на- адресные входы проГ|жммируемого запоминающегоустройства 29, выполненного, например, на схеме 155 РЕЗ. На первые входы элементов 2И{39) коммутаторов 30-35 поступают сигналы от прямого либо инверсного выходов задающего генерагора 27, а на вторые входы подают ся противофазные сигналы с ПЗУ 29. На выходе элемента 39, а следовательно, на выходе ячейки основного ко1 мутатора формируются последовательности импульс сов, повторяющие сигналы задающего генератора, снимаемые спрямого либо инверсного выхода его. Каждый выход основных коммутаторов 30-35 подключав к своему усилителю:мощности, выполненному по инверторной схеме с нулевой точкой, формирующему последовательности импульсов таким образом, что на выходной обмотке каждого инвертора могут формироваться напряжения 1-1; О; +1. На 4яг. 3 показано тактовое напряжение 41, позволяющее судить о полярности BI ходного напряжения 42-44 каждой ячейки 2-4. Сигналы с выхода дополнительного коммутатора 36, который выполнен по одинаковой схеме с основным, следую также с частотой задающего генератора. Так как демодулятор переключается под действием сигналов одного усилителя 758 мсшйости 26, то в отличив от травзисторов ячеек 2-4 в любой момент времени открыли ключи 16 и 19 или 17 и 18. При атом на выходе демодулятора 15 формируется ступенчато изменяющееся выходше напряжение 46. Приближение выходного напряжения к синусоидаль ной обеспечивается за счет высокой про межуточной частоты работы ячеек 2-4 и болыпого числа ступеней. При перепопнэнии реверсивного счетчика на выходе прямого переноса появляется сигнал, который опрокидывает основной триггер 37 в состояние О и заставляет работать счетчик 28 в режиме обратного счета. При этом на выходе демодуттятора формируется ступенчато убывающее напряжение 46, симметричное показанному на фиг.3« При обнулении счетчика 28 ш выходе обратного переноса появляется импупьс, опрокидывающий основной триггер 37 в состояние I, воздействующее на входы прямого и обратного счета. Процесс работы счетчика 28 при этом происходит аналогично рассмотренному. Одновреме но при обнулении счетчика 28 импупьс с выхода обратшэгю переноса последнего поступает на тактовый вход дополнитепы ного триггера 38 и изменяет его состояние. Сигнал с выхода дополнительного триггера 38 поступает на управляющий вход дополнительного коммутатора 36 и осуществляет реверс фазы работы ключей демодулятора 15 на 18О эл.град. На выходе инвертора формируется отрицательная полуволна выходного напряжения 46. Таким образом, в предлагаемом уст ройстве при выполнении силовой части, содержащей модзотятор и демодулятор, осуществггается п|юо6разование постоявного напряжения в переменное с шлсокой частотой. Построение системы управп ния, содержащей реверсивный счетчик, программируемое запоминающее устройство, коммутаторы, основной и допсихнвтельный т{жгтер, выпопнеивой на цифровых элементах, позволяет осушествгшть коммутадшо всех трювэисторов внверторных ячеек, т.е. обеспечивать три состояния ( О; ) каждой ячейки . относительно тактового сигвапа. Изменение коэффициентов трансформации выходных трансформаторов осуществпяется по троичному закону. Поэтому в выходном напряжешш преоб|)азоввгепя формируется большое чисто ступени С (щя N З В 13) Выбор частоты работы ввверто

ров в 80 и nee раз большей выходной частоты преобрааоватепя обеспечивает бопыиую ступень приближения к -синусоиде. Например, при вылодной частоте ВЬК SO Г частота работы инверторов ДОПЖ1К1 быть большей 4ООО Гц, .при этом апя f я13 Кг «,9%. При дапыюйшем повышении частоты масса силовой части преобразователя определяется в

основном только массой полупроводниковых элементов и обеспечивается замема сердечников из электротехнической стали на ферритовые пра одновременнсад умен : шении объема меди, используемой на изготовление обмоток. Это помимо умеш шения габаритов преобразователя снижает материалоемкость трансформаторов и стоимость их..

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь постоянного напряжения в переменное напряжение заданной формы | 1986 |

|

SU1379925A1 |

| Преобразователь напряжения с многозонной импульсной модуляцией | 1985 |

|

SU1259449A1 |

| Преобразователь постоянного напряжения в квазисинусоидальное | 1982 |

|

SU1193760A1 |

| Преобразователь постоянного напряжения в переменное программируемой формы | 1981 |

|

SU972650A1 |

| Способ преобразования переменного напряжения в постоянное | 1985 |

|

SU1385208A1 |

| Устройство для управления преобразователем постоянного напряжения в постоянное | 1983 |

|

SU1144174A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Устройство для управления тиристорным статическим преобразователем | 1982 |

|

SU1115199A1 |

| Преобразователь @ -фазного напряжения с промежуточным ВЧ-преобразователем | 1985 |

|

SU1394370A1 |

| Программируемый преобразователь напряжения произвольной формы в напряжение требуемой формы | 1990 |

|

SU1711303A1 |

1. ИНВЕРТОР СО СТУПЕНЧАТЫМ КВАШСИНУСОИДАЛЬНЫМ ВЫХОДНЫМ НАПРЯЖЕНИЕМ, содержащий модупяго|, млпопкенвый ш базе VI моб- трвых инверторных ячеек с оыходвыми трансформаторами, вторичные охотки которых соедиввнв последовательно, задающий генератор, реверсивный счетчик и освовшЛ треттер, отпичающнА. с я тем, что, с цепью улучшения киссо1.ба|)втных показателей, ju него введены дешщулятор, JвкгuючeнШ9Iй на выходе ин вертора, программируемое запоминакушее устройство, основные и дополнитепь ный коммутаторы и допопнительный триг гер, причем прямой выход запакядехх} ге, нератора соединен со счетным входом реверсивного счетчика, выходами прямого и обратного перевккя подключенного соответственно к R- и S -входам основнюго триггера, прямым и инверсным выходам связанного сортвегственно с суммирующим и вычитаюо1им входами реверсиввого счетчика, выход обратного переноса котоPOIX подключен к тактовому входу допопнитепьного триггера, выходом соединенното с управляющим входам дополнительного к(:.1мутатора, выход которого подключен It управляющему входу демодулятора, выходы триггеров реверсивного счетчика подключены к адресным входам програм (Л мируемого запоминающего устрсЛства, выходами подкточенного к управляющим . входам основных коммутаторов, выходами СезанныX с утфавляющими входами ин- ; верторвых ячеек модулятора, а входы коммутаторе соединены с прямым и ин|Версным выходами задающего генератора. о 2. Инвертор по m 1, о т л и ч а ю щ и и с я тем. Что каждый коммута- СП тор выполюн на логическом апшдевте н 2-2И-2ИЛИ, Еыход которого образует :л выход коммутатора, первые входы впэддеяЭО тов 2И образуют входы ксвлмутатора а управляющий вход к(Я 4мутатора соединен непосредственно со вторым входом первого эпемевта 2И и через нЬвертирукяаий епемент - со вторым входом второго элемента 2И.

f

1

(рив.2

Авторы

Даты

1983-08-15—Публикация

1982-04-29—Подача