Текст описания приведен в факсимильном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| Статический возбудитель электрических машин | 1991 |

|

SU1786618A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Устройство для защиты погружного электродвигателя от перегрузки и анормальных режимов | 1990 |

|

SU1777198A1 |

| Стабилизированный источник питания | 1986 |

|

SU1390736A1 |

| Устройство для управления разрядником электроимпульсной установки | 1990 |

|

SU1778752A1 |

| Измерительный преобразователь для тензорезисторных весоизмерительных устройств | 1990 |

|

SU1830463A1 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Преобразователь тока в частоту | 1989 |

|

SU1695504A1 |

| Множительно-делительное устройство | 1980 |

|

SU949662A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ В ПОСТОЯННОЕ | 1995 |

|

RU2094936C1 |

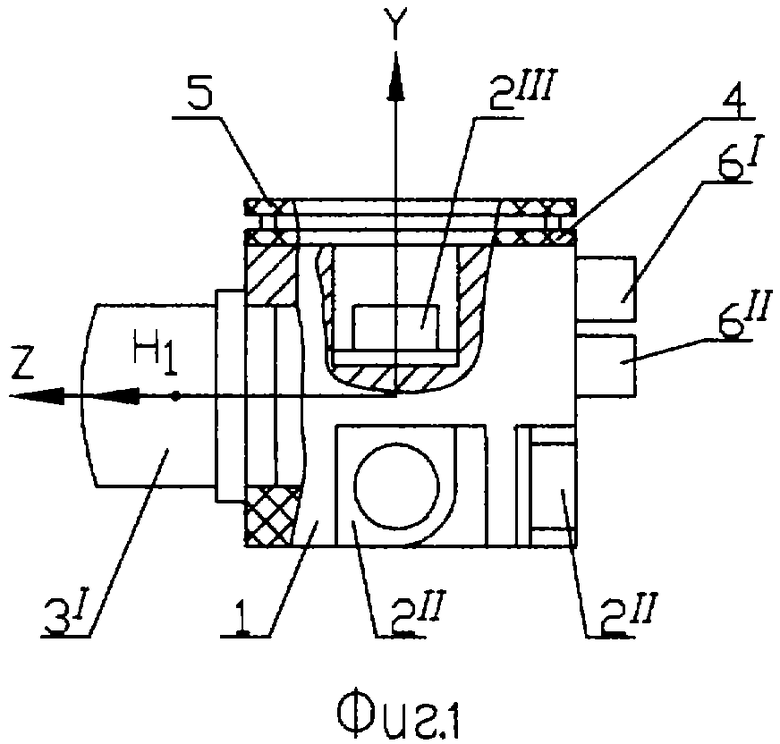

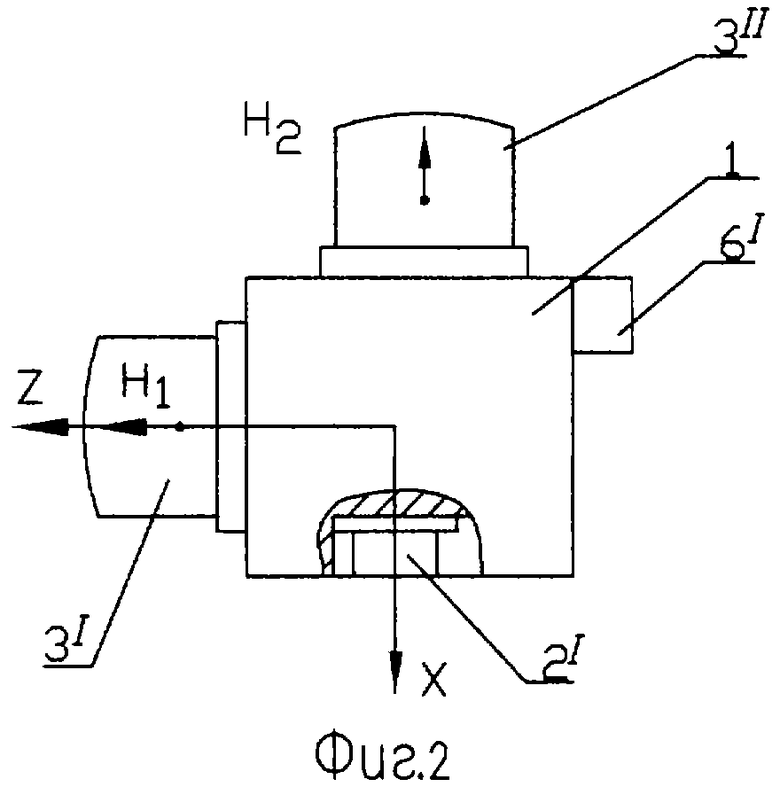

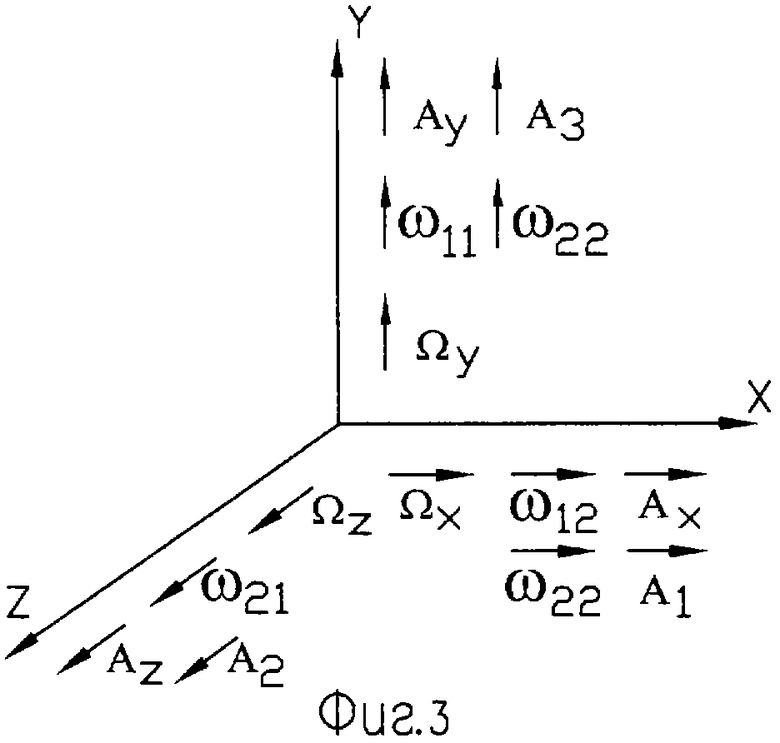

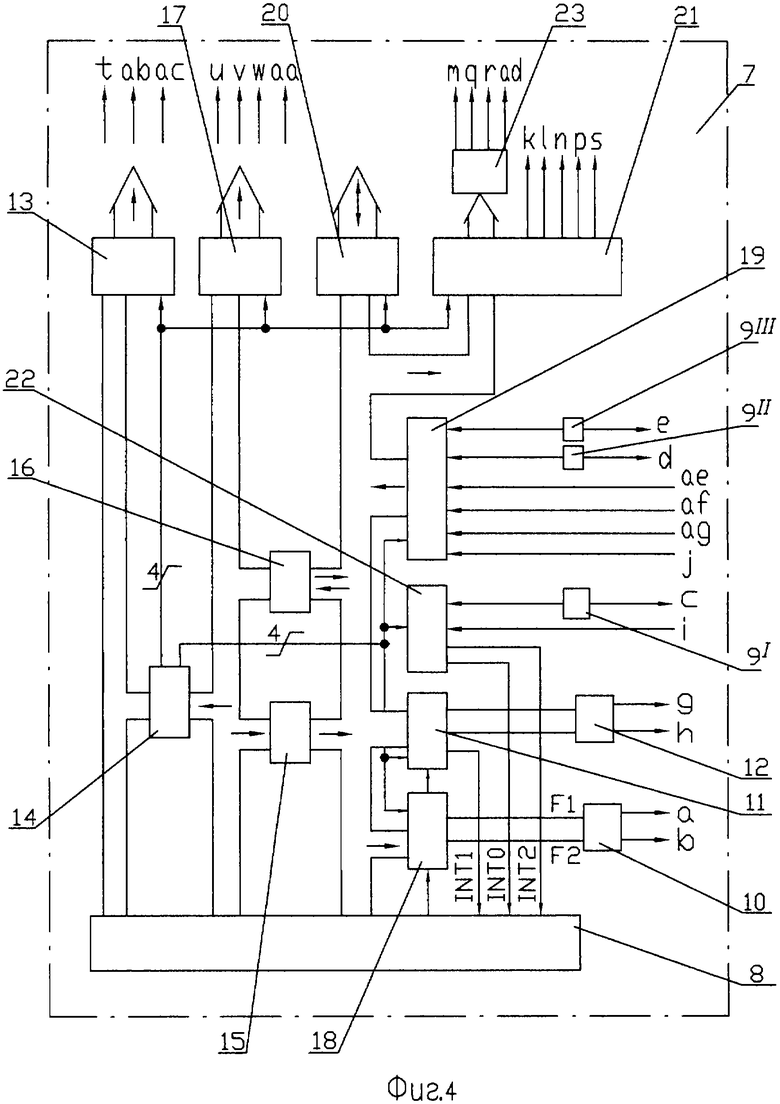

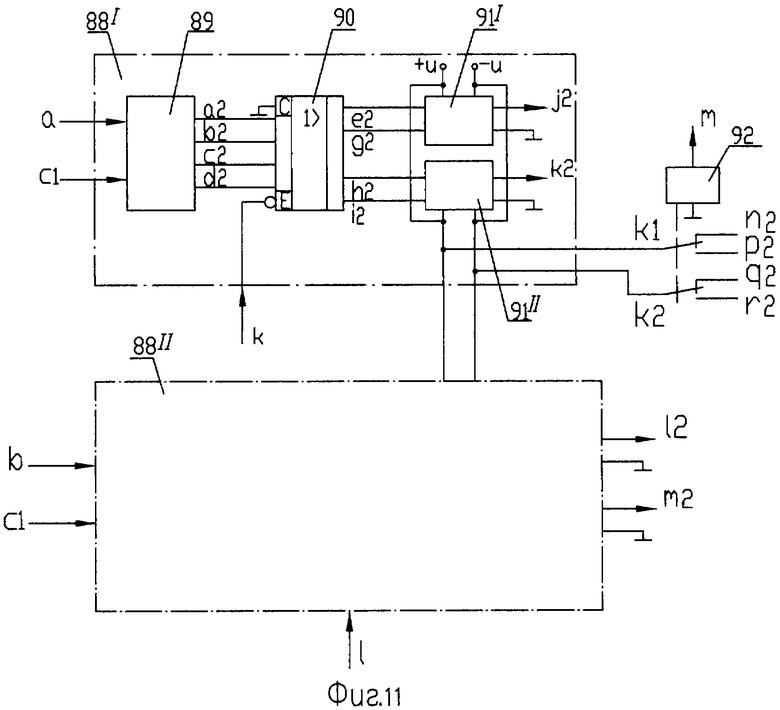

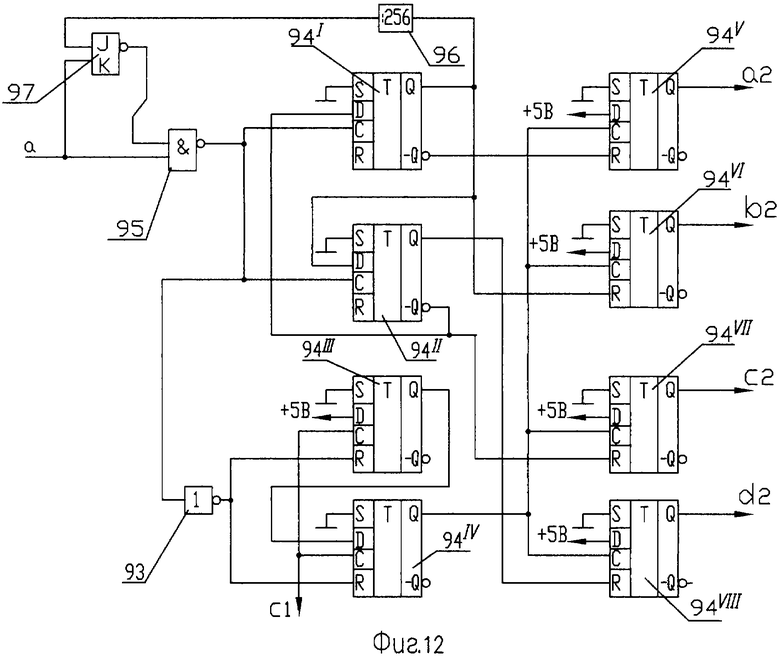

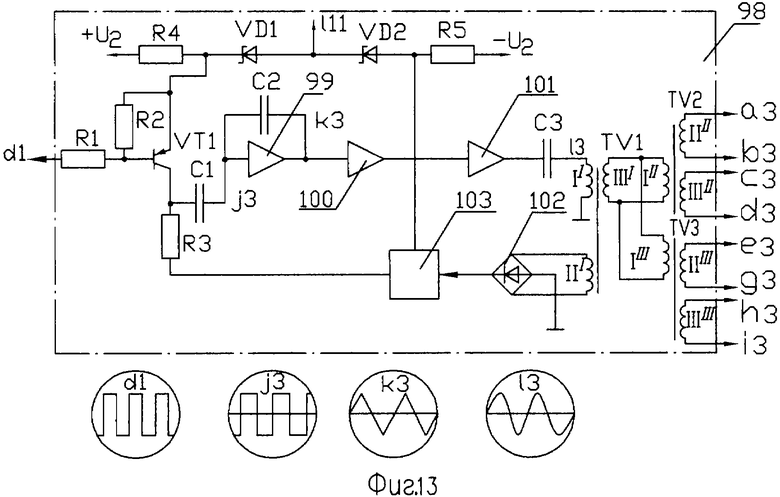

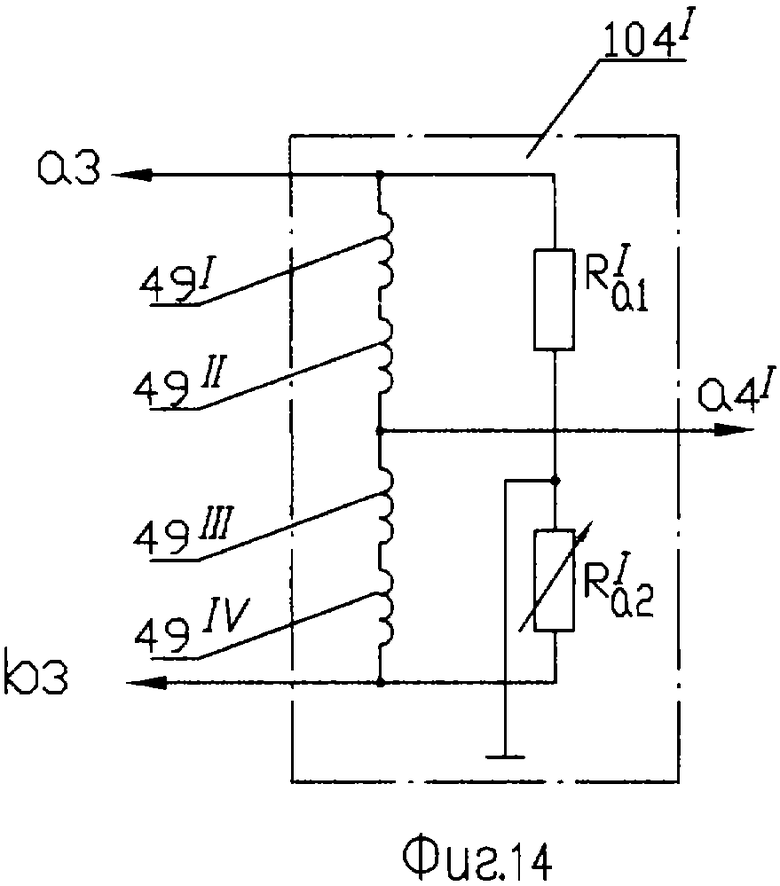

Изобретение относится к измерительной технике, а именно к устройствам, содержащим преобразователи угловой скорости и линейного ускорения по нескольким осям. Преобразователь инерциальной информации содержит устройства измерения линейных ускорений и угловых скоростей, устройство преобразования аналоговых сигналов в цифровой код, центральное вычислительное устройство (ЦВУ), источники вторичного питания переменного и постоянного тока, устройство тест-контроля. В устройстве измерения угловых скоростей в каждый канал выведены три коммутируемых по сигналам от ЦВУ нагрузочных резистора. В устройстве измерения линейных ускорений в каждый канал введены три эталонных резистора, коммутируемых по сигналам от ЦВУ. В устройстве преобразования аналоговых сигналов в цифровой код выполнены семь мультиплексоров, семь цифроаналоговых преобразователей, шинный формирователь, регистр управления, дешифратор управления, дешифратор записи, дешифратор выбора чтения, дешифратор чтения, два калибровочных резистора, стабилизатор напряжения, три повторителя и три инвертора, сдвоенный ключ, в нем выполнено устройство управления на восьми инверторах, семи D-триггерах, четырех логических устройствах 2И-НЕ, логическом устройстве И. В источниках вторичного питания переменного тока формирователь импульсов управления выполнен на инверторе, восьми D-триггерах, логическом устройстве И-НЕ, делителе частоты, JK-триггере, в них введены аналоговый интегратор, компаратор, два стабилизатора напряжения, три трансформатора, выполнен ключ на транзисторе. В источник вторичного питания постоянного тока введены фильтр радиопомех, транзистор, два диода, электромагнитное реле, три конденсатора, батарея буферных конденсаторов, в каждый из четырех преобразователей напряжения введены входной LC-фильтр, RC-цепь, полевой транзистор, два дифференциальных усилителя, транзисторная оптопара, источник опорного напряжения. В ЦВУ введены три оптрона, буферное устройство, электрически перепрограммируемое постоянное запоминающее устройство, программируемый таймер, дешифратор, буфер команд, регистры приема и выдачи разовых команд, триггер прерываний, логические устройства «открытый коллектор», в микропроцессор ЦВУ введены накапливающий сумматор, тактовый генератор. Технический результат: повышение точности измерения угловой скорости и линейного ускорения. 36 ил.

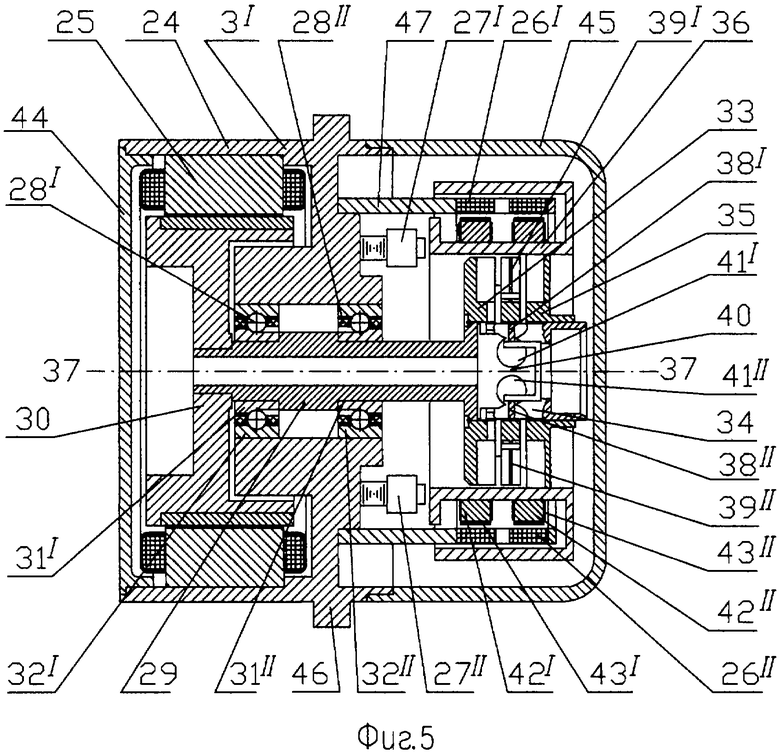

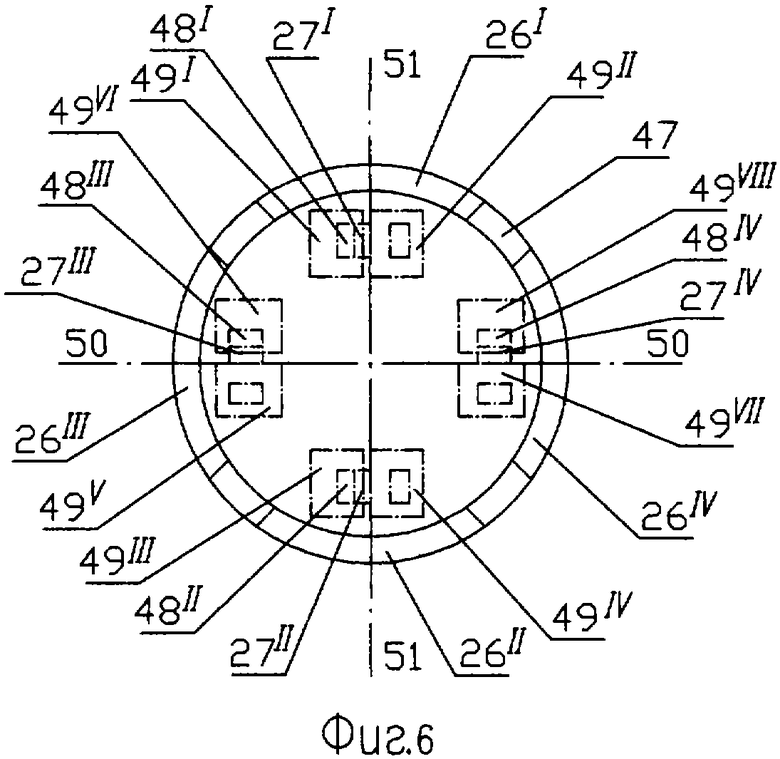

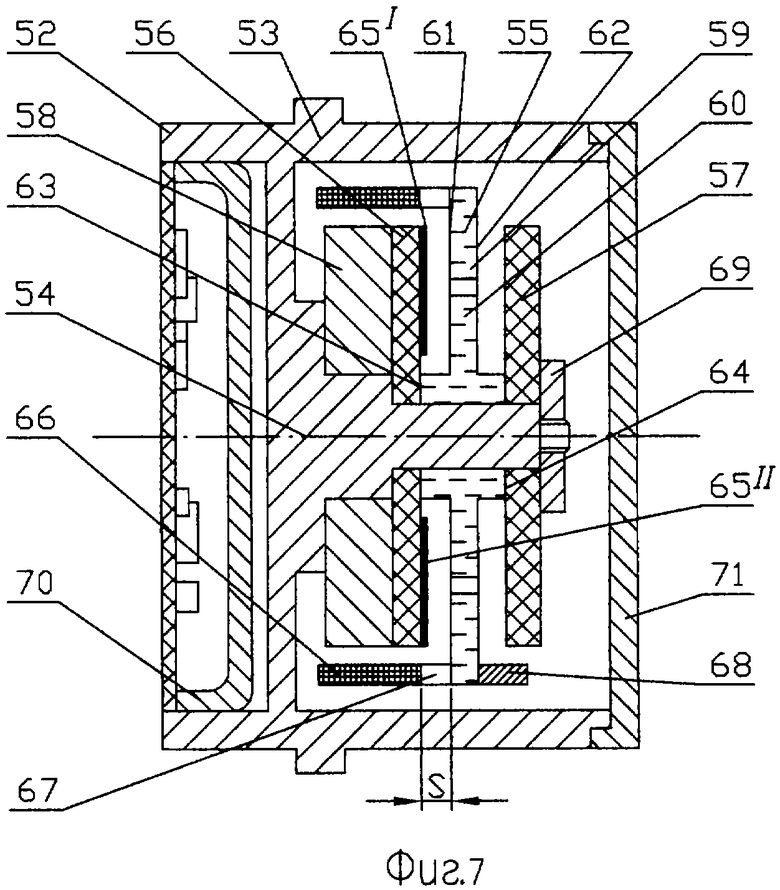

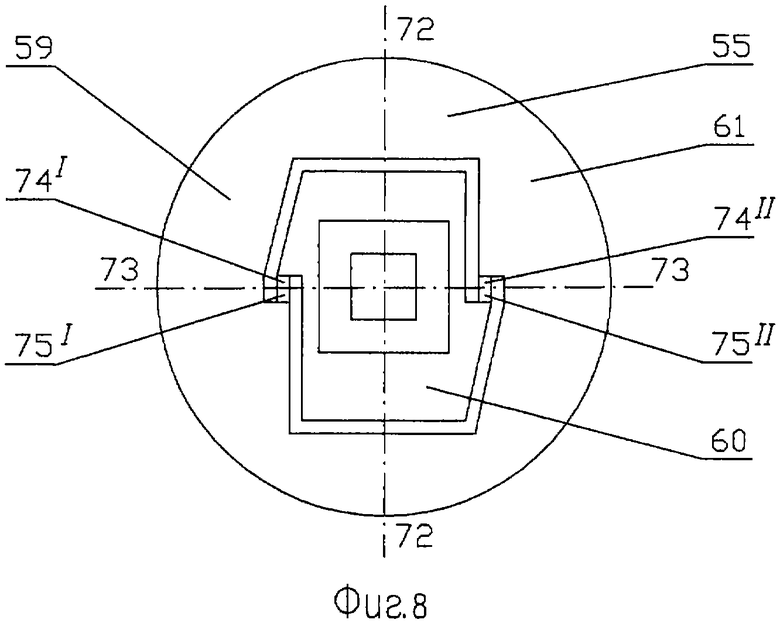

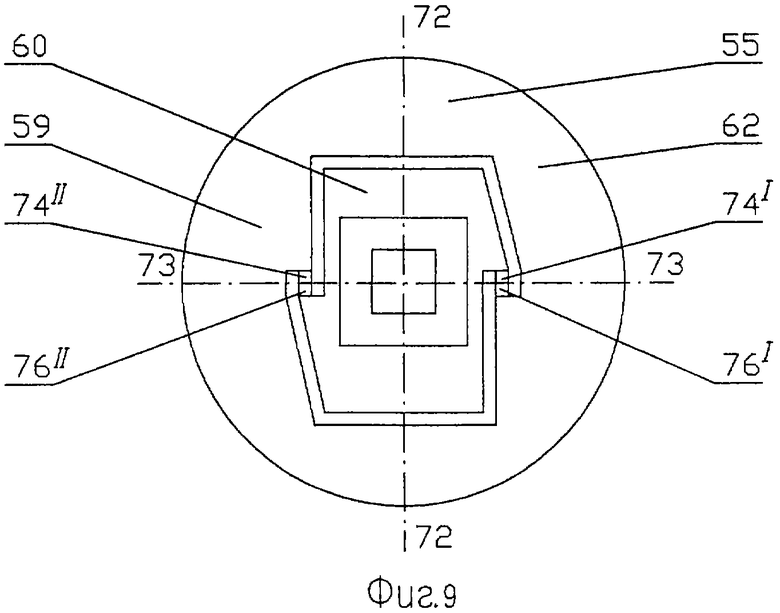

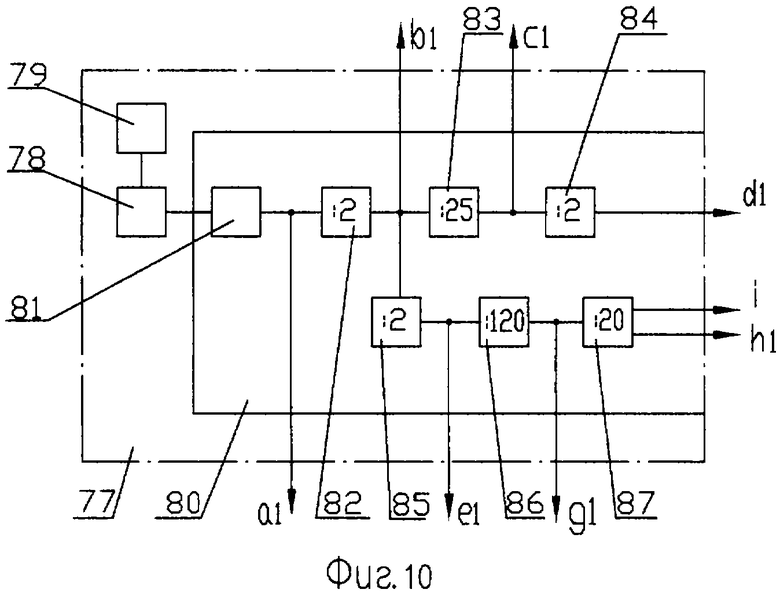

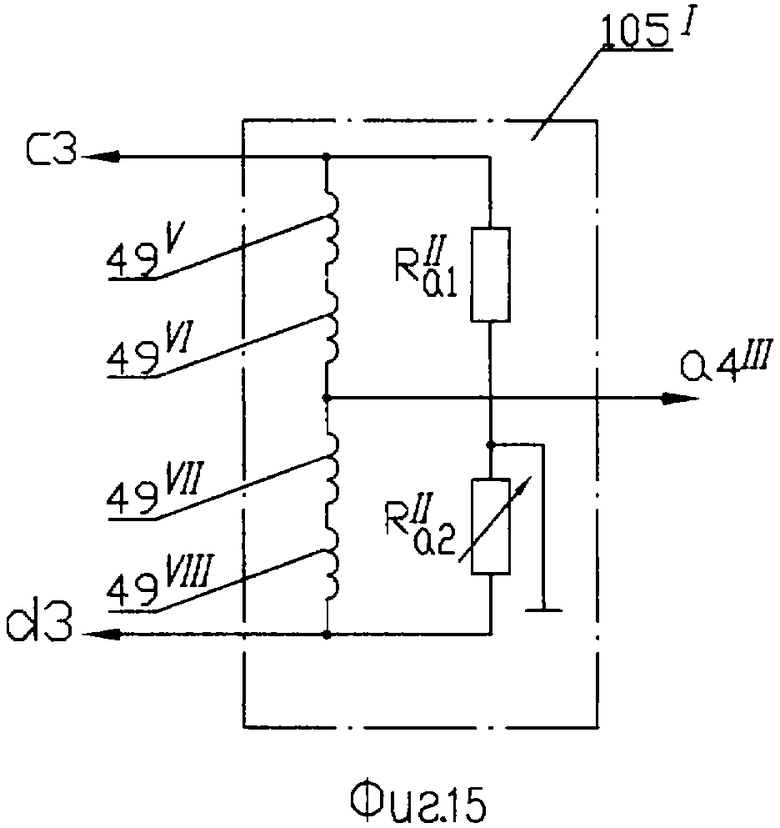

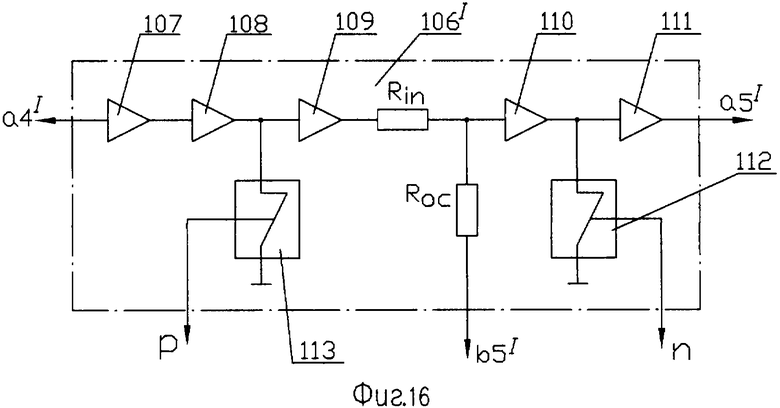

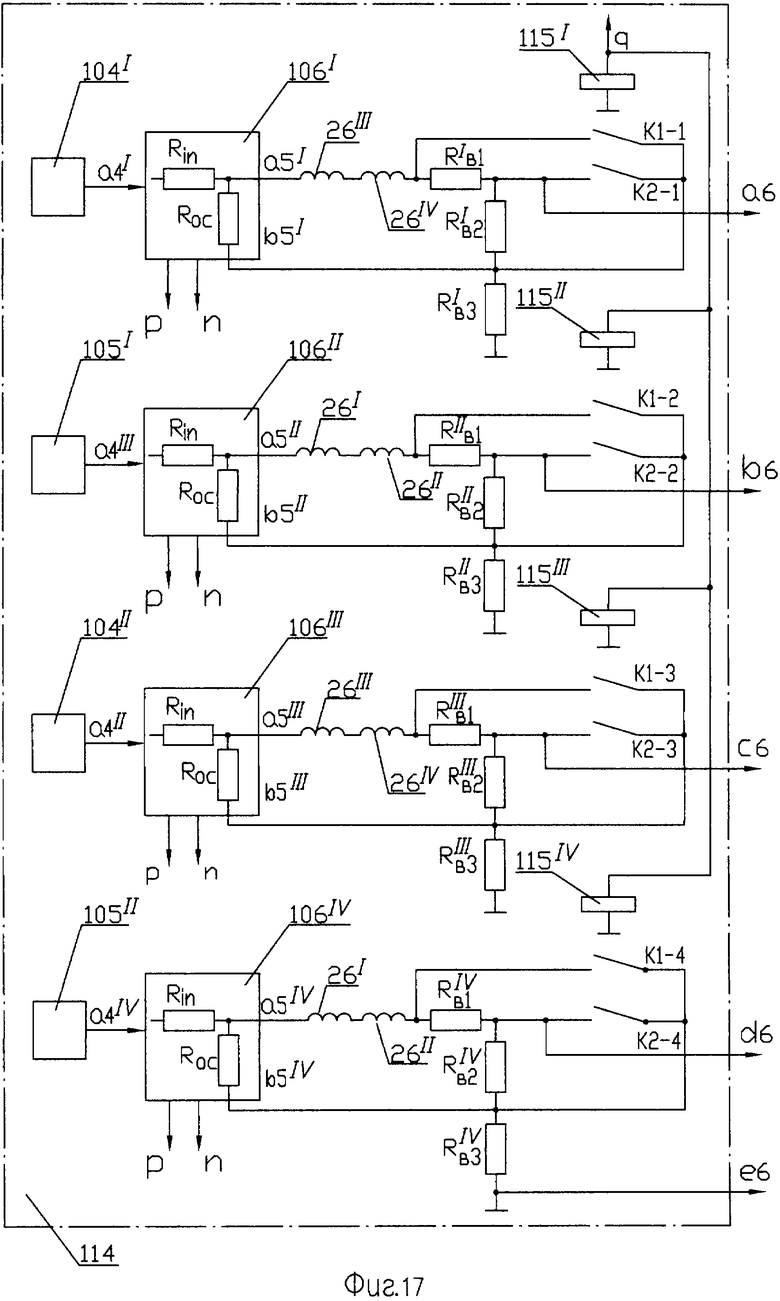

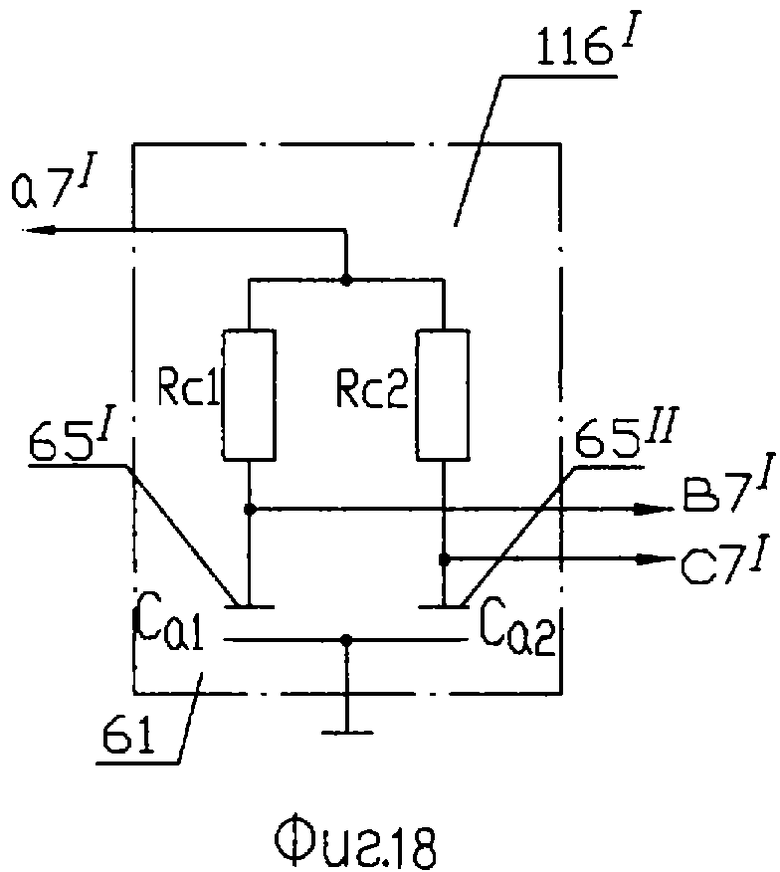

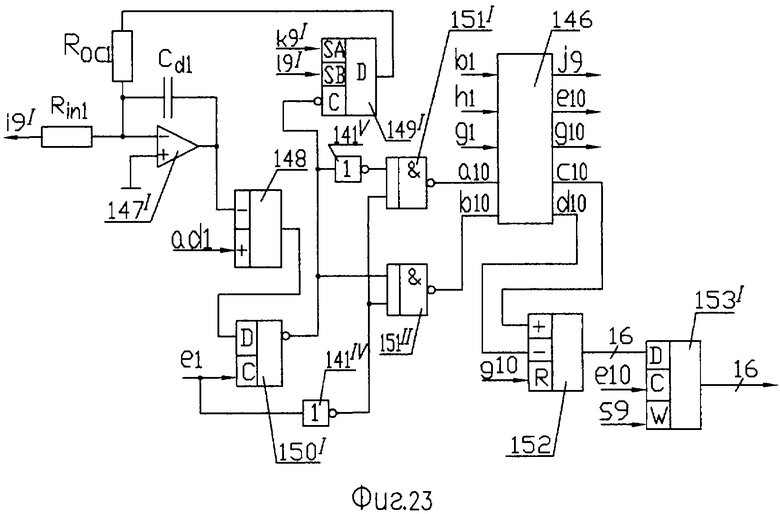

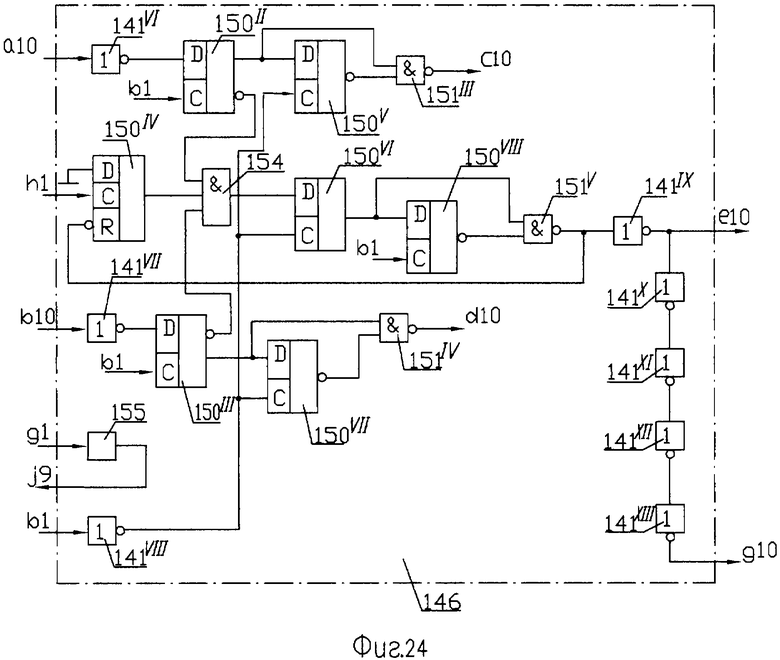

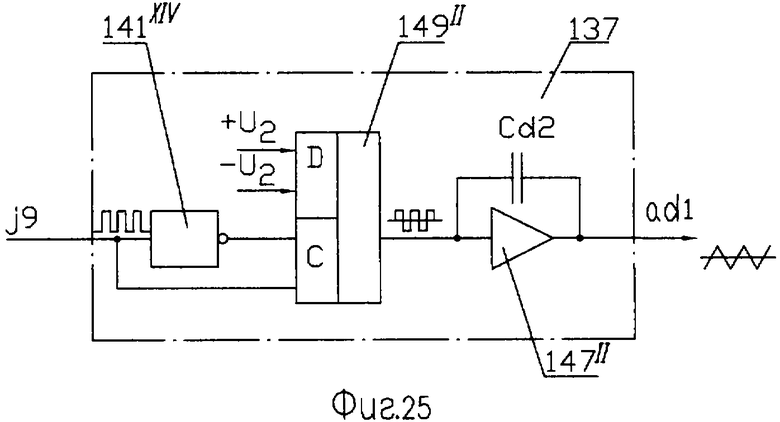

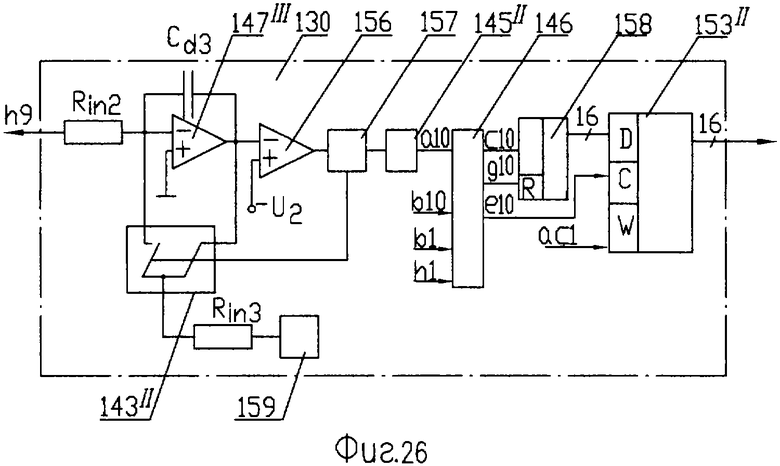

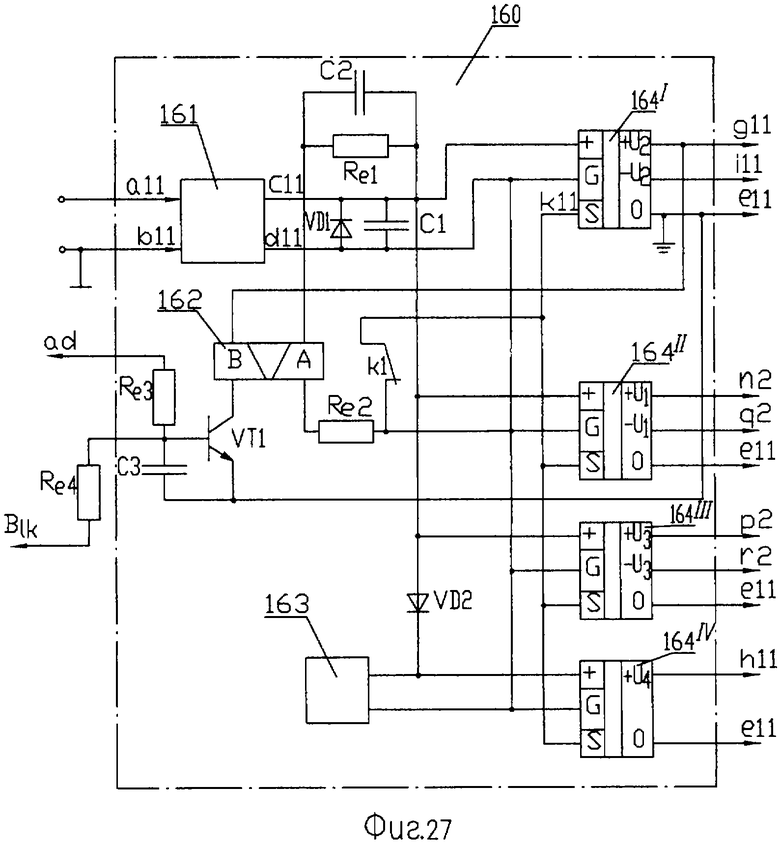

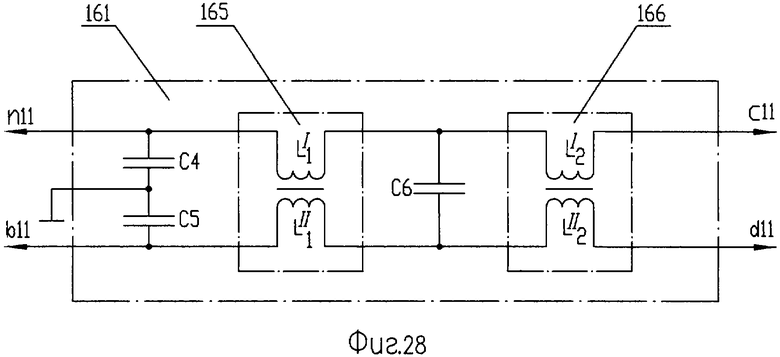

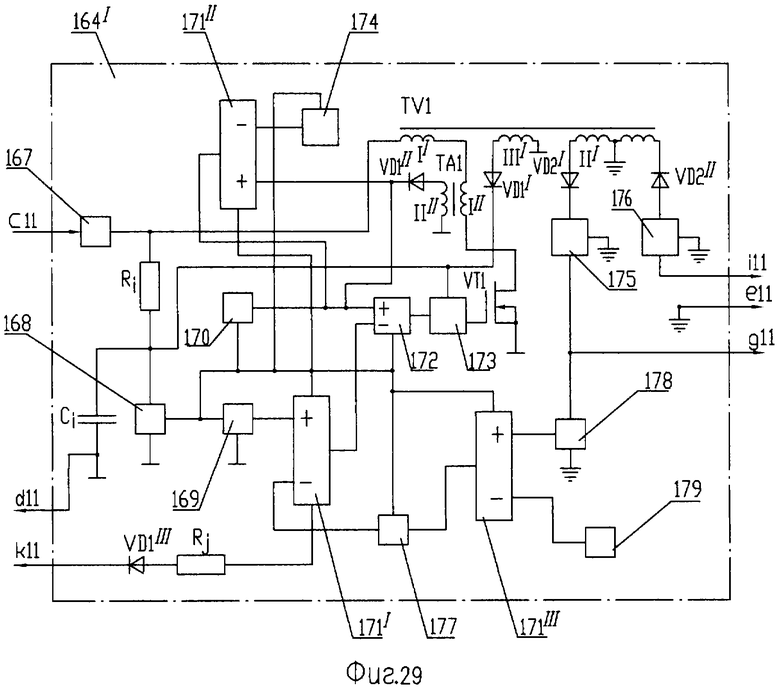

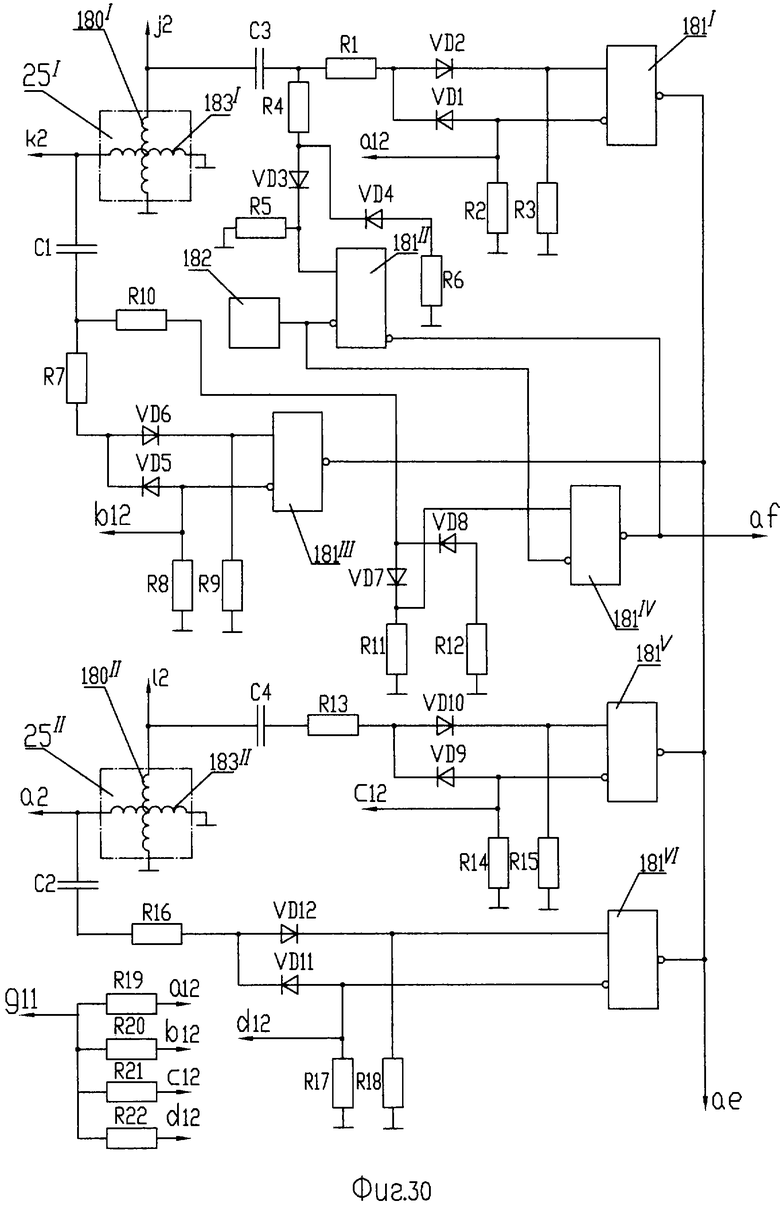

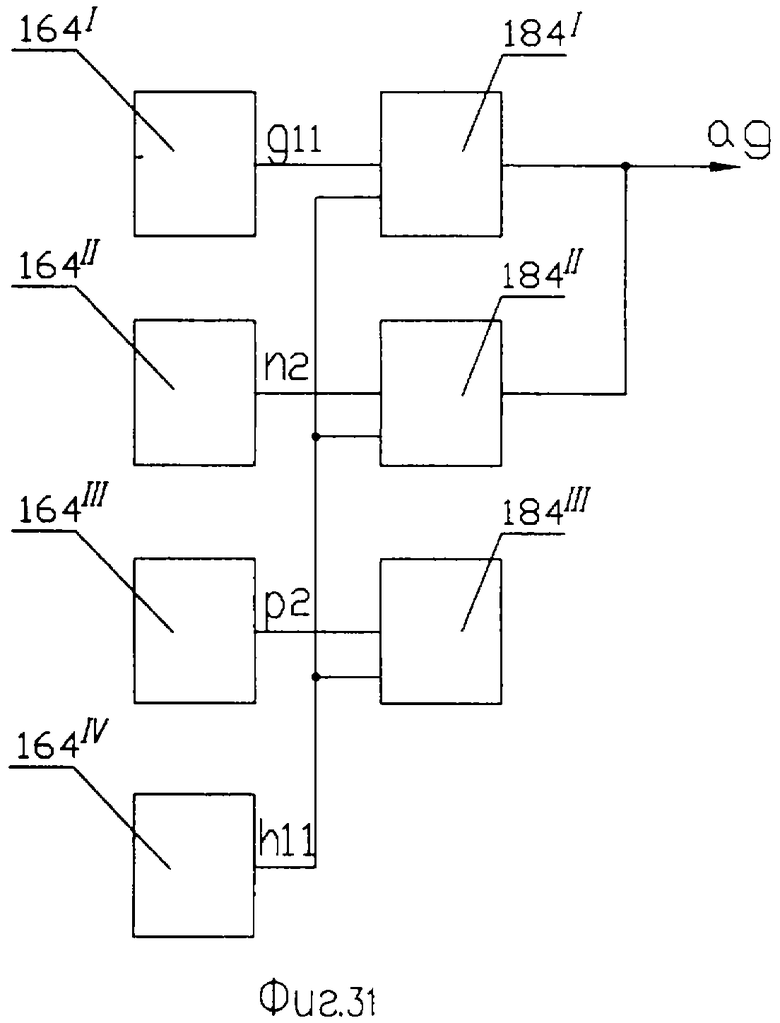

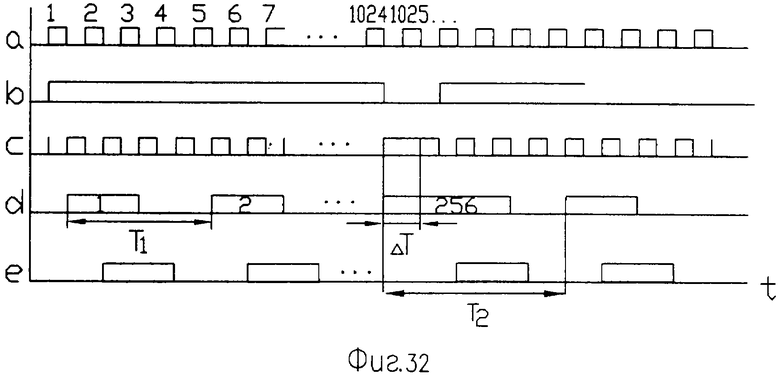

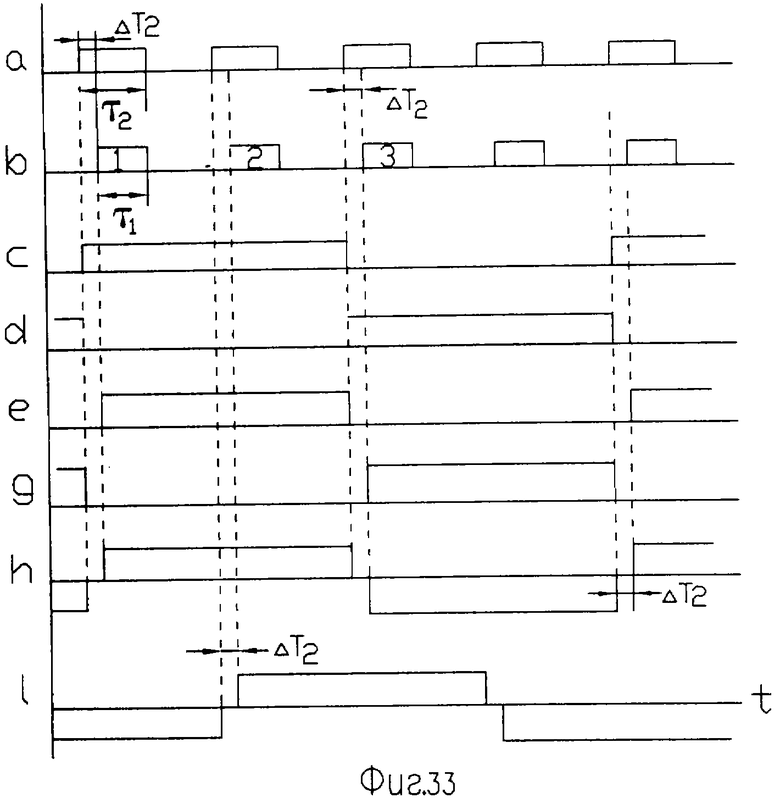

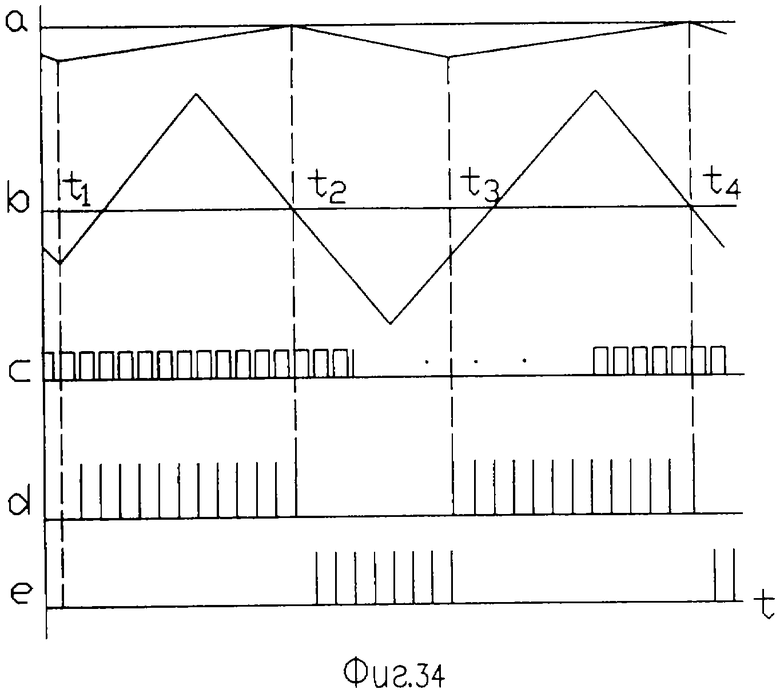

Преобразователь инерциальной информации, содержащий устройство измерения линейных ускорений с каналами измерения линейного ускорения по каждой из трех ортогональных осей с одним из трех акселерометров, устройство измерения угловых скоростей с каналами измерения угловой скорости относительно каждой из вышеуказанных трех ортогональных осей с одной из измерительных осей первого и второго гироскопов и дополнительным каналом измерения угловой скорости относительно одной из трех вышеуказанных ортогональных осей с одной из измерительных осей одного из двух вышеуказанных гироскопов, устройство преобразования аналоговых сигналов в цифровой код, источник специальных сигналов с генератором высокой частоты и базовым делителем частоты, первый и второй источники вторичного питания переменного тока, каждый из которых содержит формирователь импульсов управления; третий источник вторичного питания переменного тока, содержащий ключ, предварительный усилитель, усилитель мощности и выпрямитель; источник вторичного питания постоянного тока с преобразователем напряжения, содержащим широтно-импульсный модулятор, источник служебного электропитания, устройство обратной связи по напряжению, измерительный трансформатор, ключевой усилитель, стабилизаторы напряжения, выходные LC-фильтры, импульсный трансформатор с вторичными обмотками, к которым подключены диодные выпрямители; устройство тест-контроля, центральное вычислительное устройство с микропроцессором, оперативным запоминающим устройством (ОЗУ), буферами данных и адреса, причем микропроцессор выполнен с образованием трех внешних прерываний, каждый акселерометр содержит чувствительный элемент с неподвижной и подвижной частями, соединенными упругими перемычками, емкостный преобразователь положения, обратный преобразователь магнитоэлектрического типа с постоянным магнитом и компенсационной катушкой, усилитель, каждый гироскоп содержит двигатель, два преобразователя положения индуктивного типа, два преобразователя момента магнитоэлектрического типа с постоянными магнитами, узел двухстепенного упругого подвеса, каждый преобразователь момента содержит первую и вторую компенсационные катушки, соединенные последовательно своими первыми выводами; каждый канал измерения угловой скорости содержит усилитель следящей системы с усилителем переменного тока, демодулятором и усилителем постоянного тока; устройство тест-контроля содержит подключенные к обмоткам статоров двигателей гироскопов делители напряжения с резисторами и выпрямители в виде диодов, первый, второй, третий и четвертый компараторы, выходы которых соединены вместе, а диоды включены между резисторами делителей напряжения; в гироскопах установлены соответственно первый и второй терморезисторы; акселерометры и гироскопы установлены на основании; в центральном вычислительном устройстве выполнены алгоритмы управления, вычислений и компенсации методических погрешностей, отличающийся тем, что на основании первый гироскоп расположен так, что первая его измерительная ось направлена по оси курса, вторая измерительная ось направлена по оси крена, второй гироскоп расположен так, что первая его измерительная ось направлена по оси тангажа, а вторая измерительная ось направлена по оси курса; у каждого гироскопа двигатель выполнен как двухфазный синхронный гистерезисный двигатель с тремя парами полюсов, постоянные магниты выполнены кольцевыми из пяти сегментов каждый, изготовленных из сплава редкоземельных металлов Sm2Co5, и закрыты колпаками; в корпусах каждого акселерометра установлены соответственно третий, четвертый и пятый терморезисторы, в каждом акселерометре неподвижная часть, подвижная часть и соединяющие их упругие перемычки выполнены единым элементом в пластине из монокристаллического кремния, на постоянном магните установлена плата с двумя неподвижными электродами емкостного преобразователя положения, на одной стороне подвижной части установлен груз, на другой стороне подвижной части на четырех грузах установлена компенсационная катушка обратного преобразователя, одна сторона упругих перемычек совмещена с одной из сторон пластины из монокристаллического кремния, в корпусе каждого акселерометра установлен модуль электроники, содержащий генератор высокой частоты и усилитель, состоящий из первого и второго усилителей переменного тока, суммирующего усилителя, демодулятора и усилителя постоянного тока с корректирующим фильтром; в центральное вычислительное устройство введены первый, второй и третий оптроны, буферное устройство, канал передатчика в составе контроллера передатчика и формирователя биполярного напряжения, электрически стираемое перепрограммируемое постоянное запоминающее устройство (ППЗУ) с организацией 32К×16, статическое ОЗУ объемом 8К×16, программируемый таймер, дешифратор, буфер команд, регистр приема разовых команд, регистр выдачи разовых команд, триггер прерываний, микросхема с логическими устройствами «открытый коллектор» (ОК); в микропроцессор введены накапливающий сумматор, тактовый генератор, стабилизируемый кварцевым резонатором с частотой 16 МГц, внутрикристальное ОЗУ на 544 слова, в микропроцессоре образованы 16 портов ввода и вывода, 32-разрядные арифметические логические устройства, внешние 16-разрядные шины адреса и данных, три внутренних прерывания, микропроцессор выполнен с эффективным быстродействием до 3 млн операций/с, система его команд содержит 131 команду, в том числе операции умножения 16×16=32 с фиксированной запятой и команды нормализации чисел для реализации вычислений с плавающей запятой; выход микропроцессора от тактового генератора подключен на вход синхронизации программируемого таймера; микропроцессор, дешифратор и буфер команд соединены шиной управления; микропроцессор, дешифратор, буфер адреса, ППЗУ и ОЗУ соединены шиной адреса; микропроцессор, ППЗУ, ОЗУ, буфер данных, программируемый таймер, контроллер передатчика, регистр приема разовых команд и регистр выдачи разовых команд соединены шиной данных, выходы дешифратора соединены со входами разрешения буфера команд, буфера адреса, буфера данных, регистра приема разовых команд, программируемого таймера, контроллера передатчика, триггера прерываний, регистра выдачи разовых команд; две линии выхода контроллера передатчика подключены к входам формирователя двуполярного напряжения, в программируемом таймере выполнены соединенный с входом контроллера передатчика канал формирования частоты тактирования передатчика, а также первый и второй каналы формирования первой частоты F1=12F1вp и второй частоты F2=12F2вр (где F1вр и F2вр - соответственно частоты вращения роторов двигателей первого и второго гироскопов) с относительной дискретностью (3-5)·10-4, выход первого канала программируемого таймера с частотой F1 соединен с первым входом буферного устройства, выход второго канала с частотой F2 соединен с вторым входом буферного устройства; выходы регистра разовых команд соединены с входами микросхемы с логическими устройствами ОК; выходы команд «Запрос», «Тест-контроль» и «Выдача по запросу» от внешней ЭВМ подключены к входам первого, второго и третьего оптронов, выход первого оптрона подключен к первому входу «Запрос» триггера прерываний, первый выход с командой «Запрос» которого подключен к первому входу запроса прерываний от внешнего сигнала в микропроцессоре, а второй выход с сигналом «Цикл 1» подключен ко второму входу запроса прерываний от внешнего сигнала в микропроцессоре, выходы второго и третьего оптронов подключены соответственно к первому и второму входам регистра приема разовых команд, выход контроллера передатчика соединен с третьим входом запроса прерываний от внешнего сигнала в микропроцессоре; в ППЗУ центрального вычислительного устройства дополнительно зашиты алгоритм вычисления кода времени устаревания информации и алгоритм компенсации нелинейности акселерометров; в источнике специальных сигналов генератор высокой частоты выполнен на кварцевом резонаторе с частотой последовательного резонанса 1920 кГц; базовый делитель частоты содержит последовательно соединенные формирователь импульсного сигнала с выходом первого цифрового тактового сигнала, первый делитель частоты на 2 с выходом второго цифрового тактового сигнала, делитель частоты на 25, второй делитель частоты на 2, включенную после выхода первого делителя частоты на 2 цепь из последовательно соединенных третьего делителя частоты на 2 с выходом третьего цифрового тактового сигнала, делителя частоты на 120 с выходом сигнала в форме меандра, делителя частоты на 20 с первым выходом «Цикл 1» и со вторым выходом «Цикл 2», первый выход «Цикл 1» подключен к тактовому входу триггера прерываний центрального вычислительного устройства; в каждый первый и второй источники вторичного питания переменного тока введены шестиэлементный буферный усилитель с входом разрешения включения выходов и два ключевых двухтактных усилителя мощности; каждый формирователь импульсов управления содержит инвертор, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой D-триггеры, логическое устройство И-НЕ, делитель частоты на 256, JK-триггер, K-вход JK-триггера и один из входов логического устройства И-НЕ соединены вместе, инверсный выход логического устройства И-НЕ подключен ко входу инвертора и к тактовым входам первого и второго D-триггеров, выход инвертора подключен к входам сброса третьего и четвертого D-триггеров, к тактовым входам которых подключен выход делителя на 25 базового делителя частоты, прямой выход третьего D-триггера подключен ко входу счета четвертого D-триггера, к прямому выходу которого подключены тактовые входы пятого, шестого, седьмого и восьмого D-триггеров, прямой выход первого D-триггера подключен ко входу счета второго D-триггера и ко входу сброса шестого D-триггера, инверсный выход первого D-триггера подключен ко входу сброса пятого D-триггера, прямой выход второго D-триггера подключен ко входу сброса восьмого D-триггера, инверсный выход второго D-триггера подключен ко входу счета первого D-триггера и ко входу сброса седьмого D-триггера, прямой выход первого D-триггера подключен ко входу делителя частоты на 256, выход которого подключен к J-входу JK-триггера, выход JK-триггера соединен с вторым входом логического устройства И-НЕ, прямые выходы пятого, шестого, седьмого и восьмого D-триггеров подключены к входам буферного усилителя, два выхода которого подключены к входам первого ключевого двухтактного усилителя мощности, а два других выхода - к входам второго ключевого двухтактного усилителя мощности; к K-входу JK-триггера первого формирователя импульсов управления подключен первый выход с частотой F1 буферного устройства центрального вычислительного устройства, к K-входу JK-триггера второго формирователя импульсов управления подключен второй выход с частотой F2 буферного устройства; к выходу первого ключевого двухтактного усилителя мощности подключена первая обмотка статора двигателя гироскопа, к выходу второго ключевого двухтактного усилителя мощности подключена вторая обмотка статора двигателя гироскопа, ко входу разрешения включения выходов буферного усилителя первого источника вторичного питания переменного тока подключен первый выход регистра выдачи разовых команд центрального вычислительного устройства, ко входу разрешения включения выходов буферного усилителя второго источника вторичного питания переменного тока подключен второй выход регистра выдачи разовых команд; базовый делитель частоты и оба формирователя импульсов управления выполнены на одном базовом матричном кристалле; выводы питания первого и второго ключевых усилителей мощности первого и второго источников вторичного питания переменного тока подключены к неподвижным контактам первого и второго переключающих контактов электромагнитного реле, общего для первого и второго источников вторичного питания переменного тока, обмотка электромагнитного реле подключена к выходу одного из логических устройств ОК микросхемы центрального вычислительного устройства; в третий источник вторичного питания переменного тока введены аналоговый интегратор, компаратор, первый и второй стабилизаторы напряжения соответственно с первым и вторым стабилитронами, первый, второй и третий трансформаторы с первой и второй вторичными обмотками, ключ выполнен на транзисторе с резистором, база транзистора подключена к выходу второго делителя частоты на 2 базового делителя частоты источника специальных сигналов, к коллектору транзистора подключен первый вывод резистора, второй вывод которого подключен на выход компаратора, к эмиттеру транзистора подключен выход первого стабилизатора напряжения, к коллектору транзистора подключен вход аналогового интегратора, выход которого подключен ко входу предварительного усилителя, к выходу усилителя мощности подключена первичная обмотка первого трансформатора, к первой вторичной обмотке которого подключен выпрямитель, выход выпрямителя соединен с первым входом компаратора, ко второму входу которого подключен выход второго стабилизатора напряжения, к второй вторичной обмотке первого трансформатора подключены первичные обмотки второго и третьего трансформаторов, к первой и второй вторичным обмоткам второго трансформатора подключены соответственно первый и второй преобразователи положения первого гироскопа, к первой и второй вторичным обмоткам третьего трансформатора подсоединены соответственно первый и второй преобразователи положения второго гироскопа; второй и третий трансформаторы установлены на основании с гироскопами и акселерометрами; в устройство аппаратного контроля двигателей гироскопов введены источник опорного напряжения постоянного тока, пятый и шестой компараторы, к первой обмотке статора двухфазного двигателя первого гироскопа подключены первый делитель напряжения из первого и второго резисторов с первым включенным между ними диодом, второй делитель напряжения из первого и третьего резисторов с вторым включенным между ними диодом, третий делитель напряжения из четвертого и пятого резисторов с третьим включенным между ними диодом, четвертый делитель напряжения из четвертого и шестого резисторов с четвертым включенным между ними диодом, второй резистор подключен к аноду первого диода и инверсному входу первого компаратора, третий резистор подключен к катоду второго диода и к прямому входу первого компаратора, пятый резистор подсоединен к катоду третьего диода и к прямому входу второго компаратора, к инверсному входу которого подключен выход источника опорного напряжения постоянного тока, шестой резистор подключен к аноду четвертого диода; к второй обмотке статора двухфазного двигателя первого гироскопа подключены пятый делитель напряжения из седьмого и восьмого резисторов с пятым включенным между ними диодом, шестой делитель напряжения из седьмого и девятого резисторов с шестым включенным между ними диодом, седьмой делитель напряжения из десятого и одиннадцатого резисторов с седьмым включенным между ними диодом, восьмой делитель напряжения из десятого и двенадцатого резисторов с восьмым включенным между ними диодом, к катоду шестого диода подключены девятый резистор и прямой вход третьего компаратора, к инверсному входу которого подключены восьмой резистор и анод пятого диода, к катоду седьмого диода подсоединены одиннадцатый резистор и прямой вход четвертого компаратора, к инверсному входу которого подключен выход источника опорного напряжения постоянного тока, к аноду восьмого диода подключен двенадцатый резистор; к первой обмотке статора двухфазного двигателя второго гироскопа подключены девятый делитель напряжения из тринадцатого и четырнадцатого резисторов с девятым включенным между ними диодом, десятый делитель напряжения из тринадцатого и пятнадцатого резисторов с десятым включенным между ними диодом, к катоду десятого диода подключены пятнадцатый резистор и прямой вход пятого компаратора, к инверсному входу которого подключены четырнадцатый резистор и анод девятого резистора, ко второй обмотке статора двухфазного двигателя второго гироскопа подключены одиннадцатый делитель напряжения из шестнадцатого и семнадцатого резисторов с одиннадцатым включенным между ними диодом, двенадцатый делитель напряжения из шестнадцатого и восемнадцатого резисторов с двенадцатым включенным между ними диодом, к катоду двенадцатого диода подключены восемнадцатый резистор и прямой вход шестого компаратора, к инверсному входу которого подключены семнадцатый резистор и анод одиннадцатого диода, к выходу положительного потенциала второго преобразователя напряжения источника вторичного питания постоянного тока подключены первые выводы девятнадцатого, двадцатого, двадцать первого и двадцать второго резисторов, вторые выводы которых подключены к инверсным входам соответственно первого, третьего, пятого и шестого компараторов; в делителях напряжения соответственно к первому, четвертому, седьмому, десятому, тринадцатому и шестнадцатому резисторам подключен катод одного из соответствующих первого, четвертого, пятого, восьмого, девятого и одиннадцатого диодов, а также анод одного из соответствующих второго, третьего, шестого, седьмого, десятого и двенадцатого диодов; соединены вместе и подключены к одному из входов регистра приема разовых команд центрального вычислительного устройства инверсные выходы первого, третьего, пятого и шестого компараторов; соединены вместе и подключены к одному из входов регистра приема разовых команд инверсные выходы второго и четвертого компараторов; в каждый канал измерения угловой скорости введены первый, второй и третий нагрузочные резисторы, электромагнитное реле, третий нагрузочный резистор выполнен с сопротивлением 0,1-0,2 сопротивления второго нагрузочного резистора, первый нагрузочный резистор выполнен с сопротивлением 0,1-0,3 от суммарного сопротивления второго и третьего нагрузочных резисторов, второй и третий нагрузочные резисторы выполнены из аморфного резистивного сплава с температурным коэффициентом сопротивления не более 10-51/°С по интегральной технологии путем напыления на общей подложке, установленной на теплоотводящей площадке; в усилитель следящей системы каждого канала измерения угловой скорости введены первый ключ и второй ключ, ко входу которого подключен выход демодулятора, выход второго ключа соединен с общей линией усилителя, к управляющему входу второго ключа подключен один из выходов регистра выдачи разовых команд центрального вычислительного устройства, усилитель постоянного тока выполнен в составе входного резистора, резистора обратной связи, первого каскада, второго каскада, усилителя мощности, первые выводы входного резистора и резистора обратной связи подключены ко входу второго каскада, ко второму выводу входного резистора подключен выход первого каскада, ко входу усилителя мощности подключен вход первого ключа, выход которого соединен с общей линией усилителя, к управляющему входу первого ключа подсоединен один из выходов регистра выдачи разовых команд центрального вычислительного устройства, к выходу усилителя мощности подключен второй вывод первой компенсационной катушки преобразователя момента гироскопа, ко второму выводу второй компенсационной катушки подключен первый вывод первого нагрузочного резистора, второй вывод которого соединен с первым выводом второго нагрузочного резистора, с вторым выводом второго нагрузочного резистора соединены первый вывод третьего нагрузочного резистора и второй вывод резистора обратной связи усилителя постоянного тока, у электромагнитного реле первый замыкающий контакт подключен между точкой соединения второй компенсационной катушки преобразователя момента гироскопа с первым нагрузочным резистором и точкой соединения второго и третьего нагрузочных резисторов, а второй замыкающий контакт подключен между точкой соединения первого нагрузочного резистора с вторым нагрузочным резистором и точкой соединения второго и третьего нагрузочных резисторов, обмотки всех четырех электромагнитных реле устройства измерения угловых скоростей соединены параллельно и подключены к выходу одного из логических устройств ОК в микросхеме центрального вычислительного устройства; усилители переменного тока, демодуляторы и первые каскады усилителей постоянного тока усилителей следящих систем всех четырех каналов измерения угловой скорости выполнены по интегральной технологии в виде одной микросборки, которая вместе с четырьмя электромагнитными реле для четырех каналов измерения угловой скорости установлена на первой плате на основании с гироскопами и акселерометрами; в каждый канал измерения линейного ускорения введены электромагнитное реле, первый, второй и третий эталонные резисторы, третий эталонный резистор выполнен с сопротивлением 0,1-0,3 сопротивления второго эталонного резистора, первый эталонный резистор выполнен с сопротивлением 0,01-0,08 суммарного сопротивления второго и третьего эталонных резисторов, к выходу усилителя постоянного тока подсоединен первый вывод компенсационной катушки обратного преобразователя, ко второму выводу которой подключен первый вывод первого эталонного резистора, ко второму выводу первого эталонного резистора подсоединен первый вывод второго эталонного резистора, ко второму выводу которого подключен первый вывод третьего эталонного резистора, параллельно второму эталонному резистору подключен конденсатор, у электромагнитного реле первый замыкающий контакт подключен между точкой соединения компенсационной катушки обратного преобразователя с первым эталонным резистором и точкой соединения второго и третьего эталонных резисторов, а второй замыкающий контакт подключен между точкой соединения первого эталонного резистора с вторым эталонным резистором и точкой соединения второго и третьего эталонных резисторов; обмотки электромагнитных реле всех трех каналов измерения линейного ускорения соединены параллельно и подключены к выходу одного из логических устройств ОК микросхемы центрального вычислительного устройства, первый, второй и третий эталонные резисторы во всех трех каналах измерения линейного ускорения, подключенные параллельно вторым эталонным резисторам конденсаторы во всех трех каналах измерения линейного ускорения, электромагнитные реле во всех трех каналах измерения линейного ускорения размещены на второй плате, установленной на основании с гироскопами и акселерометрами; устройство преобразования аналоговых сигналов в цифровой код выполнено на двух многослойных печатных платах (первая плата имеет 6 слоев, вторая плата имеет 4 слоя с двухсторонним размещением элементов) и содержит шестой терморезистор, первый, второй, третий, четвертый и пятый мультиплексоры с четырьмя входами сигналов и тремя входами селекции, шестой мультиплексор с четырьмя входами сигналов и четырьмя входами селекции, седьмой мультиплексор с восемью входами сигналов и тремя входами селекции, первый, второй, третий, четвертый, пятый и шестой аналого-цифровые преобразователи первого типа, аналого-цифровой преобразователь второго типа, шинный формирователь, регистр управления, дешифратор управления, дешифратор записи, дешифратор выбора чтения, дешифратор чтения, формирователь пилообразного напряжения, источник тока, первый сдвоенный ключ, первый и второй калибровочные резисторы, первый стабилизатор напряжения, к выходу которого подключены первый, второй и третий повторители, а также первый, второй и третий инверторы; первый калибровочный резистор соединен с первым входом первого сдвоенного ключа, с вторым входом которого соединен второй калибровочный резистор, к управляющему входу первого сдвоенного ключа подключен один из выходов регистра выдачи разовых команд центрального вычислительного устройства; второй калибровочный резистор выполнен с сопротивлением 40-60 сопротивлений первого калибровочного резистора; источник тока содержит первый ключ и второй стабилизатор напряжения, в выходную цепь которого включены последовательно соединенные первый и второй резисторы, причем первый вывод первого резистора подключен к выходу положительного потенциала источника вторичного питания постоянного тока и ко входу первого ключа, выход первого ключа подключен ко второму выводу первого резистора, первый резистор выполнен с сопротивлением 8,5-9,5 сопротивлений второго резистора, управляющий вход первого ключа подсоединен к одному из выходов регистра управления; у первого, второго и третьего мультиплексоров к первому входу подключена точка соединения первого и второго эталонных резисторов одного из трех каналов измерения линейного ускорения; ко второму входу подключен выход первого стабилизатора напряжения, к третьему входу подключена общая точка соединения вторых выводов третьих эталонных резисторов каналов измерения линейного ускорения, к первому входу четвертого мультиплексора подключена точка соединения первого и второго нагрузочных резисторов второго канала измерения угловой скорости по второй измерительной оси первого гироскопа, к первому входу пятого мультиплексора подключена точка соединения первого и второго нагрузочных резисторов третьего канала измерения угловой скорости по первой измерительной оси второго гироскопа, к первому входу шестого мультиплексора подключена точка соединения первого и второго нагрузочных резисторов первого канала измерения угловой скорости по первой измерительной оси первого гироскопа, к вторым входам четвертого, пятого и шестого мультиплексоров подключена общая точка соединения вторых выводов третьих нагрузочных резисторов каналов измерения угловой скорости, к четвертому входу шестого мультиплексора подключена точка соединения первого и второго нагрузочных резисторов дополнительного четвертого канала измерения угловой скорости по второй измерительной оси второго гироскопа; у седьмого мультиплексора к первому, второму и третьему входам подключены соответственно третий, четвертый и пятый терморезисторы, установленные соответственно в первом, втором и третьем акселерометрах; к четвертому и пятому входам подключены соответственно первый и второй терморезисторы, установленные соответственно в первом и втором гироскопах, к шестому входу подключен выход первого сдвоенного ключа, к седьмому входу подключен общий провод, к восьмому входу подключен шестой терморезистор, расположенный в устройстве преобразования аналоговых сигналов в цифровой код, терморезисторы выполнены как термосопротивления с отрицательным температурным коэффициентом сопротивления и с кратностью изменения сопротивления не менее 1000 в диапазоне рабочих температур окружающей среды; каждый из первого по шестой аналого-цифровых преобразователей первого типа содержит первый аналоговый интегратор на операционном усилителе, пороговое устройство, первый коммутатор, первый D-триггер, первое и второе логические устройства И, реверсивный счетчик с выходом в параллельном 16-разрядном двоичном коде, первый буферный регистр с выходом в параллельном 16-разрядном дополнительном двоичном коде, устройство управления, инверсный вход первого аналогового интегратора соединен с выходом одного из соответствующих первого, второго, третьего, четвертого, пятого и шестого мультиплексоров и с выходом первого коммутатора, к выходу первого аналогового интегратора подключен первый вход порогового устройства, ко второму входу которого подключен выход формирователя пилообразного напряжения, выход порогового устройства подключен ко входу D первого D-триггера, к выходу третьего делителя частоты на 2 базового делителя частоты источника специальных сигналов подключены вход С первого D-триггера и вход четвертого инвертора, выход которого подключен к первым входам первого логического устройства 2И-НЕ и второго логического устройства 2И-НЕ, инверсный выход первого D-триггера подключен ко входу управления первого коммутатора, второму входу второго логического устройства 2И-НЕ и ко входу пятого инвертора, выход которого соединен со вторым входом первого логического устройства 2И-НЕ, выход первого логического устройства 2И-НЕ подключен к первому входу устройства управления, ко второму входу которого подключен выход второго логического устройства 2И-НЕ, первый выход устройства управления подключен к суммирующему входу реверсивного счетчика, к вычитающему входу которого подключен второй выход устройства управления, выход реверсивного счетчика соединен шестнадцатипроводной линией с входом данных первого буферного регистра, ко входу С разрешения записи которого подключен третий выход устройства управления, а ко входу чтения подключен выход дешифратора чтения, к четвертому выходу устройства управления подключен вход обнуления реверсивного счетчика, к первому входу первого коммутатора подключен выход первого повторителя, ко второму входу первого коммутатора подключен выход первого инвертора; к первым входам первых коммутаторов в первом и втором каналах измерения линейного ускорения подключен выход первого повторителя; ко вторым входам этих же первых коммутаторов подключен выход первого инвертора, к первым входам первых коммутаторов в третьем канале измерения линейного ускорения и во втором канале измерения угловой скорости подключен выход второго повторителя, ко вторым входам этих же первых коммутаторов подключен выход второго инвертора, к первым входам первых коммутаторов в первом, третьем и четвертом каналах измерения угловой скорости подключен выход третьего повторителя, ко вторым входам этих же первых коммутаторов подключен выход третьего инвертора; устройство управления содержит шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый и тринадцатый инверторы, второй, третий, четвертый, пятый, шестой, седьмой и восьмой D-триггеры, третье, четвертое и пятое логические устройства 2И-НЕ, логическое устройство И, делитель частоты на 4, ко входу делителя частоты на 4 подключен выход делителя частоты на 120 базового делителя частоты источника специальных сигналов, ко входу шестого инвертора (первый вход устройства управления) подключен выход первого логического устройства 2И-НЕ, к выходу шестого инвертора подключен вход D второго D-триггера, ко входу С которого, а также к входам С третьего D-триггера и восьмого D-триггера, ко входу восьмого инвертора подключен выход первого делителя частоты на 2 базового делителя частоты, ко входу седьмого инвертора (второй вход устройства управления) подсоединен выход второго логического устройства 2И-НЕ, ко входу С четвертого D-триггера подключен второй выход («Цикл» 2») с делителя частоты на 20 базового делителя частоты, ко входам логического устройства И подключены выход четвертого D-триггера и инверсные выходы второго и третьего D-триггеров, ко входам С пятого, шестого, седьмого D-триггеров подключен выход восьмого инвертора, прямой выход второго D-триггера подсоединен к первому входу третьего логического устройства 2И-НЕ и ко входу D пятого D-триггера, инверсный выход которого подключен ко второму входу третьего логического устройства 2И-НЕ, прямой выход третьего D-триггера подсоединен к первому входу четвертого логического устройства 2И-НЕ и ко входу D седьмого D-триггера, инверсный выход которого подключен ко второму входу четвертого логического устройства 2И-НЕ, выход логического устройства И подключен ко входу D шестого D-триггера, выход которого соединен со входом D восьмого D-триггера и с первым входом пятого логического устройства 2И-НЕ, инверсный выход восьмого D-триггера подключен ко второму входу пятого логического устройства 2И-НЕ, выход которого подключен ко входу R четвертого D-триггера и ко входу девятого инвертора, выход девятого инвертора подключен ко входу десятого инвертора, выход которого соединен с входом одиннадцатого инвертора, выход одиннадцатого инвертора соединен со входом двенадцатого инвертора, выход которого подключен ко входу тринадцатого инвертора, выход третьего логического устройства 2И-НЕ (первый выход устройства управления) предназначен для подключения к суммирующему входу реверсивного счетчика аналого-цифрового преобразователя первого типа, выход четвертого логического устройства 2И-НЕ (второй выход устройства управления) предназначен для подключения к вычитающему входу реверсивного счетчика, выход девятого инвертора (третий выход устройства управления) предназначен для подключения ко входу разрешения записи первого буферного регистра, выход тринадцатого инвертора (четвертый выход устройства управления) предназначен для подключения ко входу обнуления реверсивного счетчика, выход делителя частоты на 4 (пятый выход устройства управления) предназначен для подключения ко входу формирователя пилообразного напряжения; формирователь пилообразного напряжения содержит четырнадцатый инвертор, второй коммутатор, второй аналоговый интегратор на операционном усилителе, ко входу четырнадцатого инвертора и к одному управляющему входу второго коммутатора подключен пятый выход устройства управления, ко второму управляющему входу второго коммутатора подключен выход четырнадцатого инвертора, к двум входам D второго коммутатора подсоединены выводы положительного и отрицательного потенциалов источника вторичного питания постоянного тока, к выходу второго коммутатора подключен вход второго аналогового интегратора, выход которого подключен ко входу аналого-цифрового преобразователя первого типа; к выходу седьмого мультиплексора подключен выход источника тока и вход аналого-цифрового преобразователя второго типа, содержащего третий аналоговый интегратор на операционном усилителе, компаратор, однополупериодный вибратор, второй ключ, устройство управления, счетчик, второй буферный регистр, третий стабилизатор напряжения, второй сдвоенный ключ, инверсный вход третьего аналогового интегратора подключен к выходу седьмого мультиплексора, к выходу третьего аналогового интегратора подключены инверсный вход компаратора и первый выход второго сдвоенного ключа, второй выход которого подключен ко входу третьего аналогового интегратора, выход компаратора подключен ко входу однополупериодного вибратора, выход которого подключен ко входу второго ключа и к управляющему входу второго сдвоенного ключа, выход второго ключа подключен к первому входу устройства управления, к первому выходу которого подключен вход счетчика, к выходу счетчика подключен вход второго буферного регистра, второй вход устройства управления подключен к выводу положительного потенциала источника вторичного питания постоянного тока, выход третьего стабилизатора напряжения подключен на вход второго сдвоенного ключа, ко входу С разрешения записи буферного регистра подключен третий выход устройства управления, ко входу R сброса счетчика подключен четвертый выход устройства управления; выходы первых буферных регистров аналого-цифровых преобразователя первого типа и второго буферного регистра аналого-цифрового преобразователя второго типа подключены к шине, которая соединена с входом шинного формирователя; входы дешифратора выбора чтения, дешифратора чтения и дешифратора записи соединены с шиной выхода буфера адреса центрального вычислительного устройства, входы дешифратора записи и дешифратора выбора чтения соединены с шиной выхода буфера команд центрального вычислительного устройства, шинный формирователь и входы данных регистра управления соединены с шиной выхода буфера данных центрального вычислительного устройства, выход дешифратора записи подключен к тактовому входу регистра управления, одни выходы которого подключены ко входу дешифратора управления, три выхода подключены к входам селекции седьмого мультиплексора, еще один выход подключен к управляющему входу первого ключа источника тока, первый, второй и третий выходы дешифратора управления подключены соответственно к первому, второму и третьему входам селекции с первого по шестой мультиплексоров, четвертый выход дешифратора управления подключен к четвертому входу селекции шестого мультиплексора, выход дешифратора выбора чтения подключен ко входу разрешения чтения шинного формирователя и ко входу дешифратора чтения, к выходу которого подключены входы разрешения чтения первого и второго буферных регистров аналого-цифровых преобразователей первого и второго типов; источник вторичного питания постоянного тока содержит фильтр радиопомех, транзистор, первый и второй диоды, электромагнитное реле поляризованного типа, первый, второй и третий конденсаторы, первый, второй, третий и четвертый резисторы, батарею буферных конденсаторов, первый, второй, третий и четвертый преобразователи напряжения; фильтр радиопомех содержит первый и второй индуктивные элементы с первой и второй обмотками, четвертый, пятый и шестой конденсаторы, первый вывод четвертого конденсатора подключен к выводу положительного потенциала внешнего источника питания постоянного тока и к первому выводу первой обмотки первого индуктивного элемента, первый вывод пятого конденсатора подсоединен к выводу нулевого потенциала внешнего источника питания постоянного тока и к первому выводу второй обмотки первого индуктивного элемента, вторые выводы четвертого и пятого конденсаторов подключены к корпусу преобразователя инерциальной информации, к первому выводу шестого конденсатора подсоединены второй вывод первой обмотки первого индуктивного элемента и первый вывод первой обмотки второго индуктивного элемента, ко второму выводу шестого конденсатора подключены второй вывод второй обмотки первого индуктивного элемента и первый вывод второй обмотки второго индуктивного элемента, ко второму выводу первой обмотки второго индуктивного элемента подключены катод первого диода, анод второго диода, первые выводы первого резистора, первого и второго конденсаторов, входы положительного потенциала первого, второго и третьего преобразователей напряжения, ко второму выводу второй обмотки второго индуктивного элемента подключены анод первого диода, второй вывод первого конденсатора, первый вывод второго резистора, входы нулевого потенциала первого, второго, третьего и четвертого преобразователей напряжения, один вывод батареи буферных конденсаторов; вторые выводы второго конденсатора и первого резистора подсоединены к первому выводу обмотки управления электромагнитного реле, ко второму выводу которой подключен второй вывод второго резистора, к базе транзистора подключены первые выводы третьего конденсатора, третьего и четвертого резисторов, эмиттер транзистора подключен ко второму выводу третьего конденсатора и к выходу нулевого потенциала первого преобразователя напряжения, к коллектору транзистора подключен первый вывод обмотки обратного переключения электромагнитного реле, второй вывод которой подключен к выходу положительного потенциала первого преобразователя напряжения, размыкающий контакт электромагнитного реле подключен между входами нулевого потенциала и соединенными вместе входами управления включением первого, второго, третьего и четвертого преобразователей напряжения, второй вывод батареи буферных конденсаторов и катод второго диода подключены ко входу положительного потенциала четвертого преобразователя напряжения, второй вывод третьего резистора подключен к одному из выходов регистра выдачи разовых команд центрального вычислительного устройства, второй вывод четвертого резистора подключен к выходу блокировки отключения, подсоединенному к технологическому разъему, ко входам положительного и нулевого потенциалов четвертого преобразователя напряжения подключены цепи питания постоянного тока центрального вычислительного устройства; в каждом преобразователе напряжения первая вторичная обмотка импульсного трансформатора выполнена со средней точкой, источник служебного электропитания выполнен введением в импульсный трансформатор второй вторичной обмотки, введением первого дополнительного диодного выпрямителя, подключенного ко второй вторичной обмотке импульсного трансформатора, подключением к первому дополнительному диодному выпрямителю входа стабилизатора напряжения; в каждом преобразователе напряжения широтно-импульсный модулятор выполнен в одном кристалле в составе генератора пилообразного напряжения, первого дифференциального усилителя и компаратора, в преобразователь напряжения введены полевой транзистор, второй дифференциальный усилитель, входной LC-фильтр, RC-цепь, первый вывод резистора которой подключен к выходу входного LC-фильтра, первый и второй резистивные делители, второй дополнительный диодный выпрямитель, в устройство обратной связи по напряжению введены транзисторная оптопара, третий резистивный делитель, источник опорного напряжения, третий дифференциальный усилитель, ко входу положительного потенциала от внешнего источника питания постоянного тока подключен вход входного LC-фильтра, ко входу стабилизатора напряжения подключена точка соединения второго вывода резистора RC-цепи с конденсатором RC-цепи, к выходу входного LC-фильтра подключен первый вывод первичной обмотки импульсного трансформатора, ко второму выводу которой подключен первый вывод первичной обмотки измерительного трансформатора, второй вывод первичной обмотки измерительного трансформатора подключен к стоку полевого транзистора, к выходу стабилизатора напряжения подключены цепи питания генератора пилообразного напряжения, первого, второго и третьего дифференциальных усилителей, компаратора, транзисторной оптопары, первый и второй резистивные делители, выход первого резистивного делителя подключен к прямому входу первого дифференциального усилителя, выход генератора пилообразного напряжения подключен к прямому входу компаратора, к инверсному входу которого подключен выход первого дифференциального усилителя, выход компаратора соединен с входом ключевого усилителя, к одному выводу вторичной обмотки измерительного трансформатора подключен анод второго дополнительного диодного выпрямителя, к катоду которого подключены прямые входы компаратора и второго дифференциального усилителя; выходы положительного и нулевого потенциалов преобразователя напряжения подключены к третьему резистивному делителю, к выходу которого подключен прямой вход третьего дифференциального усилителя, к инверсному входу третьего дифференциального усилителя подключен выход источника опорного напряжения, к выходу третьего дифференциального усилителя подключен вход транзисторной оптопары, выход которой соединен с инверсным входом первого дифференциального усилителя, к затвору полевого транзистора подключен выход ключевого усилителя, к инверсному входу второго дифференциального усилителя подключен выход второго резистивного делителя, выход второго дифференциального усилителя подсоединен к прямому входу компаратора, к неподвижному контакту размыкающего контакта электромагнитного реле в источнике вторичного питания постоянного тока подключены соединенные последовательно третий дополнительный диодный выпрямитель и балластный резистор, который также подключен к выходу промежуточного каскада усиления первого дифференциального усилителя, коэффициенты трансформации первых вторичных обмоток импульсных трансформаторов, полярность подключении первого и второго диодных выпрямителей выполнены такими, что относительно выхода нулевого потенциала на первом выходе второго преобразователя напряжения образован первый положительный потенциал, на втором выходе образован первый отрицательный потенциал, модуль которого равен величине первого положительного потенциала, на первом выходе первого преобразователя напряжения образован второй положительный потенциал, больший первого потенциала, на втором выходе первого преобразователя напряжения образован второй отрицательный потенциал, модуль которого равен величине второго положительного потенциала, на первом выходе третьего преобразователя напряжения образован третий положительный потенциал, больший второго положительного потенциала, на втором выходе третьего преобразователя напряжения образован третий отрицательный потенциал, модуль которого равен величине третьего положительною потенциала, на выходе четвертого преобразователя напряжения образован четвертый положительный потенциал величиной, соответствующей высокому уровню логики ТТЛ; выход второго положительного потенциала второго преобразователя напряжения подключен к замыкающему контакту первого переключающего контакта электромагнитного реле, общего для первого и второго источников вторичного питания переменного тока, выход положительного потенциала второго преобразователя напряжения подключен к размыкающему контакту первого переключающего контакта электромагнитного реле, выход отрицательного потенциала третьего преобразователя напряжения подключен к замыкающему контакту второго переключающею контакта электромагнитного реле, выход отрицательного потенциала второго преобразователя напряжения подключен к размыкающему контакту второго переключающего контакта электромагнитного реле, в устройстве аппаратного контроля источника вторичного питания постоянного тока выходы положительного потенциала первого, второго и третьего преобразователей напряжения подключены к первым входам соответственно первого, второго и третьего компараторов, ко вторым входам которых подсоединен выход положительного потенциала четвертого преобразователя напряжения, выходы первого, второго и третьего компараторов соединены вместе и подключены к одному из входов регистра приема разовых команд центрального вычислительного устройства, каждый первый, второй, третий и четвертый преобразователи напряжения выполнены в плоском корпусе из алюминиевого сплава с двухсторонней печатной платой с бескорпусными пассивными элементами, элементы платы загерметизированы посредством компаунда; фильтр радиопомех выполнен на печатной плате и его элементы помещены в экран из пермаллоя; преобразователь инерциальной информации выполнен в корпусе с двумя отсеками, внешняя вертикальная стенка корпуса, примыкающая к первому отсеку, выполнена ребристой, основание с гироскопами и акселерометрами установлено в первом отсеке на нижней плите корпуса на четырех крепежных выступах и зафиксировано посредством двух штифтов в основании и двух отверстий на нижней плите корпуса, в первом отсеке также установлены рядом расположенные выходные соединители и фильтр радиопомех.

| Attitude and Heading Reference System | |||

| Горный компас | 0 |

|

SU81A1 |

| RU 2058534 C1, 20.04.1996 | |||

| СПОСОБ КОМПЛЕКСНЫХ ИСПЫТАНИЙ БЕСПЛАТФОРМЕННЫХ ИНЕРЦИАЛЬНЫХ ИЗМЕРИТЕЛЬНЫХ БЛОКОВ НА ОСНОВЕ МИКРОМЕХАНИЧЕСКИХ ГИРОСКОПОВ И АКСЕЛЕРОМЕТРОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2256880C1 |

| US 4914598 A, 03.04.1990 | |||

| US 4303978 A, 01.12.1981. | |||

Авторы

Даты

2008-05-27—Публикация

2006-05-24—Подача