3, Устройство по n.l, о т л и ч аю щ ее ся тем, что блок выбора основного сигнала состоит из последовательно соединенных триггера, элемента И, элемента памяти и компаратора, второй вход и выход которого соединены соответственно с вторым входом элемента памяти и с входом триггера, при этом вход элемента па мяти является входом блока выбора основного сигнала, выходом которого являетйя выход элемента И.

4. Устройство ПОП.1, отличающееся тем, что накопитель разнесенных сигналов .состоит из двух оптронов и двух интеграторов, входы которых соединены с одними выводами резисторов соответствующих оптронов, аноды светодиодов которлх объединены, при этом выходы интеграторов являются выходами накопителя разнесенных сигналов, входами которого являются аноды светодиодов оптронов и другие выводы резисторов оптронов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1051737A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Устройство для детектирования фазоманипулированных сигналов | 1978 |

|

SU786047A1 |

| Способ регистрации сейсмических сигналов | 1984 |

|

SU1312501A1 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1999 |

|

RU2140090C1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ | 2004 |

|

RU2267230C1 |

| Устройство синхронизации м-последовательности с инверсной модуляцией | 1974 |

|

SU702534A1 |

| ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВ С МНОГОПОЗИЦИОННОЙ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2021 |

|

RU2776968C1 |

| СИСТЕМА ВЫСОКОСКОРОСТНОЙ ДЕКАМЕТРОВОЙ РАДИОСВЯЗИ | 2014 |

|

RU2608554C2 |

1. УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ, содержащее блок синхронизации и управления, выходи которого подключены к управляющим входам блока,вычисления разности фаз и многоканального коррелятора, выходы которого соедиН(ены с однит входами блока вычисления разности фаз, выходы которого под- . -ключены к входам блока подстройки фаз, выход которого соединен с входом реверсивного счетчика, выходы которого подключены к входам цифрового блока памяти, выходы которого соединены с другими входами блока вычисления разности фаз, выходы которого подкгаочены к входам декодера разнесенных сигналов, отличающееся тем, что, с целью повышения помехоус-тойчивости при когерентном приеме, введены измеритель разнесенных сигналов, коммутатор, компаратор, накопитатель разнесенных сигналов, декодер суммарного сигнала, логический сумматор, переключающий блок, инвертор, арифметический сумматор и последовательно соединенные блок выбора основного сигнала и запоминающий бло1 выходы которого подключены к одним входам логического сумматора, выходы которого соединены с одними входакш переключающего блока и арифметического сумматора и с входом инвертора, выход которого подключен к другому входу переключающего блока, выход которого соединен с другим входом арифметического сумматора, соответст вующие входы которого соединены с дополнительными выходами реверсивного счетчика и с входами ксялмутатора, выходы которого подключены к дополнительным входам цифрового блока памяти, при этом выходы блока вычисления- разности фаз подключены к входям накопителя разнесенных сигналов и измерителя разнесенных сигИалов, выход которого подключен к входам блока выбора основного сигнала и компаратора, выход которого сое динен .с соответствующим входом коммутатора, причем выходы накопителя % разнесенных сигналов подключены к входам декодера суммарного сигнала а выход измерителя разнесенных сигналов соединен с соответствующим вхо дом накопителя разнесенных сигналов, причем шлходы декодера разнесенных сигналов соединены с соответствующими входами запоминающего блока и логического сумматора. 2. Устройство по п.1, о т л и- Г) ч а ю щ е е с я тем, что измери тель разнесенных сигналов состоит э из трех выпрямителей, вычитающего блока, операционного усилителя, инРО вертора, трех резисторов, диода и блока обратных связей, KOTojart соединен с операционным усилителем, :о вход которого соединен с одними выводами резисторов и анодом диода, катод которого соединен с другим выводом первого резистора и с выходом инвертора, к входу которого подключен выход первого выпрямителя, вход которого соединен с выходом вычитающего блока, входы которого соединены с другими выводами второго и третьего резистору и с выходами второго и третьего выпрямителей, входы которых являются входами измерителя разнесенных сигналов,Выходом которого является выход операционного усилителя.

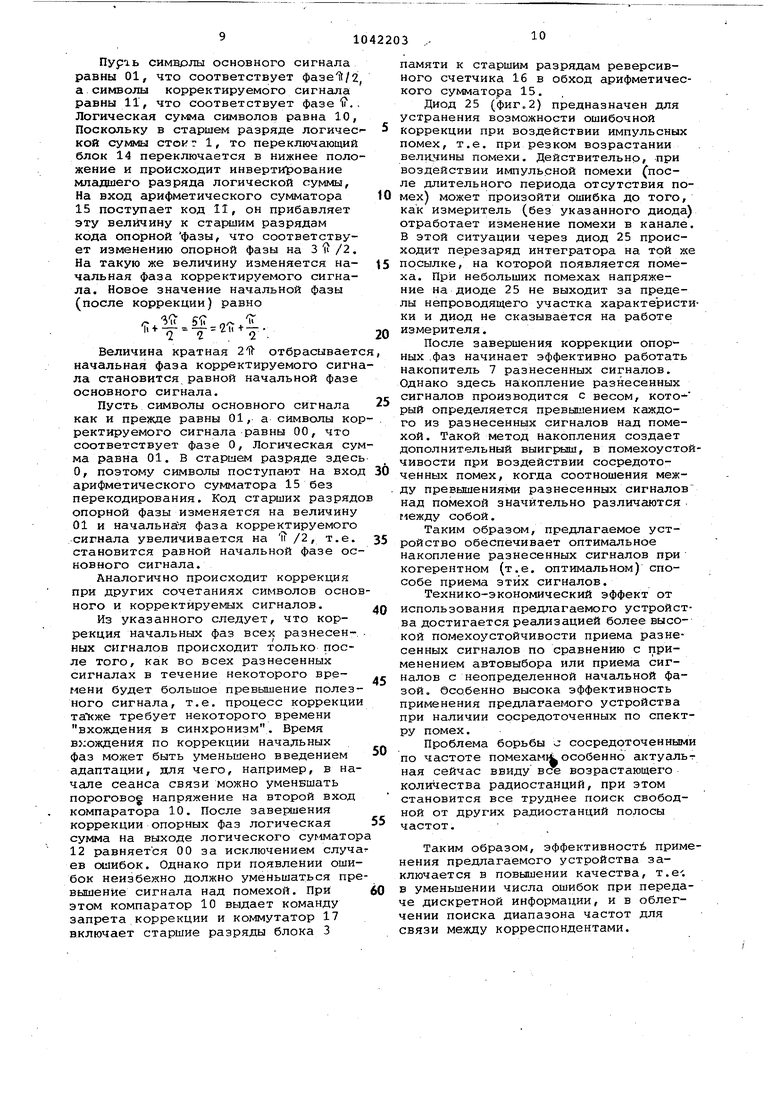

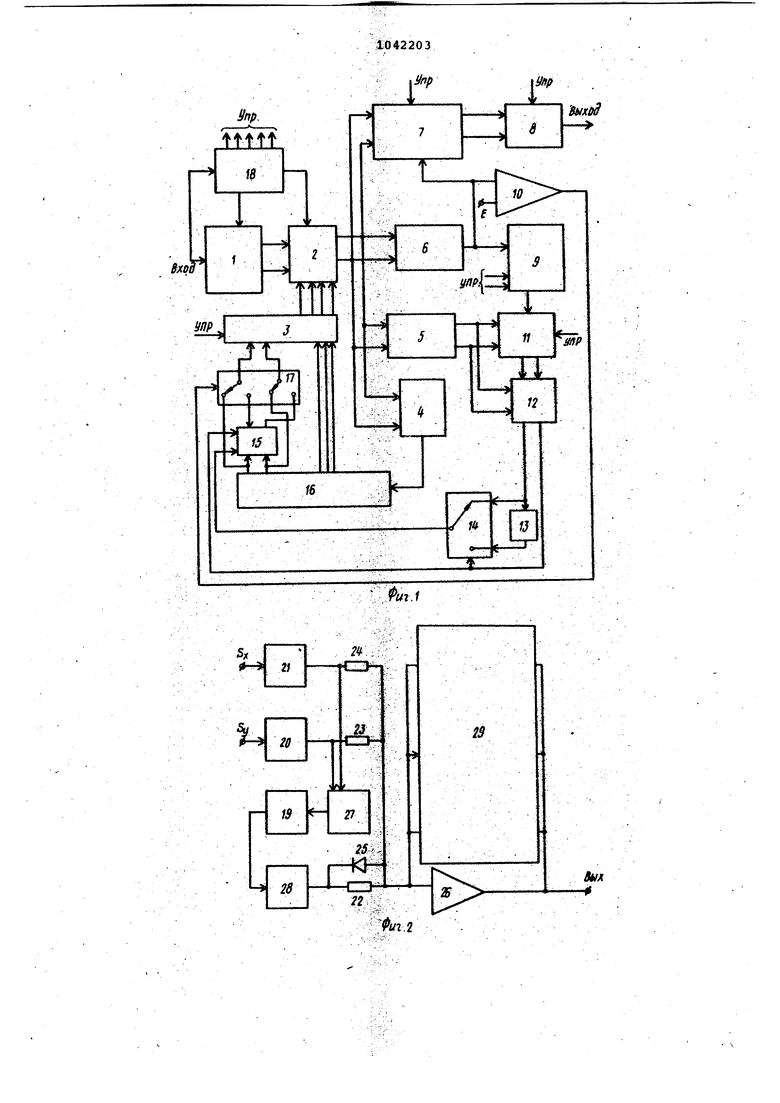

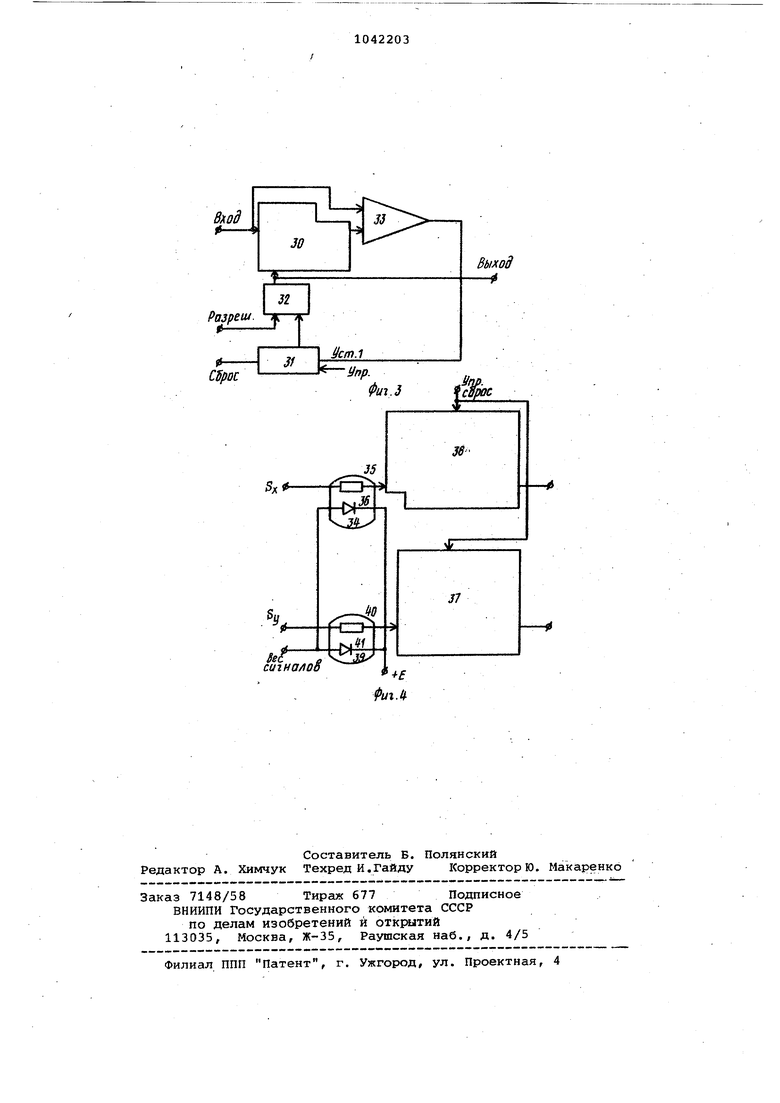

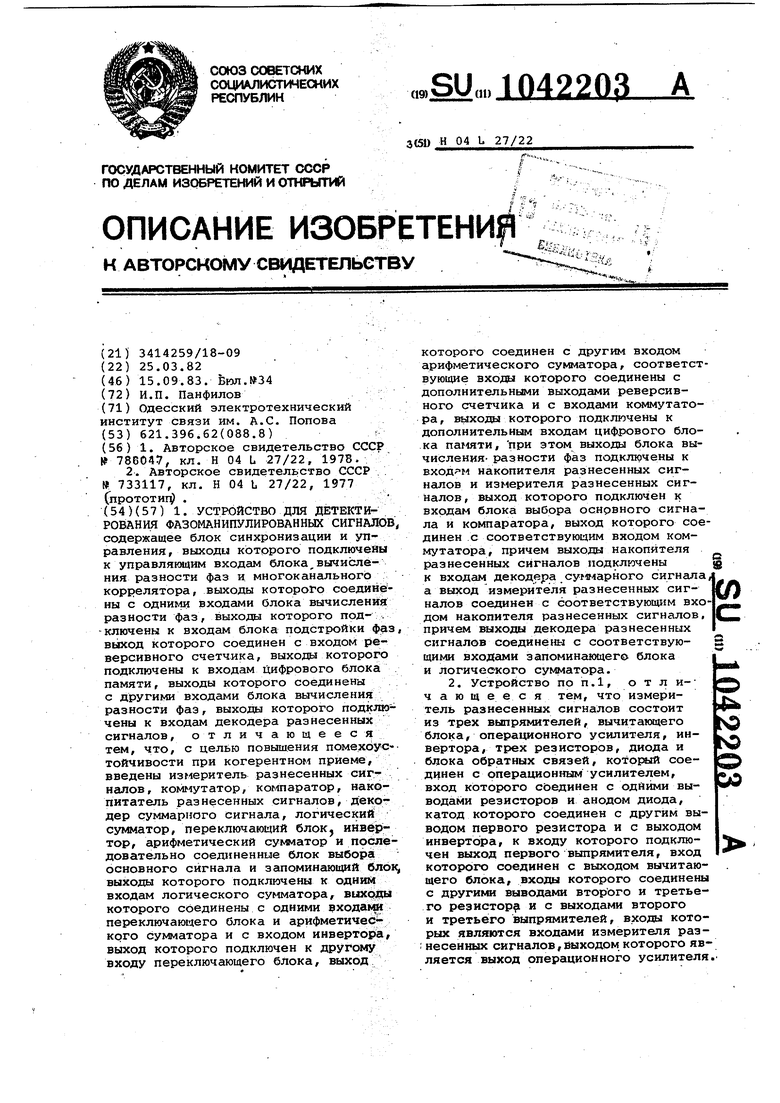

Изобретение относится к технике передачи дискретных сообщений по каналоц связи. Известно устройство для. детектирования фазоманипулированных сигналов, работа которого основана на при менении когеретного способа детектирования сигналов, содержащее многоканальный коррелятор, декодер, два блока вычисления разности фаз, cyivwa тор, анализатор настройки, накопител и постоянные запоминакяцие элементы Недостатком известного устройств является низкая достоверность из-за неопределенности опорного колебания Наиболее близким к изобретению п техническому решению является устро ство для детектирования фазоманипул рованных сигналов, содержащее блок синхронизации и управления, выхода которого подключены к управляющим вх дам блока вычисления разности фаз и многоканального коррелятора, выходы которого соединены с одними входами блока вычисления разности фаз, выходы которого подключены к входам блока подстройки фаз, выход которого соединен с входом реверсивного счетчика выходы которого подключены к входам цифрового блока памяти, выходы которого соединены с другими входами блока вычисления разности фаз, выходы которого подключены к входам декодера разнесенных сигналов 2 , Однако это устройство имеет низкую помехоустойчивость при когерентном приеме. Цель изобретения - повышение помехоустойчивости при когерентнс приеме. Цель достигается тем, что в устройство для детектирования фазоманип лированных сигналов, содержавшее блок синхронизации и управления, выхода которого подллючены к равляюиим входам блока вычисления разности фаз и многоканального коррелятора, выходы которого соединены с одними входами блока вычисления разности фаз,, выходы которого подключены к входам блока подстройки фаз, выход которого соединен с входом реверсивного счетчика, выходы которого подключены к входам цифрового блока памяти, выходы которого соединены с другими входами блока вычисления разности фаз, выходы которого подключены к входам декодера разнесенных сигналов, введены измеритель разнесенных сигналов, коммутатор, компаратор, накопитель разнесенных сигналов, декодер суммарного сигнала, логический сукматор, переключакя1дай блок, инвертор, арифметический сумматор и последовательно соединенные блок выбора основного сигнала и запоминающий блок, выходы которого подключены к одним входам логического сумматора, выходы которого соединены с одними входсЦ и переключакяцего блока и арифметического сумматора и с входс 1 инвертора, выход которого подключен к другому входу переключающего блока, выход которого соединен с другим входом арифметического сукматора, соответствующие входы которого соединены с дополнительными выходами реверсивного счетчика и с входами коммутатора, выходы которого подключены к дополнительным входам цифрового блока памяти, при этом 1быходы блока вычисления разности фаз подключены к входам Накопителя размеренных сигналов и измерителя разнесенн1дх сигналов, выход которого подключен к входам блока выбора основного сигнала и компаратора, выход котсфого соадагнен с соответстВУЮЩШ4 входом коммутатора, причем выходы накопителя разнесенных сигналов подключены к входам декодера суммарного сигнала, а выход измерителя разнесенных сигналов соединен с соответствуювдам входом накопителя разнесенных Сигналов, причем выходы декодера разнесенных сигналов соединены с соотв втствующими входами запоминающего блока и логического сумматора. Измеритель разнесенных сигналов состоит из трех выпрямителей, вычитающего блока, ,операционного усилителя, инвертора, трех резисторов, диода и блока обратных связей, который соединен с операционным усилителем, вход которого соединен с одними выводами резисторов и анодом диода, катод которого соединен с другим выводом первого резистора и с выходом инвертора, к входу которого подключен ВЫХОД первого вы- прямителя, вход которого соединен с выходом вычитающего блока, входы которого соединены с другими выводами второго и третьего резисторов и с выходами второго и третьего выпрямителей, входы которых являются входами измерителя разнесенных сигналов, выходом которого является выход операционного усилителя. Бяок выбора основного сигнала состоит из последовательно соединенных триггера, элемента И, злемента памяти и компаратора, второй вход и выход которого соединены соответст венно с вторым входом элемента памяг ти и с входом триггера, при этом вход элемента памяти является входом блока выбора основного сигнала, вы-. ходом которого является выход элемен та И. ,., , . Накопитель разнесенных сигналов состоит из двух оптронов и двух интеграторов, входы которых соедине с одними выводами резисторов соотве ствующих оптронов, аноды светодиодов которых объединены, при этом вы ходы интеграторов являются выходами накопителя разн сенных сигналов, вх дами которых являются аноды светрдиодов onTpioHOB и другие выводы рё зисторов оптронов. На фиг.1 представлена структурна электрическая схема предлагаемого устройства; на фиг.2 - измеритель разнесенных сигналов, вариант выпо ненияна фиг.3-блок выбора основно сигНсьИа, вариант вьшолнения «на фиГi накопитель разнесенных сигналов, . вариант выполнения. Устройство для детектирования фаэоманипу.лированных сигналов содер жит многоканальный коррелятор 1, бл 2 вычисления разности фаз, цифровой блок 3 памяти, блок 4 подстройки фа декодер 5 разнесенных сигналов, H3f меритель 6 разнесенных сигналов/на кОпитель 7 разнесенных сигналов, декодер 8 суммарного сигнала, блок выбора основного сигнала, компаратр JLO, запоминающий блок 11, логически сумматор 12, инвертор 13, переключающий блок 14, арифметический сумматор 15, реверсивный счетчик 16,, коммутатор 17, блок 18 синхронизации и управления. Измеритель разнесенных сигналоьсостоит из (фиг.2) первого, второго, и третьего выпрямителей 19-21 соответственно первого, второго, и третьего резисторов 22-24 соответственно, диода 25, операционного усилителя 26, вычитающего блока 27, инвертора 28 и блока 29 обратных связей. ; Блок выбора основного сигнала состоит из (фиг.З) элемента 30 памяти, триггера 31, элемента 32 И и компаратора 33. Накопитель разнесенных сигналов состоит из (фиг.4) первого оптрона 34, в состав которого входят резистор 35 и светодиод 36, двух интеграторов 37 и 38 и второго оптрона 39, в состав которого входят резистор 40 и светодиод 41. Устройство работает следующим образом. Сигнал, поступающий на один или несколько входов устройства состоит из набора разнесенных сигналов. Эти сигналы могут состоять из нескольких групп разнесенных канальных сигналов, причем разнесение может быть выполнено как по частоте (передачаи прием одних и тех же сигналов на разных частотах) , так и по антеннам (прием одних и тех же сигналов 1яа разные, разнесенные в пространстве антенны) . Здесь рассматривается работа устройства применительно к приему только одной группы разнесенных по частоте сигналов. Обработку нескольких групп (набора) разнесенных сигналов производят либо набором аналогичных устройств, либо ограничиваются использованием набора многоканальных корреляторов, а дальнейшую обработку производят путем разделения во времени. Группа разнесенных по частоте канальных сигналов обрабатывается в. многоканальном корреляторе 1 путем вычисления корреляции принимаемых сигналов с опорными колебаниями приемника (не показан), фаза которых не связана с фазами опорных колебаний передатчика (не показан) . Напряжения X и Y, которые формируются на выходах многоканального коррелятора 1, представляют собой проекции канальных сигналов на опорные колебания приемника. Для получения напряжений, соответствующих проекциям канальных сигналов на опорные колебания передатчика S и 5,,в блоке2 вычисления разности фаз производится пересчет проекций по алгоритму. B Xcosif + j 5 Xsinqi-4co5Cf, где tf - сдвиг фазы между опорными колебаниями передатчика и приемника. Значения Cos ср (f определяются в результате подстройки, причем подбираются аргументы if (опорные фазы так, чтобы абсолютные величины 5 и &у были равны междУ собой. Сложение разнесенных сигналов можно производить только после устране ния неопределенности значений опорных фаз. Для этого сопоставляются между собой пары символов (дибиты), полученные в результате декодирования разнесенных сигналов и производи ся коррекция опорных фаз так, чтобы устранить взаимную неопределен ность начальных фаз канальных сигналов .

Устранение взаимной нерпредгвленно ти позволит осуществить сложение ранесенных сигналов при когерентном способе приема и тем самым повысить помехоустойчивость.

Для устранения взаимной неопределенности начальных фаз разнесенных сигналов в предлагаемом устройстве выявляется из всех разнесенных сигналов сигнал, имеющий наибольшее превьшение над помехой (основной сигнал). Для этого производится измерение превьадения полезного сигнала над помехой для всех разнесенных сигналов. Измеренные значения превьшенйй используются прежде всего для ыявления основного Из разнесенных сигналов и для формирования команды разрешения коррекции, причем коррекция начальной фазы каждого из разнесенных сигналов производится только в том случае, если измеренное значение превышения полезного . сигнала над помехой указывает на достаточно малую вероятность ошибки при декодировании. Кроме того, измерение значений превышения позволяет осуществить в предлагаемом устройстве взвешенное сложение разнесенных сигналов, обеспечивающее дополнительное увеличение помехоустойчивости при воздействии узкополосных помех.

Принцип работы измерителя разнесеных сигналов (принцип измерения превынения сигнала над помехой) основан на том (фиг.2), что после подстройки опорных фаз, абсолютные значения напряжения 5х и Sj равны между собой. Поэтому различие между абсолютными значениями этих Напряжений служат мерой помехи. За сигнал принимается cyNwa абсолютных величин этих напряжений. Такой метод дает смещенную оценку.

Расчеты показывают, что при отсутствии полезного сигнала, если на вхо де устройства присутствует только помеха, средйее значение суммы абсолютных значений S и 5j приблизительно в 4 раза больше среднего значения абсолютной величины их разности. Поэтому для получения несмещенной

оценки в измерителе производится вычитание из сую1ы 15к| и абсолютной величины учет еренйой разности I -/$ |

Абсолютные величины 5х и Sy формруются вторым и третьим выпрямителями 20 и 21, на входы которых значения BX и 5 поступаиот из блока вычисления разности фаз. Суммирование производится сумматором-усреднителем, выполненным на базе операционного усилителя 26, Величины первого и второго резисторов 23 и 24 равны между собой. Разность абсолютных величин 5ц и S формируется вычитаюгаим блоком 27. Затем в первом выпрямителе 19 формируется абсолютная величина разности, инвергтируется инвертором 28, и поступает на первый резистор 22. Величина этого резистора в 4 раза меньше равных между собой резисторов 23 и 24, Операционный усилитель 26 имеет блок 29 обратных связей, в котором накапливаются средние значения величин

1 1Чву|-4||б,Мб,1| ,

Из указанного ясно, что эти средни значения близки к нулю если полезного сигнала нет, а при наличии полезного сигнала, указанная величина тем больше, чем больше превышение сигнала над помехой.

Диод 25 служит для быстрого отслеживания импульсных помех.

Блок 9 выбора основного сигнала ,(фиг.3) предназначен для того, чтобы записать в запоминающий блок 11 (фин. символы того из разнесенных сигналов, у которого наибольшее превышение сигнала над помехой.

На вход блока 9 поочередно поступают напряжения выхода измерителя разнесенных сигналов, величины которых пропорциональны прёвьгиению разнесенных сигналов над помехой.

В начале интервала обработки первого из разнесенных сигналов триггер 31 импульсом от блок:а управления (не показан) на один из входов Установка единицы переводится в состояние 1 и подает разрешение на один из входов элемента 32 И. На второй вход этого элемента И подается импульс разрешения во время второй половины интервала обработки каждого из каналь,ных сигналов. Во время присутствия этоt-o разрешающего импульса формируется разрешающий импульс на выходе элемента 32 И, покоторому через элемент 30 памяти производится запись символов первого из разнесенных Сигналов в запоминающий блок 11. В конце ийтервала обработки триггер 31 импульсом по шине Сброс переводится в нулевое состояние.

Затем в начале обработки второго из разнесенных сигналов компаратор 33 производит сравнение превьшения

второго сигнала с превышением первогё сигнал, ранее записанном в элементе 30 памяти. Если превышение второго сигнала Ьольше превышения первого сигнала то разрешающее напряжение с выхода coмпapaтopa устанавливает триггер 31 в состояние 1. В этом случае дальнейший процесс аналогичен предыдущему. Если же превыиение второго сигнала меньше превышения первого тогда ксмипаратор 33 не выдает разрешения на перезапись ив элементе 30 памяти и запоминающем блоке 11 остаются параметры первого сигнала.

Нетрудно понять, что в конце цикла обработки всех разнесенных сигналов в запоминаклдем блоке записываются символы того из разнесенных сигналов, у которого наибольшее превышение полезного сигнала над помехой.

Накопитель разнесенных сигналов . (фиг,Ч) служит для взвешенного сложения разнесенных сигналов. Накопление сигналов производится р интеграторах 37 и 38. Интегрирующими резисторами служат резисторы 35 и 40 оптронов 34 и 39.: .

Перед началом каждого цикла накопления разнесенных сигналов производится сброс интеграторов,

Проекции разнесенных сигналов 5х и 5у подаются на входы оптронов 34 и 39 и накапливаются в интеграторах. i Ток заряда зависит как 6т входного сигнала, так и от резисторов оптронов Интервалы накопления каждого из разнесенных сигналов одинаковы, поэтому вес учета каждого из них пропорциоНсШен резистору оптрона, а . следовательно, определяется напряжением на входе, соединенном с анодами светодиодов 36 и 41 оптронов 34 и 39. Следует особо отметить,что если напряжение на входе оказывается меньше, чем напряжение источника соединенного с катодами светодиодов оптронов, тогда ток через светодиоды не протекает и этот сигнал из разнесенных сигналов не учитывается. Поэтому напряжение источника соединенного с катрдами светодиодов является порогом я азрешения учета каждого из разнесенных сигналов.

В общих принципах работы устройства показано, что на выходе блока вычисления разности фаз формируются проекции разнесенных сигналов в координатах передатчика с неопределенностью на1чальных фаз кратной/. Сложения разнесенных сигналов можно производить только после устранения взаимной неопределенности начальных фаз разнесенных сигналов, jinn этого вьщеляется основной сигнал, имеющий наибольшее превышение полезного сигнала над помехой, и затем устраняется неопределенность опорньрс

--s--

8

1042203

фаз всех других разнесенных сигналов относительно основного сигнала.

Для устранения этой неопределенности определяется логическая сумма символов основного сигнала и символов каждого из разнесенных сигналов (поразрядная суьма по модулю два) . Эта операция производится в логическом сумматоре 12 (фиг,1). Эта сумма перекодируется инвертором 13 и переключающим блоком 14 и поступает на соответствукяцие входы арифметического сук«атора 15, Он осуществляет прибавление в два старших разряда опорных фаз целых чисел (от О до 3), соответствующих разнице между опорными фазами основного сигнала и одного из разнесенных сигналов. Однако коррекция разрешается только в том случае если на данной посылке вероятность ошибки корректируемого разнесенного сигнала достаточно мала. Возможность коррекции контролируется коммутатором 17, подключающим к цифровому блоку 3 памяти старшие разряды реверсивного счетчика 16 либо непосредственно, либо через арифметический сумматор 15, Команда разрешения коррекции вырабатывается- компараторомЮ, который сравнивает .величину превышения полезного сигнала над nofiexon, сфорредрованной в измерителе разнесенных сигналов 6 с заданным порогом.

Процесс демодуляции каждой посылки разнесенных сигналов производится двумя циклами. При этом дважды за посылку из памяти многоканального коррелятора 1 сканируются и обрабатываются в блоке 2 проекции всех разнесенных сигналов.

На первом цикле производится декодирование всех разнесенных сигналов детектором 5. При этом измеритель 6 разнесенных сигналов выдает последовательно во времени значения превьииений полезного сигнала над помехой на вход блока 9. Блок 9 выбора основного сигнала разрешает запись символов разнесенных сигналов в запоминающий блок 11 в том случае если превыиение очередного из разнесенных сигналов над по техой выше, чем у всех ранее обработанных сигналов, В конце первого Цикла в запоминающем блоке, 11 записываются символы того ite разнесенных сигналов, у которого наибольшее превышение полезного сигнала над помехой. На первом цикле перезапись опорных фаз в цифровой блок 3 памяти запрещена, а накопитель 7 разнесенных сигналов находится в состоянии сброса, т,е. производится разряд интеграторов.

На втором цикле производится коррекция опорных фаз и накопление разнесенных сигнгшов. Пураь симврлы основного сигнала равны 01, что соответствует фаэей/2 а символы корректируемого сигнала равны 11, что соответствует фазе 1. , Логическая сумма символов равна 10, Поскольку в старшем разряде логичес кой суммы стой г 1, то переключающий блок 14 переключается в нижнее поло жение и происходит инверти ование младшего разряда логической суммы, На вход арифметического сумматора 15 поступает код 11, он прибавляет эту величину к старшим разрядам кода опорной фазы, что соответствует изменению опорной фазы на 3 ii /2. На такую же величину изменяется начальная фаза корректируемого сигнала. Новое значение начальной фазы (после коррекции) равно .f.. Величина кратная 2П отбрасываетс начальная фаза корректируемого сигн ла становится равной начальной фазе основного сигнала. Пусть символы основного сигнала как и прежде равны 01, а символы кор ректируемого сигнала равны 00, что соответствует фазе О, Логическая сум ма равна 01. В старшем разряде здесь О, поэтому символы поступают на вход арифметического сумматора 15 без перекодирования. Код старших разрядо опорной фазы изменяется на величину 01 и начальная фаза корректируемого сигнала увеличивается на ff /2, т.е. становится равной начальной фазе основного сигнала. Аналогично происходит коррекция при других сочетаниях символов основ ного и корректируемых сигналов. Из указанного следует, что коррекция начальных фаз всех разнесенных сигналов происходит только после того, как во всех разнесенных сигналах в течение некоторого времени будет большое превышение полезного сигнала, т.е. процесс коррекции таЧкже требует некоторого времени вхождения в синхронизм. Время вхождения по коррекции начальных фаз может быть уменьшено введением адаптации, для чего, например, в начале сеанса связи можно уменвшать noporoBog напряжение на второй вход компаратора 10. После эаверыения коррекции опорных фаз логическая сумма на выходе логического cyr-iMaTop 12 равняется 00 за исключением случа ев ошибок. Однако при появлении ошибок неизбежно должно уменьшаться пре вьЕиенйе сигнала над помехой. При этом компаратор 10 выдает команду запрета коррекции и коммутатор 17 включает старшие разряды блока 3 памяти к старшим разрядам реверсивного счетчика 16 в обход арифметического сумматора 15. Диод 25 (фиг.2) предназначен для устранения возможности ошибочной коррекции при воздействии импульсных помех, т.е. при резком возрастании величины помехи. Действительно, при воздействии импульсной помехи (после длительного периода отсутствия помех) может произойти ошибка до того, как измеритель (без указанного диода) отработает изменение помехи в канале. В этой ситуации через диод 25 происходит перезаряд интегратора на той же посылке, на которой появляется помеха. При небольших помехах напряжение на диоде 25 не выходит за пределы непроводящего участка характеристики и диод не сказывается на работе измерителя. После завершения коррекции опорных ,фаз начинает эффективно работать накопитель 7 разнесенных сигналов. Однако здесь накопление разнесенных сигналов производится с весом, который определяется превышением каждого из разнесенных сигналов над помехой. Такой метод накопления создает дополнительный , в помехоустойчивости при воздействии сосредоточенных помех, когда соотношения между превышениями разнесенных сигналов над помехой значительно различаются между собой. Таким образом, предлагаемое устройство обеспечивает оптимальное накопление разнесенных сигналов при когерентном (т.е. оптимальном) способе приема этих сигналов. Технико-экономический эффект от использования предлагаемого устройства достигается реализацией более высокой помехоустойчивости приема разнесенных сигналов по сравнению с применением автовыбора или приема сигналов с неопределенной начальной фазой. Особенно высока эффективность применения предлагаемого устройства при наличии сосредоточенных по спектру помех. Проблема борьбы о сосредоточенными по частоте noMexanii особенно актуальт ная сейчас ввиду все возрастающего количества радиостанций, при этом становится все труднее поиск свободной от других радиостанций полосы частот. Таким образом, эффективности применения предлагаемого устройства заключается в повышении качества, т.е . в уменьшении числа ошибок при передаче дискретной информации, и в облегчении поиска диапазона частот для связи между корреспондентами.

Упр.

ХОВ

ШЛ

сигналов

Выход

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1978 |

|

SU786047A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для детектирования фазоманипулированных сигналов | 1977 |

|

SU733117A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-09-15—Публикация

1982-03-25—Подача