пятой логической -схемы И - выходом для пониже П1я ча стоты, а выход .третьей логической схемы И - выходом для включения .автомата генератора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматический синхронизатор с постоянным временем опережения | 1980 |

|

SU888270A2 |

| Устройство для автоматической синхронизации с постоянным временем опережения | 1979 |

|

SU855855A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1981 |

|

SU995200A1 |

| Автоматический синхронизатор с постоянным временем опережения | 1979 |

|

SU777772A1 |

| Автоматический синхронизатор с постоянным углом опережения | 1982 |

|

SU1065957A2 |

| Автоматический синхронизатор с постоянным углом опережения | 1981 |

|

SU961045A2 |

| Устройство для подгонки частоты одного источника напряжения к частоте другого источника напряжения | 1981 |

|

SU991551A1 |

| Автоматический синхронизатор | 1987 |

|

SU1444916A2 |

| Устройство для подгонки частоты одного источника напряжения к частоте другого источника напряжения | 1983 |

|

SU1141509A2 |

| Устройство для измерения фазового дрожания | 1987 |

|

SU1469556A1 |

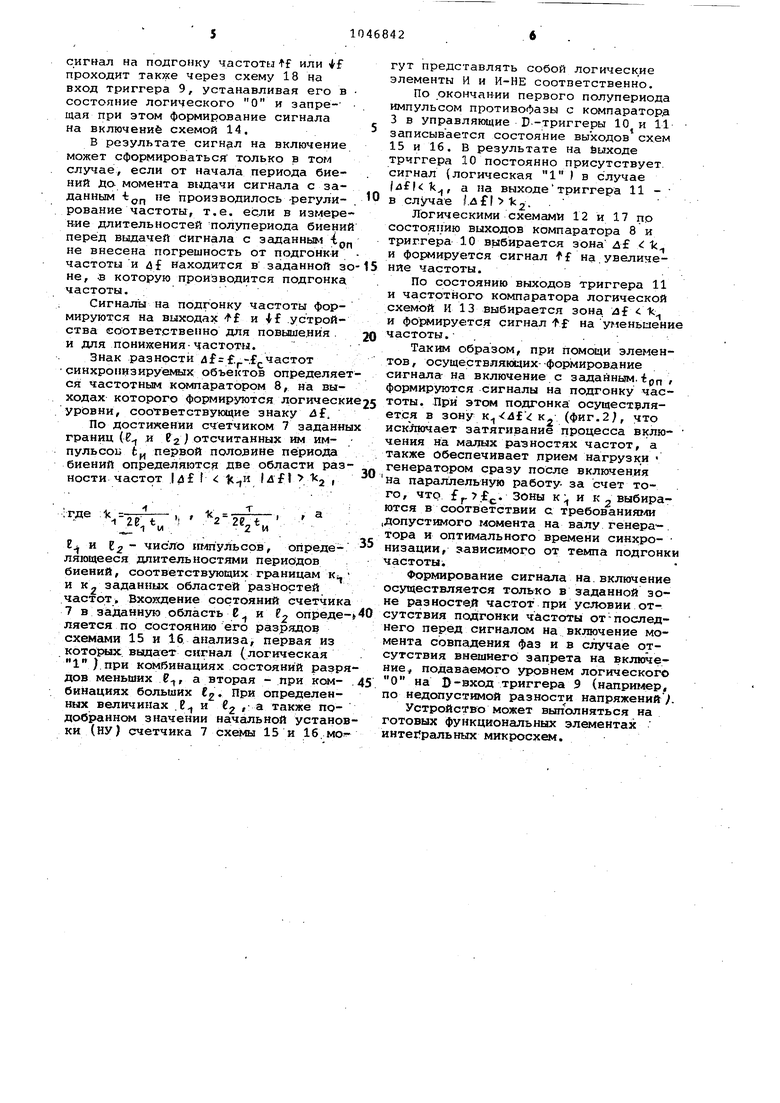

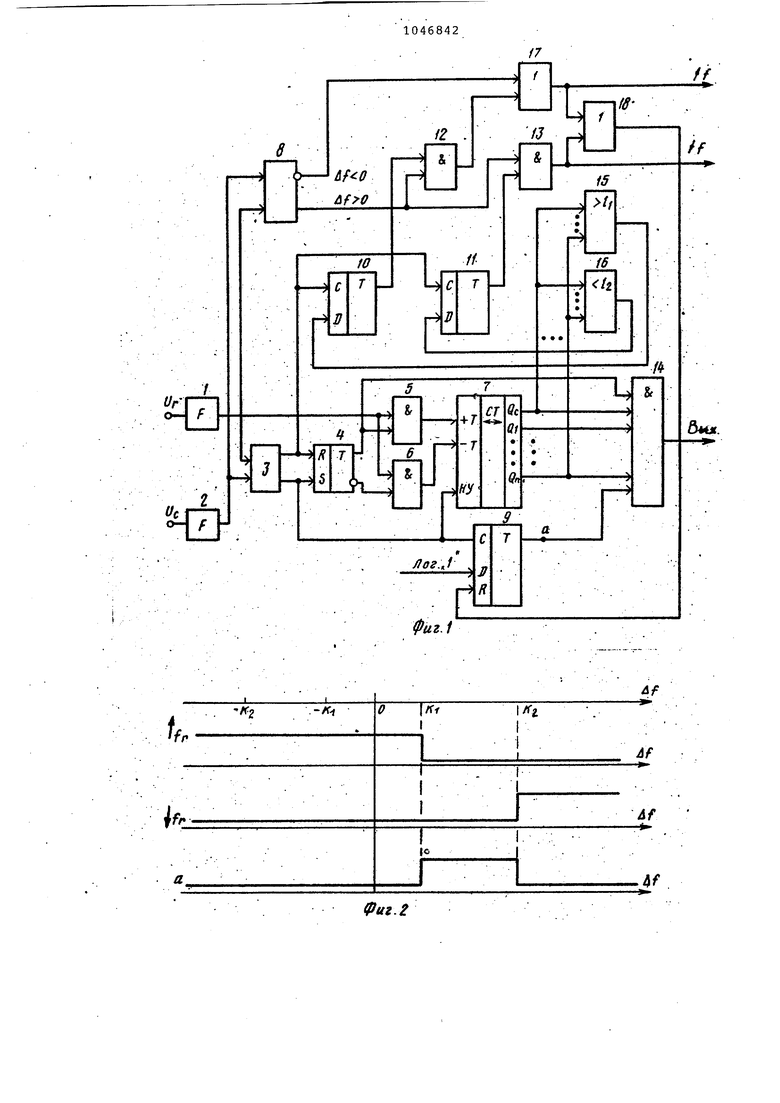

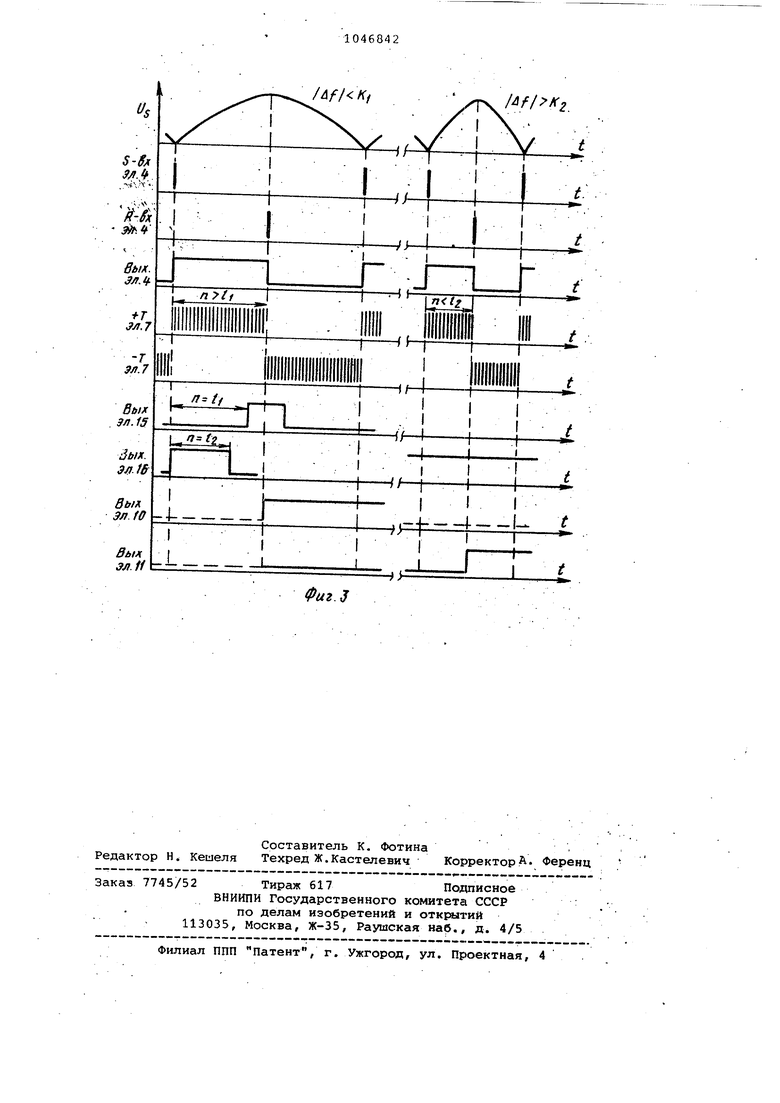

. 1 Изобретение относится к электроэнергетике, в частности к автоматической синхррнизации- возбужденных, генераторов переменного тока. Известны у.стройства автоматическо синхронизации с постоянным временем опережения, ,в которых определение . времени опережения производится по цифровым принципам прч определенной разност.и частоты и разности фаз 1J и C2J. . . Недостатком указаншлх устройств. является низкая точность и надежност при близкой к нулю разности частот синхронизируемых напряжений, т.е. при малых значениях приращений раз ности частот, так какпри этрм умен шается точность вычислений в цифровом решающем блоке, который должен также иметь сложное исполнение. Уст ройство может формировать сигнал по недопустимой разности частот, одна.ко этот сигнал не указывает знак ра ности lacTOT. . .; Наиболее близким к. предлагаемЬму является устройство для автсадатичес кой синхронизации с постоянным временем опережения, содержащее формирова.тели прямоугольных импульсов, подключенные на входы фазового компаратора, выходы КОТОРОГО подключен к установочным входам фазового 5триггера, две логические схемы И, один вход первой из которых подключен к прямому выходу фазового RSтриггера,. а другой - к выходу одног из формирователей прямоугольных импульсов и к. одному и.з входов второй логической схемы И,другой вход, кото рой подсседин.ен к инверсному выходу фазового RS-триггера, а выход пер,вой логическо.й схемы подсоединен K входу прямого счета счетчика импуль сов ГЗ J. . . , . Устрой ство работает по принципу подсчета и сравнения количества так товых импульсов за первую и вторую половину периода биений И имеет высокую точность при любой величине скольжения в случае ее постоянства на всем интервале периода биений. Оно не обладает малыг. временем синхронизации при малых разностях частот, так как требует для вычисления времени опережения полного периода биений, а Также способностью формирования сигналов.на подгонку частот учетом знака разности частот. Цель изобретения 7 уменьшение. вр.емени синхронизации при малых разностях частот, повышение точности формирования сигнала с заданным временем опережения, расширения функциональных возможностей путем формиров ния сигналов на подгонку частоты с учетог) знака разности частот. Поставленная цель достигается тем, что в известное уcTpoficTBO.,содержащее формирователи прямоугольных импульсов, подключенные на входь фазового компаратора, выходы которого подключены к установочным входам фазового .RS-триггера, две логические схе№1 и, .один вход первой из которых подключен к прямому выходу фазового | 5-триггера, а. другой -. к выходу одного из форм Е ователей прямоугольных импульсов и к одному ИЗ входов ВТО-. рой логической схемы И, другой -вход которой по соедииен к инверсному выходу фазового РЗ-триггера, а выход первой логической подсоединен к входу прямого счета счетчика го ульсов, введены частотный компаратор, три управляющих синхронными D -триггера, один из которых имеет вход-ну.- левой установки,, третья, четвертая и пятая логические И, две логическиё схеФ анализа содержимого счетчика импульсов, две .логические схемы ИЛИ, а .счетЧик импульсов выполнен реверсивным с входог-; обратного счета, подключенным к. выходу второй схемы И, причем Частотный . кс 4паратор подключен к выходам формирователей прямоугольных импульсов, входы третьей логической схемы Н подключены к прямому выходу фазового RS-триггера, к выходам разрядов счетчика импульсов и выходу первого управляющего синхронного D-триггера, С-вход которого соединен с входом начальнойг установки счетчика импульсов и с фазным выходом фазово- го компаратора, выход противофазы которого подключен к С-входам второго и .третьего управлягачих синхронных D-триггеров, входы схем анализа содержимого счетчика импульсов полключекы к выходам разрядов счетчика импульсов, а выходы - к D-входу, соответственно второго и третьего управляющих синхронных JJ-триггеров, первые входы четвертой и пятой логичес ких схем И объединены и подключены | прямому выходу частотного компаратора, а вторые - -соответственно к -ВЫХОДУ второго и третьего управ ляющихсинхронных D -триггеров, вхо ды первой логической схемы ИЛИ подключены соответственно к выходу чет вертой . схемы И и инверсному выходу частотного компаратора, а входы вто рой логической схемы ИЛИ соединены соответственно с выходок первой логической схемы. ИЛИ НС выходом пято логической схемы И, выхой -второй ло гической схемы ИЛИ подключен к . R-входу первого управляющего синхрон ного ЗЭ-триггера,, Б -вход которого является входрм внешнего разрешения на синхронизацию, причём выход первой логической ИЛИ является выходом .для повыпления частоты, выход пятой логической схемы И - выходом для пониже-пия частоты, а выход треть ей логической схемы И - выходом для включения автомата генератора, . На .1 дана функциональная , схема устройства, на фиг. 2 - диаграм мы, поясняющие формирование зон работы устройства; на фиг.3 - диаграммы, поясняющие работу элементов устройства. . Устройство содержит формирователи прямоугольных импульсов .1 и,2,фазовый компаратор 3, фазовый RS-TpHri гер 4, первую и вторую логические схемы И 5 и 6, реверсивный счетчик 7 импульсов с входами прямогосчета (+Т ), обратного счет-а (-Т ) п начальной установки (иу ) и выходами разрядов 01, Q... ft, частотный компаратор 8, первый, второй и третий, управляющие синхронные Р -триггеры 9-11, третью, четвертуй .и. пятую логические схемы И 12 - 14, логические схемы .1-5 и 16 анализа содержимого счетчика 7 .импульсов, а такжедве логические схемы ИЛИ 17 и 18. . .. Формирователи прямоугольных импульсов 1 и 2 обеспечивают преобразование синусоидальных напряжений (Т и иt одноименных синхронизуемых объектов в прямоугольные импульсы. Сформированные импульсы подаются на вход фазового компаратора 3, который по одному выходу выдае.т импульс в момент совпадения фаз напряжений Up и и синхронизируемых объектов,. а по другом -. в момент, когда (Jf и и находятся в противофазе. Сигналы фазы и противофазы .подаются на установочные входы фазового. RS -триггера 4, .прямой выход которого находится в единичном состоянии при нарастании разности фаз лЧ от О до 180°, т.е. в течение первой половины периода биений. Т, и в нулевом при уменьшении от 180 до 0 т.е. в течение второй .половины периода биений. Схема И 5, управляемая прямым выходом R5 -триггера 4, про- . пускает прямоугольные галпульсы с формирователя- 1 на вход (-«-Т/ реверсивного счетчика 7 импульсов только в течение первой половины периода биений Т (при нарастании 4Ч от О до 180.;. Схема И- б, управляемая и11версным выходом RS-триггера 4, пропускает прямоугольвше импульсы с формировате-ля 1 на вход обратного счета (-Т) счетчика 7 иглпульсов в течение второй половины периода -биений (при уменьшении дЧ от 180 до 0°;. Один из формирователей импульсов, например 1, используют как источниктактовой частоты для определения где t, времени опережения период следования тактовых .импульсов, соо,тветствующий частоте синхронизируемого напряжения, m г количество импульсов, необходимое для отсчета нужного tjj, для определения ширины первой половины периода биений Т/2 . n-t| ,- где .п - количество тактовых импульсов .а половину периода биений.. Счетчик 7 по входу (+т) отсчиты.вает счетные импульсы, поступающие через вентиль в первой половине периода биений, имея, например, нулевое исходное состояние в момент совпаде- . НИН фаз Uc и и , отсчитыва-я -таким образом п тактовых импульс.ов, количество которых соответствует длительности первой половины-периода биений. Для формирования сигнала ,с заданным временем опережения -fc ц из отсчитанных за первую половину периода биений П счетных импульсов необходимо по входу «вычитания (-Т ) сч.етчика 7 отсчитать (п-т) импульсов, где iofi/i число импульсов, соответствующее заданному .времени .опережения. Тогда число и 1пульсов n-m соответствует, времени Т/2-6д(м-гп) , а момент, когда- счетчик 7 имеет состояние m во втором полупериоде биений, свидетельствует о том,, что до момента совпадения фаз осталось время t, . При появлении в счетчике 7 состояния m , которое определяется по состоянию выходов его разрядов в.о второй .половине периода биений разрешающим уровнем с прямого выхода фазового триггера 4, а при-наличии разрешающего уровня (логической с инверсного выхода управляющего, тригг.ера. 9 на выходе- логической, схемы 17 формируется сигнсШ длительностью Т, который затем расширяется до необходимой величины..)-триггер 9 может иэменять свое состояние на разрегчающее (логическая 1 ) для схемы 17 . только в момент совпадения фаз импульсов с фазового компаратора 3, т.е. вначале периода биений. В случае, если производится подгон1ка частоты, т.е. разность частот д находится в области, запрещенной для включения на параллельную работу. сигнал на подгонку частоты tf или if проходит таюхе через схему 18 на вход триггера 9, устанавливая его в состояние логического О и запрещая при этом формирование сигнала на включение схемой 14. В результате сигнал на включение может сформироваться только в том случае, если от начала периода биений До момента вндачи сигнала с заданным , пе производилось -регулирование частоты, т.е. если в измере ние длительностей полупериода биени перед выдачей сигнала с заданным не внесена погрешность от подгонки частоты и 4f находится в заданной з не, а которую производится подгонка частоты. Сигналь на подгонку частоты формируются на выходах -ff и -tf .устройства соответственно для повышения . и для понижения-частоты. Знак разности ,частот синхронизИРУекялх объектов определяе ся: частотным компаратором 8, на выходах которого формируются логическ уровни, соответствующие знаку Л{, По достижении счетчиком 7 заданн границ (г и 82) отсчитанных им импульсоц 6 первой половине периода биений определяются две области раз ности частот It-, , :где:К Е И 2 число шлпуЛьсов, определяющееся длительностями периодов биений, соответствующих границам Kij и к2 заданных областей разностей частот. Вхождение состояний счетчик 7 в заданную область е и 2 опреде ляется по состоянию его разрядов схемами 15 и 16 анализа, первая из которых выдает сигнал (логическая 1 ) при комбинациях состояний разр дов меньших , а вторая - при комбинациях больших С. При определенных величинах .6 и 62 , а также подобранном значении начальной устано ки (НУ) счетчика 7 схеМы 15 и 16, мо гут представлять собой логическ.ие элементы И и И-НЕ соответственно. По окончании первого полупериода импульсом противофазы с компаратора 3 в управляющие Г--триггеры 10 и 11 записывается состояние выходов схем 15 и 16. В результате на йыходе триггера 10 постоянно присутствует, сигнал (логическая 1 ) в случае (, а на выходе триггера 11 - в случае 1.. Логическими схемами 12 и 17 по состоянию выходов компаратора 8 и триггера 10 выбирается зона д Ic и формиру€ тся сигнал ff на. увеличение частоты. По состоянию выходов триггера 11 и частотного компаратора логической схемой И 13 выбирается зонд л i k, и формируется сигнал ff на уменьшение частоты.- .. Таким образом, при помсяди элементов, осуществляющих формирование сигнала на включение с заданным, tpn формируются сигналы на подгонку частоты. При этом подгонка осуществляется в зону (фиг.2, что исключает затягивание процесса вклю- чения на малых разностях частот, а также Обеспечивает прием нагрузки генератором сразу после включения на параллельную работу- за счет того, что ff. j.. зоны к:, и к 2 выбираются в соответствии с требованиями .Допустимого момента на валу генератора и оптимального времени синхро- низации, зависимого от темпа подгонки частоты Формирование сигнала на.включение осуществляется только в заданной зоне разностеЯ частот при условии отсутствия подгонки частоты от-последнего перед сигналом на включение момента совп адения фаз и в случае отсутствия внешнего запрета на включение, подаваемого уровнем логического О на D-вход триггера 9 (например, по недопустимой разности напряжений Л Устройство может выполняться на готовых функциональнвлх элементах интег ральных микросхем.

Фа г. г

Фиг.З

,

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для взрывобезопасной диспетчерской телефонной связи в шахтах | 0 |

|

SU53123A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| . | |||

Авторы

Даты

1983-10-07—Публикация

1982-03-22—Подача