05

х

СП СП

о:

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный регенератор | 1986 |

|

SU1363490A1 |

| Формирователь сигналов со сдвигом фазы | 1986 |

|

SU1396239A1 |

| ЧАСТОТНО-ФАЗОВОЕ РЕЛЕ | 2016 |

|

RU2641096C2 |

| Приемник тонального вызова | 1984 |

|

SU1246417A1 |

| Устройство синхронизации сигналов времени | 1984 |

|

SU1167577A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1425770A2 |

| Одноканальное устройство для управления -фазным преобразователем | 1978 |

|

SU775855A1 |

| Фазовый дискриминатор | 1988 |

|

SU1598109A1 |

| Устройство для фазирования аппаратуры передачи информации циклическим кодом | 1973 |

|

SU478450A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

Изобретение относится к технике связи и м.б. использовано для контроля качества каналов связи. Цель изобретения - повышение точности измерения фазового дрожания как в циф- ровьк, так и в аналоговых системах связи. Достигается это за счет введения в устр-во формирователя импульсов 5, фазового детектора 21, фильтра низкой частоты 24, г-ра 25 импульсов и узла 29 выделения: опор.1 ной тактовой частоты, который содержит блок 7 определения опережения и запаздьюания фазы, блок 11 определения среднего значения фазы, RS- триггеры 13, 18, элементы И 14, 15, дешифратор 20, счетчик 22, блок сравнения 23 и счетный триггер 26. В устр-ве осуществляется формирование из псевдослучайного линейного сигнала двух регулярных импульсных последовательностей. При этом одна из последовательностей формируется как - опорный высокостабильный импульсный сигнал, а вторая повторяет фазовые флуктуации линейного сигнала. Обе эти последовательности подаются на фазовый детектор 21, где происходит выделение огибающей измеряемого фазового дрожания, поступающей далее на индикатор. 2 з.п. ф-лы, 5 ил. (Л

Шиг. /

Изобретение от юсится к технике связи и может быть исиользоваио для контроля качестпа каналов связи.

Цель изобретения - повышение точности измерения фазового дрожания как в цифровых, так и в аналоговых системах ,

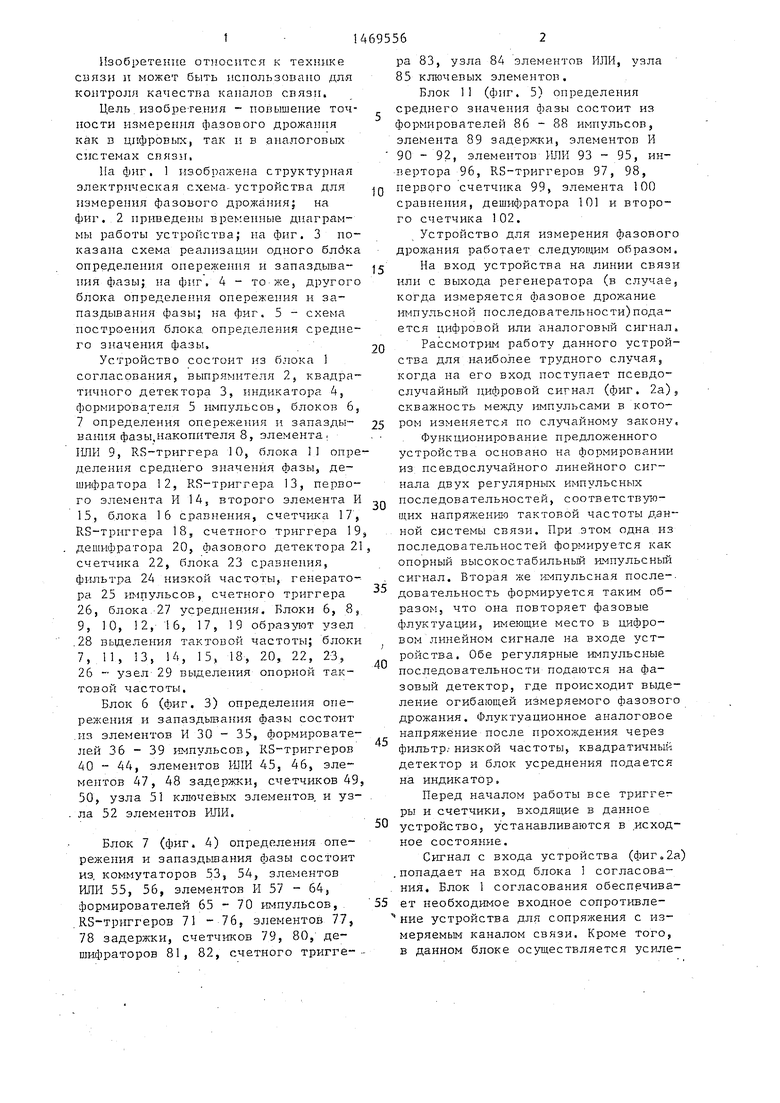

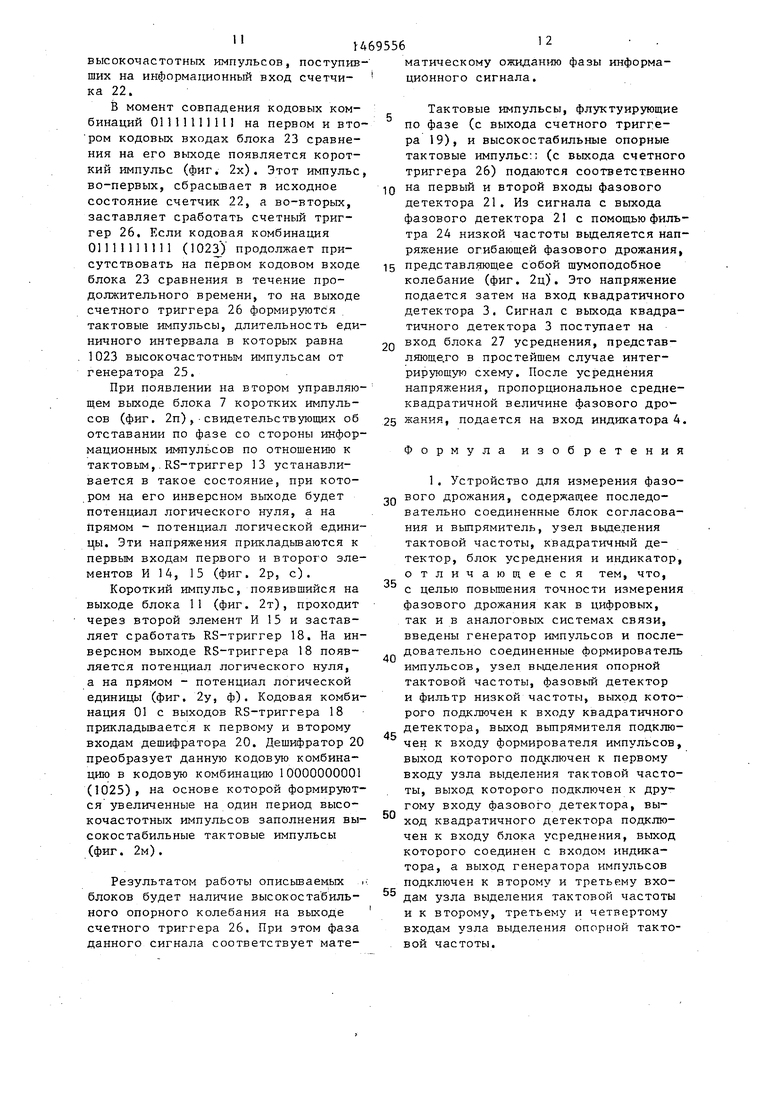

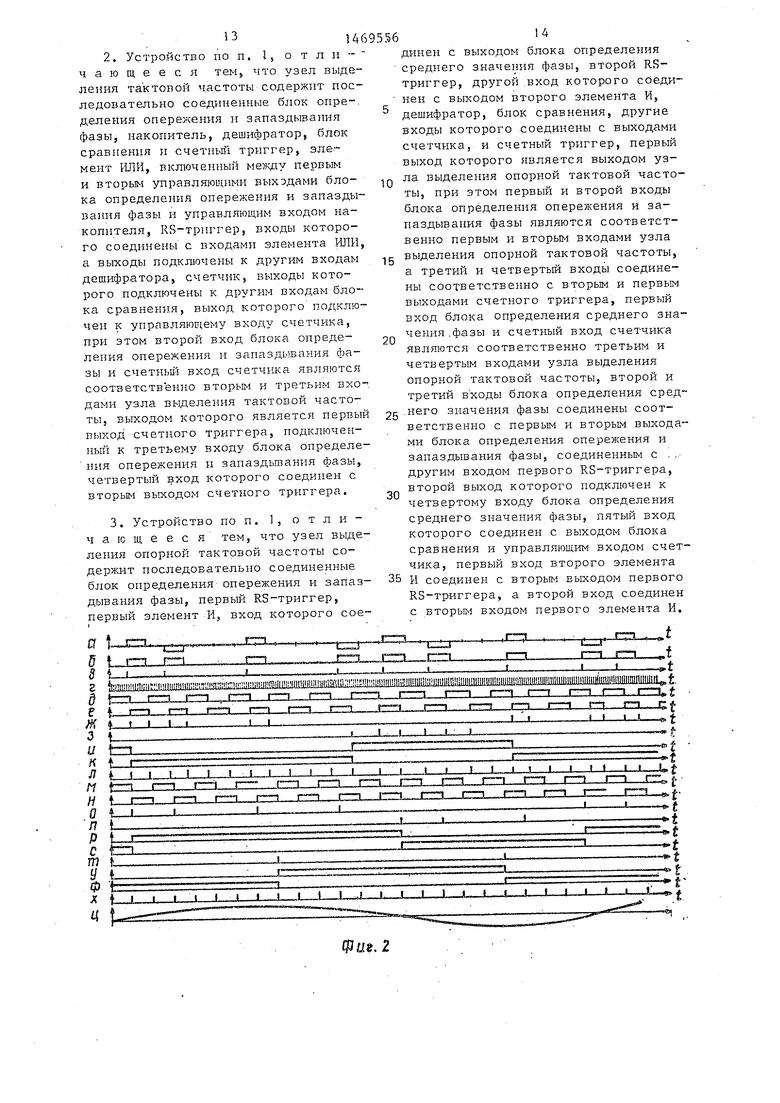

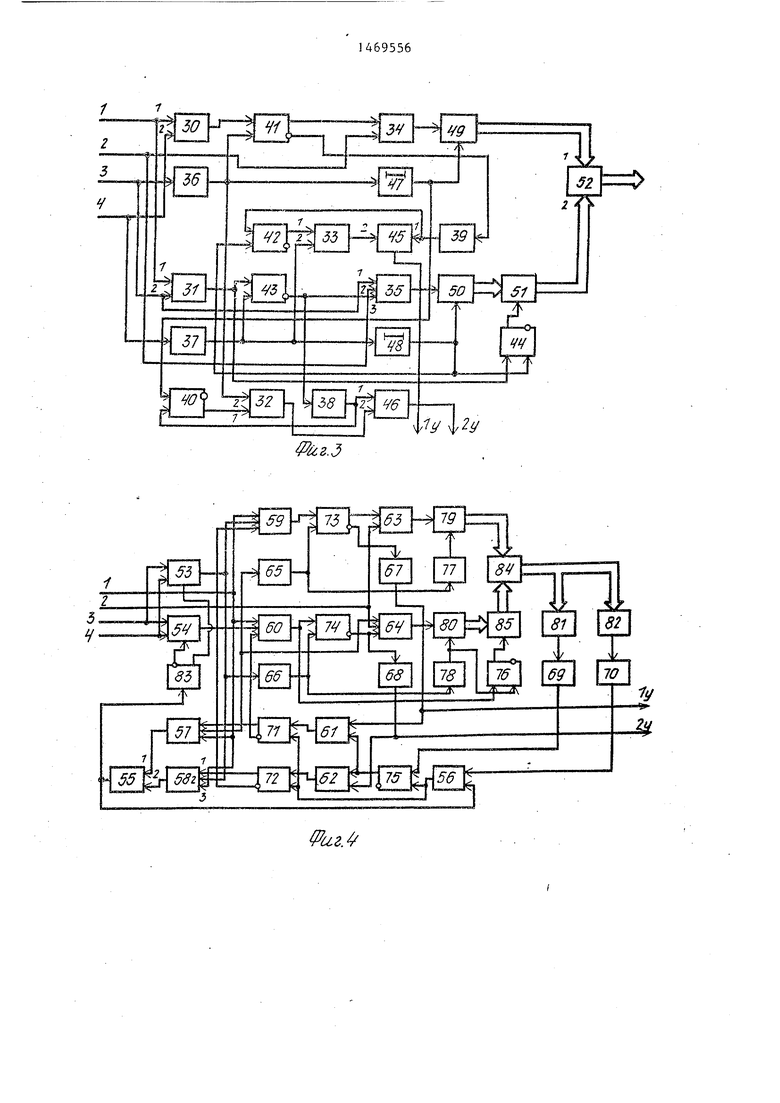

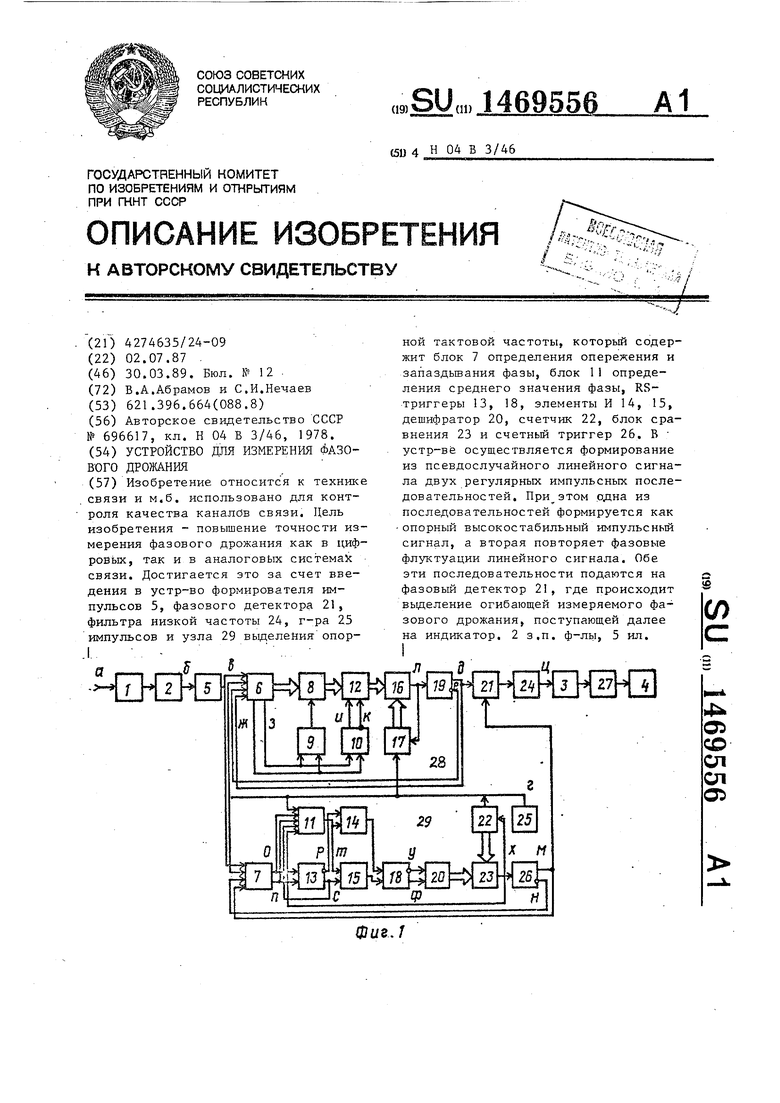

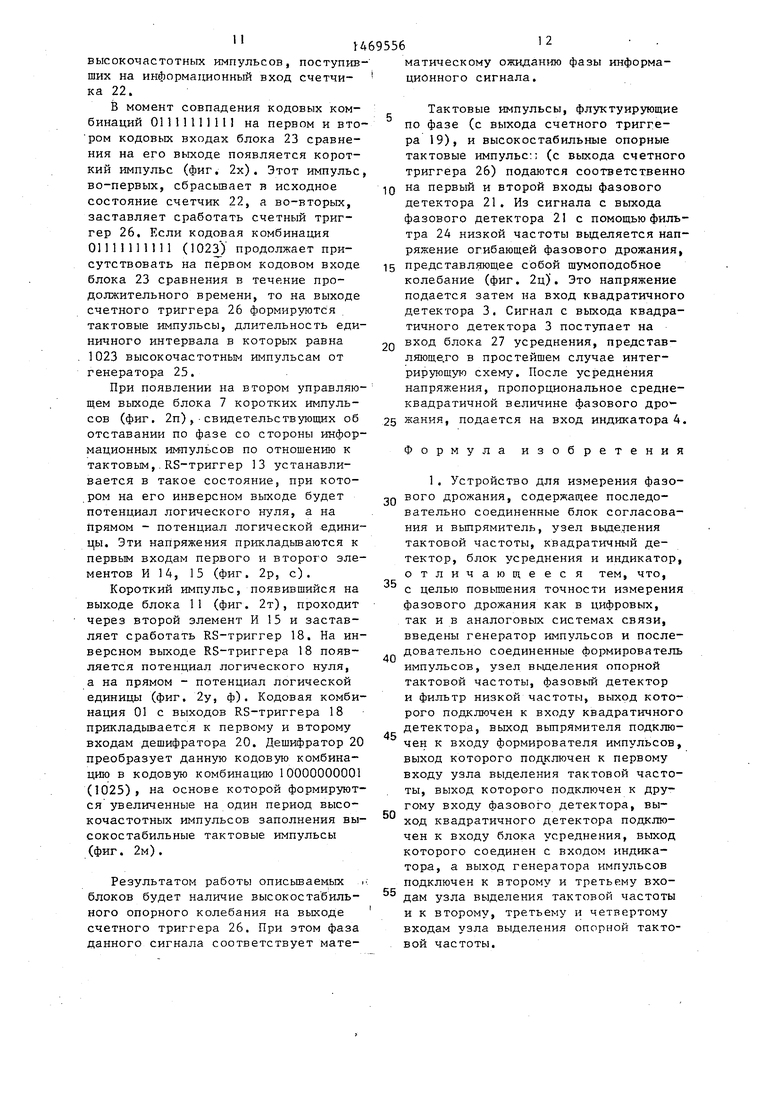

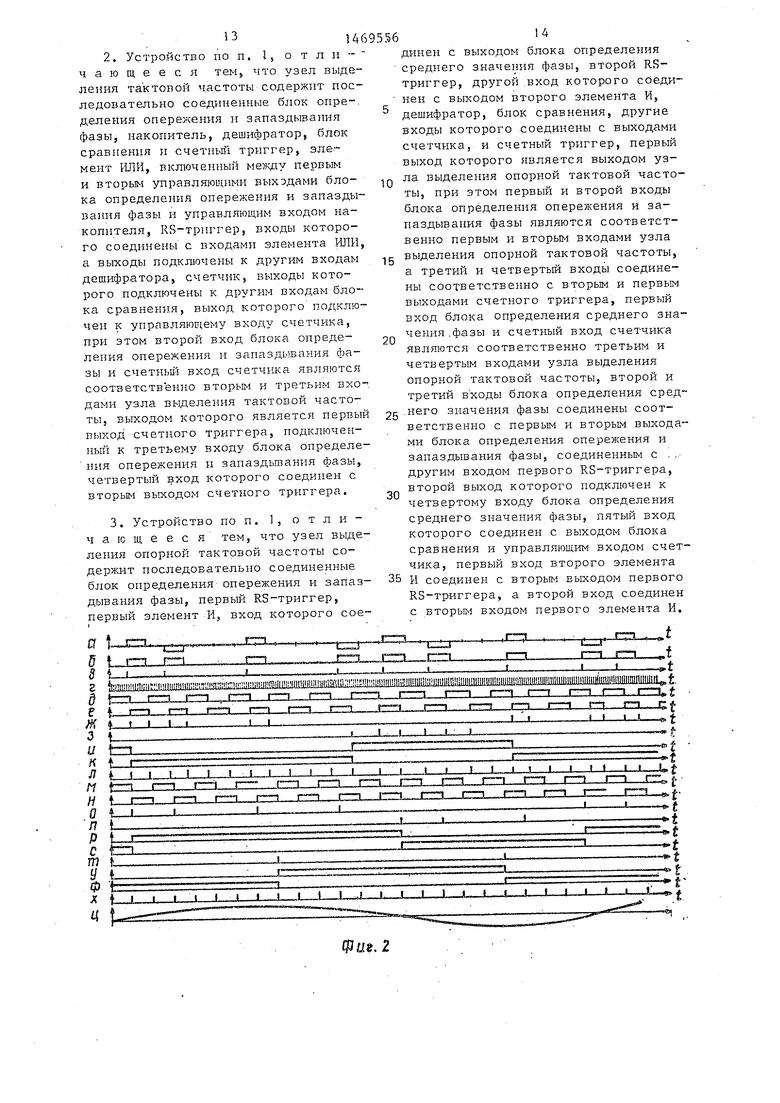

На фиг, 1 изображена структурная электрическая схема- устройства для измерения фазового дрожания5 на фиг, 2 нрнведены временные диаграммы работы устройства; на фиг. 3 но- казана схема реализации одного блбка онределения онережения и заназдыва- ния фазы; на фиг, 4 - то же, другого блока определения опережет я и запаздывания фазы; на фиг. 5 - схема построения блока определения среднего значения фазы.

Устройство состоит из блока 1 согласования, выпрямителя 2, квадратичного детектора 3, индикатора 4, формирователя 5 импульсов, блоков 6, 7 определения опережения и запаздывания фазы,накопителя 8, элемента:

IfflH 9, КЗ-триггера 10, блока 11 определения среднего значения фазы, дешифратора 12, Е-Я-триггера 13, первого элемента И 14, второго элемента И 15, блока 16 сравнения, счетчика 17, RS-триггера 18, счетного триггера 19s дешифратора 20, фазового детектора 21 , счетчика 22, блока 23 сравнения, фильтра 24 низкой частоты, генератора 25 импульсов, счетного триггера 26, блока,27 усреднения. Клоки 6, 8s 9, 10, 12, 16, 17, 19 o6pa3;snoT узел

28 выделения тактовой частоты; блоки 7,11, 13, 14, 15, 18, 20, 22, 23, 26 - узел 29 выделения опорной тактовой частоты.

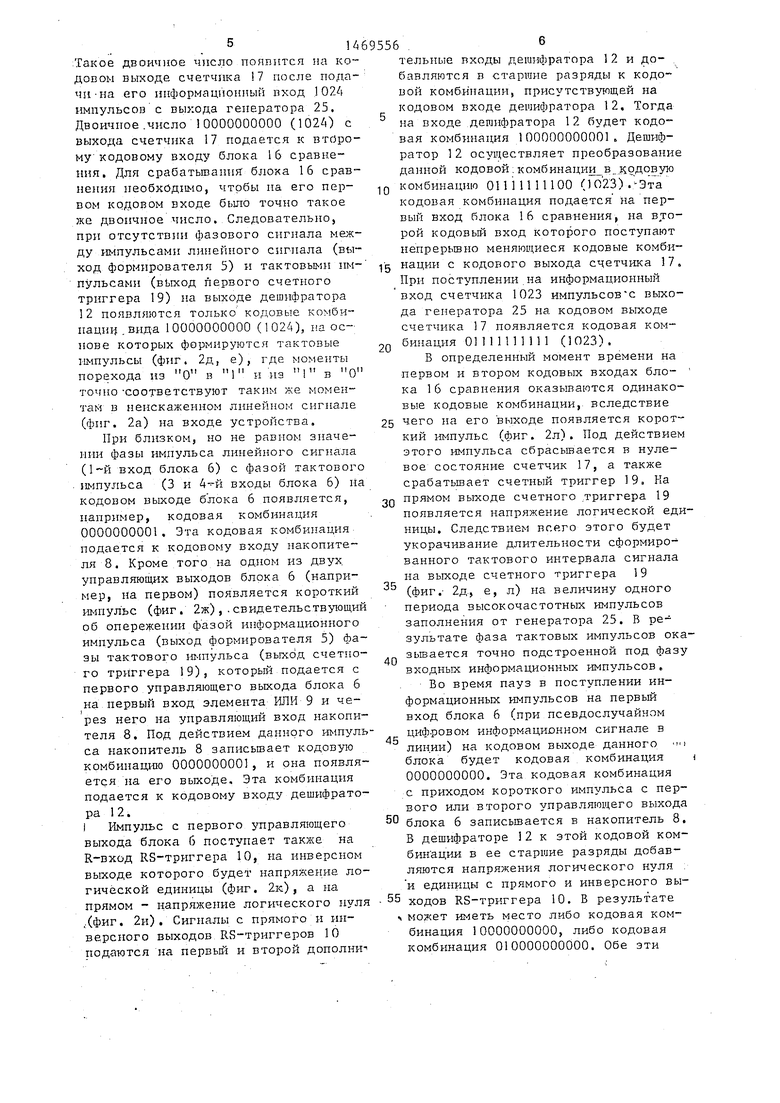

Блок 6 (фиг. 3) определения опережения и запаздывания фазы состоит из элементов И 30 - 35, формирователей 36-39 1&шульсов, RS-триггеров 40 - 44, элементов Ш1И 45, 46, элементов 47, 48 задержки, счетчиков 49, 50, узла 51 ключевых элементов, и узла 52 элементов ИЛИ.

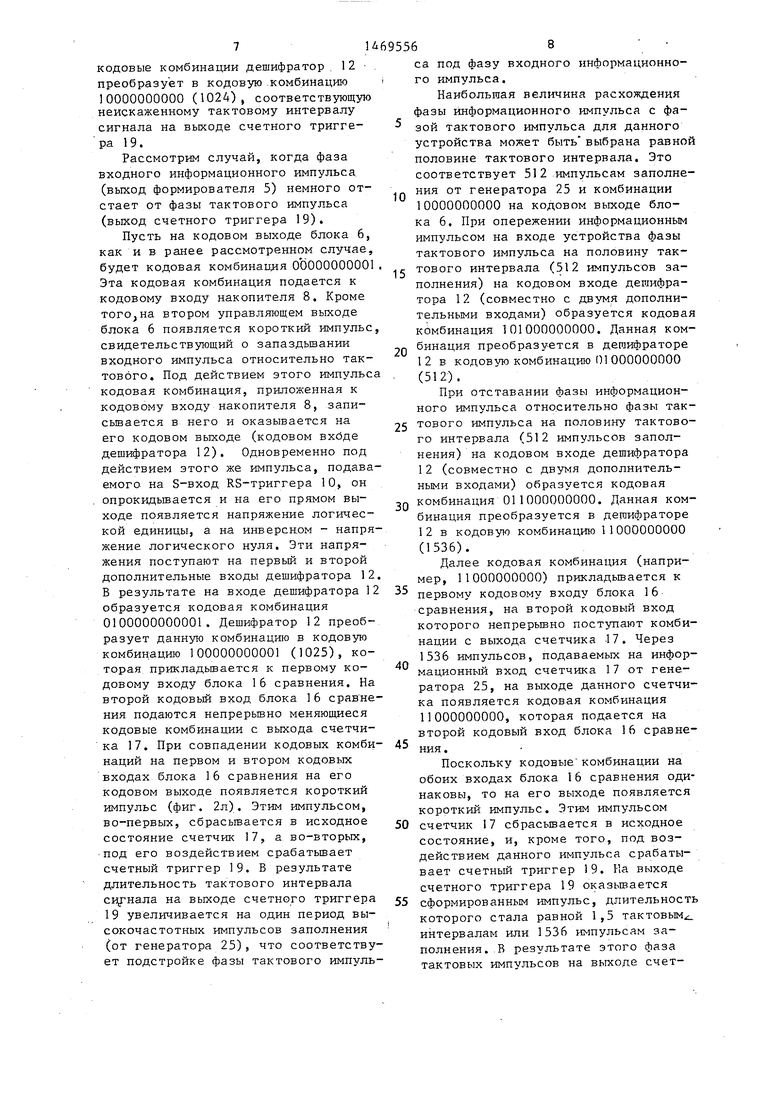

Блок 7 (фиг. 4) определения опережения и запаздьшания фазы состоит из, коммутаторов 53 54, элементов ИЛИ 55, 56, элементов И 57 - 64, формирователей 65-70 импульсов, RS-триггеров 71 - 76, элементов 77, 78 задержки, счетчиков 79, 80, дешифраторов 81, 82, счетного тригге0

5

0

5

0

5

0

5

0

5

ра 83, узла 84 элементов ИЛИ, узла 85 ключевых элементов.

Блок 11 (фиг. 5) определения сред1 его значения фазы состоит из формирователей 86 - 88 импульсов, 89 задержки, элементов И 90 - 92, элементов ИЛИ 93 - 95, инвертора 96, RS-триггеров 97, 98, первого счетчика 99, элемента 100 сравнения, дешифратора 101 и второго счетчика 102.

Устройство для измерения фазового дрожания работает следующим образом.

На вход устройства на линии связи или с выхода регенератора (в случае, когда измеряется фазовое дрожание импульсной последовательности)пода ется цифровой или аналоговый сигнал.

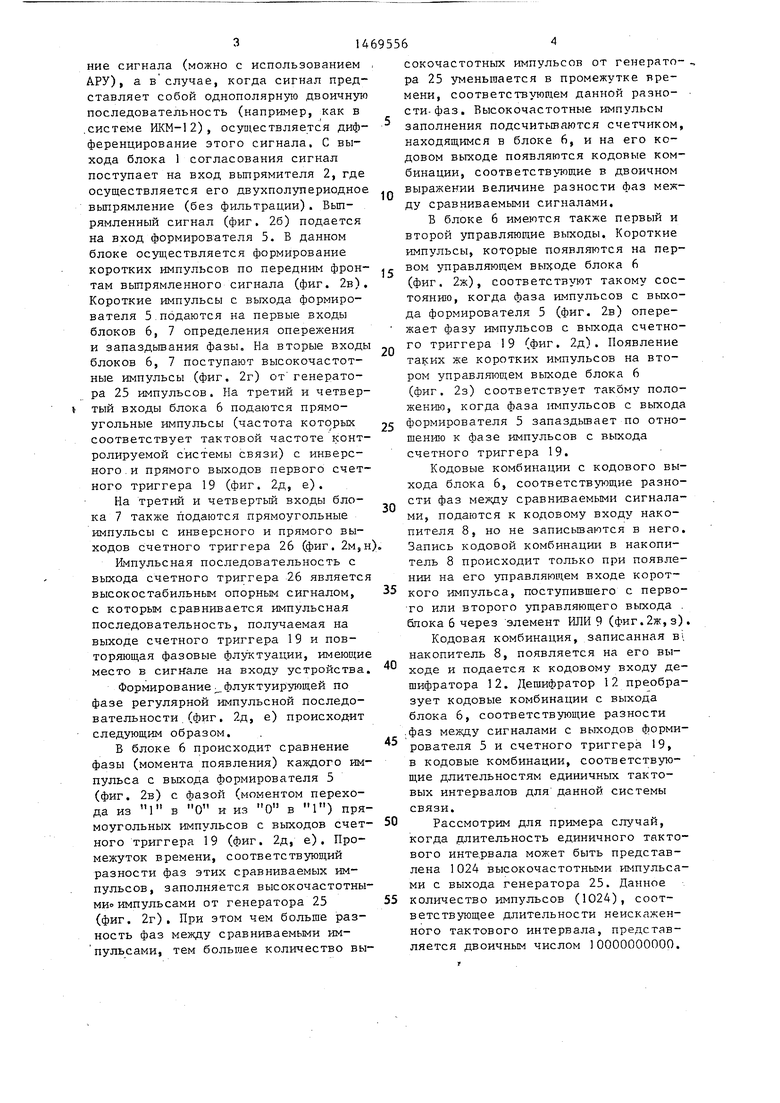

Рассмотрим работу данного устройства для наиболее трудного случая, когда на его вход поступает псевдослучайный цифровой сигнал (фиг. 2а), скважность между импульсами в котором изменяется по случайному закону.

Функционирование предложенного устройства основано на формировании из псевдослучайного линейного сигнала двух регулярных импульсных последовательностей, соответствующих напряжению тактовой частоты данной системы связи. При этом одна из последовательностей формируется как опорный высокостабильньм импульсньш сигнал. Вторая же импульсная после-- довательность формируется таким об- разоь, что она повторяет фазовые флуктуации, имеющие место в цифровом линейном сигнале на входе устройства. Обе регулярные импульсные последовательности подаются на фазовый детектор, где происходит выделение огибающей измеряемого фазового дрожания. Флуктуационное аналоговое напряжение после прохождения через фильтр. низкой частоты, квадратичньш детектор и блок усреднения подается на индикатор.

Перед началом работы все триггеры и счетчики, входящие в данное устройство, устанавливаются в .исходное состояние.

Сигнал с входа устройства (фиг.2а) .попадает на вход блока 1 согласования. Блок I согласования обеспечивает необходимое входное сопротивле- нив устройства для сопряжения с измеряемым каналом связи. Кроме того, в данном блоке осуществляется усиле

314

ние сигнала (можно с использованием АРУ), а в случае, когда сигнал представляет собой однополярную двоичную последовательность (например, как в .системе ЖМ-1 2) , осуп1ествляется дифференцирование этого сигнала. С выхода блока 1 согласования сигнал поступает на вход вьшрямителя 2, где осуществляется его двухполупериодное выпрямление (без фильтрации). Бьш- рямленный сигнал (фиг, 26) подается на вход формирователя 5. В данном блоке осуществляется формирование коротких импульсов по передним фрон- там вьшрямленного сигнала (фиг. 2в), Короткие импульсы с выхода формирователя 5.подаются на первые входы блоков 6, 7 определения опережения и запаздьшания фазы. На вторые входы блоков 6, 7 поступают высокочастотные импульсы (фиг. 2г) от генератора 25 импульсов. На третий и четвертый входы блока 6 подаются прямоугольные импульсы (частота которых соответствует тактовой частоте контролируемой системы связи) с инверсного . и прямого выходов первого счетного триггера 19 (фиг. 2д, е).

На третий и четвертый входы блока 7 также подаются прямоугольные импульсы с инверсного и прямого выходов счетного триггера 26 (фиг. 2м,н

Импульсная последовательность с выхода счетного триггера 26 является высокостабильным опорным сигналом, с которым сравнивается импульсная последовательность, получаемая на выходе счетного триггера 19 и повторяющая фазовые флуктуации, имеюпдае место в сигнале на входу устройства.

ФормирОБание флуктуирующей по фазе регулярной импульсной последовательности . (фиг . 2д, е) происходит следующим образом.

В блоке 6 происходит сравнение фазы (момента появления) каждого импульса с выхода формирователя 5 (фиг. 2в) с фазой (моментом перехода из 1 в О и из О в 1) прямоугольных импульсов с выходов счетного триггера 19 (фиг. 2д, е). Промежуток времени, соответствующий разности фаз этих сравниваемых импульсов, заполняется высокочастотными импульсами от генератора 25 (фиг. 2г), При этом чем больше разность фаз между сравниваемыми им

пульсами, тем большее количество вы

0

5

Q

0

сокочастотных импульсов от генерато- . ра 25 уменьшается в промежутке времени, соответствуюп1ем данной разно- сти-фаз. Высокочастотные импульсы заполнения подсчитьгоаются счетчиком, находящимся в блоке 6, и на его кодовом выходе появляются кодовые комбинации, соответствующие в двоичном выражении величине разности фаз между сравниваемыми сигналами,

В блоке 6 имеются также первый и второй управляющие выходы. Короткие импульсы, которые появляются на первом управляющем выходе блока 6 (фиг. 2ж), соответствуют такому состоянию, когда фаза импульсов с выхода формирователя 5 (фиг. 2в) опережает фазу импульсов с выхода счетного триггера 19 (фиг. 2д). Появление таких же коротких импульсов на втором управляющем выходе блока 6 (фиг. 2з) соответствует такому положению, когда фаза 1-1мпульсов с выхода формирователя 5 запаздьшает по отношению к фазе импульсов с выхода счетного триггера 19.

Кодовые комбинации с кодового выхода блока 6, соответствующие разности фаз между сравниваемыми сигналами, подаются к кодовому входу нако

55

0

45

50

пителя 8, но не записьшаются в него. Запись кодовой комбинации в накопитель 8 происходит только при появлении на его управляющем входе короткого импульса, поступившего с перво- то или второго управляющего выхода . блока 6 через элемент ИЛИ 9 (фиг.2ж,з).

Кодовая комбинация, записанная в1 накопитель 8, появляется на его выходе и подается к кодовому входу дешифратора 12. Дешифратор 12 преобразует кодовые комбинации с выхода блока 6, соответствующие разности .фаз между сигналами с выходов формирователя 5 и счетного триггера 19, в кодовые комбинации, соответствующие длительностям единичных тактовых интервалов для данной системы связи.

Рассмотрим для примера случай, когда длительность единичного тактового интервала может быть представлена 1024 высокочастотными импульсами с выхода генератора 25. Данное количество импульсов (1024), соответствующее длительности неискаженного тактового интервала, представляется двоичным числом 10000000000.

1А69556

:Такое двоичное число появится на кодовом выходе счетчика 7 после подачи -на его информационный пход 102А импульсоп с выхода генератора 25. Двоичное.число 10000000000 ( с выхода счетчика 17 подается к втс5ро- му кодовому входу блока 16 сравнения. Для срабатьшания блока 16 сравнения необходимо, чтобы на его первом кодовом входе было точно такое же двоичное число. Следовательно, при отсутствии фазового сигнала между импульсами линейного сигнала (выход формирователя 5) и тактовыми импульсами (вЬгход первого счетного триггера 19) на выходе дешифратора 12 появляются только кодовые комбинации.вида 10000000000 (1024), наос-; нове которых формируются тактовые импульсы (фиг. 2д, е), где моменты порехода из О в 1 и из 1 в О точно -соответствуют таким же моментам в неискаженном линейном сигнале (фиг. 2а) на входе устройства.

При близком, но не равном значении фазы импульса линейного сигнала ( вход блока 6) с фазой тактового . импульса (3 и входы блока 6) на кодовом выходе блока 6 появляется, например, кодовая комбинация 0000000001. Эта кодовая комби гация подается к кодовому входу накопителя 8 . Кроме того на одном из двух, управляющих выходов блока 6 (например, на первом) появляется короткий импульс (фиг. 2ж),.свидетельствующий об опережении фазой информационного импульса (выход формирователя 5) фазы тактового 1с-1пульса (выхбд счетного триггера 19), который подается с первого управляющего выхода блока 6 на первый вход элемента ИЛИ 9 и че- рез него на управляющий вход накопителя 8. Под действием данного импульса накопитель 8 записьшает кодовую комбинацию 0000000001, и она появля етсяНа его выходе. Эта комбинация подается к кодовому входу дешифратора 12. I Импульс с первого управляющего

выхода блока 6 поступает таклсе на R-вход RS-триггера 10, на инверсном выходе которого будет напряжение логической единицы (фиг. 2ic), а на прямом - напряжение логического нул ,(Фиг. 2и). Сигналы с прямого и инверсного выходов RS-триггеров 10 подаются на первый и второй дополни

6

5

0

5

технэные входы дешифратора 12 и до- . бавляются в старшие разряды к кодовой комбинации, присутствующей на кодовом входе дешифратора 12. Тогда на входе деганфратора 12 будет кодовая комбинация 100000000001. Дешифратор 12 осуществляет нреобразование данной кодовой; комбинации в. комбинацию 0111 11 11100 (1023) . кодовая комбинация подается на первый вход блока 16 сравнения, на второй кодовый вход которого поступают непрерьшно меняющиеся кодовые комбинации с кодового выхода счетчика 17. При поступлении на информационный вход счетчика 1023 импульсов с выхода генератора 25 на кодовом выходе счетчика 17 появляется кодовая комбинация 0111 1111 11 1 (1023).

В определенный момент времени на первом и втором кодовых входах бло- ка 16 сравнения оказываются одинаковые кодовые комбинации, вследствие чего на его выходе появляется короткий импульс (фиг. 2л). Под действием этого импульса сбрасьшается в нулевое состояние счетчик 17, а также срабатьшает счетный триггер 19, Ка прямом выходе счетного .триггера 19 появляется напряжение логической единицы. Следствием всего этого будет укорачивание длительности сформированного тактового интервала сигнала на выходе счетного триггера 19 (фиг.- 2д, е, л) на величину одного периода высокочастотных импульсов заполнения от генератора 25. В результате фаза тактовых импульсов ока- зьюается точно подстроенной под фазу входных информационных импульсов,

Во время пауз в поступлении информационных импульсов на нервьй вход блока 6 (при псевдослучайном цифровом информационном сигнале в лиции) на кодовом выходе данного , блока будет кодовая комбинация i 0000000000. Эта кодовая комбинация с приходом короткого импульса с первого или второго управляющего выхода 50 блока 6 записьтается в накопитель 8. В дешифраторе 12 к этой кодовой ком- бин ации в ее старшие разряды добавляются напряжения логического нуля : и единицы с прямого и инверсного вы- 55 ходов RS-триггера 10. В результате ч может иметь место либо кодовая комбинация 10000000000, либо кодовая комбинация 010000000000. Обе эти

0

5

40

45

кодовые комбинации дешифратор .12- преобразует в кодовую комбинацию 10000000000 (1024), соответствующую неискаженному тактовому интервалу сигнала на выходе счетного триггера 19.

Рассмотрим случай, когда фаза входного информационного импульса (выход формирователя 5) немного отстает от фазы тактового импульса (выход счетного триггера 19).

Пусть на кодовом выходе блока 6, как и в ранее рассмотренном случае, будет кодовая комбинаиля 00000000001 Эта кодовая комбинация подается к кодовому входу накопителя 8. Кроме того,на втором управляющем выходе блока 6 появляется короткий импульс, свидетельствующий о запаздьшании входного импульса относительно тактового. Под действием этого импульса кодовая комбинация, приложенная к кодовому входу накопителя 8, запи- сьюается в него и оказывается на его кодовом выходе (кодовом вхбде дешифратора 12). Одновременно под действием этого же импульса, подаваемого на S-вход RS-триггера 10, он опрокидывается и на его прямом выходе появляется напряжение логической единицы, а на инверсном - напряжение логического нуля. Эти напряжения поступают на первьш и второй дополнительные входы дешифратора 12 В результате на входе дешифратора 12 образуется кодовая комбинация 0100000000001. Дешифратор 12 преобразует данную комбинацию в кодовую комбинацию 100000000001 (1025), которая прикладьшается к первому кодовому входу блока 16 сравнения. На второй кодовый вход блока 16 сравнения подаются непрерывно меняющиеся кодовые комбинации с выхода счетчика 17. При совпадении кодовых комбинаций на первом и втором кодовых входах блока 16 сравнения на его кодовом выходе появляется короткий импульс (фиг. 2л). Этим импульсом, во-первых, сбрасьгоается в исходное состояние счетчик 17, а во-вторых, под его воздействием срабатьшает счетный триггер 19. В результате длительность тактового интервала сигнала на выходе счетного триггера 19 увеличивается на один период высокочастотных импульсов заполнения (от генератора 25), что соответствует подстройке фазы тактового импуль

5

0

5

0

5

0

5

0

5

са под фазу входного информационного импульса.

Наибольшая величина расхождения фазы информационного импульса с фазой тактового импульса для данного устройства может быть выбрана равной половине тактового интервала. Это соответствует 512 импульсам заполнения от генератора 25 и комбинации 10000000000 на кодовом выходе блока 6. При опережении информационным импульсом на входе устройства фазы тактового импульса на половину тактового интервала (512 импульсов заполнения) на кодовом входе дешифратора 12 (совместно с двумя дополнительными входами) образуется кодовая комбинация 101000000000. Данная комбинация преобразуется в дегаифраторе 1 2 в кодовую комбинацию 01 000000000 (512).

При отставании фазы информационного импульса относительно фазы тактового импульса на половину тактового интервала (512 импульсов заполнения) на кодовом входе дешифратора 12 (совместно с двумя дополнительными входами) образуется кодовая комбинация 011000000000. Данная комбинация преобразуется в дегаифраторе 12 в кодовую комбинацию 11000000000 (1536).

Далее кодовая комбинация (например, 11000000000) прикладьшается к первому кодовому входу блока 16 сравнения, на второй кодовый вход которого непрерьшно поступают комбинации с выхода счетчика -17. Через 1536 импульсов, подаваемых на информационный вход счетчика 17 от генератора 25, на выходе данного счетчика появляется кодовая комбинация 11000000000, которая подается на второй кодовый вход блока 16 сравнения .

Поскольку кодовые комбинации на обоих входах блока 16 сравнения одинаковы, то на его выходе появляется короткий импульс. Этим импульсом счетчик 17 сбрасьшается в исходное состояние, и, кроме того, под воздействием данного импульса срабатывает счетный триггер 19, На выходе счетного триггера 19 оказьгоается сформированным импульс, длительность которого стала равной 1,5 тактовым интервалам или 1536 импульсам заполнения. .В результате этого фаза тактовых импульсов на выходе счет914

ного триггера 19 оказалась точно подстроенной под фазу информационного сигнала на входе устройства.

Таким образом, любое изменение фазы входных импульсов относительно тактовых импульсов (выход счетного триггера 19) всегда завершается подстройкой фазы данных тактовых импульсов под фазу входного сигнала. В результате проделанньк операций происходит переход от линейного сигнала со случайной скважностью (фиг. 2а) к регулярной импульсной последовательности (фиг. 2д) с сохранением информации о фазовом дрожании сигнала. Это необходимо было проделать для того, чтобы исключить влиярие случайной скважности линей- 1ного сигнала на измеряемое фазовое дрожание. Без данного преобразования измерение фазовьк флуктуации в .цифровом сигнале со случайной скважностью между импульсами оказалось б невозможным.

Регулярное тактовое колебание (фиг. 2д) с выхода счетного триггера 19 поступает на первый вход фазового детектора 21. Однако для выделения огибающей фазовых флуктуа- ций из этого сигнала необходимо иметь высокостабильное опорное колебание. Это колебание получают с помощью блоков 7, 11, 13, 14, 15, 18, 20, 22, 23, 26, образующих узел 29 выделения опорной тактовой часто ты.

Формирование высокостабильной импульсной последовательности

.

(фиг. 2м, н) осуществляется следующим образом.

В блоке 7 происходит сравнение фазы (момента появления) импульса с выхода формирователя 5 (фиг. 2в) с фазой прямоугольных импульсов, поступающих с прямого и инверсного выходов счетного триггера 26. Наличие опережения или запаздьшания фазы информационных импульсов проявляется в появлении на первом или втором управляющем входе блока 7 коротких импульсов (фиг, 2о, п). Эти сигналы подаются на R- и S-входы RS-тригге- ра 13 и на второй и третий входы блока 11 определения среднего значения фазы.

При появлении на первом управляющем выходе (фиг. 2о) блока 7 короткого импульса (свидетельствующего об

5 о 5

о

5

0

5

10

опережении фазы информационного импульса по отношение к тактовому) RS- триггер 13 устанавливается в такое состояние, при котором на его инверсном выходе будет напряжение логической единицы, а на прямом - нап- ряжение логического нуля (фиг. 2р, с). Эти напряжения прикладьшаются к первым входам первого и второго элементов И 14, 15, однако не проходят через них, так как на вторые входы данных элементов подается напряжение логического нуля с выхода блока 11 определения среднего значения фазы.

На первый вход блока 11 поступают высокочастотные импульсы (фиг. 2г) с выхода генератора 25, На четвертый вход блока П подаются напряжения логических нулей и единиц с прямого выхода RS-триггера 13, а на пятый вход блока 11 - короткие импульсы (фиг. 2х) с выхода блока 23 сравнения. Моменты появления импульсов на выходе блока 11 в стационарном режиме работы измерительного устройства соответствуют средним значениям фазы информационного сигнала на входе данного .устройства. Короткий импульс с выхода блока 11 (фиг. 2т) поступает на вторые входы первого и второго .элементов И 14, 15, однако про- ходит только через первый элемент И 14, поскольку на его первом входе в это время действует потенциал логической единицы с инверсного выхода RS-триггера 13. Этот короткий импульс подается на К-вход RS-триггера 18 и опрокидьшает его. На инверсном выходе RS-триггера 18 появляется потенциал логической единицы, а на прямом - потенциал логического нуля. Кодовая комбинация 10 прикла- дьшается к первому и второму входам дешифратора 20. Дешифратор 20 преобразует данную кодовую комбинацию в кодовую комбинацию 01111111111(1023) на основе которой формируются укороченные на один период высокочастотных импульсов заполнения высокостабильные тактовые импульсы (фиг. 2м), Происходит это следующим образом. Кодовая комбинация 011111111П (lb23)- прикладьгоается к первому кодовому входу блока 23 сравнения. На второй кодовый вход блока 23 с кодового выхода счетчика 22 поступают непрерьшно меняющиеся кодовые комбинации, пропорциональные количеству

n

высокочастотных импульсов, поступив ших на информатщонный вход счетчи- ка 22.

В момент совпадения кодовых комбинаций 0111111111 на первом и вто ром кодовых входах блока 23 сравнения на его выходе появляется короткий импульс (фиг. 2х). Этот импульс во-первых, сбрасьшает в исходное состояние счетчик 22, а во-вторых, заставляет сработать счетный триггер 26. Если кодовая комбинация 01111111111 (1020 продолжает присутствовать на первом кодовом входе блока 23 сравнения в течение продолжительного времени, то на выходе счетного триггера 26 формируются тактовые импульсы, длительность единичного интервала в которых равна 1023 высокочастотным импульсам от генератора 25.

При появлении на втором управляющем выходе блока 7 коротких импульсов (фиг. 2п),свидетельствующих об отставании по фазе со стороны информационных импульсов по отношению к тактовым,.RS-триггер 13 устанавливается в такое состояние, при котором на его инверсном выходе будет потенциал логического нуля, а на прямом - потенциал логической единицы. Эти напряжения прикладьшаются к первым входам первого и второго элементов И 14, 15 (фиг. 2р, с).

Короткий импульс, появившийся на выходе блока 11 (фиг. 2т), проходит через второй элемент И 15 и заставляет сработать RS-триггер 18. На инверсном выходе RS-триггера 18 появляется потенциал логического нуля, а на прямом - потенциал логической единицы (фиг. 2у, ф). Кодовая комбинация 01 с выходов RS-триггера 18 прикладьшается к первому и второму входам дешифратора 20. Дешифратор 20 преобразует данную кодовую комбинацию в кодовую комбинацию 10000000001 (1025), на основе которой формируются увеличенные на один период высокочастотных импульсов заполнения высокостабильные тактовые импульсы (фиг. 2м).

Результатом работы описьшаемых блоков будет наличие высокоста биль- ного опорного колебания на выходе счетного триггера 26. При этом фаза данного сигнала соответствует матеУ469556

в-

12

матическому ожиданию ционного сигнала.

0

0

Тактовые импульсы, флуктуирующие по фазе (с выхода счетного триггера 19), и высокостабильные опорные тактовые импульс:; (с выхода счетного триггера 26) подаются соответственно на первый и второй входы фазового детектора 21. Из сигнала с выхода фазового детектора 21 с помощью фильтра 24 низкой частоты выделяется напряжение огибающей фазового дрожания,

5 представляющее собой шумоподобное колебание (фиг. 2ц). Это напряжение подается затем на вход квадратичного детектора 3. Сигнал с выхода квадратичного детектора 3 поступает на вход блока 27 усреднения, представ- ляюще.го в простейшем случае интегрирующую схему. После усреднения напряжения, пропорциональное среднеквадратичной величине фазового дро-

5 жания, подается на вход индикатора 4.

Формула изобретения

5

0

5

0

1314

Фи«. 2

10

9556

15

динен с выходом блока определения среднего значения фазы, второй RS- триггер, другой .вход которого соединен с выходом второго элемента И, дешифратор, блок сравнения, другие входы которого соединены с выходами счетчика, и счетный триггер, первый выход которого является выходом узла выделения опорной тактовой частоты, при этом первый и второй входы блока определения опережения и запаздывания фазы являются соответственно первым и вторым входами узла выделения опорной тактовой частоты, а третий и четвертьш входы соединены соответственно с вторым и первым выходами счетного триггера, первый вход блока определения среднего значения .фазы и счетный вход счетчика являются соответственно третьим и четвертым входами узла выделения опорной тактовой частоты, второй и третий входы блока определения сред- .него значения фазы соединены соответственно с первым и вторьм выходами блока определения опережения и запаздывания фазы, соединенным с .., другим входом первого RS-триггера, второй выход которого подключен к четвертому входу блока определения среднего значения фазы, пятый вход которого соединен с вы.ходом блока сравнения и унравляющим входом счетчика, нервый вход второго элемента 35 и соединен с вторым выходом первого RS-триггера, а второй вход соединен с вторьм входом первого элемента И.

20

25

30

иг.

фцг.5.

| Устройство для измерения фазового джиттера | 1978 |

|

SU696617A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-03-30—Публикация

1987-07-02—Подача