Изобретение относится к электротехнике и может быть использовано при разработке средств вторичного электропитания радиоэлектронной аппаратуры.

Известно устройство, содержащее двухтактный транзисторный инвертор с датчиком тока и разделительным трансформатором, имеющим N вторичных обмоток, N выпрямительных мостов, каждый из которых подключен к выводам соответствующих вторичных обмоток трансформатора, N управляемых ключей, каждый из которых подключен к одному из выводов соответствующего выпрямительного моста, N развязывающих диодов, включенных в обратном направлении между соответствующим управляемым ключом и другим выводом выпрямительного моста, причем все развязывающие диоды включены между собой последовательно и параллельно им включен Г-образный фильтр, а также распределитель импульсов управления ключами 1.

Однако в данном устройстве происходит снижение КПД при переключении ступеней двухтактного транзисторного инвертора, так как транзисторь выходят из области насыщения в активную область на время, необходимое для подзарядки конденсатора выходного фильтра.

Кроме того, быстродействие ограничено величиной емкости фильтра и внутренним сопротивлением инвертора тока, который при переключении ступеней работает в режиме источника тока, -. уровень пульсаций и стабильность ограничены дискретностью схемы электронного переключ-ателя.

Наиболее близким по технической сущности к предлагаемому является стабилизированный конвертор постоянного напряжения, содержащий преобразовательные ячейки, включенные по выходу последовательно, реверсивный счетчик, выходы которого соединены с входами управления преобразовательных ячеек, щиротно-импульсный модулятор, выход которого соединен со входом управления инвертора преобразовательной . ячейки, а модулирующий вход - с выходным выводом, элемент И, включенный в цепи управления реверсивным счетчиком, первый и второй компараторы напряжения и источник опорного напряжения.

При этом между выходом широтно-импульсного модулятора и цепью питания транзисторного инвертора преобразовательной ячейки включен ключевой регулятор напряжения, а для управления реверсивным счетчиком служат цепи обратной связи, связывающие входы реверсивного счетчика через компараторы с выходом конвертора и ключевым регулятором напряжения 2.

Недостатками известного устройства являются низкие КПД н быстродействие, которые обусловлены наличием ключевого регулятора в силовой цепи преобразовательной ячейки и тем, что переключение ячеек происходит в зависимости от напряжения на ключевом регуляторе.

Цель изобретения - повыщение КПД и быстродействия.

Указанная цель достигается тем, что в устройство, содержащее преобразовательные ячейки, включенные по выходу последовательно, реверсивный счетчик, выходы которого соединены с входами управления преобразовательных ячеек, широтно-импульсный модулятор, выход которого соединен с Эходом управления инвертора преобразовательной ячейки, а модулирующий вход - с

5 выходным выводом, первый элемент И, первый и второй компараторы напряжения и источник опорного напряжения, введены второй и третий элементы И, делитель источника опорного напряжения, а преобразовательные ячейки выполнены с общим транзисторо ным интвертором с датчиком тока на входе, при этом первые входы компараторов соеди-. нены с выходным выводом, второй вход первого компаратора соединен с выходом верхнего плеча делителя источника опорного нап5 ряжения, а второй вход второго компаратора - с выходом нижнего плеча делителя источника опорного напряжения, неинвертирующий выход первого ком.паратора через второй элемент И соединен с щиной «-1 реверсивного счетчика, инвертирую0 щий выход второго компаратора через третий элемент И соединен с шиной « + 1 реверсивного счетчика, вторые входы второго и третьего элементов И соединены с вводом тактовых импульсов, третий вход третьего элемента И с выходом датчика тока, инвертирующий выход первого и неинвертирующий выход второго компараторов соединены с соответствующими входами первого двухвходового элемента И, выход которого соединен с входом включения щи0 ротно-импульсного модулятора.

(

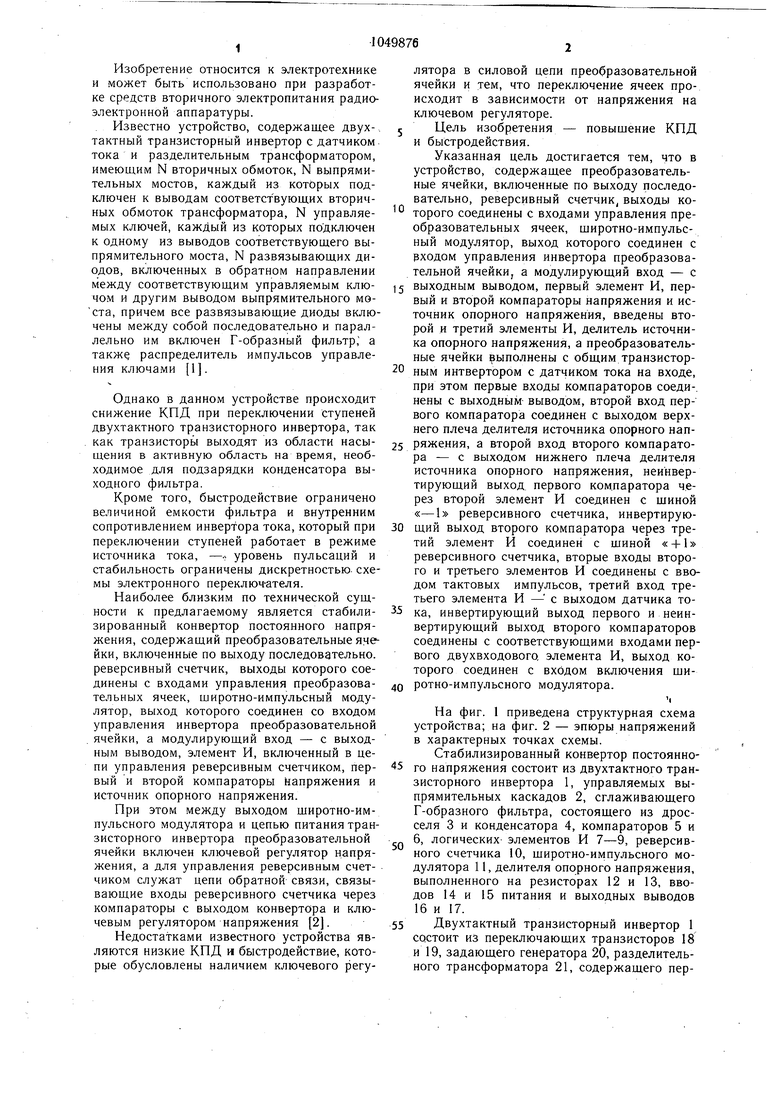

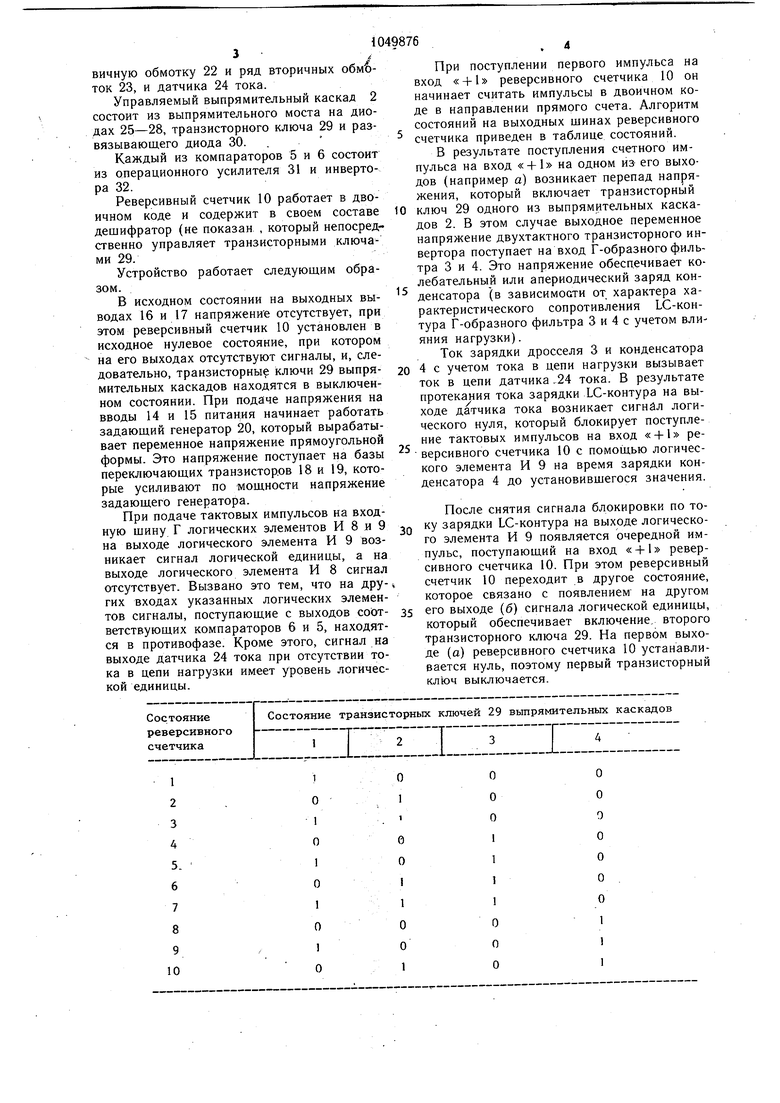

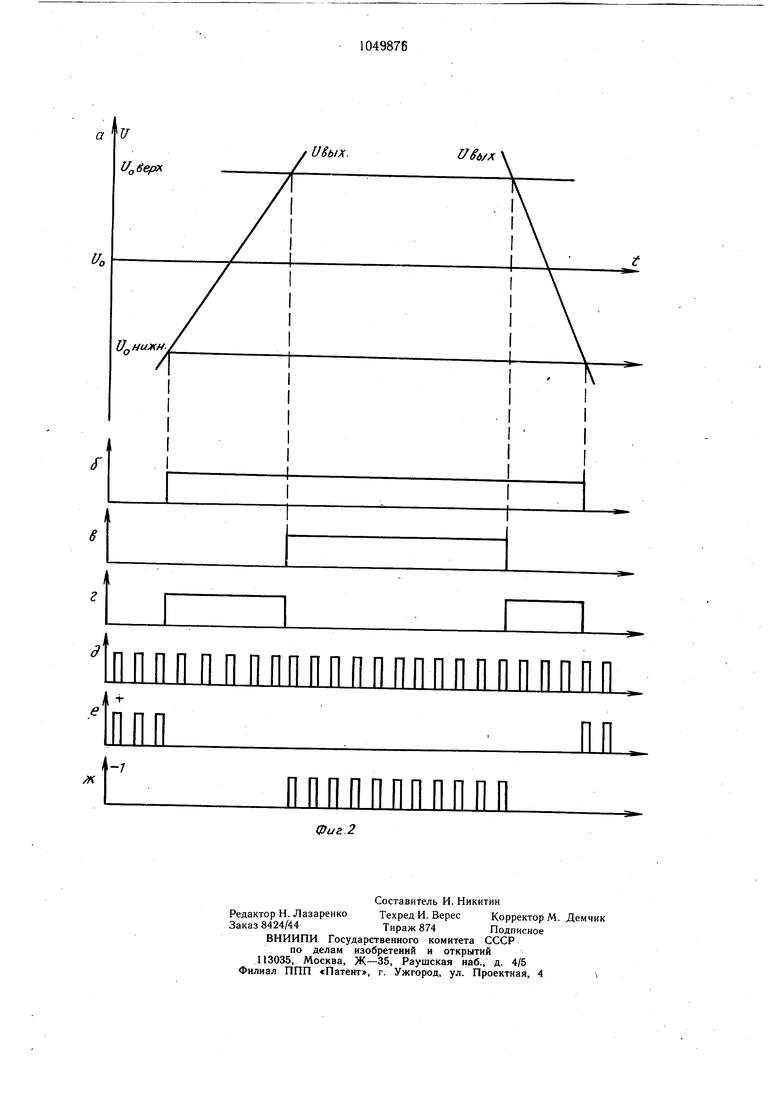

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - эпюры напряжений в характерных точках схемы.

Стабилизированный конвертор постоянно5 го напряжения состоит из двухтактного транзисторного инвертора 1, управляемых выпрямительных каскадов 2, сглаживающего Г-образного фильтра, состоящего из дросселя 3 и конденсатора 4, компараторов 5 и 6, логических элементов И 7-9, реверсивного счетчика 10, щиротно-импульсного модулятора 11, делителя опорного напряжения, выполненного на резисторах 12 и 13, вводов 14 и 15 питания и выходных выводов 16 и 17.

5 Двухтактный транзисторный инвертор 1 состоит из переключающих транзисторов 18 и 19, задающего генератора 20, разделительного трансформатора 21, содержащего вичную обмотку 22 и ряд вторичных обмбток 23, и датчика 24 тока. Управляемый выпрямительный каскад 2 состоит из выпрямительного моста на диодах 25-28, транзисторного ключа 29 и развязывающего диода 30. . Каждый из компараторов 5 и 6 состоит из операционного усилителя 31 и инвертора 32. Реверсивный счетчик 10 работает в двоичном коде и содержит в своем составе дешифратор (не показан , который непосредственно управляет транзисторными ключами 29. Устройство работает следующим образом. В исходном состоянии на выходных выводах 16 и 17 напряжение отсутствует, при этом реверсивный счетчик 10 установлен в исходное нулевое состояние, при котором на его выходах отсутствуют сигналы, и, следовательно, транзисторные ключи 29 выпрямительных каскадов находятся в выключенном состоянии. При подаче напряжения на вводы 14 и 15 питан:ия начинает работать задающий генератор 20, который вырабатывает переменное напряжение прямоугольной формы. Это напряжение поступает на базы переключающих транзисторов 18 и 19, которые усиливают по мощности напряжение задающего генератора. При подаче тактовых импульсов на входную щину Г логических элементов И 8 и 9 на выходе логического элемента И 9 возникает сигнал логической единицы, а на выходе логического элемента И 8 сигнал отсутствует. Вызвано это тем, что на других входах указанных логических элементов сигналы, поступающие с выходов соответствующих компараторов 6 и 5, находятся в противофазе. Кроме этого, сигнал на выходе датчика 24 тока при отсутствии тока в цепи нагрузки имеет уровень логической единицы. 6 При поступлении первого импульса на вход « + 1 реверсивного счетчика 10 он начинает считать импульсы в двоичном коде в направлении прямого счета. Алгоритм состояний на выходных щинах реверсивного счетчика приведен в таблице состояний. В результате поступления счетного импульса на вход « + 1 на одном из его выходов (например а) возникает перепад напряжения, который включает транзисторньш ключ 29 одного из выпрямительных каскадов 2. В этом случае выходное переменное напряжение двухтактного транзисторного инвертора поступает на вход Г-образного фильтра 3 и 4. Это напряжение обеспечивает колебательный или апериодический заряд конденсатора (в зависимости от характера характеристического сопротивления LC-контура Г-образного фильтра 3 и 4 с учетом влияния нагрузки). Ток зарядки дросселя 3 и конденсатора 4 с учетом тока в цепи нагрузки вызывает ток в цепи датчика,24 тока. В результате протекания тока зарядки LC-контура на выходе датчика тока возникает сигнал логического нуля, который блокирует поступление тактовых импульсов на вход «-f 1 реверсивного счетчика 10 с помощью логического элемента И 9 на время зарядки конденсатора 4 до установившегося значения. После снятия сигнала блокировки по току зарядки LC-контура на выходе логического элемента И 9 появляется очередной импульс, поступающий на вход « + 1 реверсивного счетчика 10. При этом реверсивный счетчик 10 переходит в другое состояние, которое связано с появлением на другом его выходе (б) сигнала логической единицы, который обеспечивает включение второго транзисторного ключа 29. На первом выходе (а) реверсивного счетчика 10 устанавливается нуль, поэтому первый транзисторный выключается. В результате очередного скачка напряжения на входе фильтра на такую же величину происходит подзарядка конденсатора. На время подзарядки конденсатора 4 выходной сигнал датчика 24 тока блокирует поступление тактовых импульсов на. вход « + 1 реверсивного счетчика 10 аналогичным образом с помощью логического элемента И 19. Далее процессы в схеме повторяются и происходит включение транзисторных ключей по алгоритму, указанному в таблицею состояний. При каждом переключении обмоток трансформатора напряжение в установившемся состоянии возрастает на постоянную величину. Процесс переключения выходных обмоток 23 с помощью транзисторных ключей 29 происходит до тех пор, пока напряжение на выходе устройства не достигнет нижнего значения опорного напряжения UOHK...При этом происходит срабатывание компаратора 6.J (фиг. 26). В результате срабатывания компаратора 6 блокируется вход « +1 реверсивного счетчика с помощью логического элемента И 9 . и в счетчике прекращается счет импульсов в прямом направлении. Так как сигнал с2 выходов компараторов поступает на вход логического элемента И 7, то с учетом состояний компараторов (фиг. 2,6 и в) на выходе логического элемента И 7 возникает логический сигнал (фиг. 2,г), который включает широтно-импульсный модулятор 11. При включении щиротно-импульсного модулятора И задающий генератор начинает работать в режиме модуляции переменного напряжения по длительности. Глубина модуляции импульсов переменного напряжения3 определяется сигналом обратной связи по выходному напряжению, поступающему vCa второй вход щиротно-импульсного модулятора 11. В этом режиме устройство работает как обычный ключевой регулятор, в котором стабилизация напряжения обеспечивается за счет изменения щирины импульсов. В случае, если выходное напряжение устройства превысит величину заданного напряжения Uojepx . .(фиг. 2,а), срабатывает другой компаратор 5 (фиг. 2,0). При срабатывании компаратора 5 широтно-импульсный модулятор, 11 вык ючается с помощью элемента И 7 совпадения) (фиг. 2, и включается вход «-1 реверсивного счетчика 10, так как на входе логического элемента И 8 будет действовать сигнал логической «1, поступающий с выхода компаратора 5. В этом случае очередной импульс, поступающий на щину тактовых импульсов, сдвигает реверсивный счетчик в обратном направлении, и напряжение на выходе устройства снижается дискретно на заданную величину. Снижение выходного напряжения за счет,тока нагрузки происходит до тех рюр пока устройство не перейдет в зону щиротно-импульсного регулирования (фиг. 2,а). Далее процессы в схеме повторяются, Для больщей ясности на фиг. 2, показаны эпюры напряжений на щине тактовых импульсов, на фиг. 2,е - импульсы на входе « + 1 и на фиг. 2,ж - импульсы на входе «-1 реверсивного счетчика 10 для случая прямого и обратного счета. Выбирая число управляемых выпрямительных каскадов, можно дискретно регулировать выходное напряжение с заданной точностью и значительно повысить степень стабилизации за счет схемы щиротно-импульсного регулирования. В связи с тем, что глубина щиротно-импульсного регулирования импульсов обычно составляет доли процента, предлагаемый конвертор постоянного напряжения обладает рядом преимуществ, которые отсутствуют, в известных устройствах, а именно: - заданный уровень пульсаций обеспечивается применением фильтра с незначительной величиной реактивных элементов; - устройство обладает высоким быстродействием в условиях работы на динамическую нагрузку; - устройство может работать с сохраненнем указанных выще характеристик в щироком диапазоне входных и выходных напряжений, так как форма напряжения не изменяется. )i ЛГ Выход

V U eepif

а

USbiX.

US6/X

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления и защиты преобразователя | 1985 |

|

SU1336171A1 |

| Устройство для управления и защиты преобразователя | 1986 |

|

SU1403281A2 |

| Устройство для управления преобразователем напряжения | 1983 |

|

SU1112525A2 |

| Стабилизированный преобразователь постоянного напряжения | 1983 |

|

SU1121756A1 |

| Стабилизированный конвертор | 1978 |

|

SU811442A2 |

| Усилитель класса Д | 1982 |

|

SU1127074A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Групповой преобразователь частоты | 1987 |

|

SU1436236A2 |

| Устройство регулирования скорости | 1984 |

|

SU1210140A1 |

| Частотно-регулируемый асинхронный электропривод | 1985 |

|

SU1309247A1 |

СТАБИЛИЗИРОВАННЫЙ ИСТОЧНИК ВТОРИЧНОГО Э ТЕКТРОПИТАНИЯ, содержащий преобразовательные ячейки, включенные по выходу последовательно, реверсивный счётчик, выходы которого соединены с входами управления преобразовательных ячеек, широтно- .импульсный модулятор, выход которого соединен с входом управления инвертора преобразовательной ячейки, а модулирующий вход - с выходным выводом, первый элемент И, первый и второй компараторы напряжения и источник опорного напряжения, отличающийся тем, что, с целью повыщения КПД и быстродействия, в него введены второй и третий элементы И, делитель источника опорного напряжения, а преобразовательные ячейки выполнены с общим транзисторным инвертором с датчиком тока на входе, при этом первые входы компараторов соединены с выходньш выводом, второй вход первого компаратора - с ЕГыхбдом верхнего плеча делителя источника опорного напряжения, а второй вход второго компаратора - с выходом нижнего плеча делителя источника опорного напряжения, неинвертирующий выход первого, компаратора через второй элемент И соединен с щиной «-1 реверсивного счетчика, инвертирующий выход второго компаратора через третий элемент И - с шиной « + 1 реверсивного счетчика, вторые входы второго и тред-ьего элементов И SS соединены с вводом тактовых импульсов, третий вход третьего элемента И - с высл ходом датчика тока, инвертирующий вход первого и неинвертирующий выход второго компараторов - с соответствующими входами первого двухвходового элемента И, выход которого соединен с входом включения щиротно-импульсного модулятора. 4 со 00 о:

%

пппоппоопппопппппппооппо 1оппо

-1

о D ШШШММ

ж

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Прибор для подогрева воздуха отработавшими газам и двигателя | 1921 |

|

SU320A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регулируемый преобразователь напряжения | 1978 |

|

SU741387A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1983-10-23—Публикация

1982-01-06—Подача