с первым информационным входом ячейки распределителя импульсов непосредственно, первый вход второго компаратора - через первый масштабный делитель напряжения, второй вход первого компаратора соединен с вторым информационным входом ячейки распределителя импульсов через второй дели тель напряжения, второй вход второго компаратора - непосредственно, выходы компаратора соединены и через элемент задержки подключены к D-BXOду первого триггера, R-входкоторЬго соединен с первым установочным входом ячейки распределителя импульсов, а выход подключен к первым входам логического элемента И и первого элемента ИЛИ, и через формирователь узкого импульса - к второму, информационному выходу ячейки )аспрёделителя импульсов, второй установочный вход которой подключен к второму входу первого логического элемента

ИЛИ, выход которого соединен с R-BXOдом второго триггера, S-вход и Свход которого соединены соответственно с третьим установочным и счетным входами ячейки распределителя импульсов, второй вход логического элемента И соединен с входом сигнала Запрет ячейки распределителя импульсов, выход логического элемента И подключен к первому входу второго логического элемента ИЛИ, второй вход которого соединен с третьим информационным входом ячейки распределителя импульсов, выход второго логического элемента ИЛИ соединен с выходом сигнала Запрет ячейки распределителя импульсов.и D-входом второго триггера, первый выход которого соединен с первым информационным выходом ячейки распределителя импульсов, а второй выход подключен к С-входу первого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Устройство для управления многофазным импульсным регулятором | 1981 |

|

SU957411A1 |

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1624458A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Многофазный импульсный стабилизатор постоянного напряжения (его варианты) | 1984 |

|

SU1157532A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1985 |

|

SU1348801A1 |

1. МНОГОФАЗНЫЙ ИЬШУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ, содержащий силовой блок, включающий Е себя N параллельно соединенных преобразовательных ячеек, минусовые выводы которых подключены к выходной клемме стабилизатора через соответствующие датчики тока, и блок управления, включающий для каждой преобразовательной ячейки ячейку распределителя тактовых импульсов, сумматор сигналов рассогласования и широтноимпульсный модулятор, а также перестраиваемый генератор тактовых импульсов, усилители рассогласования пс току и напряжению с блоком опорных напряжений, причем плюсовые выводы преобразовательных ячеек подключены через усилитель рассогласования по напряжению к первым входам сумматоров, выходы которых соединены с пер-, выми входами соответствующих широт.но импульсных модуляторов, вторые :входы которых соединены с информационными выходами сигнала Тактовый импульс соответствующих ячеек распределителя импульсов, выходы широтно-импульсных модуляторов подключены к входам соответствующих преобразовательных ячеек, минусовые выводы которых подключены к первым ий- . формаадюнным входам ячеек ргспределнтеля импульсов,.счетные вхрды кото- , рых подключены к выходу перестраива емого генератора тактовых импульсов, отличающий с,я тем, что, с целью унификации при одновременном повышении надежности, введены блок подсчета неисправностей и блок симметрирования, при этом вторые информационные выходы распределителей ИМ7 пульсов подключены к входу блока подсчета Неисправностей, выход которого соединен с входом перестраиваемого генератора тактовых импульсов, минусовые выходы преобразовательных ячеек подключены к входам блока симметрирования, первый выход которого подключен к вторым информационным входам ячеек распределителя импульсов непосредственно и через усилитель рассогласования по току к вто(/) С рым входам сумматоров, второй, третий и четвертый выходы блока симметрирования подключены соответственfeo к третьим входам сумматоров, nep-J вые и вторые установочные входы ячеекg ра.спределителя импульсов подключены к входу Установка многофазного им пульсного стабилизатора, кроме второго установочного входа первой ячейки .распределителя импульсов, который сое динен с минусовой шиной, к минусовой шине подключены также третьи установочные входы ячеек распределителя импульсов, кроме третьего установочного входа первой ячейки распределителя импульсов, который соединен с входом Установка, а по сигналам и Тактовый импульс 3 апрет ячейки распределителя тактовых импульсов соединены в кольцо. 2. Стабилизатор по п. 1 отличающийся тем, что ячейка распределителя тактовых импульсов содержит два масштабных делителя на-, пряжения, два компаратора, элемент задержки, формирователь узкого импульса, два D-триггера, элемент И два элемента ИЛИ, при этом первый вход первого компаратора соединен

Изобретение относится к электротехнике, в частности к устройствам стабилизации постоянного напряжения, И может быть использовано в системах .электропитания повышенной надежности . Известен многофазный импульсный стабилизатор постоянного напряжения, содержащий силовую часть и блок управления. Силовая часть содержит четь8 е параллельно соединенные ключевые гфеобразовательные ячейки, каждая из которых содержит блок ключевых транзисторов и LCD-фильтры. Блок управления содержит для каждой из ячеек шкротно-импульсные модуляторы, предусилители, измерительные устройства, генераторы тактовых импульсов и распределитель импульсов. Ключевая преобразовательная ячейка выполнена по.схеме однотактного понижающего импульсного стабилизатора постоянного напряжения. Управление ключевыми транзисторами обеспечивается широтно-импульсным модулятором с предусилителем и измерительным устройст-г вом. Сдвиг во времени в коммутации транзисторов осуществляется распределителем импульсов, выполненным на основе УК-триггеров С1.

Недостатком устройства являются провалы выходного напряжения при отказе хотя бы одной преобразовательной ячейки, так как жесткость связей не позволяет перестроить работу исправных преобразовательных ячеек таким образом, чтобы сохранялся заданный сдвиг во времени. Кроме того, устройство имеет низкий уровень безотказности и ремонтопригодности стабилизатора в целом, что связано с централизованным блоком управления.

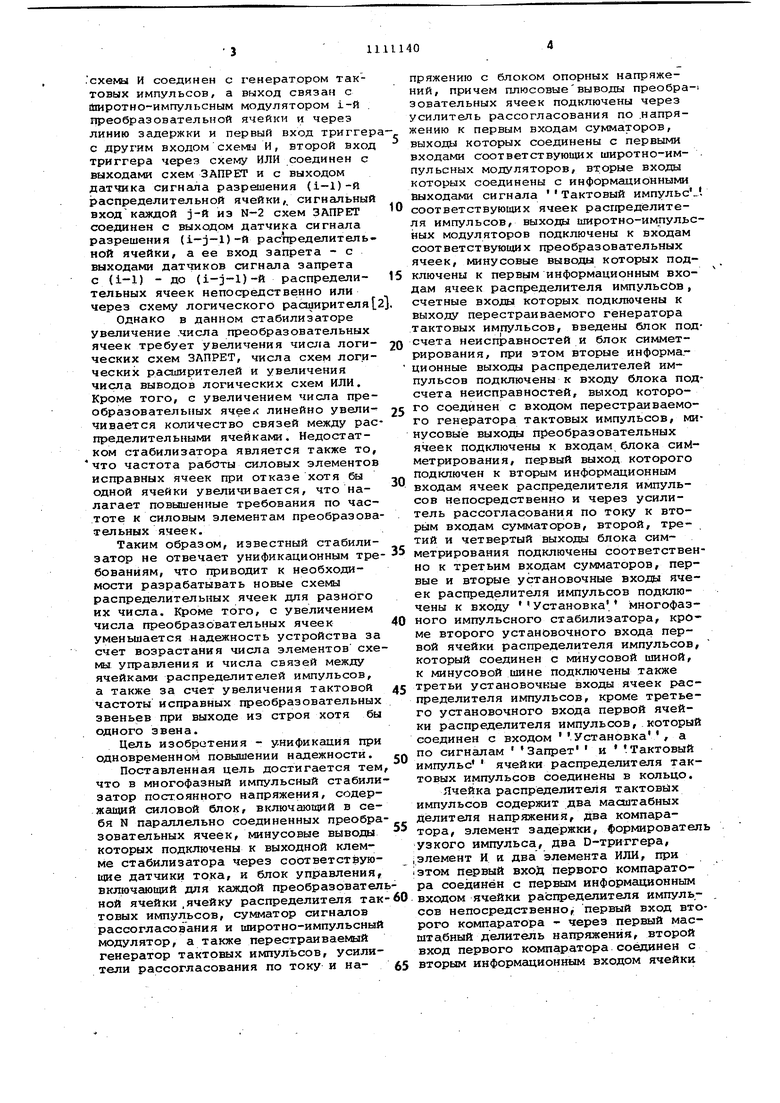

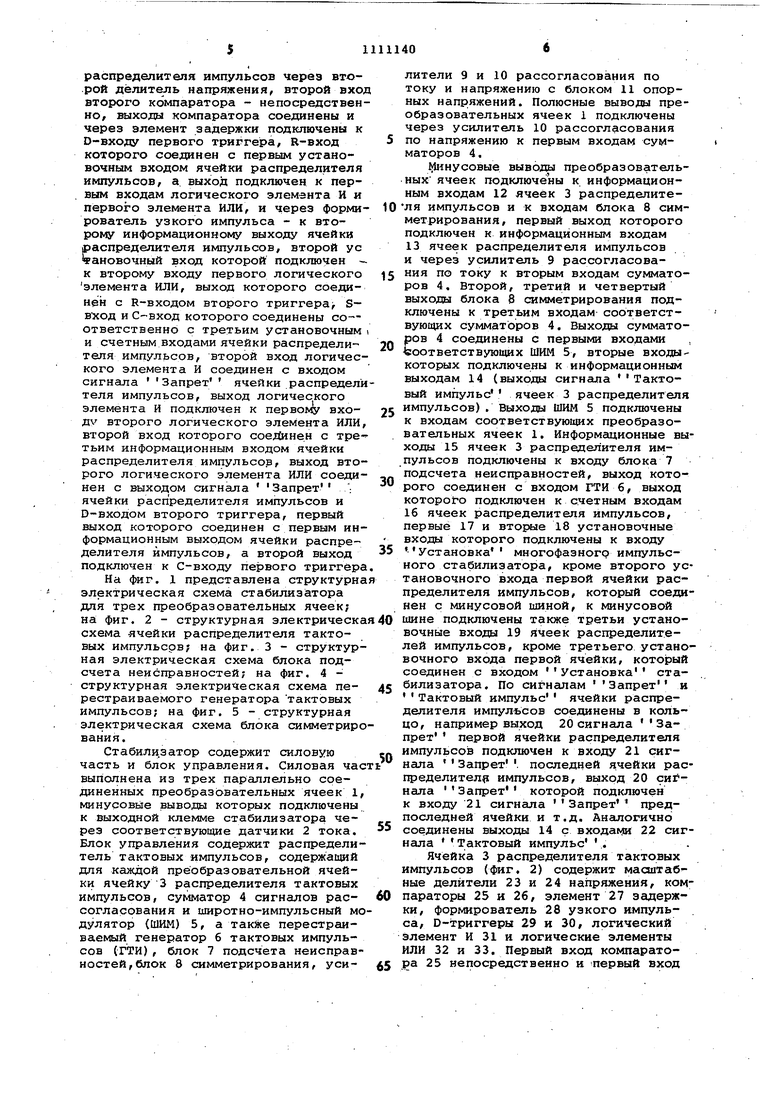

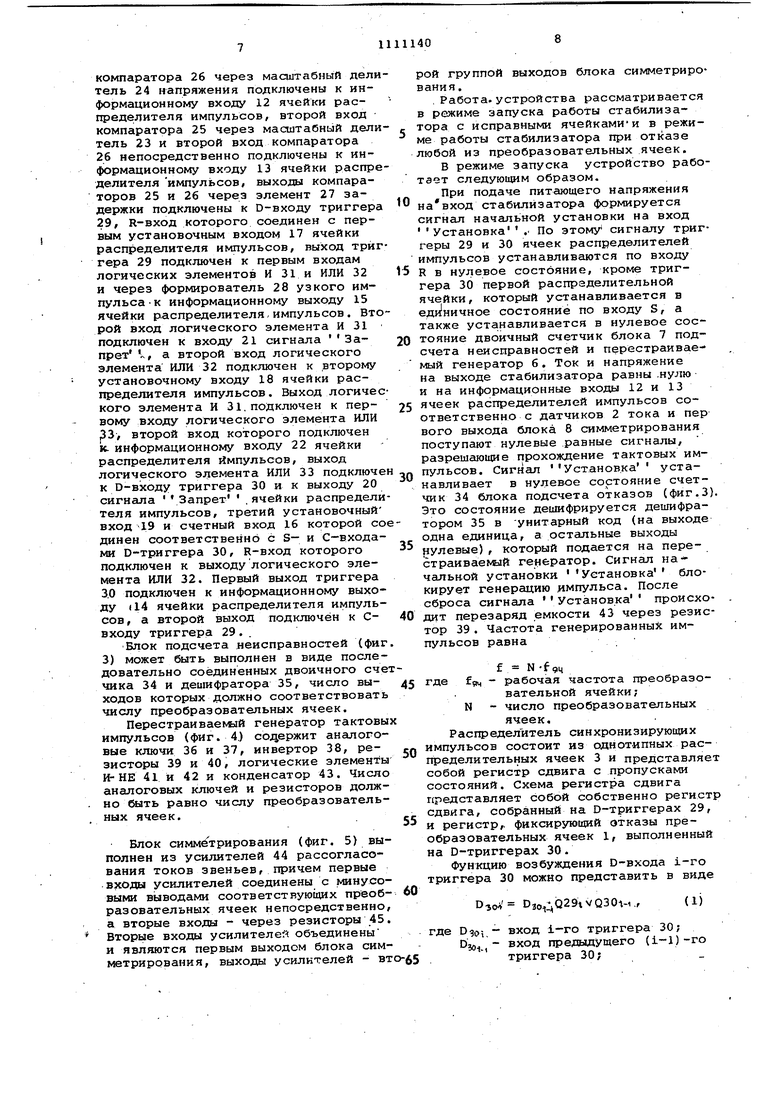

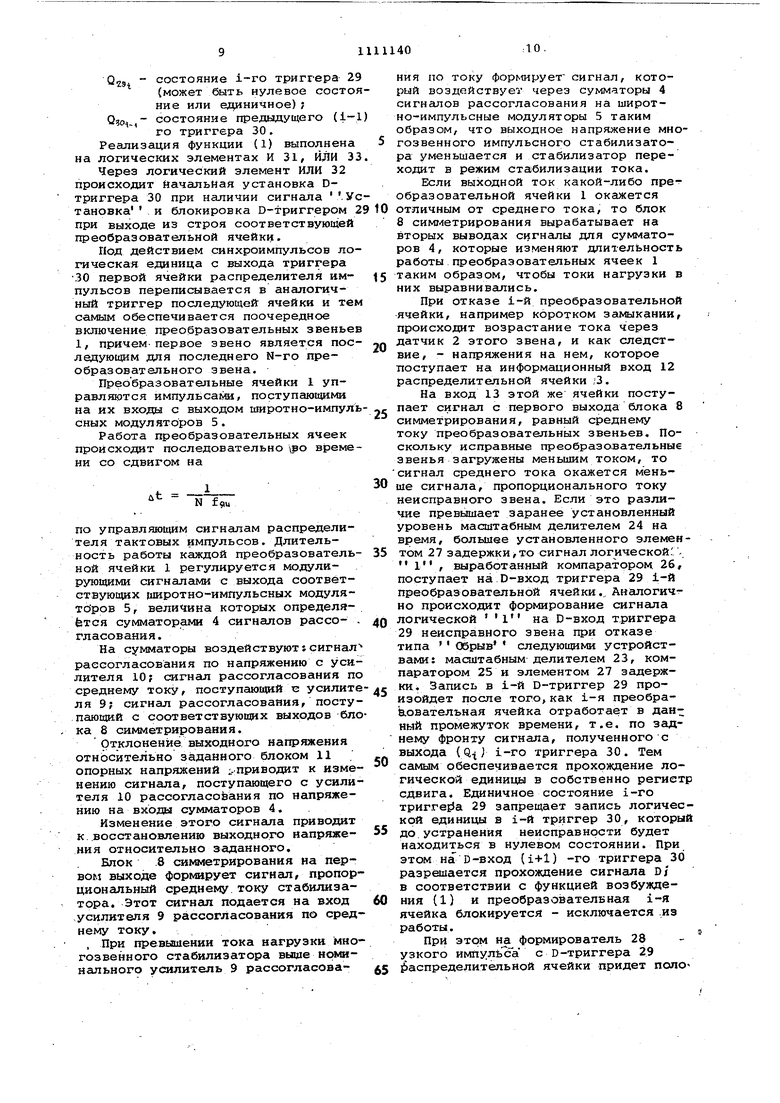

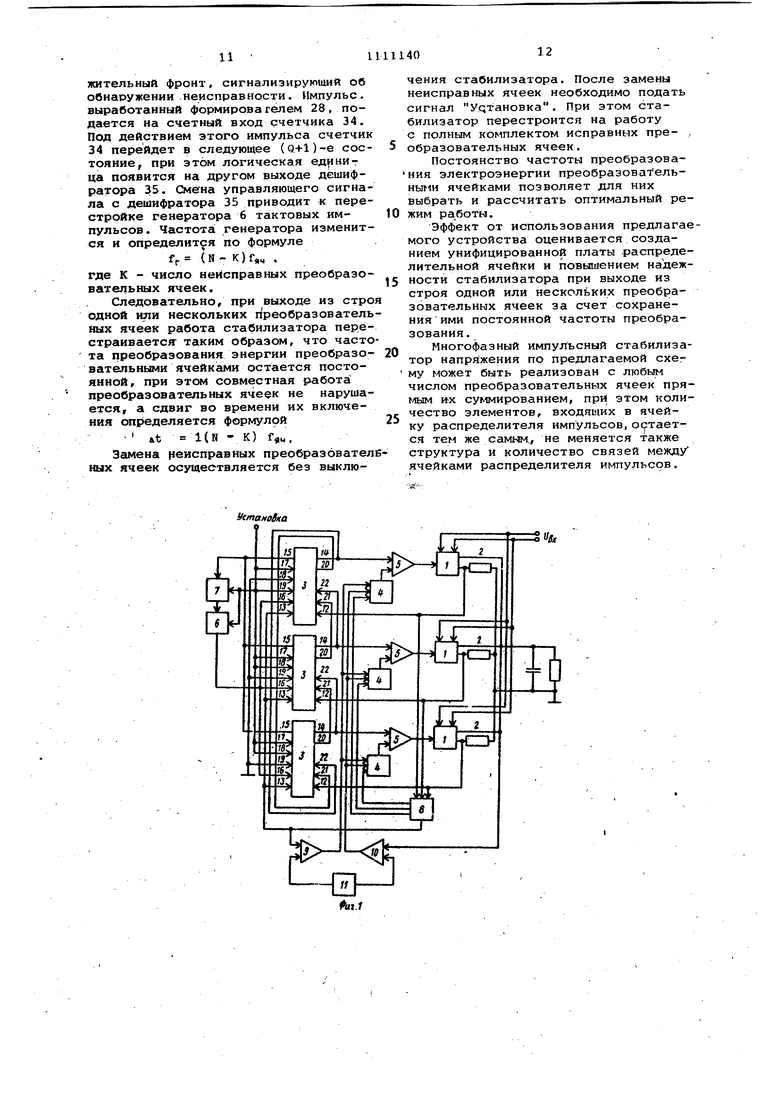

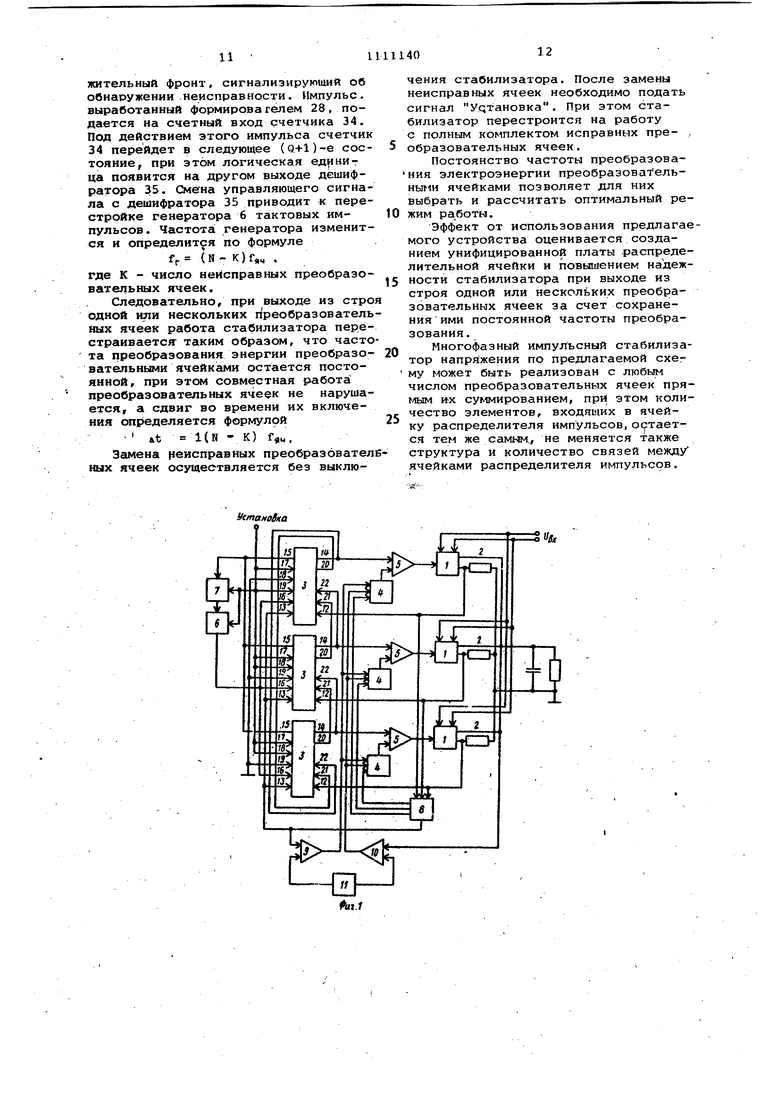

Наиболее близким к предлагаемому является многофазный импульсный ста.билизатор постоянного напряжения, содержащий силовой блок, включающий в, себя N параллельно соединенных ключевых преобразовательных ячеек, каждая из которых содержит блок ключевых транзисторов и ЬСО-фильтЕял и бло 5)правления. Блок управления содержит широтно-импульсные модуляторы, выходами подключенные К входам.: соответствующих преобразовательных ячеек а входами - к выходам соответствующи предусилителей, измерительные блоки, входами подключенные к выходным выводам стабилизатора, а выходами к входам соответствующих предусилителей , генераторы тактовых импульсов по числу преобразовательных ячеек, подключенные к входам распределителя тактовых импульсов, выходы которого подключены к каждому из предусилителей. Распределитель тактовых импульсов выполнен из N распределительных ячеек, каждая из которых содержит логическую схему И, (N-2) логических схем ЗАПРЕТ, логическую схему ИЛИ, триггер, линию задержки, схему логического расширителя, датчик сигнала запрета, датчик сигнала разрешения, при 3toM датчики подключены к дросселю LCDфильтра i-й преобразовательной ячейки непосредственно или через согласующий трансформатор, один из входов .схемы И соединен с генератором тактовых импульсов, а выход связан с йзиротно-импульсным модулятором i-й преобразовательной ячейки и через линию задержки и первый вход триггер с другим входом схемЕЛ И, второй вход триггера через схему ИЛИ соединен с выходами схем ЗАПРЕТ и с выходом датчика сигнала разрешения (1-1)-и распределительной ячейки,, сигнальный входкаждой j-й иэ N-2 схем ЗАПРЕТ соединен с выходом датчика сигнала разрешения (i-j-1)-й распределительной ячейки, а ее вход запрета - с выходами датчиков сигнала запрета с (1-1) - до (i-j-)-й распределительных ячеек непосредственно или через схему логического расширителя Однако в данном стабилизаторе увеличение .числа преобразовательных ячеек требует увеличения числа логических схем ЗАПРЕТ, числа схем логических расширителей и увеличения числа выводов логических схем ИЛИ. Кроме того, с увеличением числа преобразовательных ячеех линейно увеличивается количество связей между рас пределительными ячейками. Недостатком стабилизатора является также то, что частота работы силовых элементов исправных ячеек при отказе хотя бы одной ячейки увеличивается, что налагает повышенные требования по частоте к силовым элементам преобразова тельных ячеек. Таким образом, известный стабилизатор не отвечает унификационным тре бованиям, что приводит к необходимости разрабатывать новые схемы распределительных ячеек для разного их числа. Кроме того, с увеличением числа преобразовательных ячеек уменьшается надежность устройства за счет возрастания числа элементов схе мы управления и числа связей между ячейками распределителей импульсов, а также за счет увеличения тактовой частоты исправных преобразовательных звеньев при выходе из строя хотя бы одного звена. Цель изобретения - у.нификация при одновременном повьниении надежности. Поставленная цель достигается тем что в многофазный импульсный стабили затор постоянного напряжения, содержащий силовой блок, включающий в себя N параллельно соединенных преобра зовательных ячеек, минусовые выводы которых подключены к выходной клемме стабилизатора через соответствующие датчики тока, и блок управления, включающий для каждой преобразовател ной ячейки .ячейку распределителя так товых импульсов, сумматор сигналов рассогласования и широтно-импульсный модулятор, а также перестраиваемый генератор тактовых импульсов, усилители рассогласования по току и напряжению с блоком опорных напряжений, причем плюсовыевыводы преобра-i зовательных ячеек подключены через усилитель рассогласования по .напряжению к первым входам сумматоров, выходы которых соединены с первыми входами соответствующих широтно-им- . пульсных модуляторов, вторые входы которых соединены с информационными Выходами сигнала Тактовый импульс., соответствующих ячеек распределителя импульсов, выходы широтно-и1 ульсных модуляторов подключены к входам соответствующих преобразовательных ячеек, минусовые выводы которых подключены к первым информационным входам ячеек распределителя импульсов, счетные входы которых подключены к выходу перестраиваемого генератора тактовых импульсов, введены блок подсчета неисправностей и блок симметрирования, при этом вторые информа.ционные выходы распределителей импульсов подключены к входу блока подсчета неисправностей, выход которого соединен с входом перестраиваемого генератора тактовых импульсов, минусовые выходы преобразовательных ячеек подключены к входам блока симметрирования, первый выход которого подключен к вторым информационным входам ячеек распределителя импульсов непосредственно и через усилитель рассогласования по току к вторым входам сумматоров, второй, третий и четвертый выходы блока симметрирования подключены соответственно к третьим входам сумматоров, первые и вторые установочные входу ячеек распределителя импульсов подключены к входу Установка многофазного импульсного стабилизатора, кроме второго установочного входа первой ячейки распределителя импульсов, который соединен с минусовой шиной, к минусовой шине подключены также третьи установочные входы ячеек распределителя импульсов, кроме третьего установочного входа первой ячейки распределителя импульсов, который соединен с входом .Установка , а по сигналам Запрет и .Тактовый импульс ячейки распределителя тактовых импульсов соединены в кольцо. Ячейка распределителя тактовах импульсов содержит два масштабных делителя напряжения, два компаратора, элемент задержки, формирователь узкого импульса, два D-тритгера, элемент И и два элемента ИЛИ, при этoм первый вход первого компаратора соединён с первым информационным входом ячейки распределителя импуль- . сов непосредственно, первый вход второго компаратора - через первый масштабный делитель напряжения, второй вход первого компаратора соединен с вторым информационным входом ячейки распределителя импульсов через второй делитель напряжения, второй вхо второго компаратора - непосредствен но, выходы компаратора соединены и через элемент задержки подключены к D-входу первого триггера, R-вход которого соединен с первым установочным входом ячейки распределителя импульсов, а выход подключен к первым входам логического элемента И и первого элемента ИЛИ, и через форми рователь узкого импульса - к второму информационному выходу ячейки распределителя импульсов, второй ус чрановочный вход которой подключен к второму входу первого логического элемента ИЛИ, выход которого соединен с R-входом второго триггера S- вход и С-вход которого соединены со- ответственно с третьим установочным и счетным входами ячейки распределителя импульсов, второй вход логичес кого элемента И соединен с входом сигнала Запрет ячейки.распредели теля импульсов, выход логического элемента И подключен к первому входу второго логического элемента ИЛИ второй вход которого соединен с тре тьим информационным входом ячейки распределителя импульсов, выход вто рого логического элемента ИЛИ соедиЗапретнен с выходом сигнала ячейки распределителя импульсов и D-входом второго триггера, первый выход которого соединен с первым информационным выходом ячейки распределителя импульсов, а второй выход подключен к С-входу первого триггера На фиг. 1 представлена структурна электрическая схема стабилизатора для трех преобразовательных ячеек; на фиг. 2 - структурная электрическа схема -ячейки распределителя тактовых импульсов; на фиг. 3 - структурная электрическая схема блока подсчета неисправностей; на фиг. 4 структурная электрическая схема перестраиваемого генератора тактовых импульсов; на фиг. 5 - структурная электрическая схема блока симметриро вания. Стабили.затор содержит силовую часть и блок управления. Силовая час выполнена из трех параллельно соединенных преобразовательных ячеек 1 минусовые выводы которых подключены к выходной клемме стабилизатора через соответствующие датчики 2 тока. Блок управления содержит распределитель тактовых импульсов, содержащий для каждой преобразовательной ячейки ячейку 3 распределителя тактовых импульсов, сумматор 4 сигналов рассогласования и широтно-импульсный мо дулятор (ШИМ) 5, а такйсе перестраиваемый генератор 6 тактовых импульсов (ТТИ), блок 7 подсчета неисправностей, блок 8 симметрирования, усилители 9 и 10 рассогласования по току и напряжению с блоком 11 опорных напряжений. Полюсные выводы преобразовательных ячеек 1 подключены через усилитель 10 рассогласования по напряжению к первым входам сумматоров 4. 1 1инусовые вывода преобразовательных ячеек подключены к информационным входам 12 ячеек 3 распределителя импульсов и к входам блока 8 симметрирования, первый выход которого подключен к информационным входам 13 ячеек распределителя импульсов и через усилитель 9 рассогласования по току к вторым входам сумматоров 4. Второй, третий и четвертый выходы блока 8 симметрирования подключены к третьим входам соответствующих Сумматоров 4. Выходы сумматоров 4 соединены с первыми входс1ми Соответствующих ШИМ 5, вторые входыкоторых подключены к информационным выходам 14 (выходы сигнгша Тактовый импульс ячеек 3 распределителя импульсов). Выходы ШИМ 5 подключены к входам соответствующих преобразовательных ячеек 1. Информационные выходы 15 ячеек 3 распределителя импульсов подключены к входу блока 7 подсчета неисправностей, выход которого соединен с входом ГТИ 6, выход которого подключен к счетным входам 16 ячеек распределителя импульсов, первые 17 и вторые 18 установочные входы которого подключены к входу Установка многофазного импульсного стабилизатора, кроме второго установочного входа первой ячейки распределителя импульсов, который соединен с минусовой шиной, к минусовой шине подключены также третьи установочные входы 19 я:чеек распределителей импульсов, кроме третьего установочного входа первой ячейки, который соединен с входом Установка стабилизатора. По сигналам Запрет и Тактовый импульс ячейки распределителя импульсов соединены в кольцо, например выход 20 сигнала Запрет первой ячейки распределителя импульсов подключен к входу 21 сигнала Запрет . последней ячейки распределителр импульсов, выход 20 сигнала Запрет которой подключен к входу 21 сигнала Запрет предпоследней ячейки и т.д. Анешогично соединены выходы 14 с входами 22 сигнала Тактовый импульс . Ячейка 3 распределителя тактовых импульсов {фиг, 2) содержит масштабные делители 23 и 24 напряжения, компараторы 25 и 26, элемент 27 задержки, формирователь 28 узкого импульса, D-триггеры 29 и 30, логический элемент И 31 и логические элементы ИЛИ 32 и 33. Первый вход компаратора 25 непосредственно к первый вход

компаратора 26 через масштабный делитель 24 напряжения подключены к информационному входу 12 ячейки распределителя импульсов, второй вход компаратора 25 через масштабный дели- , тель 23 и второй вход компаратора 26 непосредственно подключены к информационному входу 13 ячейки распределителя импульсов, выходы компараторов 25 и 26 через элемент 27 задержки подключены к D-входу триггера 29, R-вход которого соединен с первым установочным входом 17 ячейки распределителя импульсов, выход триггера 29 подключен к первым входам логических элементов И 31 и ИЛИ 32 15 и через формирователь 28 узкого импульса -к информационному выходу 15 ячейки распределителя,импульсов. Второй вход логического элемента И 31 подключен к входу 21 сигнала За- 20 прет V, а второй вход логического элемента ИЛИ 32 подключен к второму установочному входу 18 ячейки распределителя импульсов. Выход логического элемента И 31,подключен к пер- 25 вому входу логического элемента ИЛИ 33, второй вход которого подключен к- информационному входу 22 ячейки распределителя импульсов, выход логического элемента ИЛИ 33 подключен „ к D-входу триггера 30 и к выходу 20 сигнала Запрет .ячейки распределителя импульсов, третий установочный вход-19 и счетный вход 16 которой соединен соответственно с S- и С-входами D-триггера 30, R-вход которого 35 подключен к выходулогического элемента ИЛИ 32. Первый выход триггера 3.0 подключен к информационному выходу (14 ячейки распределителя импульсов , а второй выход подключён к С- 40 входу триггера 29..

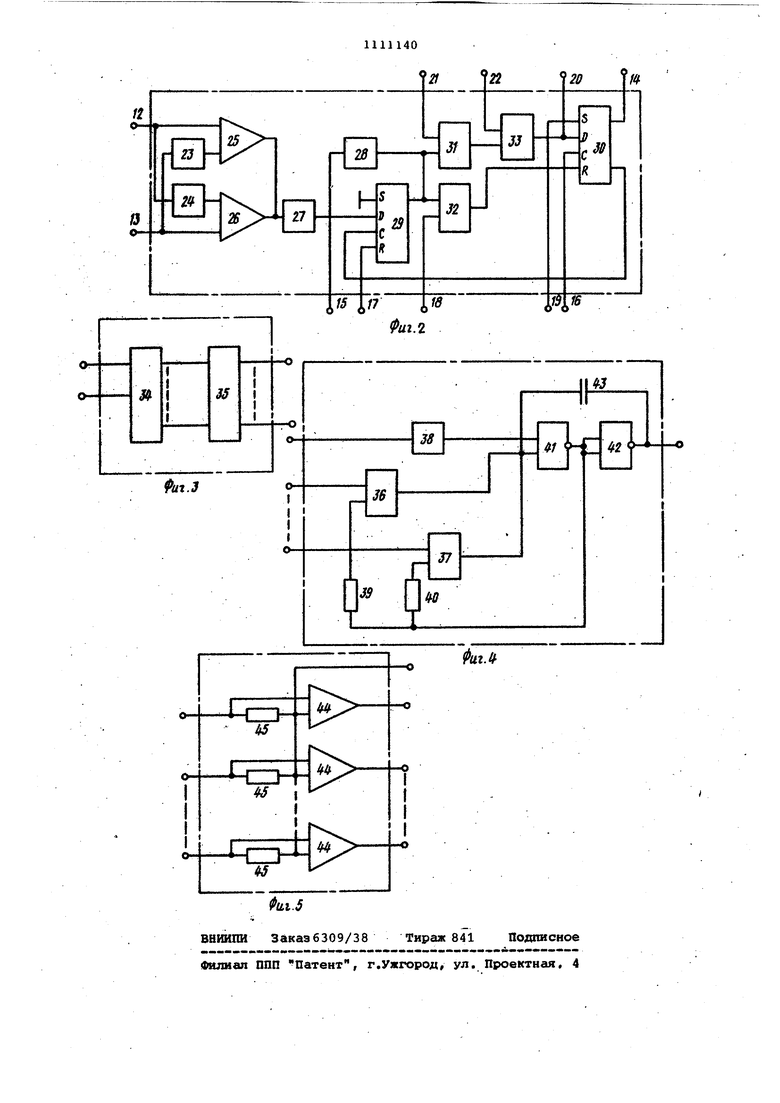

Блок подсчета неисправностей (фиг. 3) может быть выполнен в виде последовательно соединенных двоичного счетчика 34 и дешифратора 35, число вы- 45 ходов которых должно соответствовать числу преобразовательных ячеек.

Перестраиваемый генератор тактовых импульсов (фИг. 4.) содержит аналоговые ключи 36 и 37, инвертор 38, ре- ,,. зисторы 39 и 40, логические элементы И-НЕ 41 и 42 и конденсатор 43. Число аналоговых ключей и резисторов должно быть равно числу преобразовательных ячеек.

Блок симмётрирования (фиг. 5) выполнен из усилителей 44 рассогласования токов звеньев, причем первые входы усилителей соединены с минусовыми выводами соответствующих преоб- 60 разовательных ячеек непосредственно, а вторые входы - через резисторы 45. Вторые входы усилителей объединены и являются первым выходом блока симметрирования, выходы усилителей -

рой группой выходов блока симметрирования.

. Работа, устройства рассматривается в режиме запуска работы стабилизатора с исправными ячейкамии в режиме работы стабилизатора при отказе любой из преобразовательных ячеек.

В режиме запуска устройство работает следующим образом.

При подаче питающего напряжения навход стабилизатора формируется сигнал начальной установки на вход Установка. По этому сигналу триггеры 29 и 30 ячеек распределителей импульсов устанавливаются по входу R в нулевое состояние, кроме триггера 30 первой распределительной ячейки, который устанавливается в ед1 ничное состояние по входу S, а также устанавливается в нулевое состояние двоичный счетчик блока 7 подсчета неисправностей и перестраиваемый генератор 6. Ток и напряжение на выходе стабилизатора равны .нулю и на информационные входы 12 и 13 ячеек распределителей импульсов соответственно с датчиков 2 тока и пер вого выхода блока 8 симметрирования поступают нулевые равные сигналы, разрешгиощие прохождение тактовых импульсов. Сигнал Установка устанавливает в нулевое состояние счетчик 34 блока подсчета отказов (фиг.З Это состояние дешифрируется дешифратором 35 в -унитарный код (на выходе одна единица, а остальные выходы нулевые), который подается на перестраиваемый генератор. Сигнал начальной установки Установка блокирует генерацию импульса. После сброса сигнала Установка происходит перезаряд емкости 43 через резистор 39 . Частота генерированных импульсов равна

f N-f94

где уц - рабочая частота преобразовательной ячейки; N - число преобразовательных

ячеек.

Распределитель синхронизирующих импульсов состоит из однотипных распределительных ячеек 3 и представляе собой регистр сдвига с пропусками состояний. Схема регистра сдвига представляет собой собственно регист сдвига, собранный на D-триггерах 29, и регистр,, фиксирующий отказы преобразовательных ячеек 1, выполненный на D-триггерах 30.

Функцию возбуждения D-входа i-ro триггера 30 можно представить в виде

(1)

D W D30i:,Q29t VQ30vi .f

где , вход i-го триггера 30;

Djj,.,, - вход предыдущего (1-1)-го триггера 30; - состояние i-го триггера 2 (может быть нулевое состо ние или единичное); ., состояние предыдущего (1го триггера 30. Реализация функции (1) выполнена на логических элементах И 31, ИЛИ 3 Через логический элемент ИЛИ 32 происходит йачальмая установка Dтриггера 30 при наличии сигнала .У тановка и блокировка D-триггером при выходе из строя соответствующей преобразовательной ячейки. Под действием синхроимпульсов ло гическая единица с выхода триггера -.30 первой ячейки распределителя импульсов переписывается в аналогичный триггер последующей ячейки и те самым обеспечивается поочередное включение преобразовательных звенье 1, причем-первое звено является пос ледующим для последнего N-ro преобразовательного звена. Преобразовательные ячейки 1 управляются импульсами, поступающими на их входы с выходом широтно-импул сных модуляторов 5. Работа преобразовательных ячеек происходит последовательно ро време ни со сдвигом на по управляющим сигналам распределителя тактовых импульсов. Длительность работы каждой преобразователь ной ячейки 1 регулируется модулирующими сигналами с выхода соответствующих широтно-импульсных модуляторов 5, величина которых определиётся сумматорами 4 сигналов рассогласования. На сумматоры воз действуют «сиг нал рассогласования по напряжению с уси лителя 10; сигнал рассогласования по среднему току, поступающий с усилит ля 9; сигнал рассогласования, посту пающий с соответствующих выходов бло ка 8 симметрирования. Отклонение выходного напряжения относительно заданного блоком 11 опорных напряжений .приводит к изме нению сигнала, поступающего с усили теля 10 рассогласойания по напряжению на входы сумматоров 4, Изменение этого сигнала приводит к восстановлению выходного напряжеВИЯ относительно заданного. Блок 8 симметрирования на первом выходе формирует сигнал, пропор циональный среднему току стабилизатора. Этот сигнал подается на вход усилителя 9 рассогласования по сред нему току. , При превышении тока нагрузки мно гозвенного стабилизатора выше номинального усилитель 9 рассогласования по току форьотрует сигнал, который воздййствует через сумматоры 4 сигналов рассогласования на широтно-импульсные модуляторы 5 таким образом, что выходное напряжение многозвенного импульсного стабилизатора уменьшается и стабилизатор переходит в режим стабилизации тока. Если выходной ток какой-либо преобразовательной ячейки 1 окажется отличным от среднего тока, то блок 8 симтлетрирования вырабатывает на вторых выводах сигналы для сумматоров 4, которые изменяют длительность работы преобразовательных ячеек 1 таким образом, чтобы токи нагрузки в них выравнивсшись. При отказе i-й преобразовательной ячейки, например коротком замыкании, происходит возрастание тока через датчик 2 этого звена, и как следствие, - напряжения на нем, которое поступает на информационный вход 12 распределительной ячейки ;3. На вход 13 этой же ячейки поступает сигнал с первого выхода блока 8 симметрирования, равный среднему току преобразовательных звеньев. Поскольку исправные преобразовательные звенья загружены меньшим током, то сигнал среднего тока окажется меньше сигнала, пропорционального току неисправного звена. Если это различие превышает заранее установленный уровень масштабным делителем 24 на время, большее установленного элементом 27 задержки то сигнал логической. . 1, выработанный компаратором 26, поступает на.D-вход триггера 29 1-й преобразовательной ячейки.. Аналогично происходит формирование сигнала логической на D-вход триггера 29 неисправного звена при отказе типа СЗбрыв следующими устройствами: масштабным делителем 23, компаратором 25 и элементом 27 задержки. Запись в i-й D-триггер 29 произойдет после того,как i-я преобраЬ.ователъная ячейка отработает в данный промежуток времени, т.е. по заднему фронту сигнала, полученного с выхода ( 1-го триггера 30. Тем самым обеспечивается прохождение логической единицы в собственно регистр сдвига. Единичное состояние i-ro триггера 29 запрещает запись логической единицы в i-й триггер 30, который до устранения неисправности будет находиться в нулевом состоянии. При этом на D-вход (i+l) -го триггера 30 разрешается прохождение сигнала D/ в соответствии с функцией возбуждения (1) и преобразователБная i-я ячейка блокируется - исключается из работы. При этом н формирователь 28 - узкого импульса с о-триггера 29 распределительной ячейки придет положительный фронт, сигнализирующий об обнаружении неисправности. Импульс. выработанный формирователем 28, подается на счетный вход счетчика 34. Под действием этого импульса счетчик 34 перейдет в следующее (о+1)-е состояние, при этом логическая ца появится на другом выходе дешифратора 35. Смена управляющего сигнала с дешифратора 35 приводит к перестройке генератора 6 тактовых импульсов . Частота: генератора изменится и определится по формуле fr (Н- К)Г,ц . где К - число неисправных преобразовательных ячеек. Следовательно, при выходе из стро одной И71И нескольких преобразователь ных ячеек работа ста15илизатора перестраивается таким образом, что часто та преобразования энергии преобразовательными ячейками остается постоянной, при этом совместная работа преобразовательных ячеек не нарушается, а сдвиг во времени их включения определяется формулой fct 1(N - К) f,«. Замена неисправных преобразовател ных ячеек осуществляется без выклюУстановка

Ч, чения стабилизатора. После замены неисправных ячеек необходимо подать сигнал yqfaHOBKa. При этом стабилизатор перестроится на работу с полным комплектом исправных пре- , образовательных ячеек. Постоянство частоты преобразования электроэнергии преобразовательныпи ячейками позволяет для них выбрать и рассчитать оптимальный режим ра,боты. Эффект от использования предлагаемого устройства оценивается созданием унифицированной платы распределительной ячейки и повышением надежности стабилизатора при выходе из строя одной или нескольких преобразовательных ячеек за счет сохранения ими постоянной частоты преобразования. Многофазный импульсный стабилизатор напряжения по предлагаемой схег му может быть реализован с любым числом преобразовательных ячеек пряr ibiM их суммированием, при этом количество элементов, входящих в ячейку распределителя импульсов, остается тем же самым., не меняется также структура и количество связей между ячейками распределителя импульсов.

/2 о-

г{

23

ч

Zl

/9 о

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электронная техника в автомагике | |||

| Под ред | |||

| Ю.И.Конева | |||

| Вып | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Способ получения на волокне оливково-зеленой окраски путем образования никелевого лака азокрасителя | 1920 |

|

SU57A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для охлаждения водою паров жидкостей, кипящих выше воды, в применении к разделению смесей жидкостей при перегонке с дефлегматором | 1915 |

|

SU59A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1980 |

|

SU935914A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-08-30—Публикация

1983-04-07—Подача