гера состояния, D -вход которого соединен с общей шиной, а С -вход с С -входом выходного регистра и выходом элемента И, второй вход которого подключен к выходу порогрвого блока, а третий - к пятым входам элементов И-ИЛИ-НЕ суммирования и вычитания и выходу X) -триггера переноса, ГЬвход которого соединен с общей шиной, а С -вход - с первым выходом реверсивного счетчика,С -вход которого соединен с выходом элемента И-ИЛИ ХЕ предустановки, первый вход с выходом элемента И-ИЛИ-НЕ суммиро« ния, второй вход - с выходомэлемета И-ИЛИ-НЕ вычитания, информационные входы - с соответствующими выходами оперативного аапоминащего устройства, а выходы - с входами порогового блока и информационными входами оперативного запоминающего устройства, управляющие входы которого под ключены к соответствующим выходам основного счетчика, выход старшего разряда которого соединен с входом блока предварительной записи,R -вход с вторым выходом этого блока, а С-вход - с выходом старшего разряда вспомогательного счет ча.I .

| название | год | авторы | номер документа |

|---|---|---|---|

| Сенсорный переключатель | 1986 |

|

SU1401593A2 |

| Сенсорный переключатель | 1987 |

|

SU1474837A2 |

| Сенсорный переключатель | 1983 |

|

SU1092725A1 |

| Сенсорный переключатель | 1986 |

|

SU1367150A2 |

| Устройство для измерения среднего значения фазового сдвига | 1985 |

|

SU1283668A1 |

| Сенсорный переключатель | 1981 |

|

SU1010726A1 |

| Сенсорная клавиатура | 1981 |

|

SU1005311A1 |

| Измеритель линейных перемещений | 1986 |

|

SU1401273A1 |

| Запоминающее устройство | 1985 |

|

SU1305772A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1374179A1 |

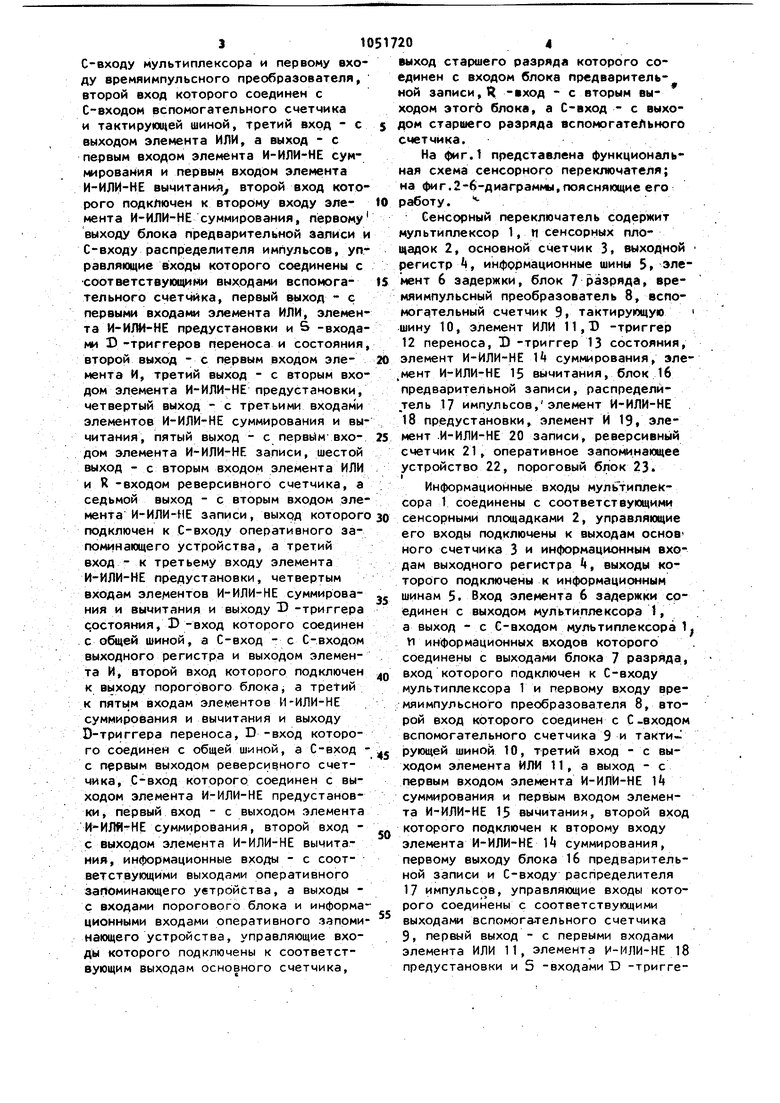

Изобретение относится к импульсной технике, а именно, к бесконтактным электронным переключателям, срабатывающим при прикосновении к сенсорным площадкам, и может быть йспол зовано в пультах управления различны устройств, в частности, в коммутаторах и устройствах ввода информации а ЭВМ. Известен сенсорный коммутатор, со держащий мультиплексор, разрядный сче чик, разрядный регистр, триггер, элемент И-НЕ, дополнит.ел-ьный разрядный счетчик, инвертор, тактирующуюj основную и дополнительную выходные шины . О . Недостаток коммутатора - низкая надежность функционирования. Наиболее близким к предлагаемому по технической сущности является сенсорное устройство, содержащее основной счетчик, выходной регистр, И сенсорных площадок, тактируюи4ую и выходные информационные шины и мультиплесор,,- II информационных входов которого соединены с соответствующим сенсорными площадками, управляющие входы - с выходами счетчика и информационными входами регистра сдви га, стробирующий вход - с тактирующей ши ной, входом счетчика и входом синхро низации регистра сдвига, выходы кото рого подключены к информационным шинйм 2 . Недостатком этого устройства является также низкая нааежность функ ционирования, обусловленная разбросом монтажных емкостей сенсорных площадок, имеющим место в реальных кон.струкциях, их взаимном расположением по отношению к внутренним конструктивным элементам и внешним окружающим предметам. Цель изобретения - повышение надежности функционирования. . Поставленная цель достигается тем, что в сенсорный переключатель, содержаций основной счетчик, выходной регистр, П сенсорных площадок, тактирующую и выходные информационные шины, мультиплексор, И информационных входов которого соединены с соответствующими сенсорными площадками, управляющие входы - с выходами основного счетчика и информационными входами выходного регистра, выходы которого подключены к информационным шинам, введены элемент И, элемент ИЛИ, элементы И-ИЛИ-НЕ предустановки, записи, суммирования и вычитания, D -триггеpь переноса и состояния, пороговый блок, оперативное запоминающее устройство, распределитель импульсов, реверсивный и вспомогательный счет- . чики, времяимпульсмый преобразователь, блок разряда, блок предварительной, загмси и элемент задержки, вход которого соединен с выходом мультиплексора, а выход - с С -входом мультиплексора, IT информационных входов которого соединены с выходами блока разряда, вход которого подключен к С-входу мультиплексора и первому входу времяимпульсного преобразователя, второй вход которого соединен с С-входом вспомогательного счетчика и тактирущей шиной, третий вход - с выходом элемента ИЛИ, а выход - с первым входом элемента И-ИЛИ-НЕ суммирования и первым входом элемента И-ИЛИ-НЕ вычитания второй вход которого подключен к второму входу элемента И-ИЛИ-НЕ суммирования, первому выходу блока предварительной записи и С-входу распределителя импульсов, управляющие входы которого соединены с соответствуЮ1дини выходами вспомогательного счетчика, первый выход - с первыми входами элемента ИЛИ, эле|«юнта И-ИЛИ-НЕ предустановки и 5 -входами D -триггеров переноса и состояния второй выход - с первым входом элемента И, третий выход - с вторым входом элемента И-ИЛИ-НЕ предустановки, четвертый выход - с третьими входами элементов И-ИЛИ-НЕ суммирования и вычитания, пятый выход - с первом входом элемента И-ИЛИ-НЕ записи, шестой выход - с вторым входом элемента ИЛИ и R -входом реверсивного счетчика, а седьмой выход - с вторым входом элемента И-ИЛИ-НЕ записи, выход которого подключен к С-входу оперативного запоминающего устройства, а третий вход - к третьему входу элемента И-ИЛИ-НЕ предустановки, четвертым входам элементов И-ИЛИ-НЕ суммирования и вычитания и выходу U -триггера достояния, D -вход которого соединен с общей шиной, а С-вход - с С-входом выходного регистра и выходом элемента И, второй вход которого подключен к выходу порогового блока, а третий к пятцм входам элементов И-ИЛИ-НЕ суммирования и вычитания и выходу D-триггера переноса, D -вход котороГО соединен с общей шиной, а С-вход с первым выходом реверсивного счетчика, С-вход которого соединен с выходом элемента И-ИЛИ-НЕ предустановки, первый вход - с выходом элемента И-ИЛЙ НЕ суммирования, второй вход с выходом элемента И-ИЛИ-НЕ вычитания, информационные входы - с соответствующими выходами оперативного запоминающего увтройства, а выходы с входами порогового блока и информационными входами оперативного запоминающего устройства, управляющие входы которого подключены к соответствующим выходам основного счетчика. выход старшего разряда которого соединен с входом блока предварительной записи,Я ХОД - с вторым выходом этого блока, а С-вход - с выхоом старшего разряда вспомогате/чьного счетчика. На фиг.1 представлена функциональная схема сенсорного переключателя; на фиг.2-6-диаграммы,поясняющие его работу. Сенсорный переключатель содержит мультиплексор 1, м сенсорных площадок 2, основной счетчик 3. выходной регистр i, информационные шины 5 элемент 6 задержки, блок 7 разряда, времяимпульсный преобразователь 8, вспомогательный счетчик 9, тактирующую шину 10, элемент ИЛИ 11,Т) -триггер 12 переноса, D -триггер 13 состояния, элемент И-ИЛИ-НЕ 1 суммирования, элемент И-ИЛИ-НЕ 15 вычитания, блок 16 предварительной записи, распределй.тель 17 импульсов,элемент И-ИЛИ-НЕ 18 предустановки, элемент И 19, элемент .И-ИЛИ-НЕ 20 записи, реверсивный счетчик 21, оперативное запоминающее устройство 22, пороговый блок 23. Информационные входы мультиплексора 1 соединены с соответствующими сенсорными площадками 2, управляющие его входы подключены к выходам основ ного счетчика 3 и информационным входам выходного регистра t, выходы которого подключены к информационным шинам 5. Вход элемента 6 задержки соединен с выходом мультиплексора , а выход - с С-входом мультиплексора 1, м информационных входов которого соединены с выходами блока 7 разряда, вход которого подключен к С-входу мультиплексора 1 и первому входу времяимпульсного преобразователя 8, второй вход которого соединен с С-входом вспомогательного счетчика 9 и такти рующей шиной 10, третий вход - с выходом элемента ИЛИ 11, а выход - с первым входом элемента И-ИЛИ-НЕ И суммирования и первым входом элемента И-ИЛИ-НЕ 15 вычитании, второй вход которого подключен к второму входу элемента И-ИЛИ-НЕ И суммирования, первому выходу блока 16 предварительной записи и С-входу распределителя 17 импульссэв, управляющие входы которого соединены с соответствующими выходами вспомогательного счетчика 9, первый выход - с первыми входами элемента ИЛИ 11, элемента И-ИЛИ-НЕ 18 предустановки и 5 -входами Т) -триггерое V2 и 13 переноса и состояния, второй выход - с первым входом элемента И 19I третий выход - с вторым входом элемента И-ИЛИ-НЕ 18 предустаноеки, четвертый выход - с третьими входами элементов И-ИЛИ-НЕ 1 и 15 суммирования и вычитания, пятый выход - с первым входом элемента И-ИЛИНЕ 20 записи, шестой выход -с втррым входом элемента ИЛИ 11 и R -входом реверсивного счетчива 21, а седьмой выход - с вторым входом элемента И-ИЛИ-НЕ 20 записи, выход которого подключен к С-входуопе|эативногр запоминающего устройства 22, а третий вход - к третьему входу элемента И-ИЛИ-НЕ 18 предустановки, четвертым входам элементов Ни 15 суммирований и вычитаний и выходу -триггера 13 состояния,Л -вход которого соединен с общей шиной, а С-вход - с С-входом выходного регистра «и выходом элемента И 19, второй вход которого подключен к выходу порогового блока 23. а третий - к пятым входам элементов И-ИЛИ-НЕ И и 15 суммирования и вычитания и выходу D -триггера 12 переноса, CD -вход KOTopJbro соединен с общей шиной, а С-вход - с первым выходом реверсивного счетчика .1, С-вход которого соединен с выходом элемента И-ИЛИ-НЕ 18 предустановки, первый вход - с вы ходом элемента И-ИШ-НЕ 1 суммирования, второй вход - с выходом э)«мента И-ИЛИ-НЕ 15 вычитания, имформационные входы - с соответствующими выходами оперативного запоминающего устройства 22, а выходы - с входами порогового блока 23 и информационными входами оперативного запоминающего устройства 22, управляющие входы которого подключены к соответст вующим выходам основного счётчика 3, выход старшего разряда которого соединен с входом блока 16 предварительной записи, R -вход - с вторым выходом этого блока, а С-вход - с выходом старшего разряда вспомогательного счетчика 9.

Работа сенсорного переключателя построе на по циклическому принципу. Цикл состоит из п строк. Строка состоит из К тактов. Длительность такта Т равна периоду следования тактовых импульсов, поступающих по тактирующей шине 10, В каяадой строке опрашивается одна сенсорнаяi площадка 2, а опрос всех площадок 2 происходит в течение цикла. Управляющие сигналы/

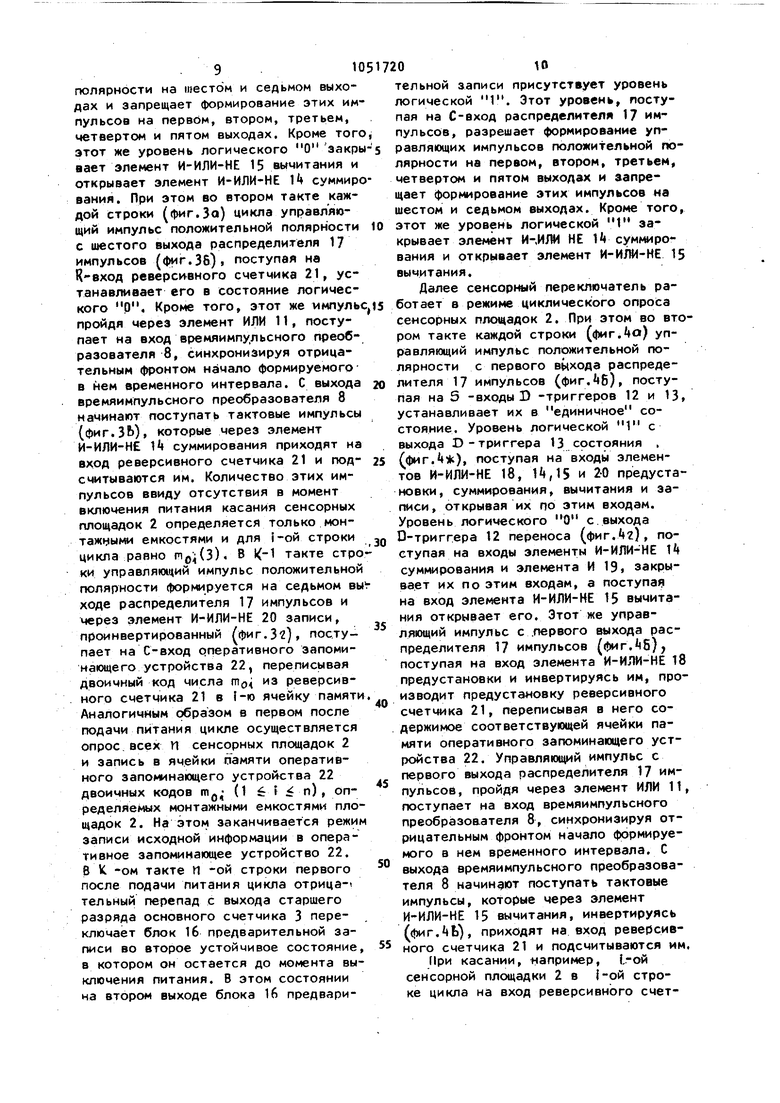

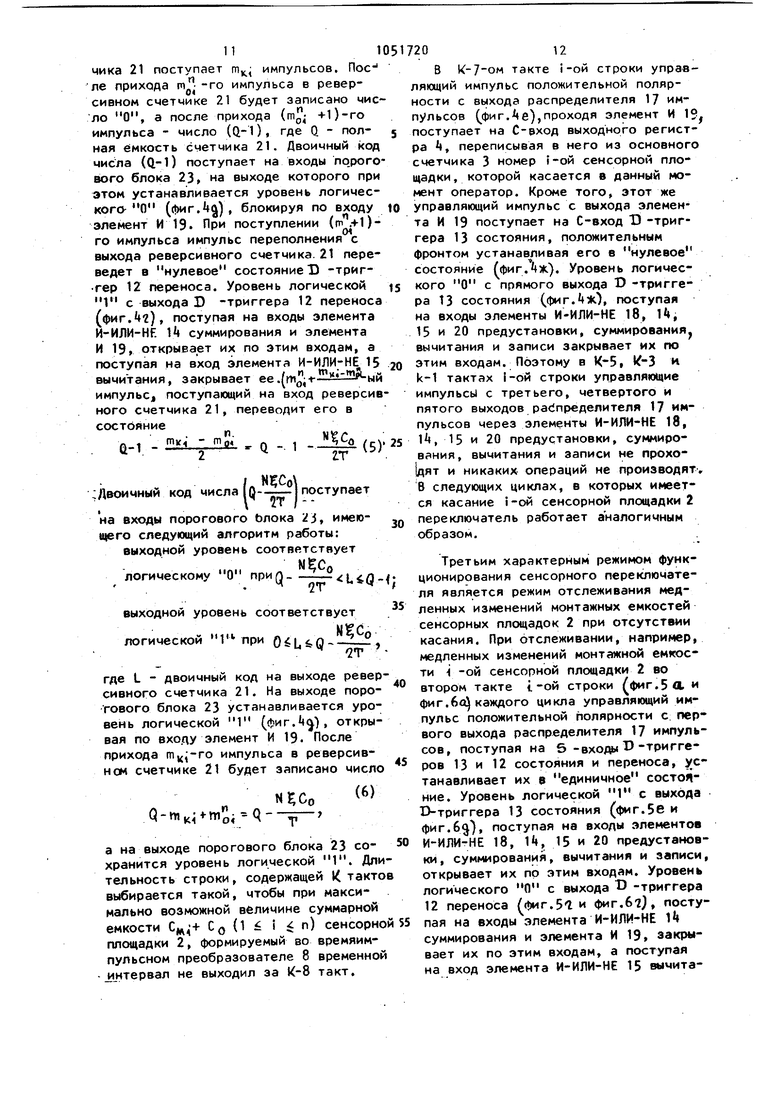

необходимые для работы сенсорного переключателя по циклическому принципу, формируются основным и вспомогательным счетчиками 3, 9 и распределителем 17 импульсов. При этом коэф фициент пересчета основного счетчика 3-П, а коэффициент пересчета вспомогательного счетчика 9V, и они определяют соответственно число опрашиваемых сенсорных площадок 2 и количество К тактов в каждой строке.

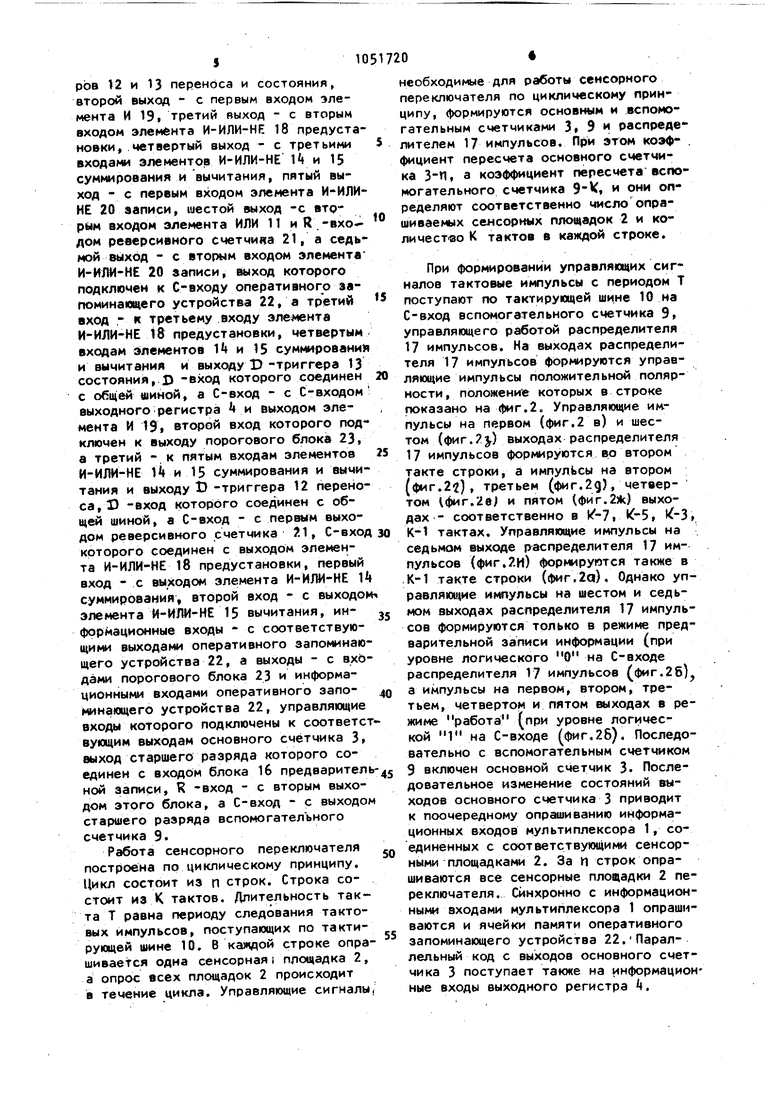

При формировании управляющих сигналов тактовые импульсы с периодом Т поступают по тактирующей шине 10 на С-вход вспомогательного счетчика 9, управляющего рвотой распределителя 17 импульсов. На выходах распределителя 17 импульсов формируются управляющие импульсы положительной полярности , пол ожение которых в строке показано на фиг.2. Управляющие импульсы на первом (фиг.2 в) и шестом (фиг.) выходах распределителя 17 импульсов формируются во втором такте строки, а импулЬсы на втором (фиг.22), третьем (фиг.29), четвертом Vфиг.2e) и пятом (фиг.2) выходах - соответственно в «-7, , К-1 тактах. Управляющие импульсы на седьмом выходе распределителя 17 импульсов {фиг.2И) формируются также в .К-1 такте строки (фиг,2а). Однако управляющие и шульсы на шестом и седьмом выходах распределителя 17 импульсов формируются только в режиме предварите льной записи информации (при уровне логического О на С-входе распределителя 17 импульсов (фиг.2б), а импульсы на первом, втором, третьем, четвертом и пятом выходах в режиме работа при уровне логической 1 на С-входе (фиг.26). Последовательно с вспомогательным счетчиком 9 включен основной счетчик 3. Последовательное изменение состояний выходов основного счетчика 3 приводит к поочередному опрашиванию информационных входов мультиплексора 1, соединенных с соответствующими сенсорными площадками 2. За и строк опрашиваются все сенсорные площадки 2 переключателя. Синхронно с информационными входами мультиплексора 1 опрашиваются и ячейки памяти оперативного запоминающего устройства 22.-Параллельный код с выходов основного счетчика 3 поступает также на информационные входы выходного регистра . 71 Мультиплексор 1 совместно с включенным последовательно с ним элементом 6 задержки образует генератор импульсов с запаздывающей обратной связью. При отсутствии касания -ой сенсорной площадки 2 в i -ой строке цикла на выходе элемента 6 формируются импульсы с периодом равным oi- t,,: + 2t время, за которое монгде tjj(. тажная емкость См , (С„- ,,)-ой сенсорной площадки 2 за рядится входным током логического О мульти-15 плексора входного порогового напряжения Unop , воспринимаемого, как уровень логической 1 En-U6: е«иМОгде Е„ - напряжение питания мультиплексора 1; Ug - падение напряжения на смещенном в прямом направлении база-эмиттерном переходе входного многоэмиттерного транзистора мультиплексора 1 jt.et i +tjj- суммарная задержка t,, мультиплексора 1 и элемента 6 задержки касании к монтажной емкости сенсорной площадки 2 добавляется .емкость тела оператора С и в 1-ой строке цикла на выходе элемен та 6 задержки будут (Ьормироваться импульсы уже с периодом равным ( tic Zt , где tj,;(C«+r,.) - время, за которо суммарная емкост CQ +Сщ, i -ой сенсо ной площадки 2 з рядится входным током логическогомультипле сора 1- вхо ного порогового напряжения поо принимаемого, ка уровень логической 1, Подключенный к информационным вхо дам мультиплексора 1 блок 7. разряда служит для разряда емкостей сенсорны площадок 2 во время положительных импульсов напряжения. В этом время 20 208 уровень логической 1 с выхода элемента 6 задержки открывает П ключей, входящих в блок 7 разряда, что приводит к образованию цепей разряда емкостей всех сенсорных площадок 2. Во время действия отрицательного импульса напряжения уровень логического О с выхода элемента 6 задержки закрывает ключи блока 7 разряда. Импульсы, сформированные мультиплексором 1, поступают на вход времяимпульсного преобразователя 8. В преобразователе 8 подсчитывается N этих импульсов и формируется временной интервал, равный длительнрсти N периодов. Этот интервал заполняется тактовыми импульсами с периодом следования Т. Количество импульсов, прошедших на выход времяимпульсного преобразователя 8 в 1-ой (1 i: i fc n) строке .цикла, равно Я«о н(См, + 2Ц) УПд. . при отсутствии касания 1-ой сенсорной площадки 2 и , (C«HtoV2i, (М т т при касании -ой сенсорной площадки 2. Начало временного интервала синхронизировано со вторым тактом строки, а конец интервала при максимально возможной величине суммарной емкости + GO 1-ой сенсорной площадки 2 не должен выходить за К-8 такт строки, Сенсорный переключатель имеет три характерных режима функционирования: запись исходной информации в оперативное запоминающее устройство 22, переключение при касании оператором сенсорной площадки 2, отслеживание медленных изменений монтажных емкостей сенсорных площадок 2. При подаче питания сенсорный пе,реключатель функционирует в первом режиме, при этом блок 16 предварительной записи вырабатывает одиночный импульс положительной полярности, устанавливающий по R -входу основного счетчика 3 в состояние логического 01 Уровень логического О с другого выхода блока 16 предварительной записи поступая на С-вход распреде ителя 17 импульсов, разрешает формирование управляющих импульсов положительной полярности на шестом и седьмом выходах и запрещает формирование этих импульсов на первЬм, втором, третьем, четвертом и пятом выходах. Кроме того, этот же уровень логического О эакры-з аает элемент И-ИЛИ-НЕ 15 вычитания и открывает элемент И-ИЛИ-НЕ k суммир вания. При этом во втором такте каждой строки (фиг.За) цикла управляющий импульс положительной полярности с шестого выхода распределителя 17 импульсов (фиг.35). поступая на К-вход реверсивного счетчика 21, устанавлиаает его в состояние логического О. Кроме того, этот же импуль пройдя через элемент ИЛИ 11, поступает на вход времяимпульсного преобразователя 8, синхронизируя отрицательным фронтом начало формируемогов нем временного интервала. С выхода времяимпульсного преобразователя 8 начинают поступать тактовые импульсы (фиг.ЗЬ), которые через элемент И-ИЛИ-НЕ 1 суммирования приходят на вход реверсивного счетчика 21 и подсчитываются им. Количество этих импульсов ввиду отсутствия в момент включения питания касания сенсорных площадок 2 определяется только монтажными емкостями и для i-ой строки цикла равно тд;|(3). В такте стро ки управляющий импульс положительной полярности формируется на седьмом вы ходе распределителя 17 импульсов и через элемент И-ИЛИ-НЕ 20 записи, проинвертированный (фиг.З), поступает на С-вход рперативного запоминающего устройства 22, переписывая двоичный код числа т из реверсивного счетчика 21 в f-ю ячейку памяти Аналогичным образом в первом после подачи питания цикле осуществляется опрос.всех П сенсорных площадок 2 и запись в ячейки памяти оперативного запоминающего устройства 22 двоичных кодов Пд (1 6 f п), определяемых монтажными емкостями площадок 2. На этом заканчивается режим записи исходной информации в оперативное запоминающее устройство 22. В К -ом такте П -ой строки первого после подачи питания цикла отрицательный перепад с выхода старшего разряда основного счетчика 3 переключает блок 1б предварительной записи во второе устойчивое состояние, в котором он остается до момента выключения питания. В этом состоянии на втором выходе блока 16 предварительной записи присутствует уровень логической 1. Этот уровень, поступая на С-вход распределителя 17 импульсов, разрешает формирование управляющих импульсов гюлoжиteльнoй полярности на первом, втором, третьем, четвертом и пятом выходах и запрещает формирование этих импульсов на шестом и седьмом выходах. Кроме того, этот же уровень логической 1 закрывает элемент И-,И/Н1 НЕ И cyMcwpoвания и открывает элемент И-ИЛИ-НЕ 15 вычитания. Далее сенсорный переключатель работает в режиме циклического опроса сенсорных площадок 2. При этом во втором такте каждой строки (фиг.ю) управляющий импульс положительной полярности с первого выхода распределителя 17 импульсов (фиг.46), поступая на 5 -входы) -триггеров 12 и 13, устанавливает их в единичное состояние. Уровень логической 1 с выхода D-триггера 13 состояния . (фиг.), поступая на входы элементов И-ИЛИ-НЕ 18, HJS и 2-0 предустановки, суммирования, вычитания и записи, открывая их по этим входам. Уровень логического О с.выхода О-триггера 12 переноса (фиг./), поступая на входы элементы И-ИЛИ-НЕ И суммирования и элемента И 19, закрывает их по этим входам, а поступав на вход элемента И-ИЛИ-НЕ 15 вычитания открывает его. Зтот же управляющий импульс с .первого выхода распределителя 17 импульсов (фиг.б), поступая на вход элемента И-ИЛИ-НЕ 18 предустановки и инвертируясь им, производит предустановку реверсивного счетчика 21, переписывая в него содержимое соответствующей ячейки памяти оперативного запоминающего устройства 22. Управляющий импульс с первого выхода распределителя 17 импульсов, пройдя через элемент ИЛИ 11, поступает на вход времяимпульсного преобразоаателя 8, синхронизируя отрицательным фронтом начало формируемого в нем временного интервала. С выхода времяимпульсного преобразователя В начинают поступать тактовые импульсы, которые через элемент И-ИЛИ-НЕ 15 вычитания, инвертируясь (фиг.), приходят на вход реверсивного счетчика 21 и подсчитываются им, (1ри касании, апример, }..-ой сенсорной площадки 2 в |-ой строке цикла на вход реверсивного счетчика 21 поступает т( импульсов, После прихода импульса в реверсивном счетчике 21 будет записано чис ло О, а после прихода (т +1)-го импульса - число (Q-1), где Q - полная ёмкость счетчика 21. Двоичный код числа (Q-l) поступает на входы вого блока 23, на выходе которого при этом устанавливается уровень логического- О (фигЛ) , блокируя по входу элемент И 19. При поступлении (tn%l)го импульса импульс переполнения с выхода реверсивного счетчика. 21 переведет в нулевое состояние D -триггер 12 переноса. Уровень логической 1 с выхода D -триггера 12 переноса (фиг.), поступая на входы элемента И-ИЛИ-НЕ I суммирования и элемента И 19, открывает их по этим входам, а поступая на вход элемента И-ИЛИ-НЕ 15 VI tm.. tm л. вычитания, закрывает ee.(mo-t-- bii: 5 p -bift импульс, поступающий на вход реверсив ного счетчика 21, переводит его в состояние . Q-l - - - g , Q -, 1 (5) N15Co поступает ;Двоичный код числа , на входы порогового Ьлока 2j, имеюtttero следующий алгоритм работы: выходной уровень соответствует логическому О прил-- Lirt. 2Т ч выходной уровень соответствует логической при O LfeQ---, где L - двоичный код на выходе реверсивного счетчика 21. На выходе порогового блока 23 устанавливается уровень логической 1 (фиг.), открывая по входу элемент И 19. После прихода m,jpro импульса в реверсивном счетчике 21 будет записано число на выходе порогового блока 23 сохранится уровень логической 1. Длительность строки, содержащей К такто вь ирается такой, чтобы при максимально возможной величине суммарной емкости GO {1 i i п) сенсорно площадки 2, формируемый во времяимпульсном преобразователе 8 временной J,1нтepвaл не выходил за К-8 такт. 2012 В такте i-ой строки управляющий импульс положительной полярности с выхода распределителя 17 импульсов (фиг.е),проходя элемент И 1. поступает на С-вход выходного регистра i, переписывая в него из основного счетчика 3 номер i-ой сенсорной площадки , которой касается в данный момент оператор. Кроме того, этот же управляющий импульс с выхода элемента И 19 поступает на С-вход ТЭ -триггера 13 состояния, положительным фронтом устанавливая его в нулевое состояние фиг.). Уровень логического О с прямого выхода D -триггера 13 состояния (фиг.ж), поступая на входы элементы И-ИЛИ-НЕ 18, }k, 15 и 20 предустановки, суммирования, вычитания и записи закрывает их по этим входам. Поэтому в Ч-5, 3 и k-1 тактах i-ой строки управляющие импульсы с третьего, четвертого и пятого выходов распределителя 17 импульсов через элементы И-ИЛИ-НЕ 18, И, 15 и 20 предустановки, суммирования, вычитания и записи не прохо|дят и никаких операций не производят, 8 следующих циклах, в которых имеется касание i-ой сенсорной площадки 2 переключатель работает аналогичным образом. Третьим характерным режимом функционирования сенсорного переключателя является режим отслеживания медленных изменений монтажных емкостей сенсорных площадок 2 при отсутствии касания. При отслеживании, например, медленных изменений монтажной емкости -i -ой сенсорной площадки 2 во втором такте i-ой строки фиг.Бл и фиг.бо каждого цикла управляющий импульс положительной полярности С: первого выхода распределителя 17 импульсов, поступая на 5 -входы 15-триггеров 13 и 12 состояния и переноса, устанавливает их в единичное состояние. Уровень логической 1 с выхода 1Э-триггера 13 состояния (фиг.Бе и фиг.6), поступая на входы элементов И-ИЛИ-НЕ 18, I, 15 и 20 предустановки, суммирования, вычитания и записи, открывает их по этим входам. Уровень логического О с выхода Т -триггера 12 переноса (фиг.51 и фиг.67), поступая на входы элемента И-ИЛИ-НЕ k суммирования и элемента И 19, закрывает их по этим входам, а поступая на вход элемента И-ИЛИ-НЕ 15 вычита13ния, открывает его. Этот же управляющий импульс с первого выхода распределителя 17 импульсов, поступая на вход элемента И-ИЛИ-НЕ 18 предустановки и инвертируясь им (фиг, 56 и фиг.68}, производит предустановку реверсивного счетчика 21, переписывая в него содержимое соответствующей ячейки памяти оперативного эапоминакицего устройства 22. Кроме того, управляющий импульс с первого выхода распределителя 17 импульсов, пройдя через элемент ИЛИ 11, поступает на вход времяимпульсного преобразователя 8, синхронизируя начало формируемого в нем временного интервала. С выхода времяимпульсного преобр|13ователя 8 начинают поступать тактовые импульсы, которые через элемент И-ИЛИ-HF. 15 вычитания, инвертируясь (фиг.5& и фиг.66), приходят на вход реверсивного счетчика 21 и подсчитываются им. При этом, поскольку касание i -ой сенсорной площадки отсутствует, коли чество импульсов, поступивших в i-ой строке цикла на вычитающий вход реверсивного счетчика, определяется согласно (l)- и (З) выражением Nf ()СМ oi;p Щ -с - ЩЦ-UgJ ив силу влияния на сенсорный перекл чатель окружающей среды подвержено дрейфу4 Так изменение взаимного расположения сенсорного переключателя и окружающих его предметов, в том числе и оператора, приводит к изменению монтажной емкости Сд, равно как и монтажных емкостей других сенсорных площадок. Изменение окружающей темпе ратуры вызывает дрейф входных токовЗ входных пороговых напряжений Ujop j падений, напряжения база-эмиттерном переходе многоэмиттерного тра зистора, суммарной задержки мультиплексора 1 и элемента 6 задерж ки, питаюо1его напряжения Е. При этом количество импульсов, по ступивших в -ой строке цикла на вы читающий вход реверсивного счетчика 21, может превышать или наоборот быт меньше числа гпр,-, хранящегося в данный момент в i -ой ячейке памяти оперативного запоминающего устройства 22 и введенного в качестве предустановки в реверсивный счетчик 21. В том пучае, когда тд Пд,- (фиг.5), после прихода на второй вход реверсивного счетчика 21 импульса в нем будет записано число О, а после прихода (т +1)-го импульса число (Q-1), где Q - полная емкость счетчика. Двоичный код числа (Q-1) поступает на входы порогового блока 23, на выходе которого при этом устанавливается уровень логического О Сфиг.54, блокируя по входу элемент И 19. При поступлении (m, 1)-го импульса импульс переполнения с выхода реверсивного счетчика переведет В нулевое состояние D -триггер 12 переноса. Уровень логической 1 с выхода D -триггера 12 переноса (фиг.5 поступая Via. входы элемента И-ИЛЙ-НЕ k суммирования и элемента И 19 открывает их по этим входам, а поступая на вход элемента И-ИЛИ-НЕ 15 вычитания, закрывает его. После прихода то;-го импульса в реверсивном счетчике 21 будет записано число Q- {%i - %i). (8) а на выходе порогового блока 23 сохранится уровень логического 0. В ()-ом такте i-ой строки управляющий импульс положительной полярности с второго выхода распределителя 17 импульсов через элемент И 19 не проходит, так как он закрыт нуле-вым уровнем с выхода порогового блока 23. В (К-5)-ом такте i-ой строки управляющий импульс положительной полярности с третьего выхода распределителя 17 импульсов, проходя через элемент 18 И-ИЛИ-НЕ 18 предустановки, инвертируется (фиг.56) и поступает на С-вход реверсивного счетчика 21, переписывая в него содержимое i-ой ячейки памяти т, оперативного запоминающего устройства 22. На выходе порогового блока 23 устанавливается уровень логической 1 (фиг.59) открывая по входу элемент И 19. В («-3)-ом такте i-ой строки управляющий импульс положительной полярности с четвертого выхода распределителя 17 импульсов, проходя через элемент И-ИЛИ-НЕ Т суммирования, инвертируется (фиг.) и поступает на вход реверсивного счетчика 21, увеличивая его содержимое на единицу. В реверсивном счетчике 21 получается число (т, V) Через элемент И-ИЛИ-НЕ 15 вычитания управляющий импульс-с четвертого выхода распределителя 17 импульсов не проходит, 15 так как он закрыт поступающим на его вход уровнем логической 1 фиг.5г} с выхода D -триггера 12 переноса. В ( )-ом такте I-ой строки управляющий импульс с пятого выхода распреде лителя 17 импульсов, проходя через элемент И-ИЛИ-НЕ 20 записи, инвертируется (фиг, и, поступая на С-вход оперативного запоминающего устройства 22, переписывает в его 1-ую ячейку памяти содержимое реверсивного счетчика 21, т.е. число (поч Г-ой строке следующего цикла уже это число будет использо.ваться в качестве знамения для гц едустг1новки реверсивного счетчика 21. в следующих циклах, если по-прежнему WQI , сенсорный переключатель работает аналогичным образом. Если же т т (фиг.6), то пос ле прихода на вычитаюо ий вход реверсивного счетчика 21 то;-го импульса в нем будет записано чкслоа oi , (9) а на выходе порогового блока 23 сохранится уровень логической 1. В ()ом такте 1-ой строки управляющий импульс с второго выхода .распределителя 17 импульсов через эл мент И 19 не проходит, так как он закрыт уровнем логического О(фиг.5 с выхода D-триггера 12 переноса (фиг.б). В {К-5)ом такте i-ой строки управляю1ций импульс с третьего вы хода распределителя 17 импульсов, гфоходя через элемент И-ИЛИ-НЕ 18 предустановки, инвертируется ( фиг.63 и поступает на С-вход реверсивного счетчика 21, переписывая в него соде жимое 1-ой ячейки памяти гг оперативного запоминающего устройства 22 В (К-З)-ом такте 1-ой строки управляющий импульс с четвертого выхода 2016 распределителя 17 импульсов, проходя черезЭлемент И-ИЛИ-HF. 15 вычитания, инвертируется фиг.6Б)и поступает на вход реверсивного счетчика 21, уменьшая его содержимое на единицу. В реверсивном счетчике 21 получается число (mg -1). Через элемент И-ИЛИ-ИЕ И суммирования управляющий импульс с четвертого выхода распределителя 17 импульсов не проходит, так как он закрыт поступающим на его вход уровнем логического О (фиг.бг) с выхода D-триггера 12 переноса. В (К-1)-ом такте i-ой строки управляюижй импульс с пятого выхода распределителя 17 импульсов, пройдя через элемент И-ИЛИ-НЕ 20 записи, инвертируется (фиг.бе) и, поступая на С-вход оперативного запоминающего устройства 22, переписывает в его 1-ую ячейку па-, мяти содержимое реверсивного счетчика 21, т.е. число (nijj)-l). В -ой строке следующего цикла уже это чис ло будет использоваться в качестве значения mQ для предустановки ревер сивного счетчика 21. В следуЮ1чих циклах, если по-прежнему Шр . п , сенсорный переключатель работает аналогичным образом. Таким образом, введение в предлагаемый сенсорньй переключатель элемента И 19, элемента ИЛИ 11, элементов И-ИЛИ-НЕ 18, 20, U и 15 предустановки, записи, суммирования и вычитания, D -триггеров 12 и 13 переноса и состояния, порогового блока 23, оперативного запоминающего устройств ва. 22, распределителя 17 импульсов, реверсивного и вспомогательного счетчиков 21 и Э, времяимпульсного преобразователя 8, блока 7 разряда, блока 1б предварительной записи и элемента 6 задержки обеспечивает повышение надежности его функционирования.

фиг.6

Авторы

Даты

1983-10-30—Публикация

1982-06-23—Подача