1305

повышение информационной емкости устройства. Устройство содержит блоки 10,-10 сортировки данных, (где k - целое число), блок 11 памяти,распределители 12 и 13 сигналов, триггеры 14. формирователь 15 сигналов, группу формирователей ISj-IS, сигналов, формирователи 16,-16| установочных сигналов, группу счетчиков 17,-17. сигналов, реверсивный счетчик 18, селектор 19, мультиплексоры 20 и 21, группу элементов И 22/ -22к, элементы И 23-25, две группы элемен1

Изобретение относится к вычислительной технике, в частности к запоминающим .устройствам, и может быть использовано в вычислительных системах для сбора информации при приори- тетном обслуживании большого числа абонентов либо при организации очереди на обслуживание абонентов.

Целью изобретения является повышение информационной емкости устрой- ства.

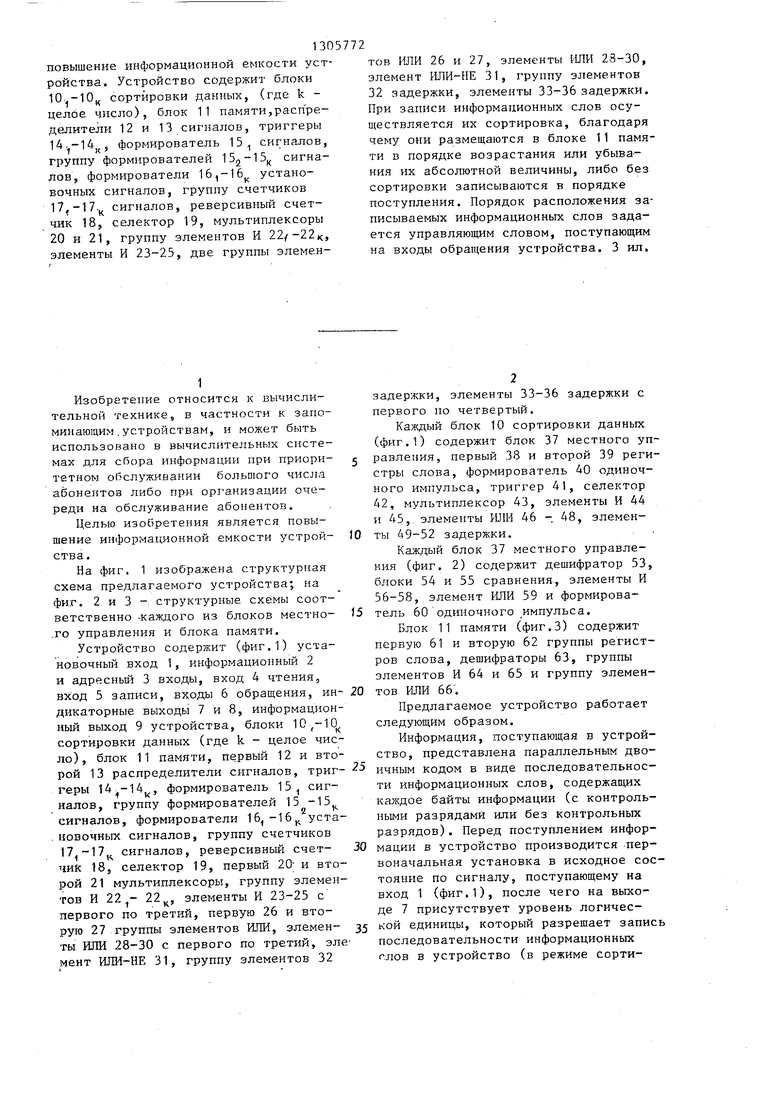

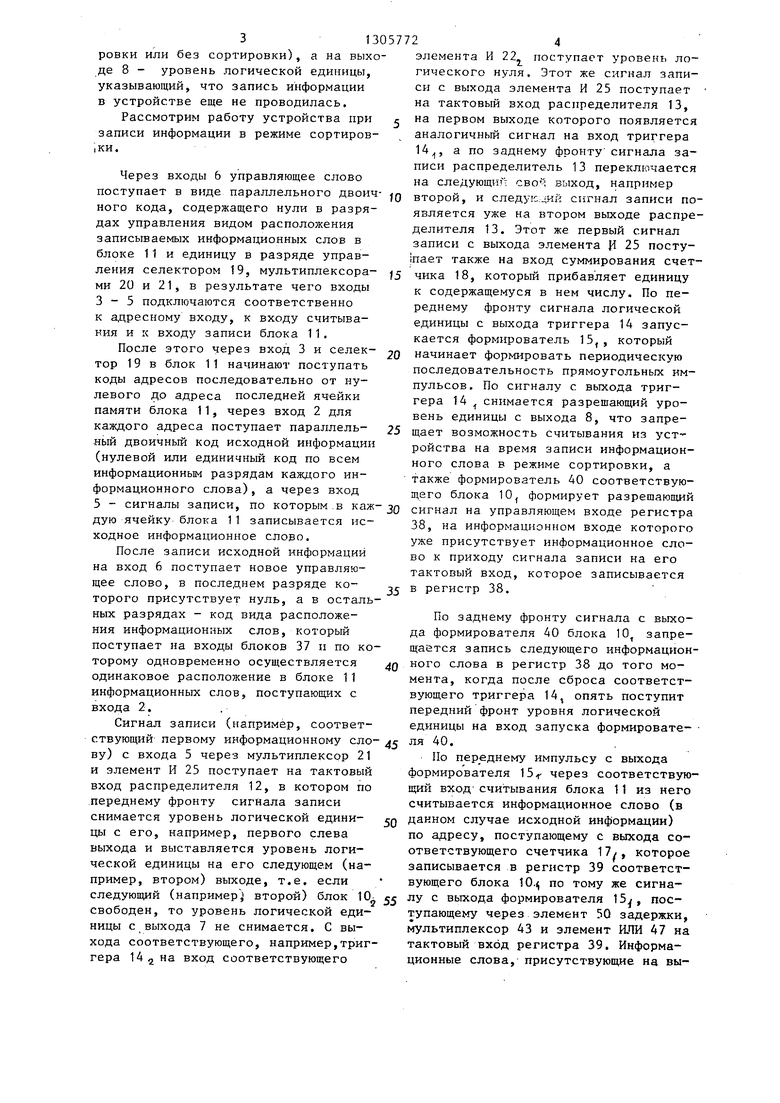

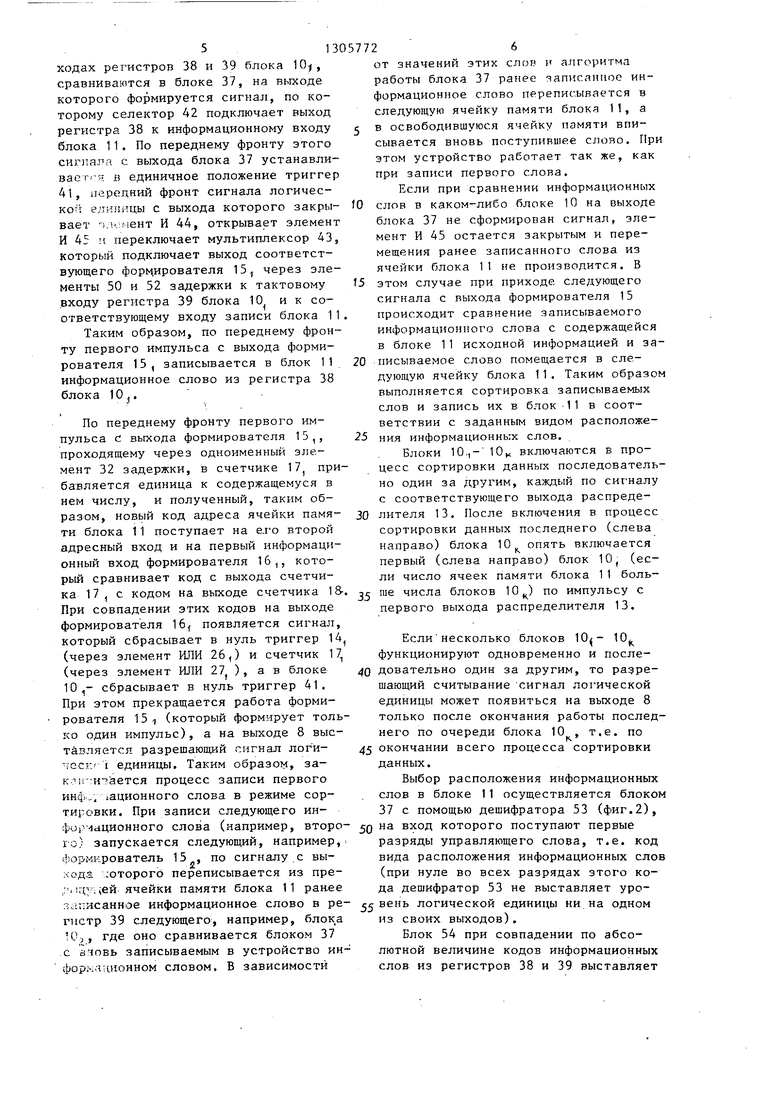

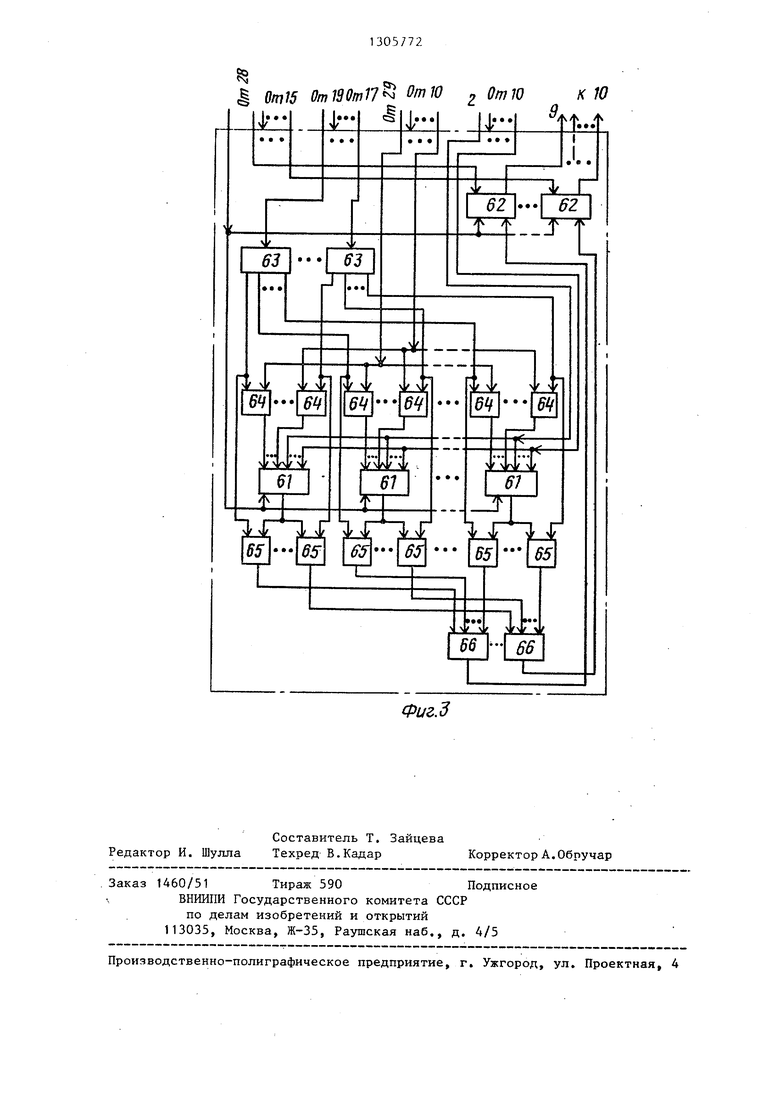

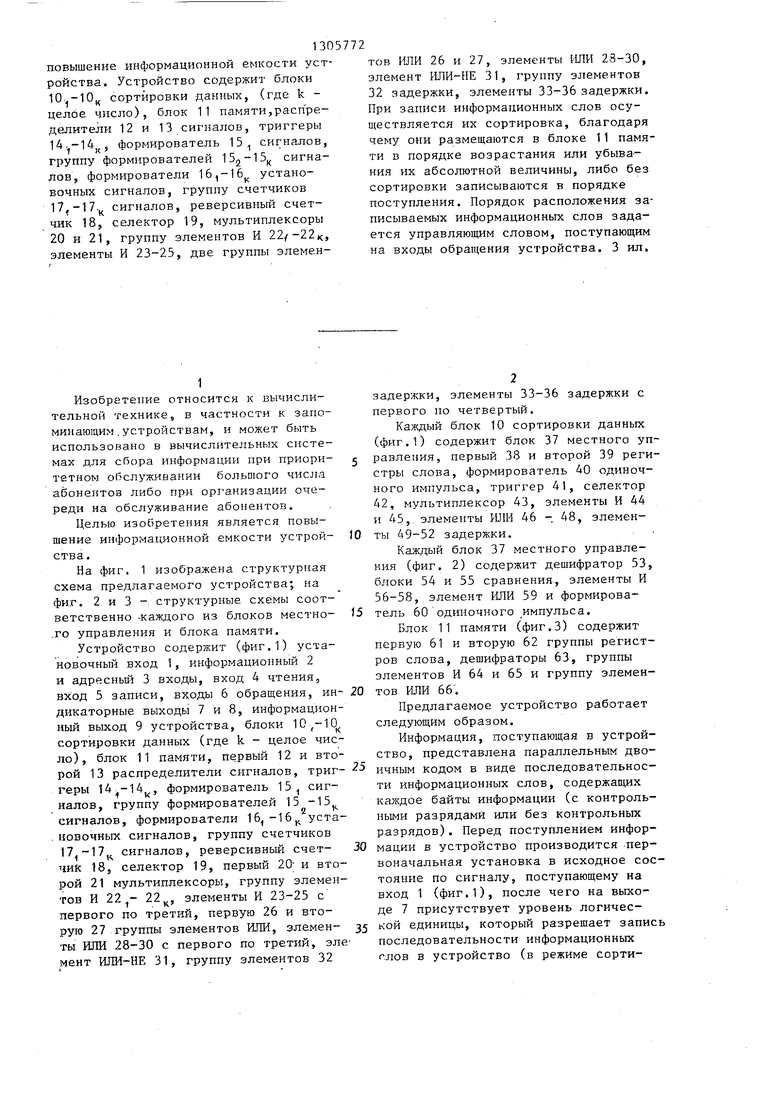

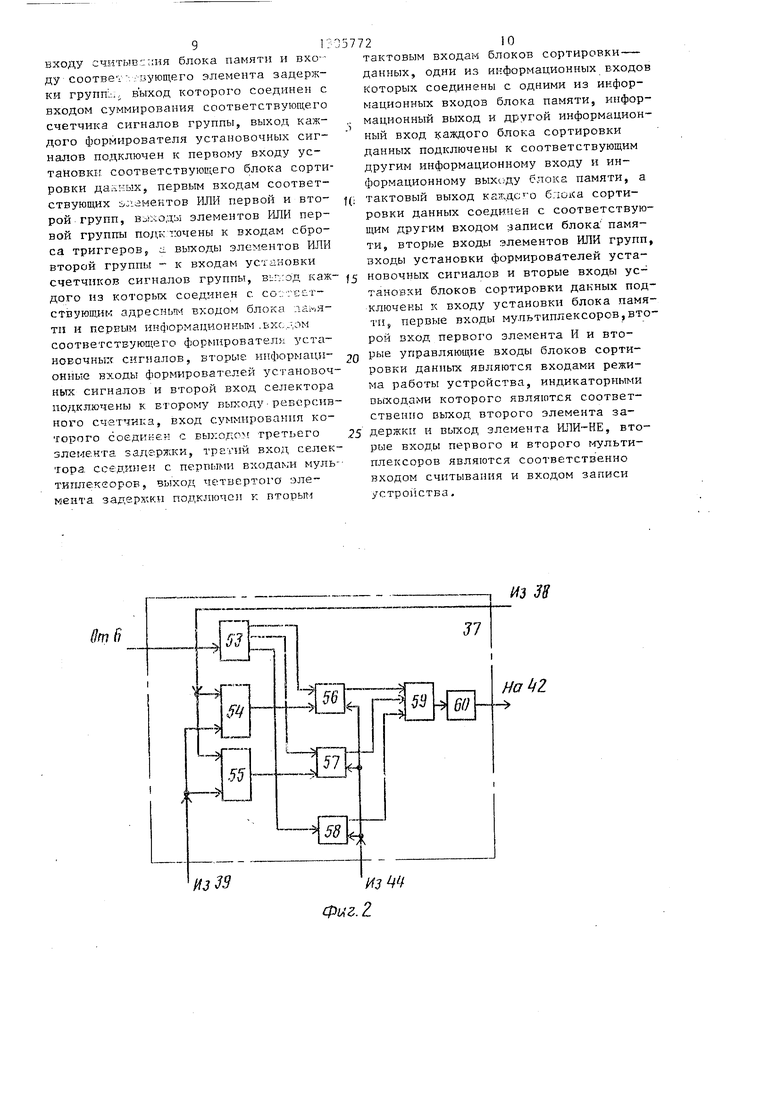

На фиг, 1 изображена структурная схема предлагаемого устройства; на фиг. 2 и 3 -, структурные схемы соответственно -каждого из блоков местно- .го управления и блока памяти.

Устройство содержит (фиг.1) установочный вход 1, информационный 2 И адресный 3 входы, вход 4 чтения, вход 5 записи, входы 6 обращения, ин- дикаторные выходы 7 и 8, информационный выход 9 устройства, блоки 10 ,-10 сортировки данных (где k - целое число), блок 11 памяти, первый 12 и второй 13 распределители сигналов, триг- геры , формирователь 15 сигналов, группу формирователей 15-15.

9

сигналов, формирователи уста- . ПОБОЧНЫХ сигналов, группу счетчиков ,( сигналов, реверсивный счет- чкК 18, селектор 19, первый 20- и второй 21 мультиплексоры, группу элементов И 22.,- 22, элементы И 23-25 с первого по третий, первую 26 и вторую 27 группы элементов ИЛИ, элемен- ты ИЛИ 28-30 с первого по третий, эле мент ИЛИ-ИЕ 31, группу элементов 32

тов ИЛИ 26 и 27, элементы t-ШИ 28-30, элемент ИЛИ-НЕ 31, группу элементов 32 задержки, элементы 33-36 задержки. При записи информационных слов осуществляется их сортировка, благодаря чему они размещаются в блоке 11 памяти в порядке возрастания или убывания их абсолютной величины, либо без сортировки записываются в порядке поступления. Порядок расположения записываемых информационных слов задается управляющим словом, поступающим на входы обращения устройства. 3 ил.

задержки, элементы 33-36 задержки с первого по четвертый.

Каяодый блок 10 сортировки данных (фиг.1) содержит блок 37 местного управления, первый 38 и второй 39 регистры слова, формирователь 40 одиночного импульса, триггер 41, селектор 42, мультиплексор 43, элементы И 44 и 45,. элементы 46 -. 48, элементы 49-52 задержки.

Каждый блок 37 местного управления (фиг. 2) Содержит дешифратор 53, блоки 54 и 55 сравнения, элементы И 56-58, элемент ИЛИ 59 и формирователь 60 одиночного ,импульса.

Блок 11 памяти (фиг.З) содержит первую 61 и вторую 62 группы регистров слова, дешифраторы 63, группы элементов И 64 и 65 и группу элементов ИЛИ 66.

Предлагаемое устройство работает следующим образом.

Инфор.мация, поступающая в устройство, представлена параллельным двоичным кодом в виде последовательности информационных слов, содержащих каждое байты информации (с контрольными разрядами -или без контрольных разрядов). Перед поступлением информации в устройство производится .первоначальная установка в исходное сос тояние по сигналу, поступающему на вход 1 (фиг.1), после чего на выходе 7 присутствует уровень логической единицы, который разрешает запис последовательности информационных глов в устройство (в режиме сорти313

ровки или без сортировки), а на выходе 8 - уровень логической единицы, указывающий, что запись информации в устройстве еще не проводилась.

Рассмотрим работу устройства цри записи информации в режиме сортиров|КИ.

Через входы 6 управляющее слово поступает в виде параллельного двоич ного кода, содержащего нули в разрядах управления видом расположения записываемых информационных слов в блоке 11 и единицу в разряде управления селектором 19, мультиплексора- ми 20 и 21, в результате чего входы 3-5 подключаются соответственно к а,цресному входу, к входу считывания и к входз записи блока 11 .

После этого через вход 3 и селек- тор 19 в блок 11 начинают поступать коды адресов последовательно от нулевого до адреса последней ячейки памяти блока 11, через вход 2 для каждого адреса поступает параллель- ный двоичный код исходной информации (нулевой или единичный код по всем информационным разрядам каждого информационного слова), а через вход 5 - сигналы записи, по которым .в каждую ячейку блока 11 записывается исходное информационное слово.

После записи исходной информации на вход 6 поступает новое управляющее слово, в последнем разряде ко- торого присутствует нуль, а в остальных разрядах - код вида расположения информационных слов, который поступает на входы блоков 37 и по которому одновременно осуществляется одинаковое расположение в блоке 11 информационных слов, поступающих с входа 2.

Сигнал записи (например, соответствующий первому информационному ело- ву) с входа 5 через мультиплексор 21 и элемент И 25 поступает на тактовый вход распределителя 12, в котором по переднему фронту сигнала записи снимается уровень логической едини- цы с его, например, первого слева выхода и выставляется уровень логической единицы на его следующем (например, втором) выходе, т.е. если следующий (напримерj второй) блок 10- свободен, то уровень логической единицы с выхода 7 не снимается. С выхода соответствующего, например,триггера 142 на вход соответствующего

24

элемента И 22 поступает уровень логического нуля. Этот же сигнал записи с выхода элемента И 25 поступает на тактовый вход распределителя 13, на первом выходе которого появляется аналогичный сигнал на вход триггера 14, а по заднему фронту сигнала записи распределитель 13 переключается на следующий своч выход, например второй, и следугс.дий сигнал записи появляется уже на втором выходе распределителя 13. Этот же первый сигнал записи с выхода элемента И 25 посту- 1пает также на вход суммирования счетчика 18, который прибавляет единицу к содержащемуся в нем числу. По переднему фронту сигнала логической единицы с выхода триггера 14 запускается формирователь 15,, который начинает формировать периодическую последовательность прямоугольных импульсов . По сигналу с выхода триггера 14 снимается разрешающий уровень единицы с выхода 8, что запрещает возможность считывания из уст- ройства на время записи информационного слова в режиме сортировки, а также формирователь 40 соответствующего блока 10, формирует разрешающий сигнал на управляющем входе регистра 38, на информационном входе которого уже присутствует информационное слово к приходу сигнала записи на его тактовый вход, которое записывается в регистр 38.

По заднему фронту сигнала с выхода формирователя 40 блока 10, запрещается запись следующего информационного слова в регистр 38 до того момента, когда после сброса соответствующего триггера 14, опять поступит передний фронт уровня логической единицы на вход запуска формировате- ля 40.

По переднему импульсу с выхода формирователя 15 через соответствующий вход-считывания блока 11 из него считывается информационное слово (в данном случае исходной информации) по адресу, поступающему с выхода соответствующего счетчика 17/, которое записывается в регистр 39 соответствующего блока 10. по тому же сигналу с выхода формирователя 15,, поступающему через элемент 50 задержки, мультиплексор 43 и элемент ИЛИ 47 на тактовый вход регистра 39. Информационные слова, присутствующие на выходах регистров 38 и 39 блока 10j, сравниваются в блоке 37, на выходе которого формируется сигнал, по которому селектор 42 подключает выход регистра 38 к информационному входу блока 11. По переднему фронту этого сигнала с выхода блока 37 устанавли- вае в единичное положение триггер 41, передний фронт сигнала логической единицы с выхода которого закры- вает )Л.;иент И 44, открывает элемент И 45 и переключает мультиплексор 43, Который подключает выход соответствующего формирователя 15 через элементы 50 и 52 задержки к тактовому входу регистра 39 блока 10 и к соответствующему входу записи блока 11 Таким образом, по переднему фронту первого импульса с выхода форми1138

рователя 15, записывается в блок информационное слово из регистра блока 10 ,|.

По переднему фронту первого импульса с: выхода формирователя 15,, проходящему через одноименный элемент 32 задержки, в счетчике 17 прибавляется единица к содержащемуся в нем числу, и полученный, таким образом, новый код адреса ячейки памяти блока 11 поступает на е.го второй адресный вход и на первый информационный вход формирователя 16,, который сравнивает код с выхода счетчика 17 с кодом на выходе счетчика 18-. При совпадении этих кодов на выходе формирователя 16 появляется сигнал, который сбрасывает в нуль триггер 14, (через элемент ИЛИ 26 ) и счетчик 17, (через элемент ИЛИ 27 ), а в блоке 10,- сбрасывает в нуль триггер 41. При этом прекращается работа формирователя 15-) (который формирует только один импульс), а на выходе 8 выставляется разрешающий сигнал лог и- . i единицы. Таким образом закон-;и ается процесс записи первого инф-, рационного слова в режиме сортировки. При записи следующего инВыбор расположения информацион слов в блоке 11 осуществляется бл 37 с помощью дешифратора 53 (ф иг.

форчационного слова (например, второ- 50 вход которого поступают первые

го; запускается следующий, например, формирователь 15 , по сигналу,с выразряды управляющего слова, т.е. код вида расположения информационных сло (при нуле во всех разрядах этого кода дешифратор 53 не выставляет уро

хода ;оторого переписывается из пре; пцт;;ей ячейки памяти блока 11 ранее

записанное информационное слово в ре- вень логической единицы ни на одном

гнстр 39 следующего, например, блок,а из своих выходов).

Блок 54 при совпадении по абсолютной величине кодов информационных слов из регистров 38 и 39 выставляет

10,, где оно сравнивается блоком 37 с ачовь записываемым в устройство ин- форлацнонном словом. В зависимости

от значений этих слов и алгоритма работы блока 37 ранее яаписапиое информационное слово переписывается в следующую ячейку памяти блока 11, а в освободившуюся ячейку памяти вписывается вновь поступившее слово. При этом устройство работает так же, как при записи первого слова.

Если при сравнении информационных слов в каком-либо блоке 10 на выходе блока 37 не сформирован сигнал, элемент И 45 остается закрытым и перемещения ранее записанного слова из ячейки блока 11 не производится. В этом случае при приходе следующего сигнала с выхода формирователя 15 происходит сравнение записываемого информационного слова с содержащейся в блоке 11 исходной информацией и записываемое слово помещается в следующую ячейку блока 11. Таким образом выполняется сортировка записываемых слов и запись их в блок -11 в соответствии с заданным видом расположения информационных слов.

Блоки 10,,- 10ц включаются в процесс сортировки данных последовательно один за другим, каждый по сигналу с соответствующего выхода распреде- хштеля 13. После включения в процесс сортировки данных последнего (слева направо) блока 10 опять включается первый (слева направо) блок 10 (если число ячеек памяти блока 11 больше числа блоков 10.,) по импульсу с

К.

первого выхода распределителя 13.

Если несколько блоков

,

функционируют одновременно и после- 40 довательно один за другим, то разрешающий считывание сигнал логической единицы может появиться на выходе 8 только после окончания работьг последнего по очереди блока 10 , т.е.

по

45 окончании всего процесса сортировки данных.

Выбор расположения информационных слов в блоке 11 осуществляется блоком 37 с помощью дешифратора 53 (ф иг.2),

50 вход которого поступают первые

разряды управляющего слова, т.е. код вида расположения информационных слов (при нуле во всех разрядах этого кода дешифратор 53 не выставляет уро

ня своем выходе сиг пал лог ической единиц., если врювь запнсыкаемое слово, находящееся в регистре 38, больше или равно ранее записанному слову находящемуся в регистре 39.

Блок 55 при совпадении по абсолютной величине информационных слов из регистров 38 и 39 выставляет на своем выходе сигнал логической единицы, если слово в регистре 38 меньше или равно слову, находящемуся в регистре 39.

Таким образом, возможно размещение записываемых в устройство информационных слов в возрастающем или убывающем по их абсолютной величине порядке (при этом исходная информация во всех ячейках блока 11 соответственно равна нулю или единице), а также последозательно в порядке доступ- ления (исходная информация во всех ячейках блока 11 равна нулю).

Считывание информации из устройст- ва выполняется по сигналу на входе 4 Который через мультиплексор 20 пос- тутает на вход вычитания счетчика 18 а через селектор 19 - на первый вход считывания блока 11 . Все инфор мацион- ные слова считываются из блока 11 последовательно, начиная с последней ячейки памяти блока 11, на выход 9.

В режиме сортировки счетчик 18 импульсов подсчитывает число сигналов записи, поступающих через вход 5,т.е число занятых ячеек памяти блока 11, и если все ячейки памяти заняты, то сугнал единицы с выхода счетчика 18 закрывает элеиент И 24, в результате чего на выходе 7 появляется сигнал, запрещающий дальнейшую запись в устройство.

Формула изобретения

Запоминающее устройство, содержащее реверсивный счетчик, элементы ;1 с первого по третий, pacпpeдeлитeJ i сигналов, формирователь сигналов,элементы задержки, элементы ИЛИ и блок памяти, одни из информационных входов и выходов которого являются соответственно информационными входом и выходом устройства, установочным вхо- дом которого являются входы установ- ки реверсивного счетчика, распределителей сигналов и блока памяти,о т- личающееся тем, что, с целью повы,;:ения информационной емкосс

o

5 0

5 О

Q

5

Q

ти устройства в него введены блоки сортировки данных, триггеры, группа формирователей сигналов, формирователи установочных снгналон. г руппа счетчиков сигналов, му.п;.гиалексоры, группа элементов И, группы элементов ИЛИ, элемент ИЛИ-НЕ, группа элемЬн- тов задержки и се-пектор, первый вход которого является адресным входом устройства, а выход подключен к од1:о- му из адресных входов блока памяти, причем один выход первого мультиплексора соединен с первым входом первого элемента ИЛИ, а другой - с входом вычитания реверсивного счетчика и входом первого элемента задержки,выход которого подключен к второму входу первого элемента ИЛИ, которого подключен к одному из входов считывания блока памяти, один из входов записи которого соединен с выходом второго элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, а второй вход - к первому выходу второго мультиплексора,второй выход которого соединен с первым входом третьего элемента И, второй вход которого подключен к выходу второго элемента задержки, вход которо-, го соединен с выходом второго элет мента И, входы которого подключены соответственно к первому выходу реверсивного счетчика и к выходу третьего элемента ИЛИ, входы которого соединены с выходами элементов И группы, прямые входы которых подключены к выходам первого распределителя сигналов, вьгход третьего элемента И соединен с входами третьего и четвертого /элементов задержки, первым входом первого элемента И, тактовыми входами первого и второго распределителей сигналов, управляющие входы которых соединены с вторым входом первого элемента И, выходы второго распределителя сигналов подключены к входам .установки триггеров, выход каждого из которых соединен с соответствующим входом элемента РШИ-КЕ, первым управляющим входом соответйтвующего блока сортировки данных, инверсным входом соответствующего элемента И группы и входом запуска соответствующего формирователя сигналов, выход которого подключен к тактовому входу сбответствующего формирователя установочных сигналов, первому тактовому входу соответствующего блока сортировки данных, соответствующему

входу считыв ;;:ня блока памяти и вхо-- ду соотвеч .-вующего элемента задержки групп:-.. выход которого соединен с входом суммирования соответствующего счетчика сигналов группы, выход каждого формирователя установочных сигналов подключен к первому входу ус- тановк, соответствующего блока сортировки данных, первым входам соответствующих ьогсзнентов ИЛИ первой и второй групп, BiKiOAbi элементов ИЛИ первой группы подключены к входам сброса триггеров, а выходы элементов ИЛИ второй группы - к входам установки счетчиков сигналов группы, вьг,:од каждого из которых соединен с со:; геет- ствуюшлк адресньп-- входом блока ла.я- тп и первым информационным .ьхс, ОМ соответствующего формирователя уста- новочны: : сигналов, вторые информационные входы формирователей установоч- ньгх: сигналов и второй вход селектора подключены к второму вьп .оду-реверсивного счетчика, вход суммирования которого соедикен с выходсл третьего элемента задержки, третий вход селектора соединен с первыми входаь;и мультиплексоров, выход четвертого элемента задержки подключен к вторым

577210

тактовым входам блоков сортировки

данных, одни из информационных входов которых соединены с одними из информационных входов блока памяти, инфор- .- мационный выход и другой информационный вход каждого блока сортировки данных подключены к соответствующим другим информационному входу и информационному выхиду блока памяти, а

f(; тактовый выход ка: Вдс о 6:ioica сортировки данных соединен с соответствующим другим входом записи блока памяти, вторые входы элементов ИЛИ групп, входы установки формирователей уста15 новочных сигналозз и вторые входы установки блоков сортировки данных подключены к входу установки блока памяти, первые входы мультиплексоров,второй вход первого элемента И и втоQ рые управляющие входы блоков сортировки данных являются входами режима работы устройства, индикаторными аькодами которого являются соответственно выход второго элемента за5 держки и выход элемента ИЛИ-НЕ, вторые входы первого и второго г-гульти- плексоров являются соответственно входом считывания и входом записи ycTpoiicTBa.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство сравнения чисел с допусками | 1987 |

|

SU1509870A1 |

| Логический анализатор | 1989 |

|

SU1695303A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Устройство для сортировки информации | 1987 |

|

SU1509871A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть использовано в вычислительных системах для сбора информации при приоритетном обслуживании либо при организации очереди на обслуживание або- кектов. Целью изобретения является (Л оо о СП ND

Hmfi

из 3S

На Ц 2.

Фиг.

| Буферное запоминающее устройство | 1982 |

|

SU1030855A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236555A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-23—Публикация

1985-11-29—Подача