к вторым входам элементов И Р-ой элементов ИЛИ второй группы, выходы группы, информационные входы устрой- , которых подключены к третьим входам ства соединены с вторыми входами элементов И t-ой группы.

10561.96

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления очередностью обслуживания запросов | 1985 |

|

SU1264175A1 |

| Устройство для обслуживания запросов | 1986 |

|

SU1383354A1 |

| Устройство для управления обслуживанием запросов | 1984 |

|

SU1185335A1 |

| Устройство для обслуживания разноприоритетных групп заявок | 1990 |

|

SU1718219A2 |

| Устройство приоритетного обслуживания каналов | 1989 |

|

SU1702369A1 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для обслуживания запросов | 1983 |

|

SU1141412A1 |

| Устройство для приоритетного управления | 1983 |

|

SU1124302A1 |

| Устройство приоритета | 1990 |

|

SU1746382A2 |

Изобретение отнрсится к вычислительной технике, а именно к устройствам промежуточного накопления и управления последовательностью обслуживания запросов на решение функциональных задач при реализации циклической дисциплины обслуживания или в порядке поступления запросов в многомашинных, одномашинных и многопроцессорных вычислительных системах различного назначения.

Известно устройство для организации очереди, содержащее счетчики, узел сравнения, блок памяти, шифратор дешифратор, элементы ИЛИ lj .

Недостатком известного устройства является его низкое быстродействие.

Наиболее близким по технической суш.ности к изобретению является устройство для обслуживания запросов в порядке поступления, содержащее М запоминающих и N-1 промежуточных регистров, 5N групп элементов И,М элементов И, N элементов ИЛИ,К тригге003 регистрации состояний, причем jинформационные входы устройства соединены с первыми входами первых груп элементов И, к вторым входам которых подключены соответствующие выходы элементов И, Выходы i-ой группы элементов И (1-1, 2, ...,N) соединены с единичными входами -го регистра, единичные и нулевые входы j-rb запоминающего регистра (J 1, 2, ...,N -1) соединены с первыми входами элементов, к вторым входам которых подключен первый управляющий вход 2 .

Недостатком известного устройства является ограниченнрсть функциональных воз ожностей. Управление обслуживанием запросов осуществляется толко в порядке поступления. Известное устройство не позволяет .ивать запросы при реализации цикли)еской дисциплины обслуживания.

Цель изобретения - расширение функциональных возможностей путем органи:Зации циклической дисциплины обслуживания.

Поставленная цель достигается тем что в устройство для обслуживания .запросов, содержащее N (N- число запросов) запоминающих и :(N-1) промежуточных М-разрядных регистров, группы элементов И, из которых

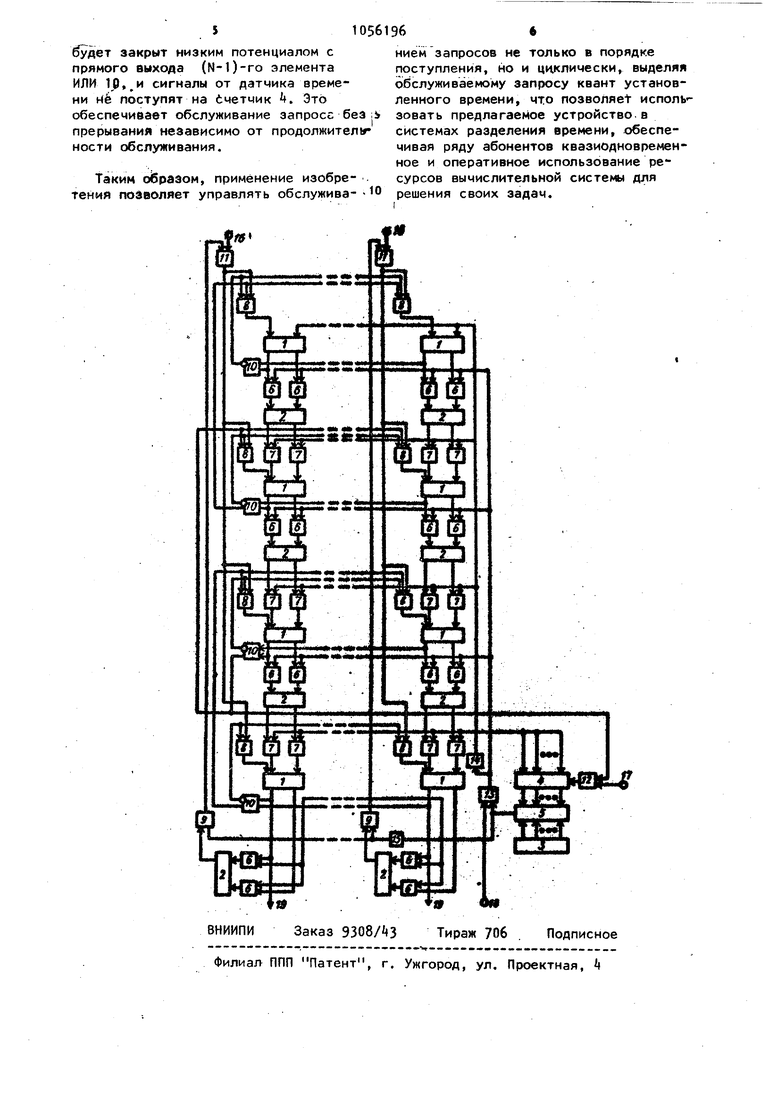

(2N-1) групп содержат по 2М элементов и (N+V) групппо М элементов И, две группы из N элементов ИЛИ, причем прямые и обратные выходы i-ro запоминающего регистра (, 2,...,N соединены с первыми входами элементов И 1-ой группы, выходы которых соединены с соответствующими входами 1 -го промежуточного регистра, пр мые и обратные выходы j-ro промежуточного регистра (, 2, ...,N-1) соединены с первыми входами элементов И К-ой группы ( +j), выходы которых подключены к соответствующим первым нулевым и единичным входам 0+1)-го запоминающего регистра, вторые нулевые входы этих регистров соединены с выходами соответствующих элементов W -ой группы (Г 2N1+j) нулевые выходы i-ro запоминающего регистра подключены к входам .1-го элемента ИЛИ первой группы, инверсный выход которого соединен с первыми входами t-ой .группы элементов И, введены регйстр задания режимов, счетчик, компаратор, элемент И, элемент ИЛИ и два элемента задержки, причем первый вход элемента И под- . ключен к тактовому входу устройства, второй вход - к прямому выходу предпоследнего элемента ИЛИ первой группы, выход элемента И соединен с входом счетчика, установочные входы которого соединены с выходом первого элемента задержки, с первыми входами элементов И К-ой группы () и с единичными входами первого запоминаюегр регистре, выходы счетчика и вы(одь1 регистра задания режимов подключены соответственно к первой и второй группам входов компаратора, выход которого соединен с вторыми входами элементов И N-ой группы, с входом второго элемента задержки и первым входом элемента ИЛИ, втЬрой вход которого соединен с входом разрешения записи устройства, а выход - с входо первого элемента задержки и с вторым входами элементов И первых (N-1) груп выход второго элемента задержки подключен к первым входам элементов И Последней группы, вторые входы которых соединены с нулевыми входами соответствующих разрядов последнего промежуточного регистра, а выход Z-ro элемента И последней группы (,2, ..., М) подключен к перво му входу Z-ro элемента ИЛИ второй группы, Ирямой выход каждого (j+l)элемента ИЛИ первой группы подключен к вторым входам элементов И F-ой группы (I 2N-1+j), информационные входы устройства соединены с вторыми входами элементов ИЛИ второй группы, выходы которых подключены к третьим входам элементов И -ой группы. На чертеже показана схема устройства для N it. Устройство содержит N запоминающи регистров 1 и промежуточных регистров 2, регистр 3 задания режима, сче чик k, компаратор 5, группы элементов И 6 - 9, группы элементов ИЛИ 10 и 11, элемент И 12, элемент ИЛИ 13, элементы и 15 задержки, информационные входы 16, входы 17 и 18 и вы ходы 19. Устройство работает следующим образом. В исходном состоянии регистры 1 и счетчик 4 устайовлены в нулевое сост ние. При обслуживании запросов в порядке их поступления все разряди регистра 3 задания режимов устанавлива ются в единичное состояние. При циклической дисциплине обслуживания в регистр 3 заносится код кванта време ни обслуживания каждого из запросов. На первые входы N-ой группы элемен тов И 8 подается р зрешающий потенциал с инверсного выхода N-ro элемента ИЛИ 10, Поступающий,на входы 16 первый запрос через элементы ИЛИ и N-ю группу элементов И 8 запишетс в N-ый регистр. После записи запроса откроется (М-1)-я группа элементо И 8, так как на.ее входы поступают диничные сигналы с прямого выхода N-ro элемента ИЛИ 10 и инверсного выхода (N-1j-ro элемента ИЛИ 10. Постуающий второй запрос запишется через элементы ИЛИ 11, (Ы-1)-ю группу элементов И 8 в (М-1)-ый регистр. В даль нейшем запись запросов будет происходить аналогично. С выхода М-го регистра запросы поступают на обслуживание. Если очередь содержит более одного запроса, т.е в (N-l)-oM запоминающем регистре 1 записан запрос, то с прямого выхода (N-l)-ro элемента ИЛИЮ единичный сигнал открывает элемент И 12 и импульсы от генератора импульсов времени с кл еммами 1/ поступают на вход счетчика 4. Если за установленное время запрос не будет обнулен, то сигнал с выхода компаратора поступит на входы элементов И 6, и содержимое регистров 1 запишется в соответствующие промежуточные регистры 2. Затем, пройдя элементы 1, сигнал поступит нл входы элементов И 7 и содержимое j -го регистра 2 (j 1, 2,..., N-1) запи1ается в (j+1)-ый регистр 1, а первый регистр 1 установится в ну левое состояние. Затем откроются элементы И 9 сигналом с выхода элемента 15 задержки, и запрос, записанный в N-OM промежуточном регистре, поступит через элементы ИЛИ 11 на вход устройства и запишется в один из очередных свободных регистров 1. Таким образом, необслуженный до конца запрос по истечении заданного кванта времени будет поставлен в конец очереди нп обслуживание. Сигналом с выхода элемента ИЛИ 3 счетчик установится в нулевое состояние. С выходов 19 очередной запрос поступает на обслуживание, а работа устройства продолжается. Если в течение установленного кванта времени очередной запрос будет обслужен, то на вход 18 поступит сигнал, по которому содержимое 1-го регистра 1 через элементы И 6 запишется в соответствующий регистр 2, а затем через элементы И 7 содержимое i-ro регистра 2 запишется в (1-И)-ый регистр 1, а первый регистр 1 установится в нулевое состояние. Счетчик установится в нулевое состояние. На выходных шинах 19 появится очередной запрос. Если в очереди на обслуживание находится один запрос, то элемент И 12

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-11-23—Публикация

1982-08-31—Подача