со 00

со

со О1

4

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах.

Целью изобретения является повышение быстродействия устройства.

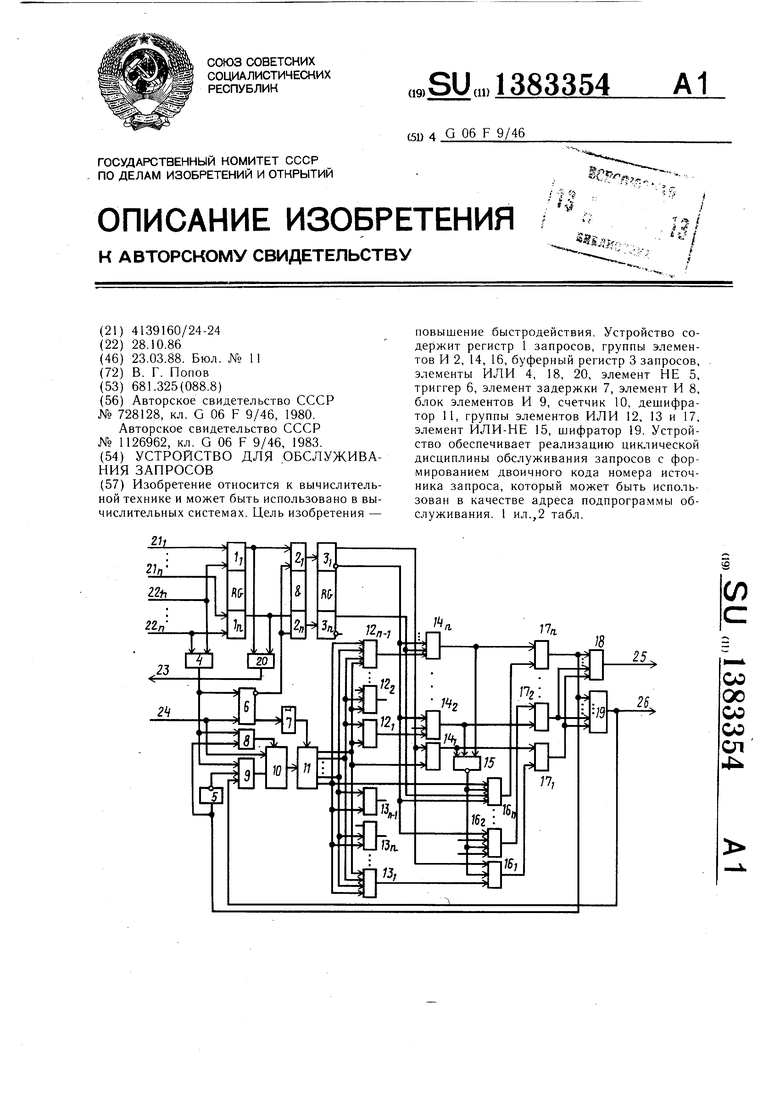

На чертеже приведена структурная схема устройства.

Устройство содержит регистр 1 запросов, группу элементов И 2, буферный регистр 3 запросов, элемент ИЛИ 4, элемент НЕ 5, триггер 6, элемент 7 задержки, элемент И 8, блок элементов И 9, счетчик 10, дешифратор 11, группы элементов ИЛИ 12 и 13, группу элементов И 14, элемент ИЛИ-НЕ 15, группу элементов И 16, группу элементов ИЛИ 17, элемент ИЛИ 18, шифратор 19, элемент ИЛИ 20, запросные 21 и ответные 22 входы, выход 23 готовности, вход 24 запуска, сигнальный выход 25, адресные выходы 26.

Устройство работает следующим образом.

В исходном состоянии регистр 3, триггер 6 и счетчик 10 установлены в состояние «О (не показано).

Устройство обеспечивает реализацию циклической дисциплины обслуживания запросов, причем каждый очередной цикл выбора источника запроса начинается с опроса источника, номер которого на единицу больше обслуженного в предыдущем цикле.

Запросы от источников по входам 21 поступают в соответствующие .разряды регистра 1, и так как триггер 6 находится в состоянии «О, то открыты элементы И 2 единичным сигналом с нулевого выхода .триггера 6. Нри этом зафиксированные запросы в регистре 1 передаются в регистр 3, чем обеспечивается отслеживание поступающих запросов. Нри наличии запросов в регистре 1 элементом ИЛИ 20 формируется единичный сигнал, поступающий в качестве сигнала готовности устройства па выход 23. Но этому сигналу обслуживающее устройство выдает по входу 24 импульс запуска, которым устанавливается в состояние «1 триггер 6, а в счетчике 10 к его содержимому добавляется единица. Нри первоначальном включении устройства в работу в счетчике 10 в данном случае формируется двоичный код единицы.

С помощью элементов ИЛИ 12 и 13 производится управление работой элементов И 14 и 16, обеспечивающих циклический режим обслуживания запросов.

Элементы ИЛИ 12 включены с выходами дешифратора 11 так, что элементами И 14 производится анализ запросов источников, начиная с /-го номера по я-й, где i - номер источников запроса, на единицу больший номера источника, обслуженного в предыдущем цикле.

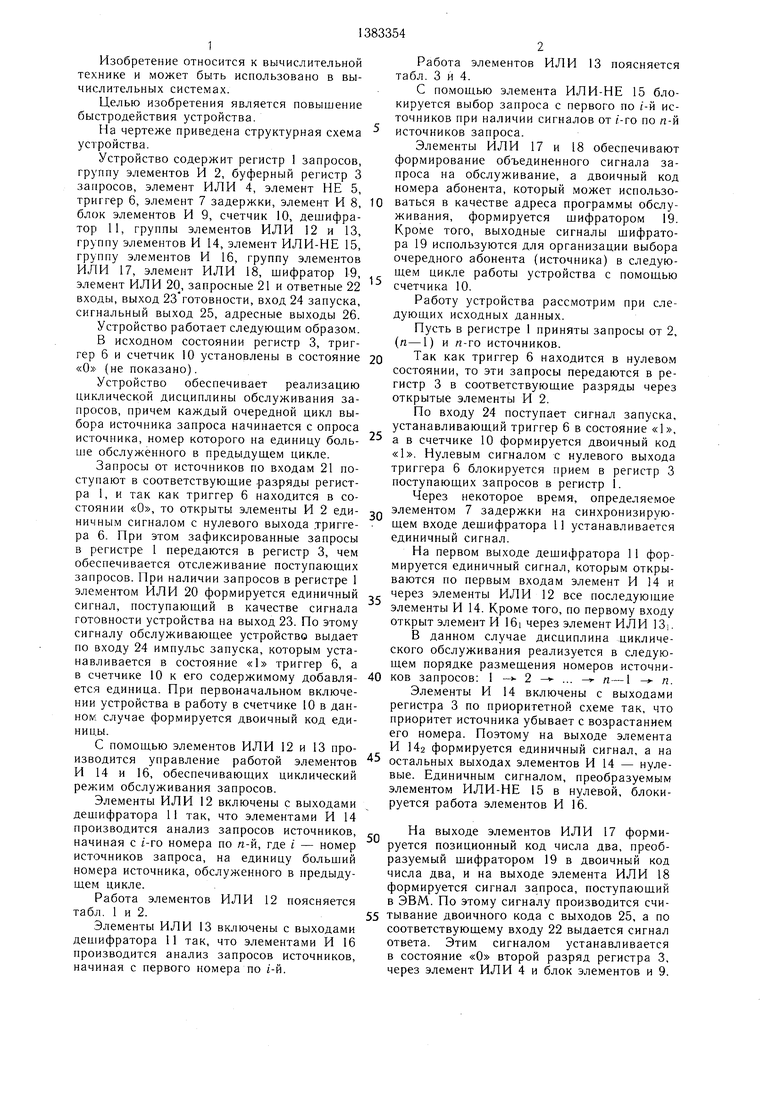

Работа элементов ИЛИ 12 поясняется табл. 1 и 2.

Элементы ИЛИ 13 включены с выходами дешифратора 11 так, что элементами И 16 производится анализ запросов источников, начиная с первого номера по г-й.

0

5

0

-зс

ИЛИ 13 поясняется

Работа элементов табл. 3 и 4.

С помощью элемента ИЛИ-НЕ 15 блокируется выбор запроса с первого по (-и источников при наличии сигналов от i-ro по л-й источников запроса.

Элементы ИЛИ 17 и 18 обеспечивают формирование объединенного сигнала запроса на обслуживание, а двоичный код номера абонента, который может использоваться в качестве адреса программы обслуживания, формируется шифратором 19. Кроме того, выходные сигналы шифратора 19 используются для организации выбора очередного абонента (источника) в следующем цикле работы устройства с помощью счетчика 10.

Работу устройства рассмотрим при следующих исходных данных.

Нусть в регистре 1 приняты запросы от 2, (п-1) и п-го источников.

Так как триггер 6 находится в нулевом состоянии, то эти запросы передаются в регистр 3 в соответствующие разряды через открытые элементы И 2.

Но входу 24 поступает сигнал запуска, устанавливающий триггер 6 в состояние «1, 5 а в счетчике 10 формируется двоичный код «1. Нулевым сигналом с нулевого выхода триггера 6 блокируется прием в регистр 3 поступающих запросов в регистр 1.

Через некоторое время, определяемое элементом 7 задержки на синхронизирующем входе дешифратора 11 устанавливается единичный сигнал.

На первом выходе дешифратора 11 формируется единичный сигнал, которым открываются по первым входам элемент И 14 и через элементы ИЛИ 12 все последуюшие элементы И 14. Кроме того, по первому входу открыт элемент И 16i через элемент ИЛИ 13i.

В данном случае дисциплина .циклического обслуживания реализуется в следую- шем порядке размещения номеров источников запросов: 1 2 - ... п-1 п.

Элементы И 14 включены с выходами регистра 3 по приоритетной схеме так, что приоритет источника убывает с возрастанием его номера. Ноэтому на выходе элемента И Иг формируется единичный сигнал, а на остальных выходах элементов И 14 - нулевые. Единичным сигналом, преобразуемым элементом ИЛИ-НЕ 15 в нулевой, блокируется работа элементов И 16.

30

40

45

50

На выходе элементов ИЛИ 17 формируется позиционный код числа два, преобразуемый шифратором 19 в двоичный код числа два, и на выходе элемента ИЛИ 18 формируется сигнал запроса, поступаюший в ЭВМ. По этому сигналу производится счи- 55 тывание двоичного кода с выходов 25, а по соответствующему входу 22 выдается сигнал ответа. Этим сигналом устанавливается в состояние «О второй разряд регистра 3, через элемент ИЛИ 4 и блок элементов и 9.

открытый единичным сигналом с выхода элемента НЕ 5, производится прием в счетчик 10 двоичного кода числа два и устанавливается в состояние «О триггер 6. После установки триггера 6 в нулевое состояние в регистре 3 оказываются в состоянии «1 только (п-1)-й и «-Й разряды. При этом элементом ИЛИ 20 удерживается единичный сигнал готовности устройства на выходе 23. По окончании обслуживания запроса от второго источника по входу 24 подается импульс запуска, устанавливающий триггер 6 в состояние «1, а в счетчике 10 формируется двоичный код числа три. В дальнейшем устройство работает аналогично рассмотренному. При этом обеспечивается выбор запроса анализа с третьего источника, в силу чего дисциплина циклического обслуживания реализуется в следующем порядке размещения номеров источников запросов: - ...-- л-1 л 1 2.

Единичным сигналом с третьего выхода дещифратора 10 через элементы ИЛИ 122, ---, 12„ открыты по первым входам элементы И 14з, ..., И 14„. Так как в регистре 3 зафиксированы запросы от (п-1)-го и п-го источников, то на выходе элемента И 14п-2 формируется единичный сигнал, которым через элемент ИЛИ-НЕ 15 блокируются элементы И 16. На выходах элементов ИЛИ 17 формируется позиционный код, имеющий единицу на (rt-1)-й позиции. Посредством элемента ИЛИ 18 формируется сигнал запроса, поступающий на выход 15 устройства, а на выходах 26 устанавливается двоичный код числа (п-1).

В дальнейшем по сигналу ответа производится установка в «О (п-1)-го разряда регистра 1 и триггера 6, а также запись в счетчик 10 двоичного кода (п-1), и по очередному сигналу запуска в устройстве устанавливается следующий порядок размещения номеров источников для циклического обслуживания: п - 1 - 2 - ..., п-1.

В соответствии с этим порядком и при наличии запроса в регистре 3 только от п-го источника аналогичным образом на выходе 25 формируется двоичное число п. При этом единичным сигналом с выхода элемента ИЛИ 17л открывается элемент ИЛИ 18, а через элемент НЕ 5 закрывается блок элементов И 9. Поэтому сигналом ответа для п-го источника через элемент ИЛИ 4 устанавливается в состояние «О триггер 6, п-й разряд регистра 1 и через элемент И 8 счетчик 10. При этом единичный сигнал на выходе 23 устройства снимается.

Если же регистр 1 оказывается в нулевом состоянии по сигналу ответа для источника запросов, номер которого не равен п, то счетчик 10 принимает двоичный код обслуженного источника, а устройство переходит в режим ожидания запросов. Как только в регистр 1 поступит хотя бы один запрос, на выходе 23 формируется сигнал готовности,

по которому обслуживающее устройство выдает сигнал запуска по входу 24. При этом анализ содержимого регистра 1 выполняется с номера источника, на единицу больного обслуженного в предыдущем цикле работы устройства.

Элементы И 16 формируют позиционный код номера источника в тех случаях, когда после выдачи на обслуживание запроса от

i-ro источника в регистре 3 имеются запросы в разрядах с 1-го по /-и включительно. В этом случае после обслуживания запроса от ( -го источника по сигналу ответа в счетчике 10 формируется двоичный код числа (/-|-1). После установки триггера 6 в состояние «1

на (/+1)-м выходе дешифратора 11 появляется единичный сигнал, которым через элементы ИЛИ 13i, ..., 13, открываются элементы И 16i, ..., 16,-+i по первым входам. Кроме того, единичным сигналом с (/-(-1)-го выхода дешифратора 11 через элементы

ИЛИ 12, ..., открываются элементы И 14,-+:, ..., 14„. Но так как запросы в разрядах с (г+1)-го по л-й регистров 3 отсутствуют, то на выходе элемента ИЛИ-НЕ 15 формируется единичный сигнал, которым

открываются по вторым входам все элементы И 16. Этими элементами в дальнейшем формируется позиционный кад номера источника, который через элемент ИЛИ 17 передается на входы элемента ИЛИ 18 и щифрато- ра 19. Далее устройство работает аналогично рассмотренному.

Формула изобретения

Устройство для обслуживания запросов,

содержащее регистр запросов, единичные входы разрядов которого являются группой запросных входов устройства, нулевые входы регистра запросов являются группой ответных входов устройства, триггер, единичный вход которого является входом запуска устройства, элемент И, первый элемент ИЛИ, выход которого является сигнальным выходом устройства, элемент задержки, счетчик, дещифратор, входы которого соединены с выходами счетчика, первую группу

элементов И, причем первый вход i-ro элемента И первой группы (, 2, ..., п, п - число источников запросов) подключен к выходу г -го разряда регистра запросов, отличающееся тем, что, с целью повышения быстродействия, в него введены шифратор,

выходы которого являются адресными выходами устройства, три группы элементов ИЛИ, вторая и третья группы элементов И, элемент ИЛИ-НЕ, буферный регистр запросов, элемент НЕ, блок элементов И, второй

элемент ИЛИ, выход которого является выходом готовности устройства, и третий элемент ИЛИ, входы которого подключены к ответным входам устройства, выход третьего элемента ИЛИ подключен к первому входу

элемента И, первому управляющему входу блока элементов И и нулевому входу триггера, нулевой выход которого соединен с вторыми входами элементов И первой группы, выходы которых подключены к единичным входам одноименных разрядов буферного регистра запросов, вход запуска устройства соединен со счетным входом счетчика, уст- тановочные входы которого подключены к выходу блока элементов И, второй управ- ляюплий вход которого соединен с выходом элемента НЕ, группа входов блока элементов И подключена к выходам шифратора, единичный выход триггера соединен через элемент задержки с управляющим входом дещифратора, первый выход которого подключен к первому входу первого элемента И второй гр-уппы и первым входам элементов ИЛИ первой группы, /-и выход дешифратора (,. 3, ..., л) соединен с /-ми входами с (/-1)-го по (п-1)-й элементов ИЛИ первой группы, п-й выход дещифратора соединен с первым входом «-го элемента И третьей группы и первыми входами элементов ИЛИ второй группы, (п-2)-и выход дешифратора (, 2, ..., п-1) подключен к (2+1)-м входам с первого по (п-2)-й элементов ИЛИ второй группы, выход 2-го элемента ИЛИ первой группы соединен с первым вхо

5 Q 5 5

0

дом (2+1)-го элемента И второй группы, выход 2-го элемента ИЛИ второй группы подключен к первому входу 2-го элемента И третьей группы, единичный выход/-го разряда буферного регистра запросов соединен с вторым входом i-ro элемента И второй группы и вторым входом /-ГО элемента И третьей группы, инверсный выход г -го разряда буферного регистра запросов соединен с (г-(-2) -м входом (г+1)-го и последующих элементов И второй группы и с (/+3)-м входом (г+1)-го и последующих элементов И третьей группы, выход г -го элемента И второй группы подключен к первому входу /-ГО элемента ИЛИ третьей группы и г -му входу элемента ИЛИ-НЕ, выход которого соединен с третьими входами элементов И третьей группы, выход I -ro элемента И третьей группы подключен к второму входу /-ГО элемента ИЛИ третьей группы, выходы элементов ИЛИ третьей группы подключены к соответствующим входам первого элемента ИЛИ и входам щифратора, выход п-го элемента ИЛИ третьей группы соединен с входом элемента НЕ и с вторым входом элемента И, выходы регистра запросов подключены к соответствующим входам второго элемента ИЛИ, выход элемента И соединен с входом сброса счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство переменного приоритета | 1983 |

|

SU1151964A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство переменного приоритета | 1986 |

|

SU1383353A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для обслуживания группы запросов | 1989 |

|

SU1674124A1 |

| Устройство для управления обслуживанием запросов | 1979 |

|

SU855663A1 |

| Устройство приоритета с шифрацией номера абонента | 1984 |

|

SU1193676A1 |

| Устройство для обслуживания группы запросов | 1988 |

|

SU1562913A1 |

| Устройство для организации очереди | 1986 |

|

SU1434431A2 |

| Устройство для поиска данных | 1990 |

|

SU1795447A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах. Цель изобретения - повышение быстродействия. Устройство содержит регистр 1 запросов, группы элементов И 2, 14, 16, буферный регистр 3 запросов, элементы ИЛИ 4, 18, 20, элемент НЕ 5, триггер 6, элемент задержки 7, элемент И 8, блок элементов И 9, счетчик 10, дешифратор 11, группы элементов ИЛИ 12, 13 и 17, элемент ИЛИ-НЕ 15, шифратор 19. Устройство обеспечивает реализацию циклической дисциплины обслуживания запросов с формированием двоичного кода номера источника запроса, который может быть использован в качестве адреса подпрограммы обслуживания. 1 ил.,2 табл.

О 1

п-1

Таблица 1

О О

О О

О О

О 1

Номер эле-Выходные сигналы элементов ИЛИ 12

ментов И 1411

,L.....:L..

11

211

11

n-11111

11111

Т л б П и 17 я3

---СодержимоеНомер выходов дешифратора 11

счетчика.,..

--J-- L.L.i.:::..

110000

/

21000

оо

п-110

П1

Таблица А

Номер эле-Выходные сигналы элементов ИЛИ 13

ментов И 16:111

11111

2111

11

п-111

п1

Таблица 2

| Устройство для обслуживания запросов | 1978 |

|

SU728128A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для обслуживания запросов | 1983 |

|

SU1126962A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-28—Подача