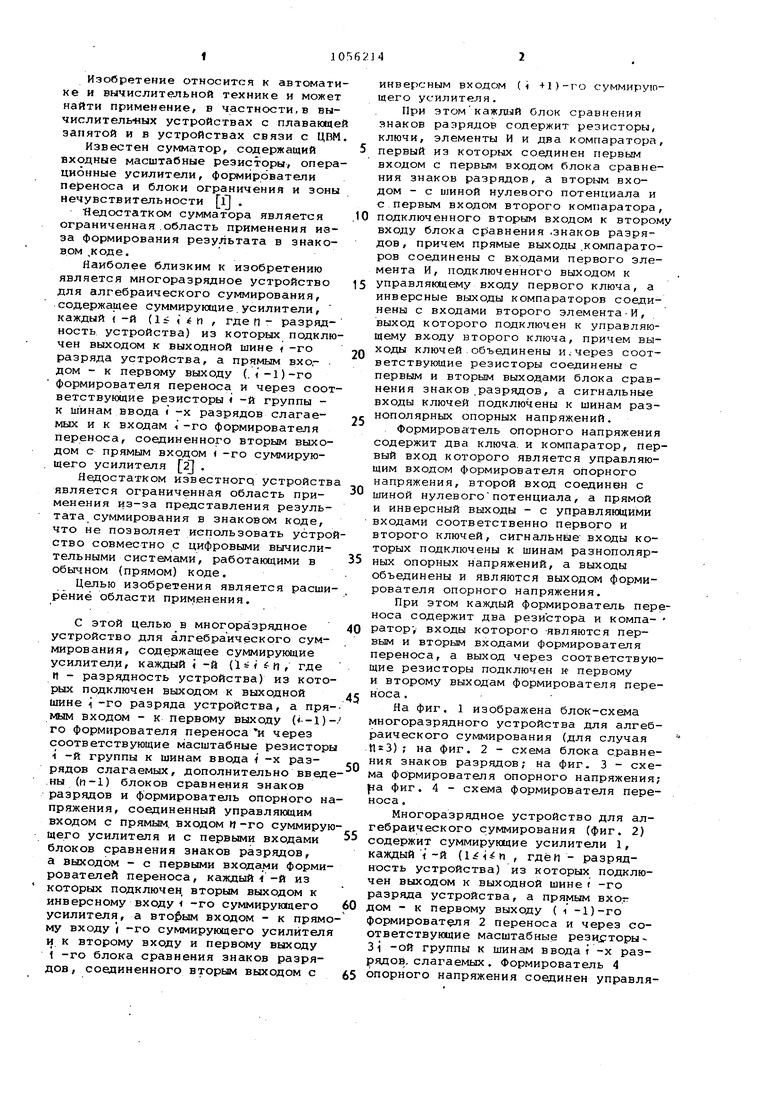

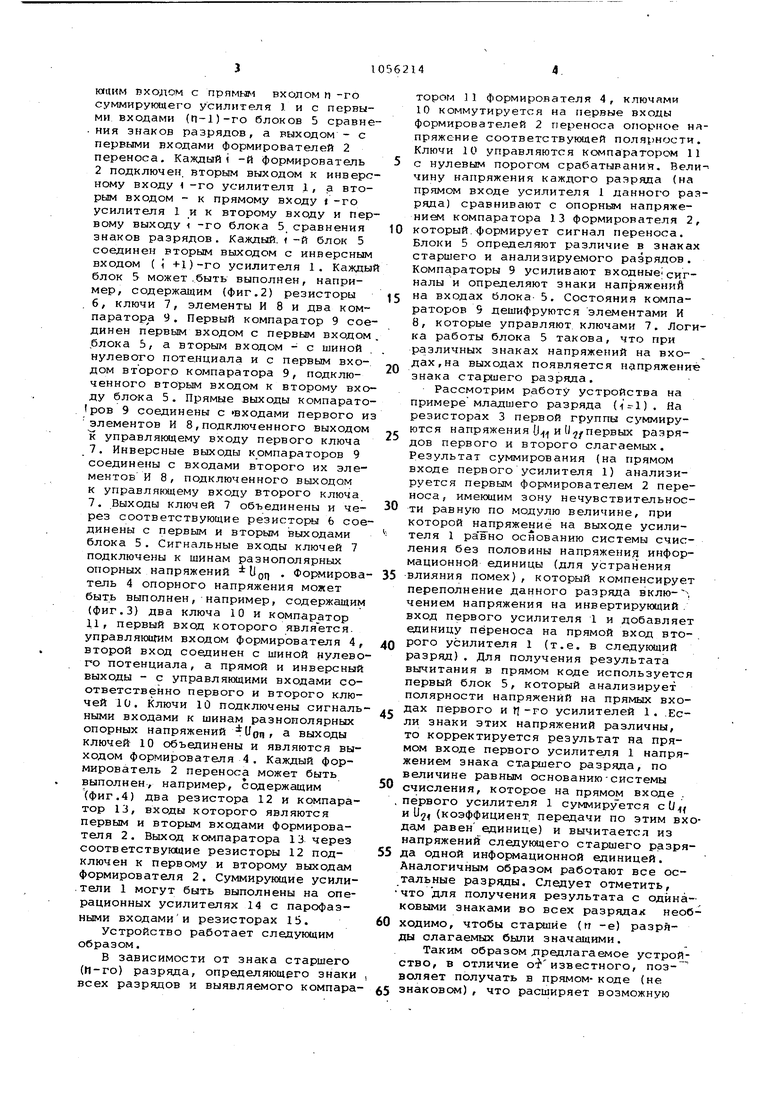

Изобретение относится к автомати ке и вычислительной технике и может найти применение, в частности,в вычислитель-ных устройствах с плавающе запятой и в устройствах связи с ЦВМ Известен сумматор, содержащий входные масштабные резисторы, опера ционные усилители, формирователи переноса и блоки ограничения и зоны нечувствительности f , Недостатком сумматора является ограниченная .область применения изза формирования результата в знаковом ,коде. Наиболее близким к изобретению является многоразрядное устройство для алгебраического суммирования, содержащее суммирующие.усилители, каждый -и (1 ( п , где п - разрядность устройства) из которых подклю чен выходом к выходной шине -го разряда устройства, а прямым вхо,- . дом - к первому выходу (.-)-го формирователя переноса и через соот ветствующие резисторы -и группы к шинам ввода -х разрядов слагаемых и к входам -го формирователя переноса, соединенного вторым выходом с прямым входом f -го суммирующего усилителя 2 . Недостатком известногр устройств является ограниченная область применения из-за представления результата суммирования в знаковом коде, что не позволяет использовать устро ство совместно с цифровыми вычислительными системами, работающими в обычном (прямом) коде. Целью изобретения является расши рение области применения. С этой целью в многоразрядное устройство для алгебраического суммирования, содержащее суммирукяцие усилители, каждый -и ( П , где ц - разрядность устройства) из кото рых подключен выходом к выходной шине i -го разряда устройства, а пря мым входом - к первому выходу (--) го формирователя переноса и через соответствующие масштабные резистор л -и группы к шинам ввода i -х разрядов слагаемых, дополнительно введ .ны (n-l) блоков сравнения знаков разрядов и формирователь опорного н пряжения, соединенный управляющим входом с прямым, входом и -го суммиру щего усилителя и с первыми входами блоков сравнения знаков разрядов, а выходом - с первыми входами форми рователей переноса, каждый -и из которых подключен, вторым выходом к инверсному входу -го суммирую(цего усилителя, а вторым входом - к прям му входу 1 -го суммирующего усилител и к второму входу и первому выходу i -го блока сравнения знаков разрядов, соединенного вторым выходом с инверсным входом (i +1.)-то суммирующего усилителя. При этомкаждый блок сравнения знаков разрядов содержит резисторы, ключи, элементы И и два компаратора, первый из KOTOpiJX соединен первыги входом с первым входом блока сравнения знаков разрядов, а вторым входом - с шиной нулевого потенциала и с первым входом второго компаратора, подключенного вторым входом к второму входу блока сравнения .знаков разрядов, причем прямые выходы .компараторов соединены с входами первого элемента И, подключенного выходом к управляющему входу первого ключа, а инверсные В1з1ходы компараторов соединены с входами второго элемента-И, выход которого подключен к управляющему входу второго ключа, причем выходы ключей объединены и.: через соответствующие резисторы соединены с первым и вторым выходами блока сравнения знаков разрядов, а сигнальные входы ключей подключены к шинам разнополярных опорных напряжений. Формирователь опорного напряжения содержит два ключа, и компаратор, первый вход которого является управляющим входом формирователя опорного напряжения, второй вход соединен с шиной нулевогопотенциала, а прямой и инверсный выходы - с управляющими входами соответственно первого и второго ключей, сигнальные входы которых подключены к шинам разнополярных опорных напряжений, а выходы объединены и являются выходом формирователя опорного напряжения. При этом каждый формирователь переноса содержит два резистора и компа- ратор; входы которого -являются первым и вторым входами формирователя переноса, а выход через соответствующие резисторы подключен к- первому и второму выходам формирователя переноса . На фиг. 1 изображена блок-схема многоразрядного устройства для алгебраического суммирования (для случая ) ; на фиг. 2 - схема блока сравнения знаков разрядов; на фиг. 3 - схема формирователя опорного напряжения; fia фиг. 4 - схема формирователя переноса . Многоразрядное устройство для алгебраического суммирования (фиг. 2) содержит суммирующие усилители 1, каждый 1-и ( , гдём - разрядность устройства) из которых подключен выходом к выходной шине ( -го разряда устройства, а прямым вхо.г дом - к первому выходу ( -i -1)-го формирователя 2 переноса и через соответствующие масштабные рези сторы 3i -ой группы к шинам вводаt -х разрядов, слагаемых. Формирователь 4 опорного напряжения соединен управляюцим входом с прямым вхолом п -го суммиругаяего усилителя ) и с первыми входами (ri-l)-ro блоков 5 сравнения знаков разрядов, а выходом - с первыми входами формирователей 2 переноса. Каждый -и формирователь 2 подключен, вторым выходом к инверсному входу 1 -го усилителя 1, а вторым входом - к прямому входу -го усилителя 1 и к второму входу и первому выходу i -го блока 5. сравнения знаков разрядов. КаждЕЛй. « -и блок 5 соединен вторым выходом с инверсным входом ( i +1)-го усилителя 1. Каждый блок 5 может.быть выполнен, например, содержащим (фиг.2) резисторы

6,ключи 7, элементы И 8 и два компаратора 9. Первый компаратор 9 соединен первым входом с первым входом . блока 5, а вторым входом - с шиной нулевого потенциала и с первым входом второго компаратора 9, подключенного вторым входом к второму входу блока 5. Прямые выходы компаратоpoB 9 соединены с «входами первого из элементов И 8,подключенного выходом к управляющему входу первого ключа

7.Инверсные выходы компараторов 9 соединены с входами второго их элементов И 8, подключенного выходом

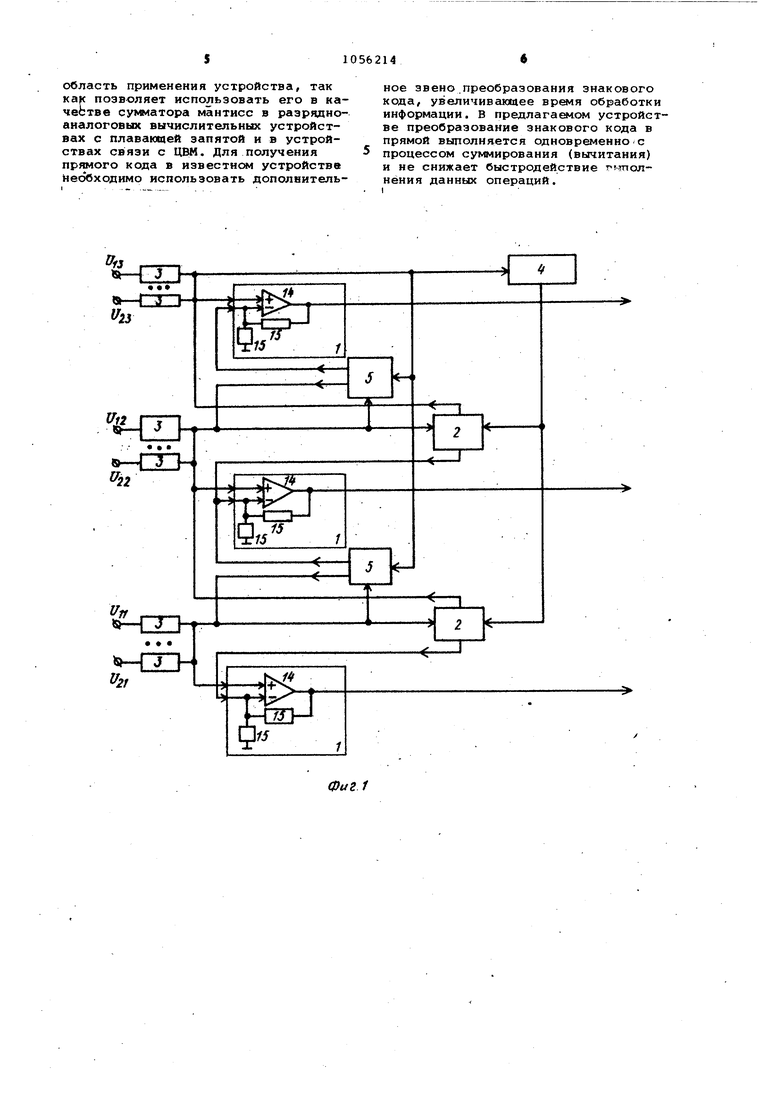

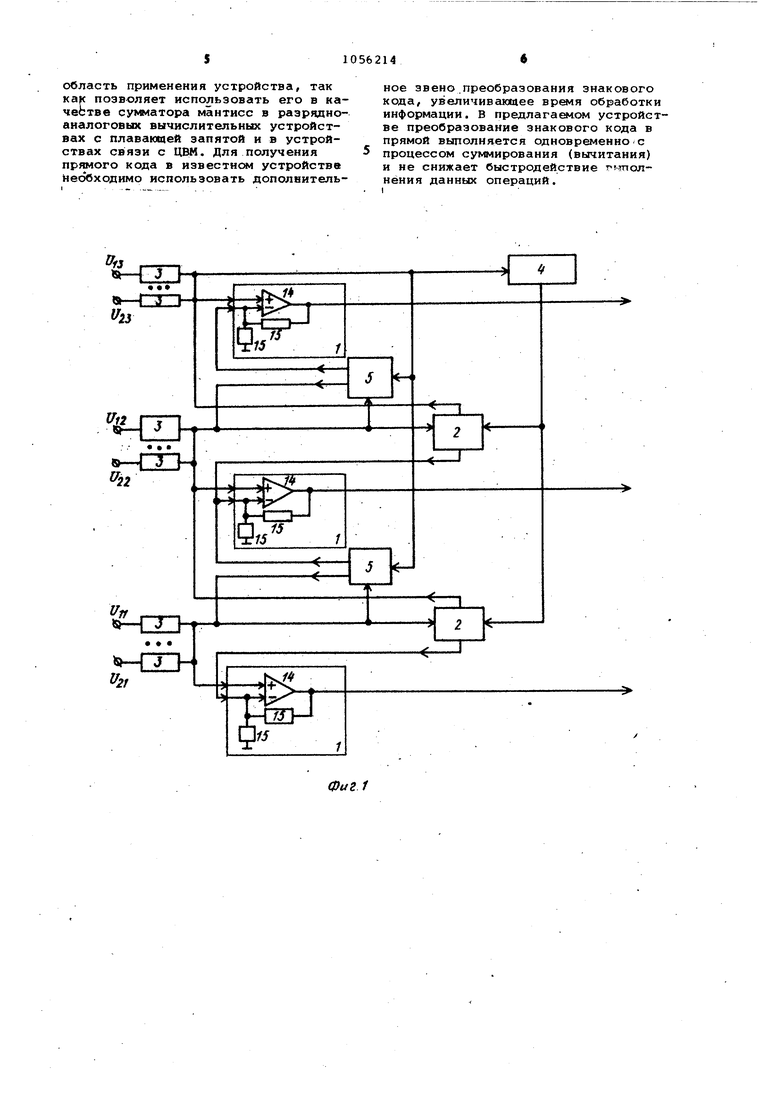

к управляющему входу второго ключа 7. Выходы ключей 7 объединены и через соответствующие резисторы 6 соединены с первым и вторым выходами блока 5. Сигнальные входы ключей 7 подключены к шинам разнополярных опорных напряжений И . Формирователь 4 опорного напряжения может быть выполнен, например, содержащим (фиг.З) два ключа 10 и компаратор 11, первый вход которого является. управляквдим входом формирователя 4, второй вход соединен с шиной нулевого потенциала, а прямой и инверсный выходы - с управляющими входами соответственно первого и второго ключей 10. Ключи 10 подключены сигнальными входами к шинам разнополярных опорных напряжений Попf а выходы ключей 10 объединены и являются выходом формирователя 4. Каждый формирователь 2 переноса может быть выполнен, например, содержащим (фиг.4) два резистора 12 и компаратор 13, входы которого являются первым и вторым входами формирователя 2. Выход компаратора 13 через оответствующие резисторы 12 подлючен к первому и второму выходам ормирователя 2. Суммирующие усилители 1 могут быть выполнены на операционных усилителях 14 с парофазными входамии резисторах 15.

Устройство работает следующим бразом.

В зависимости от знака старшего (Ц-го) разряда, определяющего знаки , сех разрядов и выявляемого компаратором 1 формирователя 4, ключами 10 коммутируется на первые входы формирователей 2 переноса огторное напряжение соответствующей поля)ности. Ключи 10 управляются компаратором 11 с нулевым порогом срабатываний. Величину напряжения каждого разряда (на прямом входе усилителя 1 данного разряда) сравнивают с опорным напряжением компаратора 13 формирователя 2,

0 который.формирует сигнал переноса. Блоки 5 определяют различие в знаках старшего и анализируемого разрядов. Компараторы 9 усиливают входные; сигналы и определяют знаки напряжений

5 на входах блока- 5. Состояния компараторов 9 дешифруются элементами И 8, которые управляют ключами 7. Логика работы блока 5 такова, что при различных знаках напряжений на вхо дах,на выходах появляется напряжений знака старшего разряда.

Рассмотрим работу устройства на примере младшего разряда (i-l). На резисторах 3 первой группы суммируются напряжения/J ;( и (/ первых разрядов первого и второго слагаемьох. Результат суммирования (на прямом входе первого усилителя 1) анализируется первым формирователем 2 переноса, имеющим зону нечувствительнос0 ти равную по модулю величине, при которой напряжение на выходе усилителя 1 раЖно основанию системы счисления без половины напряжения информационной единицы (для устранения

5 влияния помех), который компенсирует переполнение данного разряда вклю- л чением напряжения на инвертирующий . вход первого усилителя 1 и добавляет единицу переноса на прямой вход вто-.

д рого усилителя 1 (т.е. в следукмий разряд). Для получения результата вычитания в прямом коде используется первый блок 5, который анализирует полярности напряжений на прямых входах первого усилителей 1. .Если знаки этих напряжений различны, то корректируется результат на прямом входе первого усилителя 1 напряжением знака старшего разряда, по величине равным основанию-системы

0 счисления, которое на прямом входе . .первого усилителя 1 суммируется c(J и Uj, (коэффициент, передачи по этим входа 1 равен единице) и вычитается из напряжений следующего старшего разря5 да одной информационной единицей. Аналогичным образом работают все остальные разряды. Следует отметить, что для получения результата с одинаковыми знаками во всех разрядах необ0 ходимо, чтобы стаЕяийе (п -е) разряды слагаемых были значащими.

Таким образом лреялагаемое устройство, в отличие oi известного, позволяет получать в прямом- коде (не

5 знаковом), что расширяет возможную

Область применения устройства, так как поэв-оляет использовать его в качестве cyh iaTopa мантисс в раэрядноаналоговых вычислительных устройствах с плавающей запятой и в устройствах связи с ЦВИ. Для получения пряного кода в известнее устройстве Иес)6ходимо использовать дополнительное звено .преобразования знакового кода, увеличивающее вроня обработки информации. В предлагаи14ом устройстве преобразование знакового кода в прямой выполняется одновременно с процессом суммирования (вычитания) и не снижает быстродействие rt-тполнёния данных операций.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дискретной записи и воспроизведения функций | 1981 |

|

SU982034A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Генератор пилообразного напряжения | 1990 |

|

SU1758854A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ПИТАНИЯ ДЛЯ ИЗМЕРИТЕЛЯ УГЛОВОЙ СКОРОСТИ ВОЛОКОННО-ОПТИЧЕСКОГО | 1996 |

|

RU2115211C1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1985 |

|

SU1269265A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1043692A1 |

| Преобразователь напряжения в частоту | 1982 |

|

SU1077048A1 |

| Устройство для дискретного преобразования Фурье | 1984 |

|

SU1188751A1 |

1. МНОГОРАЗРЯДНОЕ УСТРОЙСТВО ДЛЯ АЛГЕБРАИЧЕСКОГО СУММИРОВАНИЯ, содержащее суммируюцие усилители, каждый i-и (, где rt - разряд-i ность устройства) из которых подключен выходном к выходной шине i -го разряда устройства,,а прямым входом - к первому выходу (i-l)-ro фррмирователя переноса и через соответствующие масштабные резисторы i -и группы - к ши-; нам ввода « -х разрядов слагаемых, отличающееся тем, что, с целью расширения области применения, в него дополнительно введены (И-1). блоков сравнения знаков разрядов и формирователь опорного напряжения, соединенный управляющим входом с прял. мым входом г -го суммируквдего усилителя и с первыми входами блоков сравнения знаков разрядов, а выходом с первыми входами формирователей переноса, каждый -и из которых подключен вторым выходе к инверсному входу 1 -го суммирующего усилителя,а вторым входом - к прямому входу i -го суммирующего усилителя и к второму входу и первому выходу i -го ,блока сравнения знаков разрядов, соединенного вторым выходом с инверсным входом ( +1)-го суммирующего усилителя. 2. Устройство по п, 1, о т л ичающеес я тем, что каждый блок сравнения знаков разрядов содержит резисторы ключи, элементы И и два компаратора, первый из которых сое- . дивен входом с первым входом блока сравнения знаков разрядов, а вторьм входсад - с шиной нулевого потенциала и с. первым входом второго ксмпаратора, подключенного вторам входом к второму входу блока сравнения знаков разрядов, причем прямые выходы компараторов соединены с входами первого элемента И, подключенного выходсм к управляющему входу первого ключа, а инверсные выходы компараторов соединены с входами второго элемента И, выход которого подключен к управляющему входу второго ключа, причем выходы ключей объединены и через соответствующие резис(О торы соединены с первым и вторым выходами блока сравнения знаков разс: рядов ,.а сигнальные входы ключей подключены к шинам разнополярных .опорных напряжений. 3.Устройство по п. 1, о т л ич.ающееся тем, что формирователь опорного напряжения содержит два ключа и кс таратор, первый вход которого является управляющим входом :л формирователя опорного напряжения, з: второй вход соединен с шиной нулевоND го потенциала, а прямой и инверсный выходы - с управляющими входами соответственно первогЪ и второго ключей, сигнальные входы которых подключены к шинам разнополярн опорных напряжений, а выходы объединены, и являются выходом формирователя опорного напряжения.. 4.Устройство по пп.1 и 3, о т-, личаюцееся тем, что каждый формирователь переноса содержи два резистора и компаратор., входы кото рого являются первым и вторым входами формирователя переноса, а вы ход через соответствующие резисторы подключен к первому и второму выходам формирования переноса.

фие.З

Ь ffoH П

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Одноразрядный сумматор | 1972 |

|

SU463990A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ И ВЫЧИТАНИЯ | 1971 |

|

SU423132A1 |

| . | |||

Авторы

Даты

1983-11-23—Публикация

1981-07-21—Подача