(54) ОДНОРАЗРЯДНЫЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1978 |

|

SU769540A1 |

| Устройство для суммирования нескольких Р-ичных чисел | 1983 |

|

SU1188730A1 |

| ПАРАЛЛЕЛЬНЫЙ ЧАСТОТНЫЙ СУММАТОР | 1967 |

|

SU204709A1 |

| Устройство для сложения в избыточной двоичной системе счисления | 1977 |

|

SU696450A1 |

| СПОСОБ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1997 |

|

RU2109325C1 |

| ОБРАТИМЫЙ МНОГОРАЗРЯДНЫЙ СУММАТОР С УМНОЖЕНИЕМ НА ПОСТОЯННЫЙ КОЭФФИЦИЕНТ | 1971 |

|

SU419906A1 |

| Комбинационный сумматор | 1975 |

|

SU570896A1 |

| Устройство для умножения | 1977 |

|

SU769539A1 |

| Преобразователь кодов | 1973 |

|

SU526884A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

1

Изобретение относится к области гибридой вычислительной техники.

Известно устройство для суммирования сигалов одной полярности в двоичной системе числения, содержащее линейку резисторов, ервые зажимы которых соединены со входаи сумматора, и п входных резисторов.

К недостаткам известного устройства относится возможность суммирования сигналов только одного знака, ограничение количества входов за счет того, что алгебраическое суммирование входных сигналов осуществляется посредством пассивных цепей, а также за счет того, что нулевому значению суммы не соответствует нуль напрял{ения на выходе схемы.

Предложенный сумматор отличается тем, что с целью повышения точности содержит резисторы переноса и п операционных усилителей, в цепи обратной связи каждого из которых включены блок зоны нечувствительности « блок ограничения. Входы операционных усилителей через соответствующие входные резисторы соединены с общей точкой линейки резисторов и через соответствующие резисторы переноса - с выходами последующих операционных усилителей.

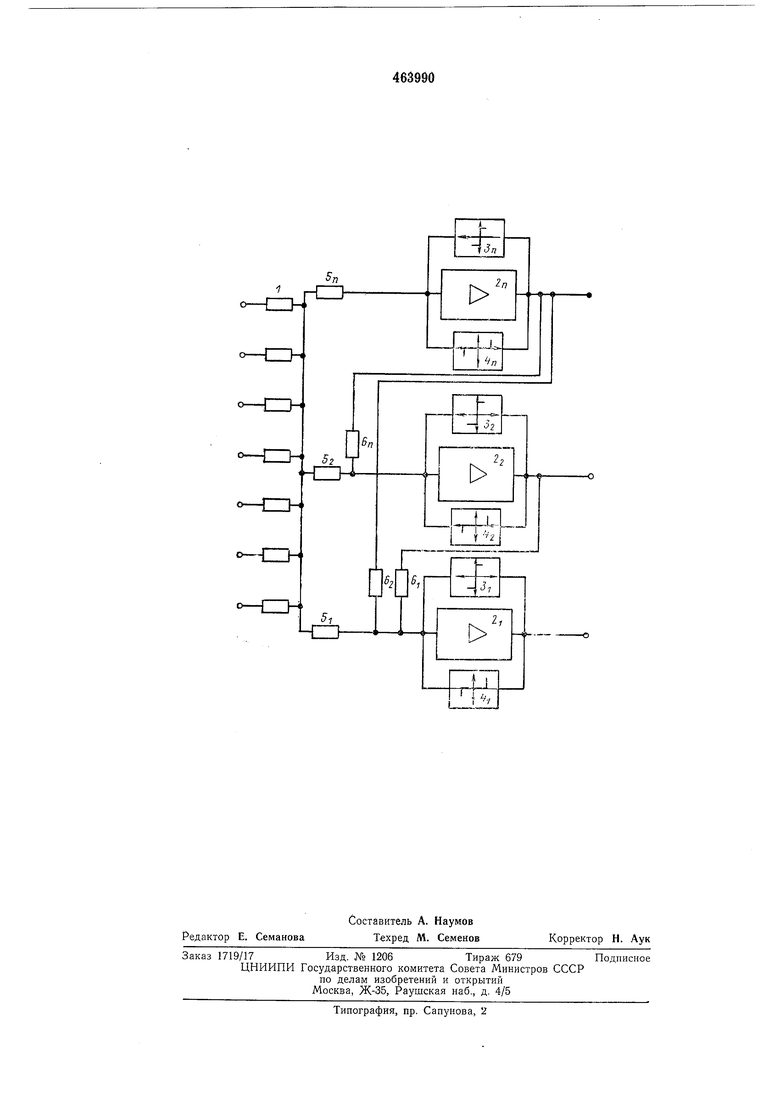

Структурная схема одноразрядного сумматора приведена на чертеже.

Сумматор содержит линейку резисторов 1, п операционных усилители , в цепи обратной связи каждого из которых включены блоки ограничения 3i-3 и блоки зоны нечувствительности 4i-4„. Ко входу каждого усилителя подключены входные резисторы и резисторы переноса 6i-6п.

Резисторы переноса 6i-6 предназначены для передачи сигнала с выходов операционных усилителей постоянного тока старщих разрядов н,а вход операционных ,усилителей младщих разрядов сЪпределенным коL -2

эффициентом передачи . Зоны нечув15

ствительности построены следующим образом (от младщего к старщему):

1,5е

у

зоны - и,0ед.

20

П/-1

ед.

яоны -

Предложенный сумматор работает следующим образом.

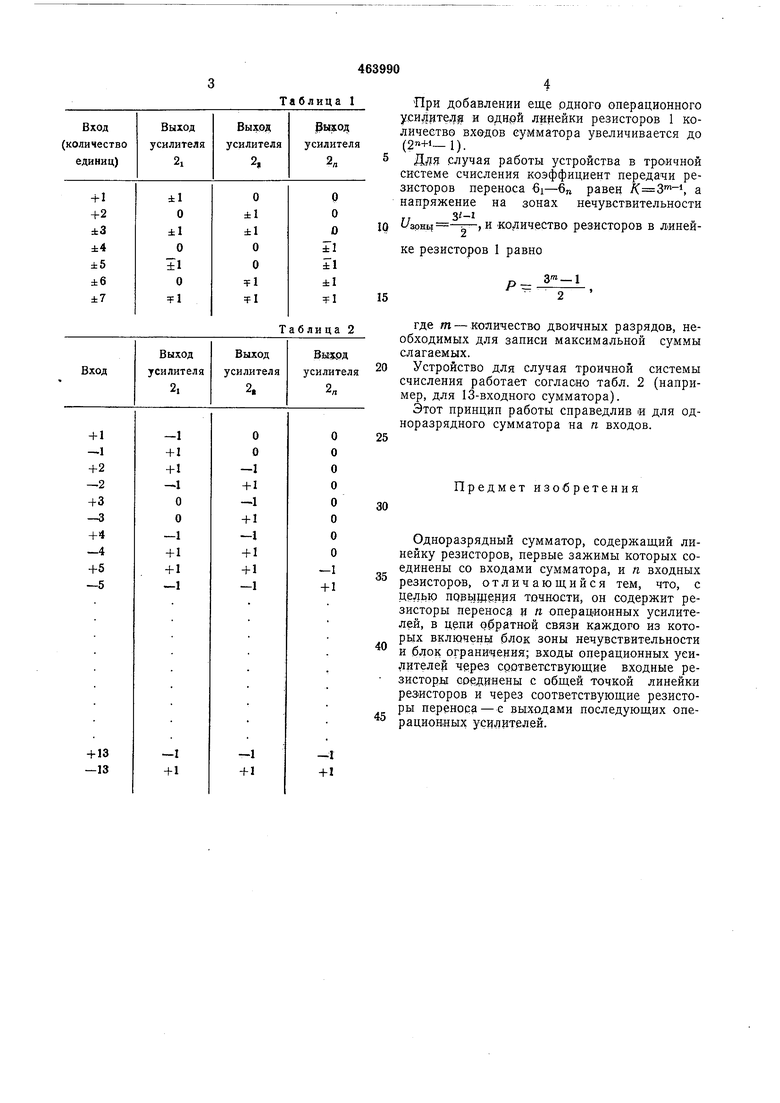

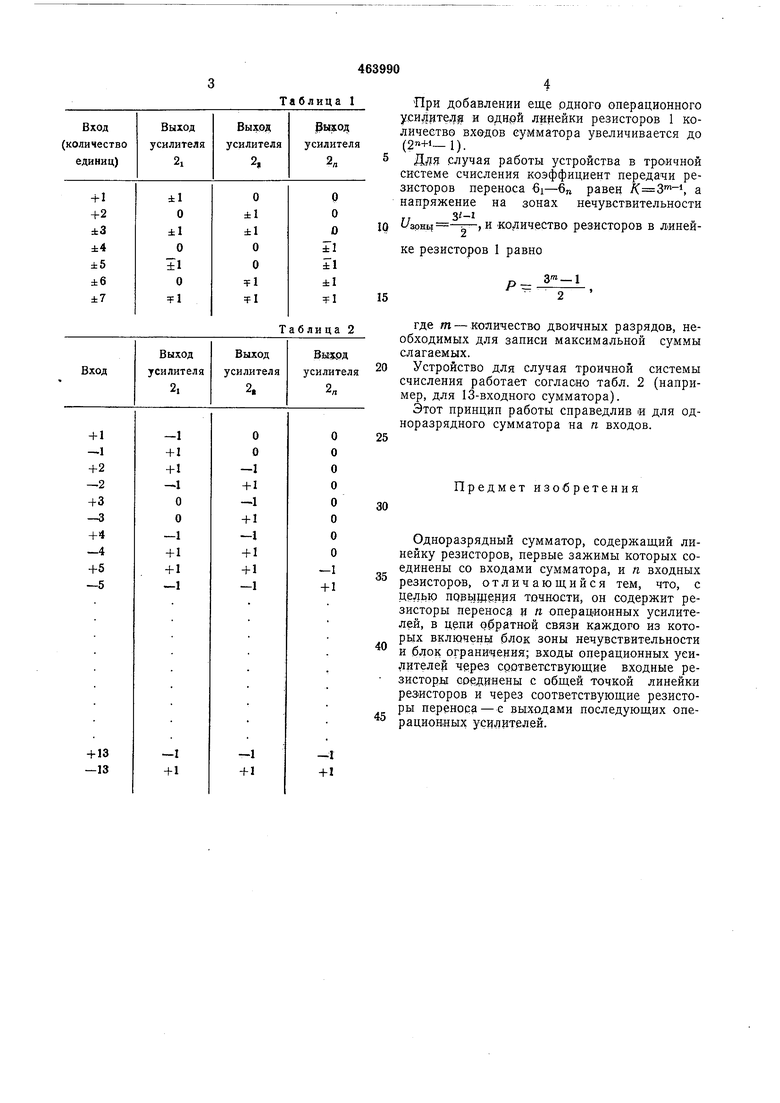

Информация поступает на вход устройства в двоичной системе счисления в знаковом коде 1; 0; - I, т. е. каждый разряд имеет свой знак. Устройство для случая двоичной системы счисления работает согласно табл. 1.

Таблица 1

Таблица 2

4

При добавлении еще .одного операционного усиляте. и однрй лирейки резисторов 1 количеетве входов сумматора увеличивается до ().

Для случая работы устройства в троечной системе счисления коэффициент передачи резисторов переноса 6i-6п равен а напряжение на зонах нечувствительности

,,3-1

1/зрнь| -ir-j и количество резисторов в линейке резисторов 1 равно

3 -1

Р

где m - количество двоичных разрядов, необходимых для записи максимальной суммы слагаемых.

Устройство для случая троичной системы счисления работает согласно табл. 2 (например, для 13-входного сумматора).

Этот принцип работы справедлив « для одноразрядного сумматора на п входов.

Предмет изобретения

Одноразрядный сумматор, содержащий линейку резисторов, первые зажимы которых соединены со входами сумматора, и п входных резисторов, отличающийся тем, что, с целью повышения точности, он содержит резисторы переноса и п операционных усилителей, в цепи обратной связи каждого из которых включены блок зоны нечувствительности и блок ограничения; входы операционных усилителей через соответствующие входные резисторы соединены с общей точкой линейки резисторов и через соответствующие резисторы переноса-с выходами последующих операционных усилителей.

Авторы

Даты

1975-03-15—Публикация

1972-11-17—Подача