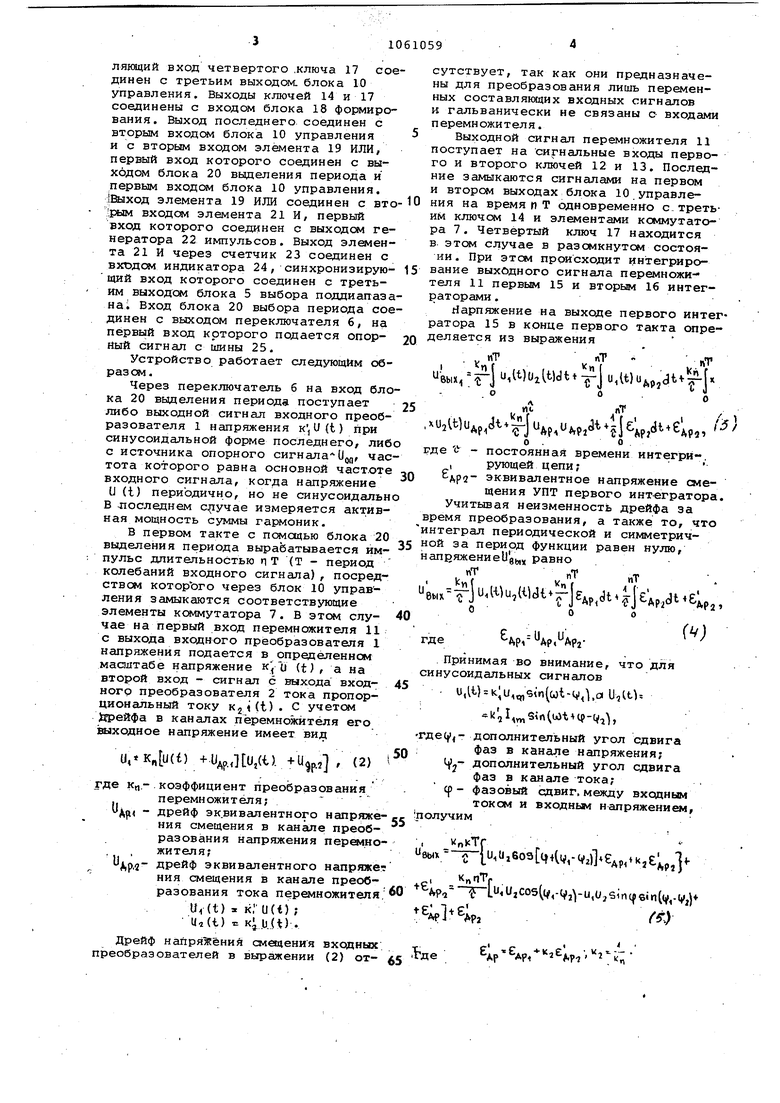

Изобретение относится к цифровой - электроизмерительной технике и может 5,ыть применено при построении измери телей активной мощности непрерывных и радиоимпульсных колебаний. По основному авт. св. № 970250 известен цифровой измеритель мощности, содержащий первый и второй входные преобразователи, входы которых подключены к шинам входных сигналов а управляющие-входы - к первому и второму выходам блока выбора диапазона, входы которого подключены к выходам преобразователей,третий выход которого -соединен с синхронизирующим входом индикатора, вход которого через счетчик соединен с выходо элемента И, входы которого подключен соответственно к выходам генератора импульсов и элемента ИЛИ, первый вхо которого подключен к первому входу блока управления коммутатором и чере блок ВБщеления периода и переключатель, к входной шине опорного сигнал или к выходу первого входного преобр зователя, а второй вход элемента ИЛИ подключен к второму входу блока управления коммутатором и через последовательно соединеннае двухтатный интегрирующий преобразователь и 5 множитель к выходам комг утатора, первый вход которого через инвертор, а второй непосредственно подключены к выходу первого входного преобразователя, третий вход - к выходу второго входного преобразователя, четвертый и пятый входы - к выходам источника Опорного сигнала, а управлягацие вхоЛы - к выходам блока управления ксмр утатором щ . В известном устройстве измеряемая мсмцность определяется как полусумма результатов двух циклов измерения, каждый из которых состоит из двух тактов где Р - итоговое значение мощности; Р.- результат первого цикла измерения;р„ - результат второго цикла измерения:к - постоянный коэффициент;. е - суммарное напр5шение смещения перемножителя и двухтактного интегрирующего преобразсвателя. Второе слагаемое i выражения (1) представляет погрешность, которая вносится из-за наличия дрейфов напря женин смодения пер шожителя и УПТ интегратора, она во много раз меньше аналогичной погрешносги при двухтактном интегрировании, Недостатком этого цифрового измери.теля модности является сравнительно невысокая точность измерения мощности вследствие существенного влияния на результат измерения дрейфа эквивалентного напряжения смацения одного из каналов перемножителя и угловых погрешностей, обусловленных неравенством сдвига фаз в каналах преобразования, а также сдвига фаз между напряжением и током. Цель изобретения - повышение точности измерения. Поставленная цель достигается тем, что двухтактный интегрирующий преобразователь .содержит блок формирования, четыре ключа и два интегратора, входы которых через первый и второй ключи соответственно подключены к входу двухтактного интегрирующего преобразователя, а выходы через третий и четвертый ключи соответственно к входу блока формирования, выход которого является выходом двухтактного интегрирующего преобразователя, управляющие входы всех ключей подключены к дополнительным выходам блока управления коммутатором. На фиг. 1 приведена структурная схема цифрового измерителя активной МОЩНОСТИ; на фиг. 2 - временные диагpaj iMH. Устройст во содержит первый 1 и . второй 2 входные преобразователи напряжения и тока, входы которых подключены к шинам 3 и 4 входных сигналов. Управляющие вх.оды входных преобразователей подключены соотвественно к первому и второму выходам блока 5 выбора диапазона. Выход входного преобразователя 1 напряжения подключен к второму входу переключате/ я б, к второму входу блока 5 выбора диапазона, к второму входу коммутатора 7 и к входу инвертора 8. Выход последнего соединен с первым входом коммутатора 7. Выход входного преобразователя 2 тока подключен к третьему входу колМутатора 7 и к первому входу блока 5 выбора диапазона. Выходы источника 9 опорных напряжений соединены с четвертым и пятым входами коммутатора 7 . Управляющие входы последнего соединены с выходами блока 10 управления.Оба выхода коммутатора 7 соединены с входами перемножителя 11. Выход последнего соединен с входами первого 12 и второго 13 ключей. Управляющий вход первого ключа 12 соединен с первьп выходом блока 10 управления и управляющим входсм третьего ключа -14, а управляющий вход второго ключа 13 соединен с вторым выходсм блока 10 управления. Выходы обоих ключей соединены с входами соответственно первого 15 и второго 16 интеграторов Выходы последних соединены соответственно с входами третье,го 14 и четвертого 17 ключей. Управлягаций вход четвертого .ключа 17 сое динен с третьим выходом, блока 10 управления. Выходы ключей 14 и 17 соединены с входом блока 18 формирования. Выход последнего соединен с вторым входом блока 10 управления и с вторым входом элемента 19 ИЛИ, первый вход которого соединен с выходом блока 20 выделения периода и первым входсми блока 10 управления. ;1Выход элемента 19 ИЛИ соединен с вто упал входом элемента 21 И, первый вход которого соединен с выходом генератора 22 импульсов. Выход элемента 21 И через счетчик 23 соединен с вход см индикатора 24, синхронизирую щий вход которого соединен с третьим выходом блока 5 выбора поддиапаза на Вход блока 20 выбора периода сое динен с выходом переключателя 6, на первый вход которого подается опорный сигнал с шины 25. Устройство работает следующим образ см. Через переключатель б на вход бло ка 20 выделения периода поступает либо выходной сигнал входного преобразователя 1 напряжения KJ U (t) при синусоидальной форме последнего/ либ с источника опорного сигнала- и д, час тота которого равна основной частоте входного сигнала, когда напряжение U (t) периодично, но не синусоидальн В лоследнем случае измеряется активная мощность суммы гармоник. В первом такте с псмацью блока 20 выделения периода вырабатывается импульс длительностью пТ (Т - период колебаний входного сигнала), посредством которЪго через блок 10 управления замыкаются соответствующие элементы коммутатора 7. В этом случае на первый вход перемножителя 11 с выхода входного преобразователя 1 напряжения подается в определенном маалтабе напряжение к, о (t) , а на второй вход - сигнал с выхода входного преобразователя 2 тока пропорциональный току ). С учетсм Йрейфа в каналах пёремножитёля его выходное напряжение имеет ви;ц и,() +идр.,КиД). .j , (2) где к.- коэффициент преобразования пёремножитёля; Дц - дрейф эквивалентного напряжения смещения в канале преобразования напряжения перемножителя; дрейф эквивалентного напряжения смещения в канале преобразования тока перемножителя Ifv(t) г kriKt) ; .) K.uJt) . Дрейф напряжений смешения входных преобразователей в выражении (2) отсутствует, так как они предназначены для преобразования лишь переменных составляющих входных сигналов и гальванически не связаны с входа ми перемножителя. Выходной сигнал перемножителя 11 поступает на сигнальные входы первого и второго ключей 12 и 13. Последние замыкаются сигналами на первом и втором выходах блока 10 управления на время п Т одновременн о с третьим ключом 14 и элементами коммутатора 7. Четвёртый ключ 17 находится в этсм случае в разомкнутом состояии. При этсм происходит интегрирование выходного сигнала перемножи- теля 11 первым 15 и вторым 16 интеграторами . Нарпяжение на выходе первого интегратора 15 в конце первого такта определяется из выражения пТпТ V -f- U,lt)UiitMtt: J U,lt), и II ,WUAp,,p,U,,p,,cJt.e,p,, о .о где V - постоянная времени интегрй-. I рующей цепи; др2- эквивалентное напряжение смещения УПТ первого интегратора. Учитывая неизменность дрейфа за время преобразования, а также то, что нтеграл периодической и симметричой за период функции равен нулю, напвяжениеи9(я равно пТпТ„т 6ь,x fjuЛi)u,(Шt/,Je,p Jtv-JeAP., ооо А,р,,%2. Принимая во внимание, что для синусоидальных сигналов li,W ,q,(ut-i,l,a и,,jI,Sin(u)t4ip-cv,j, rfie(ff- дополнительный угол сдвига фаз в канале напряжения; Ц), дополнительный угол сдвига фаз в канале тока; ср - фазовый сдвиг, между входным током и входньм напряжением, получим . Ueb.,(l,,-v,)eAp,K, , КпПТ) rPa Fl jCOS((#,-(,),(v,.V,) с -иг сАР Ар Напряжение на выходе второго интегратора 16 в конце первого такта при pafeeHCTBe постоянных времени t,. с t, оравно u,U2COSCycos((( -«(.,, гдеС; 1р EAPI +. Efp-j- дрейф эквивалентного-напряжения смещения второго интегратора. В течение первого такта выходным кмпульсом блока 20 выделения периода открывается элемент 19 ИЛИ, что приводит к срабатыванию элемента 21 и, и на вход счетчика 23 поступает числ импульсов N пТ Nr-ir, где Тд - период импульсов генератора 22 импульсов. После окончания первого такта интегрирования сигнал с выхода блока 20 вьзделения периода поступает на блок 10 управления, который размыкает второй ключ 13, а первый 12 и третий 14 ключи остаются в замкнутом состоянии. Одновременно с помощью . того же блока 10 управления подключаюгся определенные элементы коммутатора 7 таким образом, что на вход перемножителя 11 подается напряжение ( -Uo«) а на второй входио2 Выходное напряжение перемножителя и,Кп(-ио,,-ио,Чр.АР,оЛ.(8)

р ..p..f7t - /Y/;

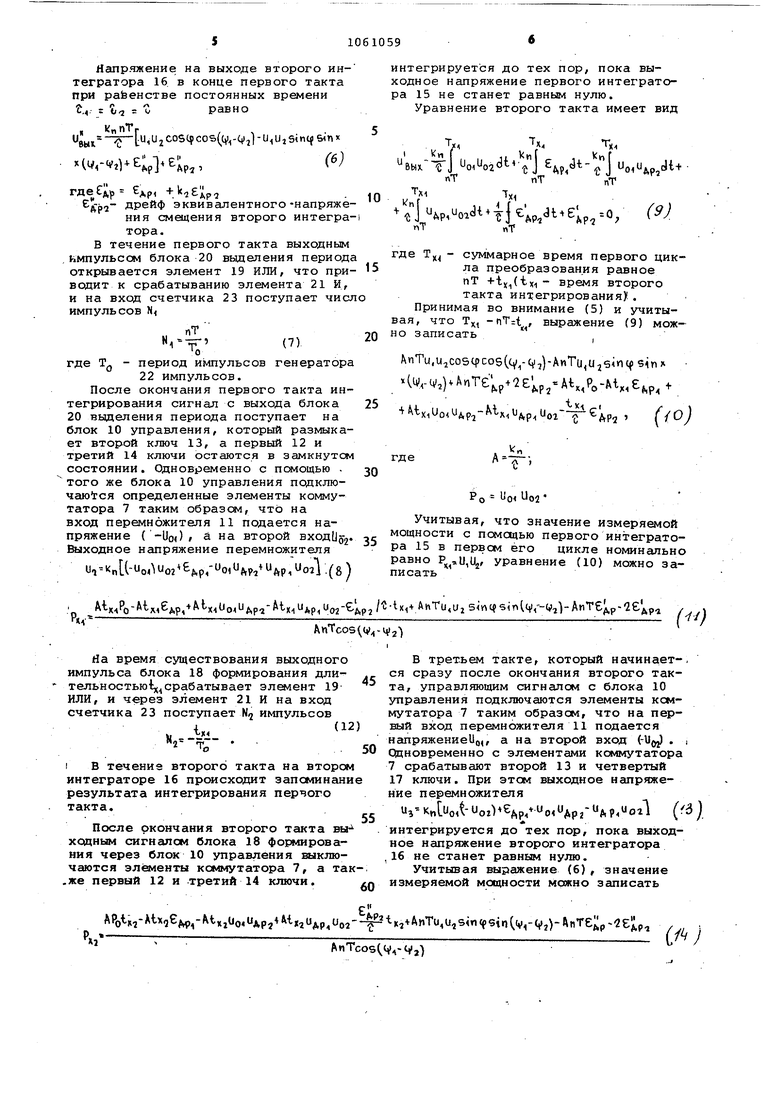

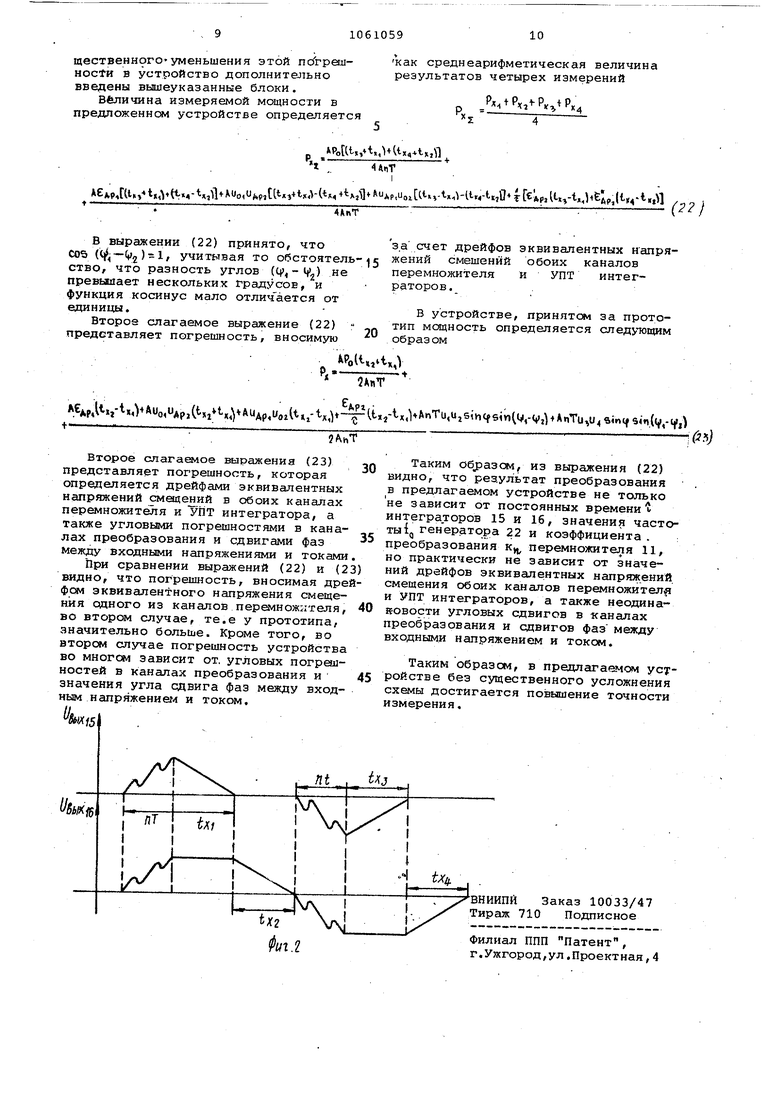

/АпТсоз.) На время существования выходного импульса блока 18 формирования длительностью4х срабатывает элалент 19 ИЛИ, и через элемент 21 И на вход счетчика 23 поступает No импульсов 1(12) 1 т„ I в течение второго такта на втором интеграторе 16 происходит запоминание результата интегрирования первого такта. После окончания второго такта вы ходным сигналом блока 18 фО жшрования через блок 10 управления выключаются элементы коммутатора 7, а так ,же первый 12 и третий 14 ключи. APon,,- txJUo,UApJ4Hx.. нтегрируется до тех пор, пока выодное напряжение первого интегратора 15 не станет равным нулю. Уравнение второго такта имеет вид 1)4« выГт Uo ioa t Ед. Uo,u p dl пТпТпТ.ьlfe;p dl..o; (9J лТпТ где Т - cyiv iapHoe время первого цикла преобразования равное пТ +tK,(txi - время второго такта интегрирования. Принимая во внимание (5) и учитывая, что TX, -nTrt, выражение (9) можно записать, ДпТи,и,,со51рсо5(,1.,)-А«Ти,и.2е4П{ | sin Hu-vW lvAnTe piQE p.., t ,,p,-Mx,u p Uor-f AP5 , ({O) гдеA -pr, Po Учитывая, что значение измеряемой мощности с помоцью первого интегратора 15 в первом его цикле номинально равно , уравнение (10) можно записатьв третьем такте, который начинает-, ся сразу после окончания второго такта, управляющим сигналом с блока 10 управления подключаются элементы коммутатора 7 таким образом, что на первый вход перемножителя 11 подается напряжениеи,, а на второй вход (-UQ . , Одновременно с эло 1ентами коммутатора 7 срабатывают второй 13 и четвертый 17 ключи. При этом выходное напряжение перемножителя Ui- «W-Uoz)e,. ( интегрируется до тех пор, пока выходное напряжение второго интегратора ,16 не станет равным нулю. Учитывая выражение (6) , значение измеряемой MOIOHOCTH можно записать ,a.Tu,.(psin((.,-(г)- nГeAp-2el;,p , L/ / ,-1у2) где, время третьего такта интегриров ани я. В третьем такте на вход счетчика 23 поступает « импульсов После окончания третьего такта . преобразования размыкаются все элеме.н ты коммутатора 7, а также первый 12, второй 13, третий 14 и четвертый 17 ключи. При этой схема возвращается в исходное состояние. В четвертом такте второго цикла, который начинается сразу после окончания третьего такта, вновь с выхода блока 20 выделения периода на вход блока 10 управления поступает импульс длительностью г Т, который через соответствующие элементы коммутатора 7 подключает к первому входу перемножителями сигнал пропорциональный току К i(-t) , а к второму входу инвертированный инвертором 8 сигнал, пропорциональный напряжению - KU(t). Одновременно с элементами коммутатора на то же время ( Т включаются первый 12 второй 13 и третий 14 ключи. При этом в момент времени пТ от начала четвертого такта напряжение на выходе первого интегратора 15 равно вых (r,-Ч2() K- e,,.elp,ekp,.(6)

Н,,,едр,+ А1 эио11Ар2 хэиАРлио1 -,,+ 2е(,р -АпТи,и4в1пСр5«п11,)

в тиестом такте управляющим сигна лом блока 10 управления включаются соответствующие элементы коммутатора 7 и второй 13 и четвертый 17 ключи,при этом на входы перемножителя 11 подаются опорные сигналы (-Uo«) и (-Uflij) . Интегрирование длится до тех пЪр, пока значение выходного напряжения второго интегратора 16 не ста,,,i,b,v.-,c,,4. случае использования в дЬух циклах 55 преобразования только одного интегратора 15, причем с перекрестным изме- . РХ/РХ, Poitx,H,,.гЧVAV

2AnTcos((4-V7 в значительной степени будет влиять погрешность, значение которой про- 5

AttTcos((4i;,-(i)

нет равным нулю. После-окончания второго цикла преобразования все элементы коммутатора 7 а также ключи 12,13,14 к 17 размыкаются, при этом схема устанавливается в исходное положение.

Значение измеряемой мощности во втором цикле преобразования с помощью

второго интегратора 16 равно AnTcosAu r4j)

Учитывая честность функции косинус и нечетность функции синус, выраже- . ние (16) можно записать следующим образе lj6bixi t ° ( Аналогично напряжение на выходе втор рого интегратора 16 Р момент време|ни пТ равно Lv Т И J4 f „ течение, пятого такта преобраэования на втором интеграторе 16 происходит запоминание результата интегрированияив„ при это второй и четвертый 17 ключи находятся в разомкнутом состоянии.Одновременно на первом интеграторе 15 происходит интегрирование произведения опорных « игналов.ио, этсж такте совместно с элементами коммутатора 7 находятся в замкнутом состоянии первый 12 и третий 14 ключи. Пятый такт длится до тех пор, пока напряжение на выходе первого интегратора 15 не станет равным нулю. После его окончания первый 12 и третий 14 ключи размыкаются. Значение измеряемой мощности во втором цикле преобразования посредстве первого интегратора 15 равно . нением в третьем такте входов перег/йюжителя:, на результат измерения,)AЦ,p,Uo,txvtx ЧU,-txУ порционально величине дрейфа одного каналов перемнржителя; Для фсу

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель мощности | 1982 |

|

SU1092422A2 |

| Цифровой измеритель мощности | 1981 |

|

SU970250A1 |

| Цифровой измеритель мощности | 1979 |

|

SU815658A1 |

| Цифровой измеритель мощности | 1977 |

|

SU661378A1 |

| Цифровой измеритель RLc-параметров | 1980 |

|

SU868629A1 |

| Интегрирующий аналого-цифровой преобразователь | 1977 |

|

SU705672A2 |

| Устройство для измерения температуры | 1987 |

|

SU1472771A1 |

| Цифровой измеритель -пара-METPOB | 1979 |

|

SU808977A1 |

| Цифровой вольтметр действующего значения | 1981 |

|

SU1073707A1 |

| Способ аналого-цифрового преоб-РАзОВАНия и уСТРОйСТВО для ЕгООСущЕСТВлЕНия | 1979 |

|

SU839050A1 |

ЦИФРОВОЙ ИЗМЕРИТЕЛЬ МОЩЙОСТИ, по авт. св. I 970250, отличающийся тем, что, с целью повышения точности измерения, двухтактный интегрирующий преобразователь содержит блок формирования, четыре ключа и два интегратора, входы которых через первый и второй ключи соответственно подключены к входу двухтактного интегрирующего преобразова-, теля, а выходы через третий и четвертый ключи соответственно - к входу блока формирования, выход которого является выходом двухтактного интегрирующего преобразователя, причон управляющие входы всех ключей подключены к дополнительным выходам блока Управления кс 1мутатооом. со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-12-15—Публикация

1982-03-03—Подача