Изобретение относится к цифровой, электроизмерительной технике и может найти применение при построении интегрирующих аналого-цифровых преобразователей. Известен способ аналого-цифрового преобразования двухтактным интегриро ванием, основанный на И41тегрировании входного напряжения в течение первого такта длительностью, кратной периоду сетевой помехи, с последующим интегрированием опорного напряжения обратной полярности во втором такте и квантованием импульсами образцовой частоты интервала времени второго такта LI. Недостатком этого способа является влияние на точность преобразования искажений помехи и ее начальной фазы. Наиболее близким к предлагаемому является способ аналого-цифрового преобразования, заключающийся в том, что в каждом цикле преобразова ния интегрируют входное напряжение в течение первого такта, затем интегрируют во втором такте опорное напряжение обратной полярности вход ному напряжению, квантуют импульсами образцовой частоты интервал врем ни от начала второго такта до момента равенства нулю проинтегрированного напряжения, через половину периода сетевого напряжения от начала первого такта интегрируют входное напряжение в третьем такте длительностью, равного длительности первого такта, затем интегрируют в четвертом такте опорное напряжение обратной полярности входному напряжению, квантуют импульсами образцовой частоты интервал времени от начала четвертого такта до момента равенства нулю проинтегрированного напряжения, результат преобразования определяют как полусумму числа импульсов, полученных во втором и четвертом-тактах, и устройство для осуществления указанного способа, содержащее блок запуска и последовательно соединенные блок переключения, интегратор и нуль-орган, выход которого подключен ко входу блока управления, к первому входу формирователя интервалов времени и к первому входу nepBdro ключа, второй вход koTOрого подключен к первому входу формирователя интервалов времени, второй выход которого подключен к управляющему входу блока переключения, два других входа блока переключения

подключены к шлходу источника входного сигнала и выходу источника опорного напряжения, третий вход первого ключа соединен с выходом генератора образцовой частоты, а выход первого ключа подключен к счетному входу первого счетчика, информационные выхода1 которого через первый регистр-сумматор соединены со входами запоминающего регистра, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к управляющему входу первого регистра-сумматора 23.

Недостатком данного изобретения является низкая точность аналого-цифрового преобразования при действии несимметричного напряжения помехи.

Цель изобретения - повьяшенне трчности.

Поставленная цель достигается тем что согласно способу аналого-цифрового преобразования, заключающемуся в том, что в каждом цикле преобразования интегрируют входное напряжение в течение первого такта, затем интегрируют во втором такте, сшорное напряжение обратной полярности входному напряжению, квантуют импульсами образцовой частоты интервал времени от начала второго такта до момента равенства нулю проинтегрированног напряжения, через половину периода сетевого напряжения от начала первог такта интегрируют входное напряжение в третьем такте длительностью, равной длительности первого такта, затем интегрируют в четвертом такте опорное напряжение обратной полярности входному напряжению, квантуют импульсами образцовой частоты интервал времени от начала четвертого такта до момента равенства нулю проинтегрированного напряжения, результат преобразования определяют как полусумму числа импульсов, полученных во втором и че1вертом тактах, в каждом следующем цикле преобразования начало интегрирования в первом и третьем тактах смещают относительно предыдущего цикла на интервал времени, пропорциональный разности числа импульсов, полученных во вторсж и четвертом тактах.

Такой способ может быть осуществлен устройством, содержащим блок запуска и последовательно соединенные блок переключения, интегратор и нуль-орган, выход которого подключен ко входу блока управления, к первому входу формирователя интервалов времени и к первому входу первого ключа, второй вход которого подключен к первому выходу Формирователя интервалов времени, второй выход которого подключен к управляющему входу блока переключения, два других входа блока переключения подключены к выходу источника входного напряжения у

выходу источника опорного напряжения, третий вход первого ключа соединен с выходом генератора образцово частоты, а ,выход первого ключа подключен к счетному входу первого счетчика, информационные выходы которого через первый регистр-сумматор соединены со входами запоминающего регистра, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к управляющему входу первого регистра-сумматора, в который дополнительно введены второй ключ, второй счетчик, второй и третий регистры-сумматоры и блок совпадения кодов, первые инфсрма1у1онные входы которого подключены через третий и второй регистры-сумматоры к информационным исходам первого счетчика, а вторые информационные входы - к информационным выходам второго счетчика, счетный вход которого подключен к выходу второго ключа, первый вход которого связан с выходом блока запуска, второй вход - с выходом генератора образцовой частоты, а третий вход -. с выходом блока совпадения кодов, вторым входом формирователя интервалов времени и входами сброса первого и второго счетчиков, причем управляющие входы второго и третьего регистров-сумматоров подключены к управляющим входам первого регистраcyjuiMaTopa и запоминакщего регистра соответственно.

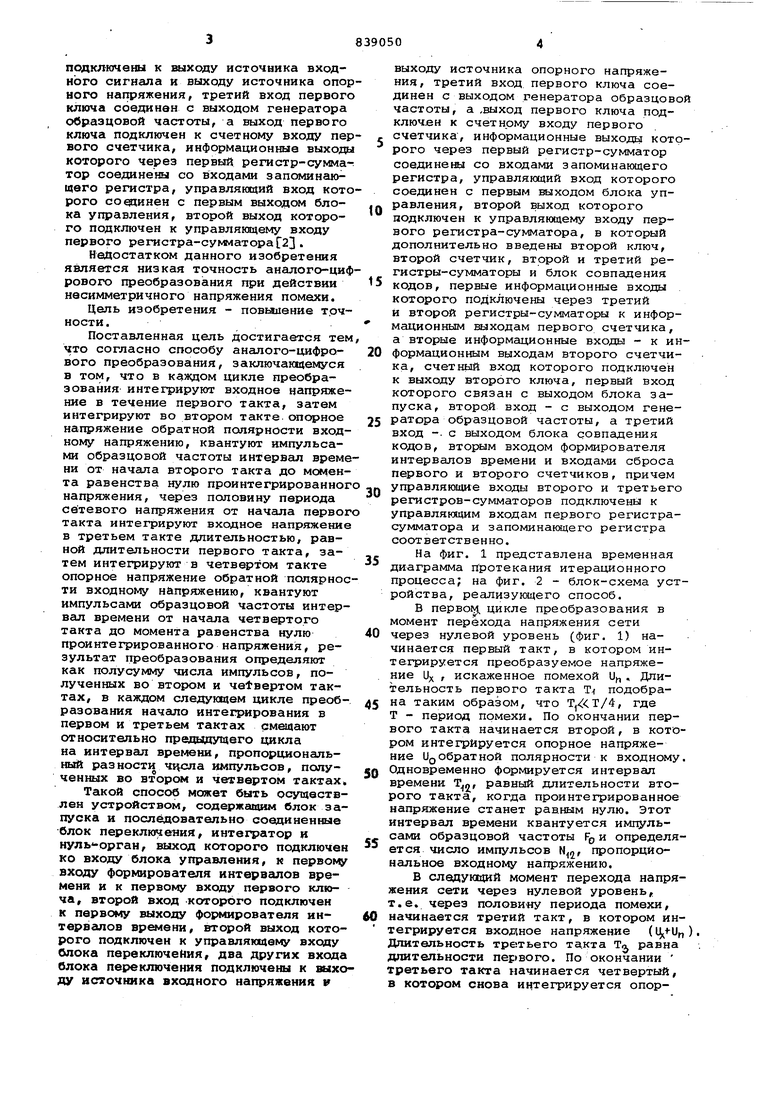

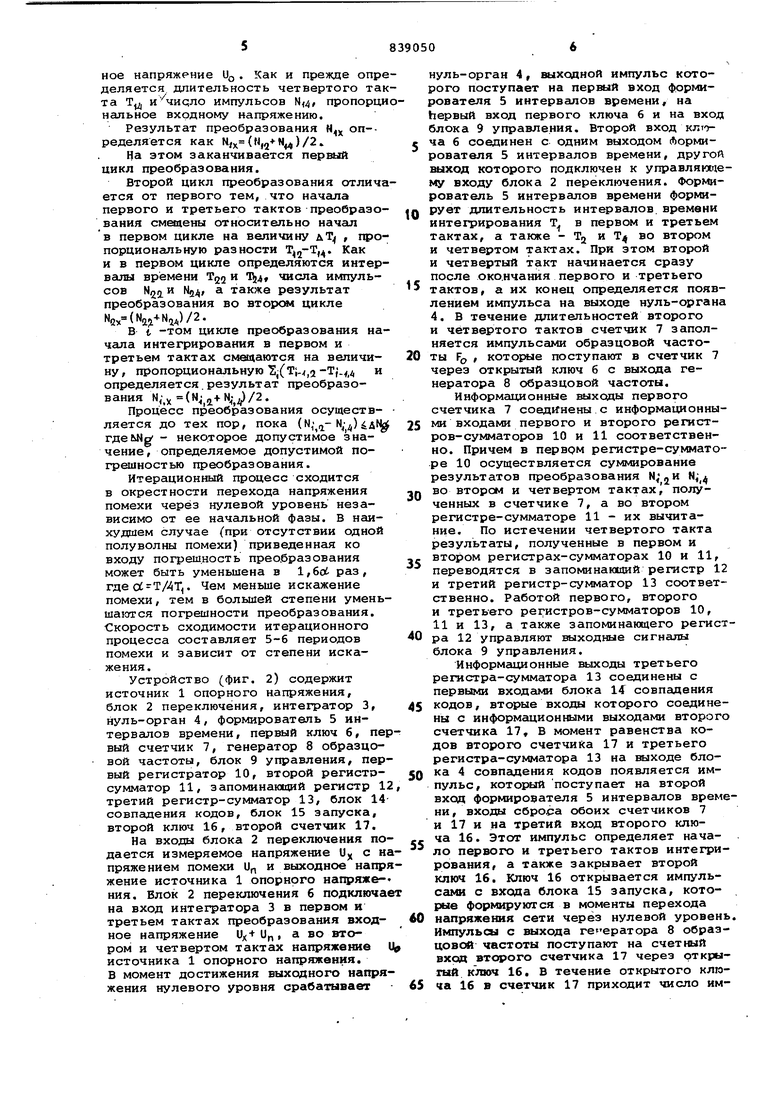

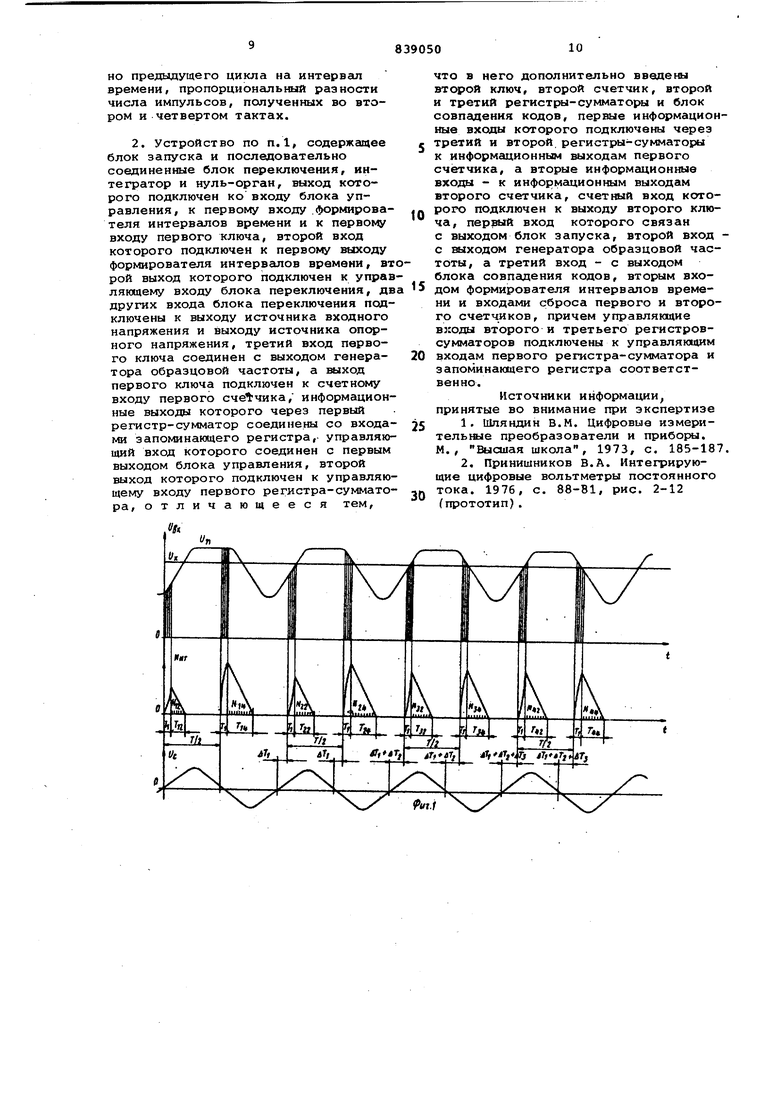

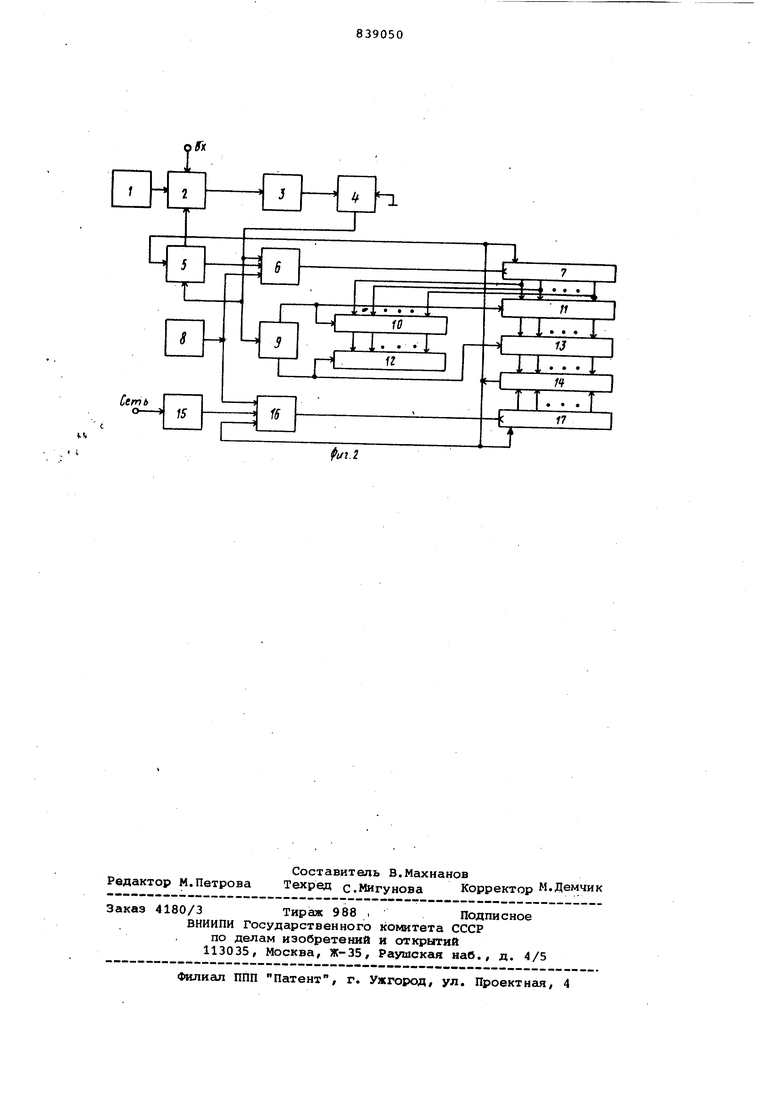

На фиг. 1 представлена временная диаграмма Протекания итерационного процесса; на фиг. 2 - блок-схема устройства, реализующего способ.

В nepBoiv| цикле преобразования в момент перехода напряжения сети через нулевой уровень (фиг. 1) начинается первый такт, в котором интегрируется преобразуемое напряжение и , искаженное помехой U, , Длительность первого такта Т подобрана таким образом, что Т,«Т/4, где Т - период помехи. По окончании первого такта начинается второй, в котором интегрируется опорное напряжение UQобратной полярности к входному Одновременно формируется интервал времени Т,п, равный длительности второго такта, когда проинтегрированное напряжение станет ранным нулю. Этот интервал времени квантуется импульсами образцовой частоты FQ и определяется число импульсов пропорциональное входному напряжению.

В следующий момент перехода напряжения сети через нулевой уровень, т.е. через полови«у периода помехи, начинается третий такт, в котором интегрируется входное напряжение ( Длительность третьего та.кта 1 равна длительности первого. По окончании третьего такта начинается четвертый, в котором снова интегрируется опорное напряжение UQ. Как и прежде опр деляется длительность четвертого та та Т и чицло импульсов пропорц нальное входному напряжению. Результат преобразования N оп-ределяется как NIX (,)/2 . На этом заканчивается первый цикл преобразования. Второй цикл преобразования отлич ется от первого тем, что начала первого и третьего тактов-преобразо вания смещены относительно начгш в первом цикле на величину лТ , порциональную разности . Как и в первом цикле определяются интер валы времени T2Q и числа импульсов Nijj, а также результат преобразования во втором цикле NQ, (Na.,)/2. В t -том цикле преобразования на чала интегрирования в первом и третьем тактах смацаются на величину, пропорциональную ,(Т;-ч,2-Т;.,/, и определяется.результат преобразования ( N /2. Процесс преобразования осуществляется до тех пор, пока () Д - некоторое допустимое значение , определяемое допустимой погрешностью преобразования. Итерационный процесс сходится в окрестности перехода напряжения помехи через нулевой уровень независимо от ее начальной фазы. В наихудшем случае (при отсутствии одной полуволны помехи) приведенная ко входу погрешность преобразования может быть уменьшена в l,6ot раз, гдео -Т/4Т|. Чем меньше искажение помехи, тем в большей степени умень шаются погрешности преобразования. Скорость сходимости итерационного процесса составляет 5-6 периодов помехи и зависит от степени искажения. Устройство (фиг. 2) содержит источник 1 опорного напряжения, блок 2 переключения, интегратор 3, нуль-орган 4/ формирователь 5 интервалов времени, первый ключ 6, пе вый счетчик 7, генератор 8 образцовой частоты, блок 9 управления, пер вый регистратор 10, второй регистрсумматор 11, запоминающий регистр 1 третий регистр-сумматор 13, блок 14 совпадения кодов, блок 15 запуска, второй ключ 16, второй счетчик 17. На входы блока 2 переключения по дается измеряемое напряжение Ujj с н пряжением помехи Ufl и выходное напр жение источника 1 опорного напряжения. Блок 2 переключения б подключа на вход интегратора 3 в первом и третьем тактах преобразования входное напряжение Ux U,, а во втором и четвертом тактах напряжение источника 1 опорного напряжения. В момент достижения выходного напря жения нулевого уровня срабатывает нуль-орган 4, ш ходной импульс которого поступает на первый вход формирователя 5 интервалов времени, на Первый вход первого ключа 6 и на вход блока 9 управления. Второй вход ключа 6 соединен с одним выходом Лормирователя 5 интервалов времени, другой выход которого подключен к управляющему входу блока 2 переключения. Формирователь 5 интервалов времени формирует длительность интервалов времени интегрирования Т. в первом и третьем тактах, а также - Т и Т во втором и четвертом тактах. При зтом второй и четвертый такт начинается сразу после око.нчания первого и третьего тактов, а их конец определяется появлением импульса на выходе нуль-органа 4. В течение длительностей второго и четвертого тактов счетчик 7 заполняется импульсами образцовой частоты FO , которые поступают в счетчик 7 через открытый ключ б с выхода генератора 8 образцовой частоты. Информгошонные выходы первого счетчика 7 соединены с информационными входами первого и второго регистров-сумматоров 10 и 11 соответственно. Причем в первом регистре-сумматоре 10 осуществляется суммирование результатов преобразования N, во втором и четвертом тактах| полученных в счетчике 7, а во втором регистре-сумматоре 11 - их вычитаHHie. По истечении четвертого такта результаты, полученные в первом и втором регистрах-сумматорах 10 и 11, переводятся в запоминающий регистр 12 и третий регистр-сумматор 13 соответственно. Работой первого, второго и третьего регистров-сумматоров 10, 11 и 13, а также запоминающего регистра 12 управляют выходные сигналы блока 9 управления. Информационные выходы третьего регистра-сумматора 13 соединены с первыми входами блока 14Г совпадения кодов, вторые входы которого соединены с информационными выходами второго счетчика 17, В момент равенства кодов второго счетчика 17 и третьего регистра-сумматора 13 на выходе блока 4 совпадения кодов появляется импульс, который поступает на второй вход формирователя 5 интервалов времени, входы сброса обоих счетчиков 7 и 17 и на третий вход второго ключа 16. Этот импульс определяет начало первого и третьего тактов интегрирования, а также закрывает второй ключ 16. Ключ 16 открывается импульсами с входа блока 15 запуска, которые формирунтгся в моменты перехода напряжения сети через нулевой уровень. Импульсы с выхода генератора 8 образjuoBOSt частоты поступают на счетный вход второго счетчика 17 через открытый ключ 16, В течение открытого ключа 16 в счетчик 17 приходит число импульсов, пропорциональное коду трет его регистра-сумматора 13, в которо гшгебраически суммируются разности преобразований второго и четвертого тактов. Время интегрирования в первом и третьем тактах подобрано из расчета, что Т т/4, где Т - период напряжения помехи. Устройство работает следующим образом. При включении устройства в обоих счетчиках 7 и 17 .и регистрах 10-13 устанавливаются нулевые состояния. В момент перехода сетевого напря жения через нулевой уровень включае ся запуск 15 и своим выходным импульсом открывает второй ключ 16, в результате чего импульсы с выхода генератора 8 образцовой частоты начинают поступать на счетный вход счетчика 17. При достижении состояния счетчика 17 равного состоянию регистра 13, срабатывает блок 14 со падения кодов, который своим выходным импульсом закрывает второй ключ 16, сбрасывает в нуль оба счетчика 7 и 17 и включает формирователь 5 и тервалов времени. Последний на время длительности первого такта через переключатель 2 подключает на вход интегратора 3 входное напряжение и,, и . По окончании первого такта формирователь 5 интервалов времени формирует следующий импульс, в результате чего на вход интегратора 3 через переключатель 2 подключается источник 1 опорного напряжения, напряжение которого имеет обратную к выходному напряжению полярность. Одновременно этот импульс открывает первый ключ 6, через который счетные импульсы с выхода генератора 8 образцовой частоты начинают поступать на вход первого счетчика 7. При достижении на вьЛходе интегра тора 3 нулевого уровня срабатывает нуль-орган 4, выходной импульс которого отключает формирователь 5, интервалов времени, закрывает ключ и включает блок 9 управления.На первом выходе бэтока 9 управления по ляется импульс, который осуществляе перезапись состояния N, счетчика 7 в регистры 10 и 11. Б следукмий момент перехода напряжения сети через нулевой уровень снова включается блок 15 запуска и устройство работает также как и в первых двух тактах за исключением того, что в счетчике 7 фиксируется состояние, так как интегрирование в третьем такте осуществляется через половину периода помехи, т.е. ПРИ ДРУГОЙ ее полуволне. Кроме того, по сигналу с nepBdro выхода блока 9 управления в регистре 10 фиксируется число -()/2,a з регистр 11 - д М - N(2- N,/,, после этого по сигналу со второго выхода блока 9 управления числа переводятся в регистры 12 и 13 соответственно, а регистры 10 и 11 обнуляются. На этом заканчивается первый цикл работы устройства. Во втором цикле устройство работает как и в первом, с тем отличием, что начало интегрирования в первом и третьем тактах смещается на величину Д Т , пропорциональную числу д N , записанному в регистре 13. По окончании второго цикла в регистре 12 записывается число NQX (N,j,-- N2)72, а в регистре 13 число Л N г д N, f U N5 , где & Nj г N25 - Nj, и ЗА результаты преобразования во втором и четвертом тактах второго цикла преобразования. В -« -том цикле преобразования смещение начала интегрирования в первом и третьем тактах относительно первого цикла определяется величиной, пропорциональной 2 . Результат преобразования определяется как N.,,4N;,.,)/2. В результате такого итерационного процесса моменты начала интегрирования в первом и третьем тактах автоматически выбираются такими, что интегрирование входного сигнала осуществляется в окрестности перехода помехи через нулевой уровень независимо от начальной фазы помехи. Формула изобретения 1. Способ аналого-цифрового преобразования, заключающийся в том, что в каждом цикле преобразования интегрируют входное напряжение, в течение первого такта, затем интегрируют во втором такте опорное напряжение обратной полярности входному напряжению, квантуют импульсами образцовой частоты интервал времени от начала второго такта до момента равенства нулю проинтегрированного напряжения, через половину периода сетевого напряжения от начала первого такта интегрируют входное напряжение в третьем такте длительностью, равной длительности первого такта, затем интегрируют в четвертом такте опорное нагфяжение обратной полярности входному напряжению, квантуют импульсами образцовой частоты интервал, времени от начала четвертого такта до момента равенства нулю проинтегрированного напряжения, результат преобразования определяют как полусумму числа импульсов, полученных во втором и четвертом тактах, отличающийся тем, что, с целью повышения точности, в каждом следующем преобразовании начало интегрирования в первом и третьем тактах смещают относительно предыдущего цикла на интервал времени, пропорциональный разности числа импульсов, полученных во втором и четвертом тактах.

2. Устройство по П.1, содержащее блок запуска и последовательно соединенные блок переключения, интегратор и нуль-оргаи, выход которого подключен ко входу блока управления, к первому входу.формирователя интервалов времени и к первому входу первого ключа, второй вход которого подключен к первому выходу формирователя интервалов времени, втрой выход которого подключен к управляющему входу блока переключения, дв других входа блока переключения подключены к выходу источника входного напряжения и выходу источника опорного напряжения, третий вход первого ключа соединен с выходом генератора образцовой частоты, а выход первого ключа подключен к счетному входу первого , информационные выходы которого через первый регистр-сумматор соединены со входами запоминающего регистра, управляющий вход которого соединен с первым выходом блока управления, второй выход которого подключен к управляющему входу первого регистра-сумматора, отличающееся тем.

что в него дополнительно введены втсчрой ключ, второй счетчик, второй и третий регистры-сумматоры и блок совпадения кодов, первые информационные входы которого подключены через третий и второй, регистры-сумматоры к информационным выходам первого счётчика, а вторые информационные входы - к информационным выходам второго счетчика, счетный вход которого подключен к выходу второго ключа, первый вход которого связан с выходом блок запуска, второй вход с выходом генератора образцовой частоты, а третий вход - с выходом блока совпадения кодов, вторым входом формирователя интервалов времени и входами сброса первого и второго счетчиков, причем управляющие входы второго и третьего регистровсумматоров подключены к управляющим входам первого регистра-сумматора и

0 запоминающего регистра соответственно.

Источники информации, принятые во внимание при экспертизе

1,Шляндин В.М. Цифровые измери5телыале преобразователи и приборы.

М., Высшая школа, 1973, с. 185-187.

2.Принишников В.А. Интегрирующие цифровые вольтметры постоянного тока. 1976, с. 88-81, рис. 2-12

0 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующий аналого-цифровой преобразователь | 1987 |

|

SU1495996A2 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Преобразователь величины мощности и действующего значения напряжения в цифровой код | 1986 |

|

SU1404952A1 |

| СПОСОБ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2354955C1 |

| Устройство для измерения температуры | 1987 |

|

SU1490504A1 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИЗНОСА РЕЖУЩЕГО ИНСТРУМЕНТА | 2004 |

|

RU2263300C1 |

иг.2

« i

Авторы

Даты

1981-06-15—Публикация

1979-09-17—Подача