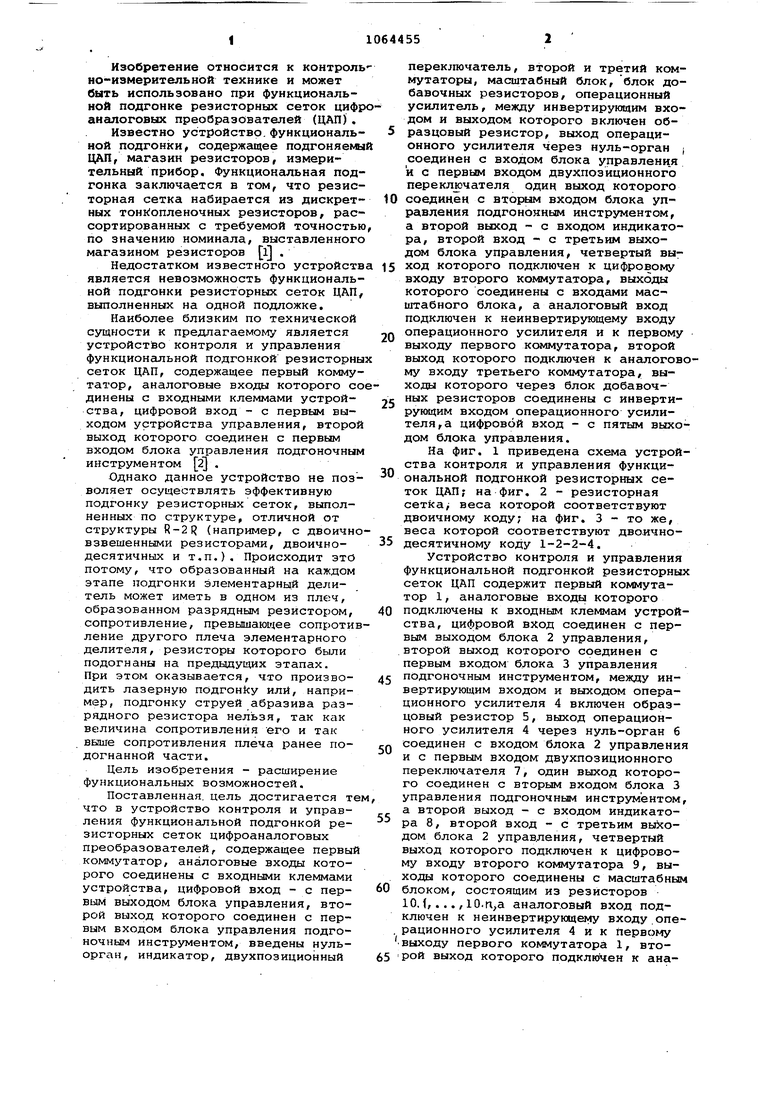

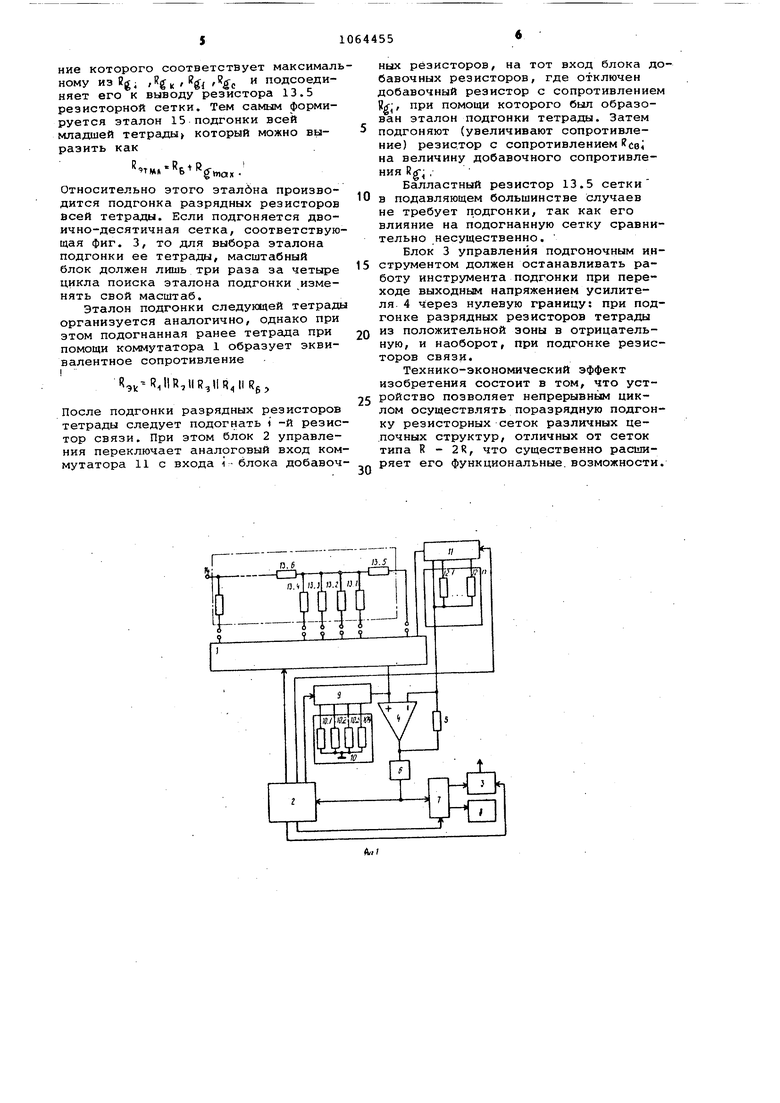

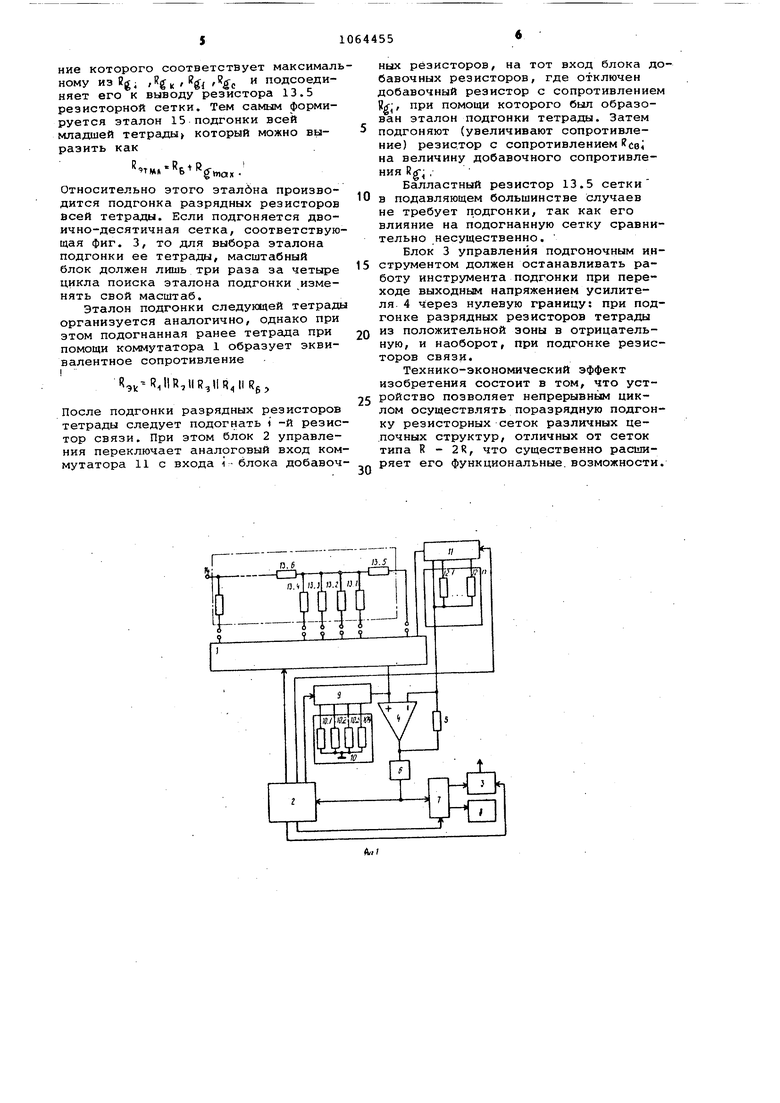

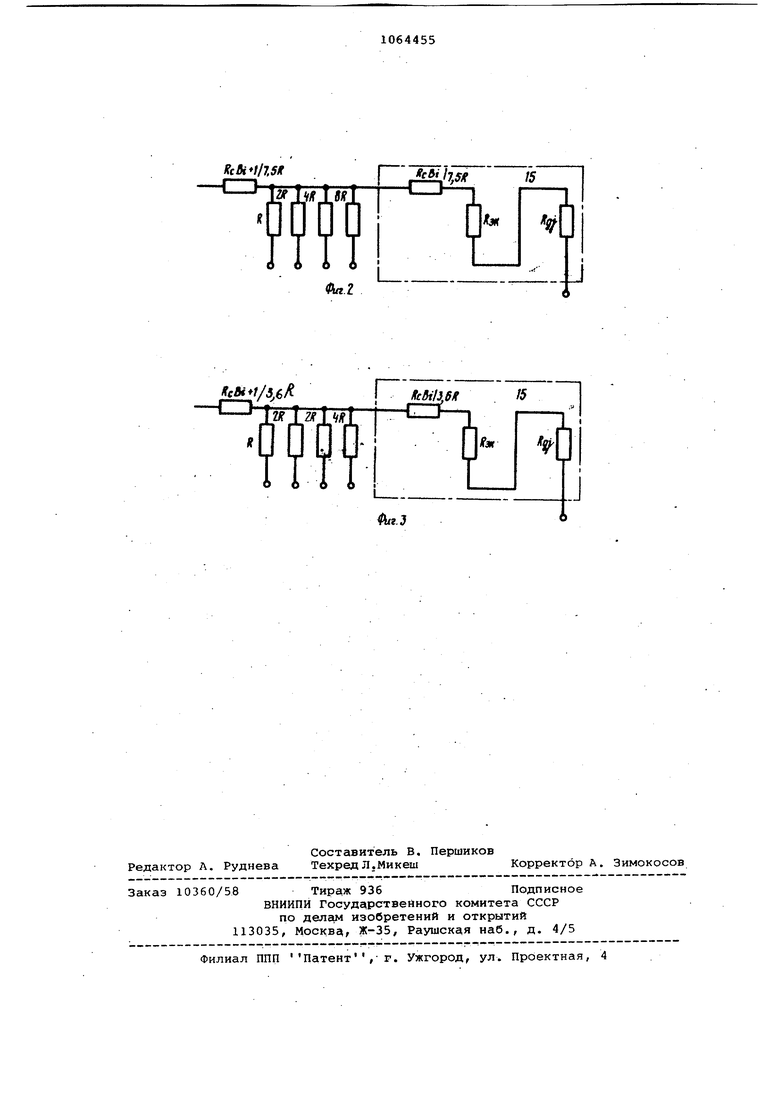

Изобретение относится к контроль но-измерительнбй технике и может быть использовано при функциональной подгонке резисторньах сеток цифр аналоговых преобразователей (ЦАП), Известно устройство, функциональной подгонки, содержащее подгоняемы ЦЛП, магазин резисторов, измерительный прибор. Функциональная подгонка заключается в том, что резисторная сетка набирается из дискретных тонкопленочных резисторов, рассортированных с требуемой точностью по значению номинала, выставленного магазином резисторов l . Недостатком известного устройств является невозможность функциональной подгонки резисторных сеток ЦАП выполненньпс на одной подложке. Наиболее близким по технической сущности к предлагаемому является устройство контроля и управления функциональной подгонкой резисторны сеток ЦАП, содержащее первый коммутатор, аналоговые входы которого со динены с входными клеммами устройства, цифровой вход - с первым выходом устройства управления, второй выход которого соединен с первым входом блока управления подгоночным инструментом 2J . Однако данное устройство не поз воляет осуществлять эффективную подгонку резисторных сеток, выполненных по структуре, отличной от структуры R-2( (например, с двоично взвешенными резисторами, двоичнодесятичньох и т.п.). Происходит это потому, что образованный на каждом этапе подгонки элементарный делитель может иметь в одном из плеч, образованном разрядным резистором, сопротивление, превышающее сопротив ление другого плеча элементарного делителя, резисторы которого были подогнаны на предыдущих этапах. При этом оказывается, что производить лазерную пoдгoнky или, например, подгонку струей абразива разрядного резистора нельзя, так как величина сопротивления его и так выше сопротивления плеча ранее подогнанной части. Цель изобретения - расширение функциональных возможностей. Поставленная, цель достигается те что в устройство контроля и управления функциональной подгонкой резисторных сеток цифроаналоговых преобразователей, содержащее первый коммутатор, аналоговые входы которого соединены с входными клеммами устройства, цифровой вход - с первым выходом блока управления, второй выход которого соединен с первым входом блока управления подгоночным инструментом, введены нульорган, индикатор, двухпозиционный ,переключатель, второй и третий коммутаторы, масштабный блок, блок добавочных резисторов, операционный усилитель, между инвертирующим входом и выходом которого включен образцовый резистор, выход операционного усилителя через нуль-орган j соединен с входом блока управления и с первым входом двухпозиционного переключателя один выход которого соединен с вторым входом блока управления подгононным инструментом, а второй выход - с входом индикатора, второй вход - с третьим выходом блока управления, четвертый выход которого подключен к цифровому входу второго коммутатора, выходы которого соединены с входами масштабного блока, а аналоговый вход подключен к неинвертирующему входу операционного усилителя и к первому выходу первого коммутатора, второй выход которого подключен к аналоговому входу третьего коммутатора, выходы которого через блок добавочных резисторов соединены с инвертирующим входом операционного усилителя, а цифровой вход - с пятым выходом блока управления. На фиг. 1 приведена схема устройства контроля и управления функциональной подгонкой резисторных сеток ЦАП; на фиг. 2 - резисторная сетка веса которой соответствуют двоичному коду; на фИг. 3 - то же, веса которой соответствуют двоичнодесятичному коду 1-2-2-4. Устройство контроля и управления функциональной подгонкой резисторных сеток ЦАП содержит первый кокмутатор 1, аналоговые входы которого подключены к входным клеммам устройства, цифровой вход соединен с первым выходом блока 2 управления, второй выход которого соединен с первым входом блока 3 управления подгоночным инструментом, между инвертирующим входом и выходом операционного усилителя 4 включен образцовый резистор 5, выход операционного усилителя 4 через нуль-орган б соединен с входом блока 2 управления и с первым входом двухпозиционного переключателя 7, один выход которого соединен с вторым входом блока 3 управления подгоночным инструментом, а второй выход - с входом индикатора 8, второй вход - с третьим вы ходом блока 2 управ.ления, четвертый выход которого подключен к цифровому входу второго коммутатора 9, выходы которого соединены с масштабным блоком, состоящим из резисторов 10. (,..., 10.п,а аналоговый вход подключен к неинвертирующему входу операционного усилителя 4 и к Первому выходу первого коммутатора 1, второй выход которого подключен к аналог-овому входу третьего коммутатора 11, выходы которого через блок добавочных резисторов 12,1-12 п (Кб,л соединены с инвертирующим входом операционного усилителя 4, а цифровой вход - с пятым выходом блока управления. На фиг. 1 также показаны подгоняемая резистбрная сетка ,с резисторами 13.1-13.6 и клемма 14 для подключения источника эталонного напряжения. На фиг. 2 представлен сформированный эталон 15 подгонки тетрады резисторной сетки двоичной, структуры, ограниченной резисторами связи сопротивлениями свол На фиг. 3 представлен сформированный эталон 15 подгонки тетрады резисторной сетки двоично-десятичной структуры, ограниченной резисторами связи с сопротивлениями Rf-a; о . cen-i Для осуществления работы устройс ва необходимо подключить выходы ра рядных резисторов подстраиваемой резисторной сетки к соответствующим входным клеммам устройства, а на клемму 14 подать эталонное напря жение. Пусть сопротивление резисторов связи подгоняемой резисторной сетки равно 7,5 R , что соответствует двоичному ЦАП с сеткой, представ ленной на фиг. 2 (при сопротивлении резисторов связи 3,6R - двоично-де сятичному ЦАП на фиг, 3). Устройство работает следующим об разом. Подбирают эталон подгонки младшей разрядной секции. При этом блок 2 управления через коммутатор 1 под ключает младший разряд - резистор 13.1 с сопротивлением R сетки к не инвертирующему входу усилителя 4, балластный резистор 13.5 с сопротивлением Rg одновременно подключается к аналоговому входу коммутатора 11, а неинвертирующий вход усилител 4 через коммутатор 9 - к одному из входов масштабного блока, например резистору 10.1, сопротивление которого рав,но R Для подгонки резисторных сеток структур, изображенных на фиг. 2 и фиг. 3, номингшы резисторов масштабного блока достаточно выбрать: резистор 10,, 10.2 10.3 , 10.4 |-. После.этого .блок 2 управления подключает поочередно аналоговый вход коммутатора 11 к его выходам, которые в свою очередь соединены с входами блока добавочных резисторов 12.1-12. с сопротив лением Rg % Rtf, причем номиналы резисторов бло ;ка добавочных резисторов увеличиваются с определенной гргщацией. Когда сработает нуль-орган 6, то ег сигнал, поступая на блок 2 управления, становится запрещакяцим для сигналов управления коммутатором 11 ; в3 блоке 2 управления фиксируется номер такта, на котором произошел останов. Этот номер определяет номинал добавочного резистора блока добавочных резисторов. Одновременно сигнал с нуль-органа 6 через двухпозиционный переключатель 7 поступает на индикатор 8, который фиксирует конец ; одного цикла поиска эталона 15 под-/ Г2Нки.. . Йайденный таким образом эталон 15 подгонки младшего разряда будет удовлетворять условию i.nRb+Rgi R r где сопротивление RI резистора 13,1 должно &ыть подогнйно по весу до со-, противления 8 R. Второй цикл поиска эталона подгонки младшей тетрады начинается с подключения блоком 2 управления следующего разряда (резистора 13,2 с сопротивлением R сетки 13) к неинвертирующему входу усилителя 4, переключения коммутатором 9 неинвертируницего входа усилителя 4 на резис- . тор 102- 2 масштабного блока, в соответствии со следующим весом сетки (фиг. 2) резистор с сопротивлением Rg остается подключенным к входу коммутатора 11. . Затем блок 2 управления вновь поочередно подключает вход коммутатора 11 к блоку добавочных резисторов, начиная с резистора с сопротивлением Rg- , до тех пор пека не сработает нуль-орган 6 и не выдаст на блок 2 управления сигнал останова переключения коммутатора 11. При эгом в блоке 2 управления вновь фиксируется номер такта, на котором.произошел останов, т.е.-на котором выполнилось соотношение , 3tnM 6 R k2-R2, где сопротивление R резистора 13.2 должно ть подогнано по весу до сопротивления 4R. Следующие циклы поиска эталона младшей тетради производятся аналогично, до выполнения соотношений 3nn-7 6 R J4-R3, . 9ТП-з б с 8-К4. Сопротивления Rg ,Kg, , Kg ,Rg- блока добавочных резисторов определяются номером такта j , k ,f,с,на котором срабатывает нуль-орган 6. После этого блок 2 управления подключает один из резисторов блока добавочных резисторов, сопротивление которого соответствует максимал ному H3Bg. fRgK , ,R, и подсоединяет его к выводу резистора 13.5 резисторной сетки. Тем самым формируется эталон 15 подгонки всей младшей тетрады который можно выразить как ,,; относительно этого эталбна производится подгонка разрядных резисторов всей тетрады. Если подгоняется двоично-десятичная сетка, соответствую щая фиг. 3, то для выбора эталона подгонки ее тетрады, масштабный блок должен лишь три раза за четыре цикла поиска эталона подгонки изменять свой масштаб. Эталон подгонки следукадей тетрады организуется аналогично, однако при этом подогнанная ранее тетрада при помощи коммутатора 1 образует эквивалентное сопротивление эГ-ЛК.ЧКэ1«411 б После подгонки разрядных резисторов тетрады следует подогнать i -и резистор связи. При этом блок 2 управления переключает аналоговый вход коммутатора 11 с входа i блока добавочных резисторов, на тот вход блока добавочных резисторов, где отключен добавочный резистор с сопротивлением %( Р помощи которого был образован эталон подгонки тетрады. Затем подгоняют (увеличивают сопротивление) резистор с сопротивлением на величину добавочного сопротивления Rtf- , Балластный резистор 13.5 сетки в подавляющем большинстве случаев не требует подгонки, так как его влияние на подогнанную сетку сравнительно .несущественно. Блок 3 управления подгоночным инструментом должен останавливать работу инструмента подгонки при переходе выходным напряжением усилителя. 4 через нулевую границу: при подгонке разрядных резисторов тетрады из положительной зоны в отрицательную, и наоборот, при подгонке резисторов связи. Технико-экономический эффект изобретения состоит в том, что устройство позволяет непрерывным циклом осуществлять поразрядную подгонку резисторных сеток различных цепочных структур, отличных от сеток ипа к - 2R, что существенно расшияет его функциональные, возможности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ функциональной подгонки резисторных сеток цифроаналоговых преобразователей | 1981 |

|

SU993343A1 |

| Способ функциональной подгонки цифроаналоговых преобразователей | 1984 |

|

SU1339887A1 |

| СПОСОБ ИЗМЕРЕНИЯ И ПОДГОТОВКИ ВЕЛИЧИНЫ СОПРОТИВЛЕНИЯ РЕЗИСТОРОВ | 2003 |

|

RU2249222C1 |

| Компаратор сопротивлений | 1977 |

|

SU687396A1 |

| СПОСОБ ИЗМЕРЕНИЯ МАЛЫХ СОПРОТИВЛЕНИЙ, В ТОМ ЧИСЛЕ И СОПРОТИВЛЕНИЯ СТОК-ИСТОК ОТКРЫТОГО КАНАЛА ПОЛЕВОГО ТРАНЗИСТОРА | 2011 |

|

RU2451297C1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЙ И ПРИРАЩЕНИЯ СОПРОТИВЛЕНИЯ | 2003 |

|

RU2249223C1 |

| Преобразователь угла поворота вала в код | 1979 |

|

SU783818A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

| Преобразователь сопротивления в напряжение | 1988 |

|

SU1622837A1 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

УСТРОЙСТВО КОНТРОЛЯ И УПРАВЛЕНИЯ ФУНКЦИОНАЛЬНОЙ ПОДГОНКОЙ РЕЗИСТОРНЫХ СЕТОК ЦИФРОАНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ, содержащее первый коммутатор, аналоговые вхохцл которого соединены с входными клеммами устройства, цифровой вход - с первым выходом блока управления, второй выход которого соединен с первым входом блока управления подго- точным инструментом, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены нуль-орган, индикатор, двухпозиционный переключатель, второй и третий коммутаторы, масштабный блок, блок добавочных резисторов, операционный усилитель,между инвертирующим входом и выходом которого включен образцовый резистор, выход операционного усилителя через нуль-орган соединен с входом блока управления и с первым входом двухпозиционного переключателя, первый выход которого соединен с вторым входом блока управления подгоночным инструментом, а второй выход - г: входом индикатора, второй вход - с третьим выходом блока управления, четвертый выход которого подключен к цифровому входу второго коммута В тора, выходы которого соединены с (Л входами масштабного блока, а аналоговый вход подключен к неинвертирующему входу операционного усилителя и к первому выходу первого коммутатора, второй выход которого подключен к аналоговому входу третьего коммутатора, выходы которого через блок добавочных резисторов соединены с инвертирующим входом операционного усилителя, а цифровой вход - с пятым выходом блока управления. 05 4 4 СЛ СП

KcRi lllSK

Фиг г

.бЯ

,sx IS

CZD

п П

j I - ... .. ..ц|

йа.д

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Скрупски | |||

| Функциональная подгонка параметров компонентов в гибридных схемах | |||

| - Электроника, 1972, т | |||

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

Авторы

Даты

1983-12-30—Публикация

1982-07-14—Подача