Изобретение относится к вычислительной технике и может быть использовано для моделирования динамических систем.

Целью изобретения является повышение надежности системы.

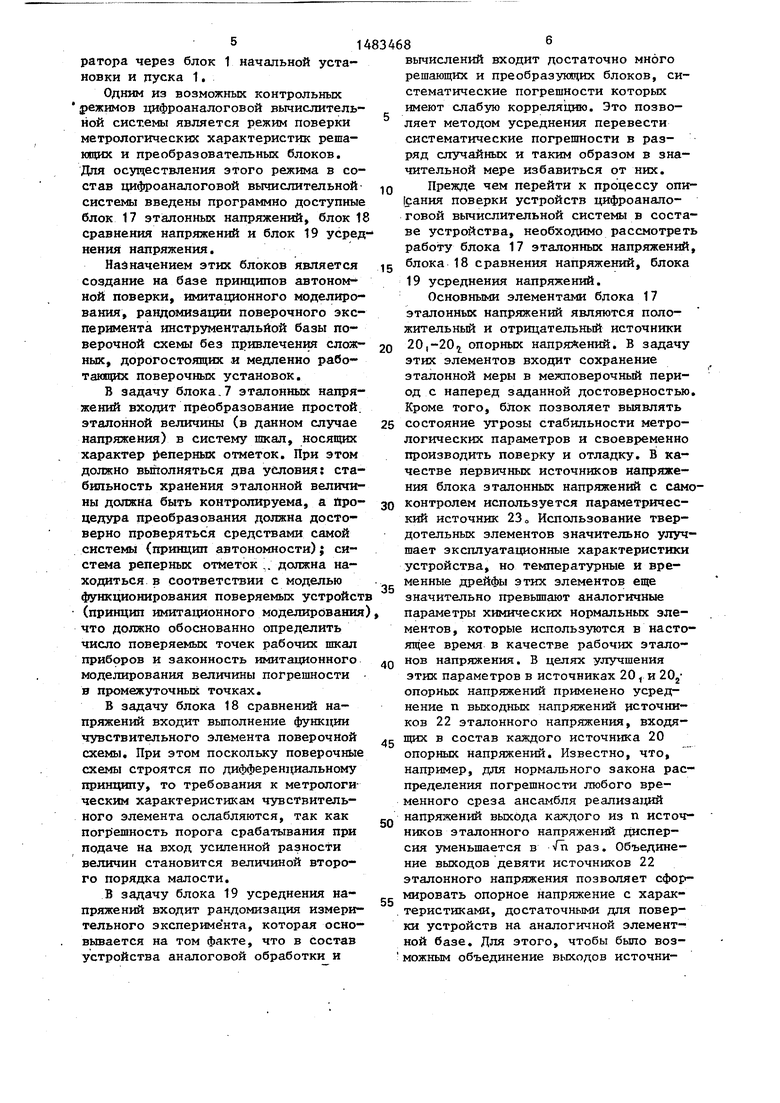

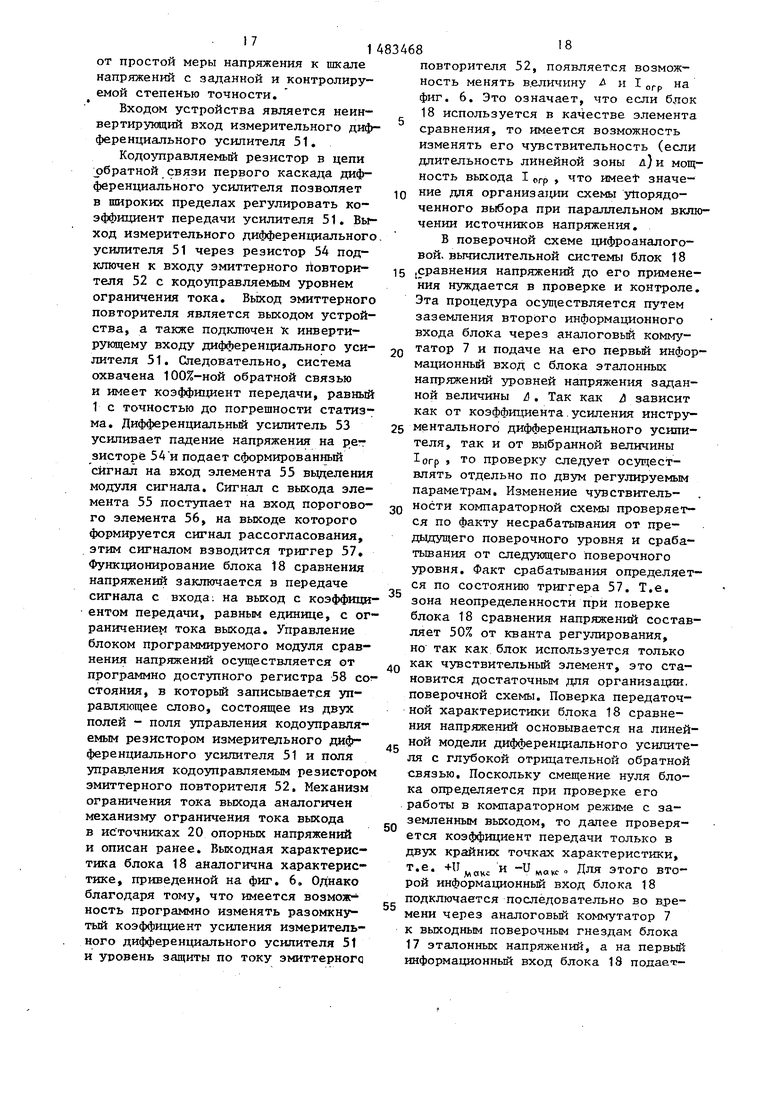

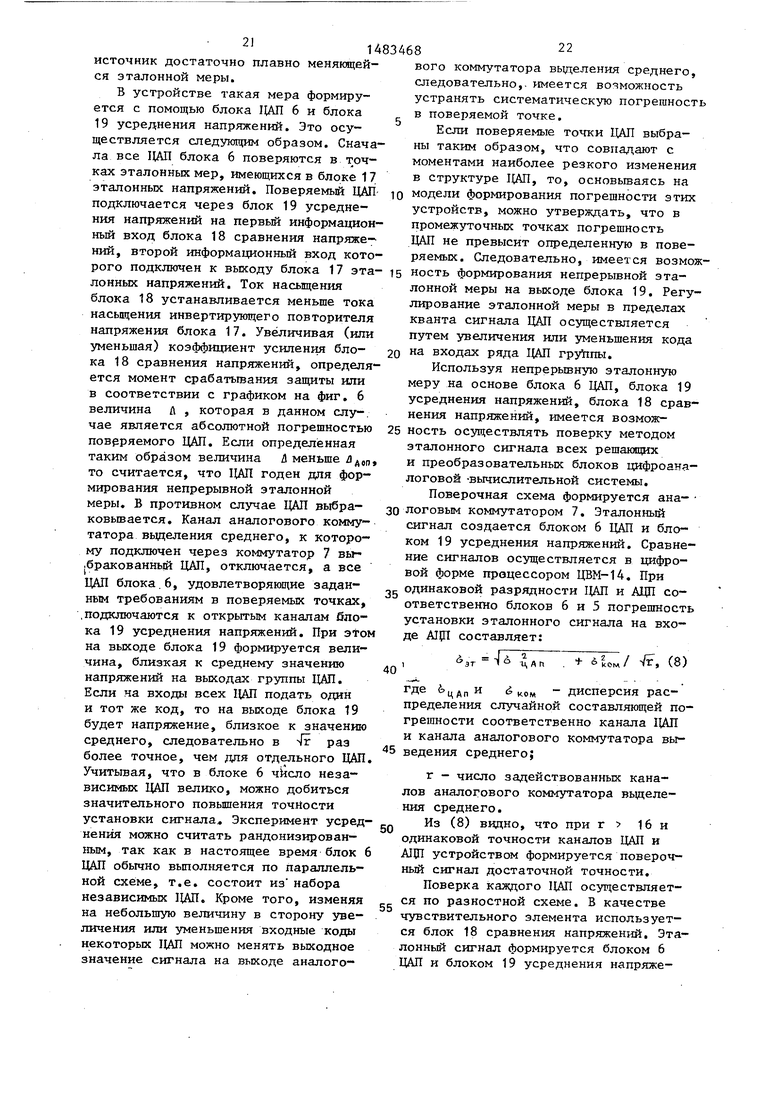

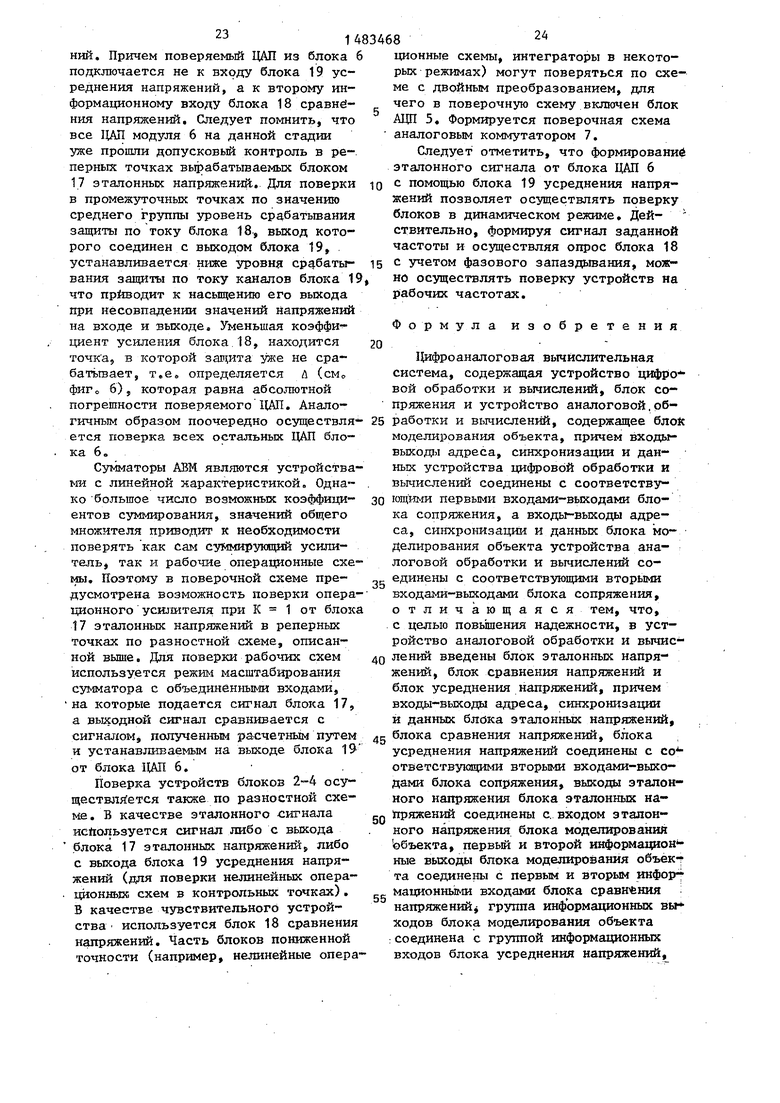

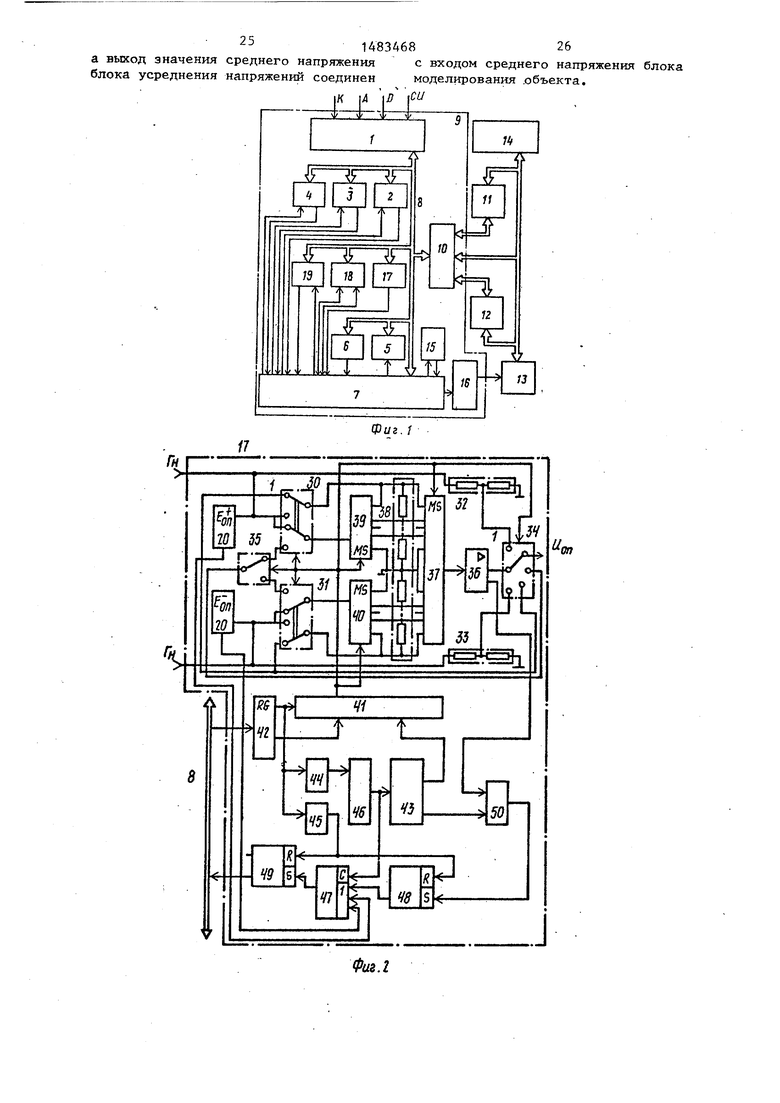

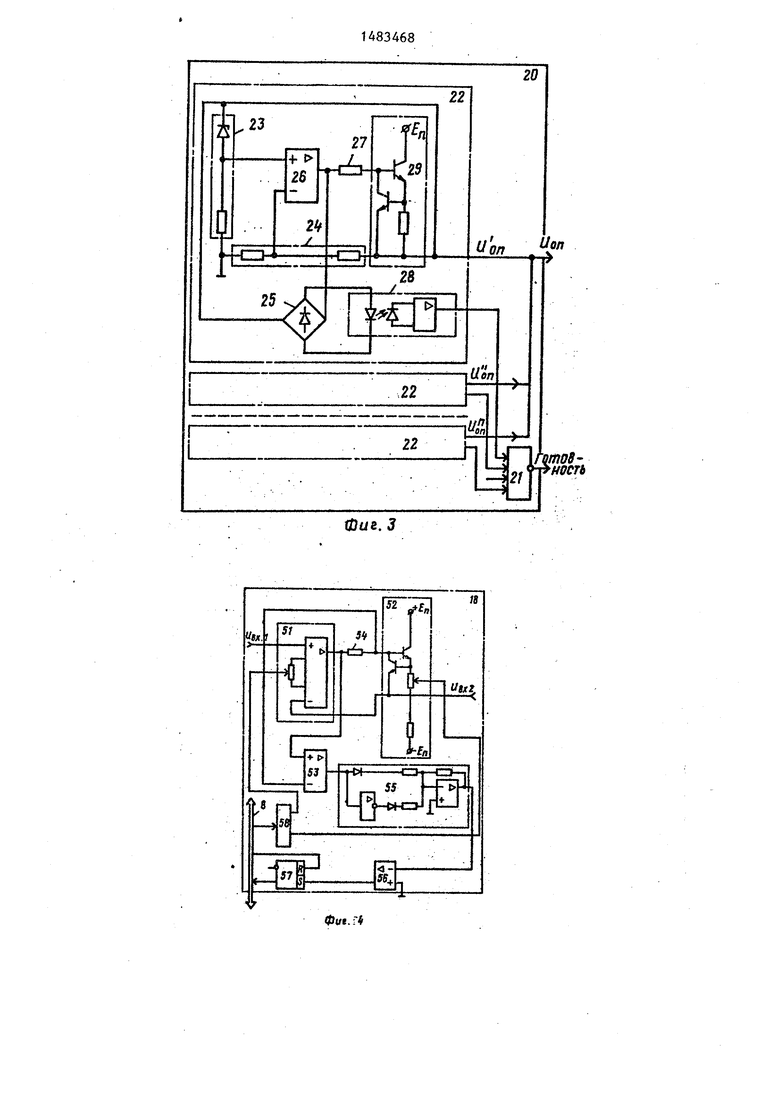

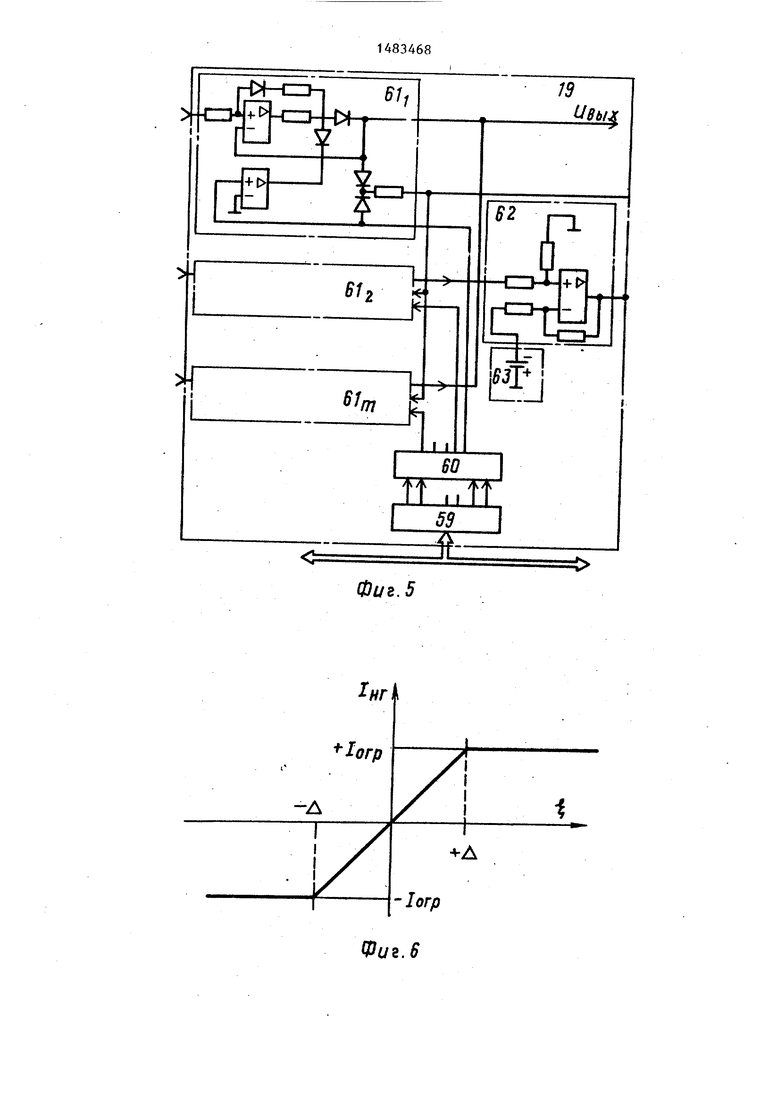

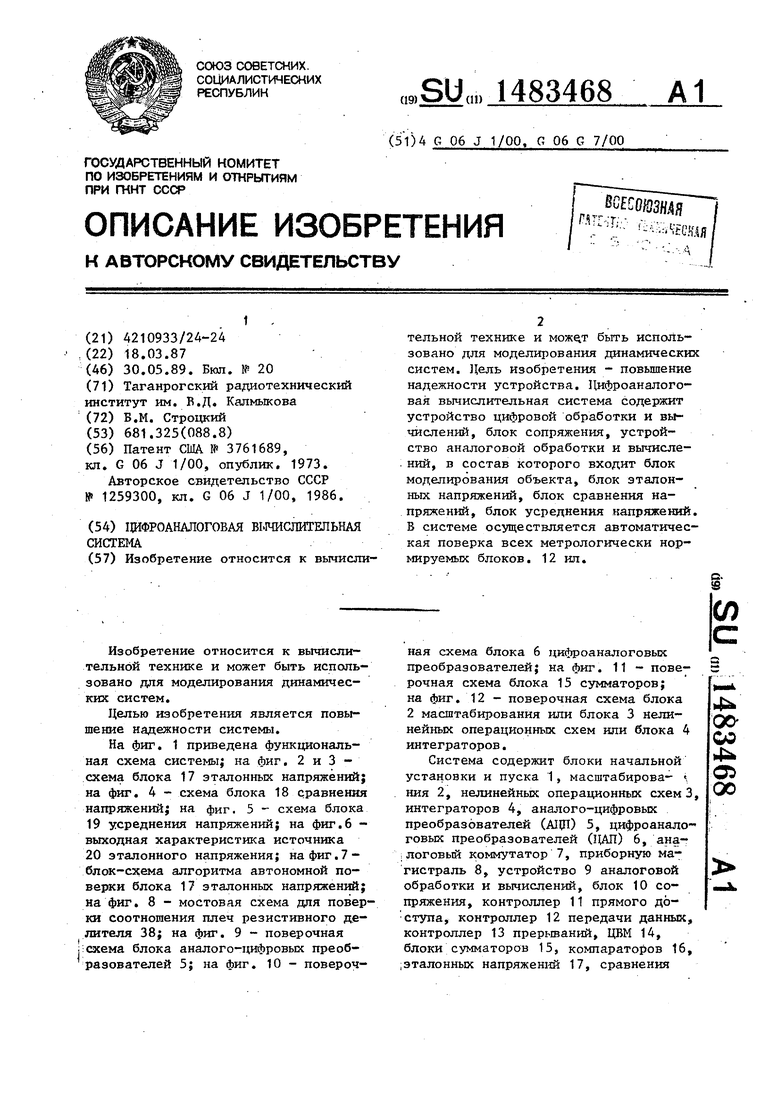

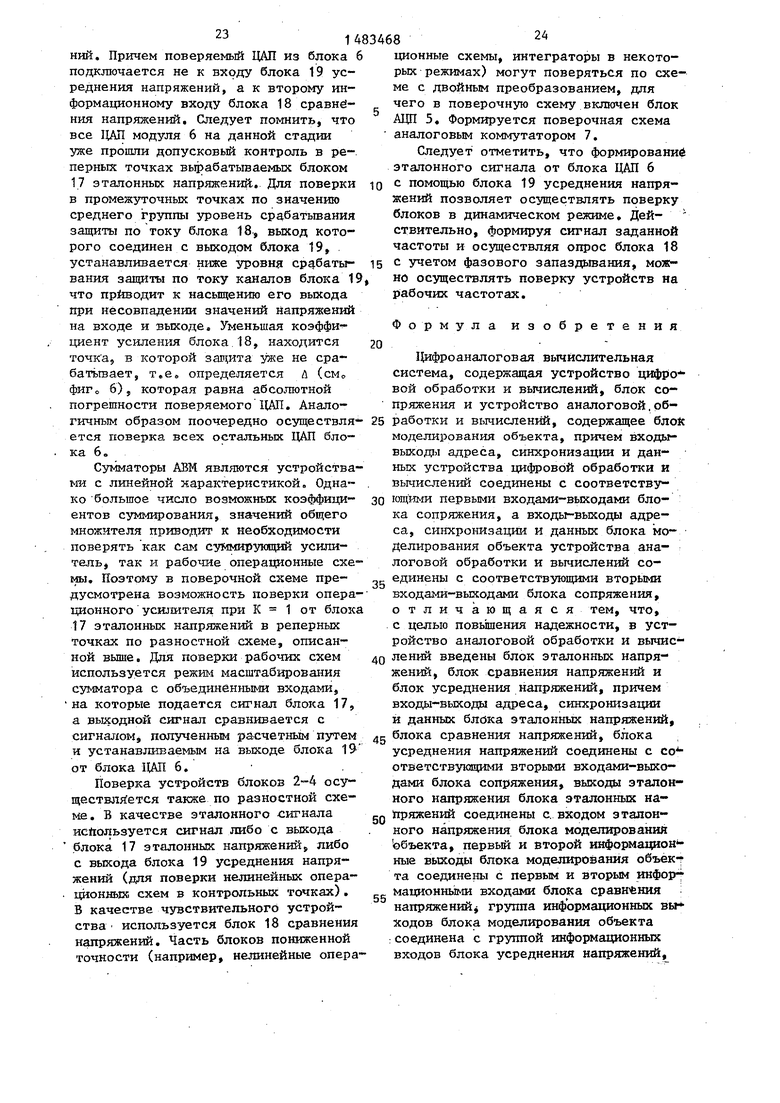

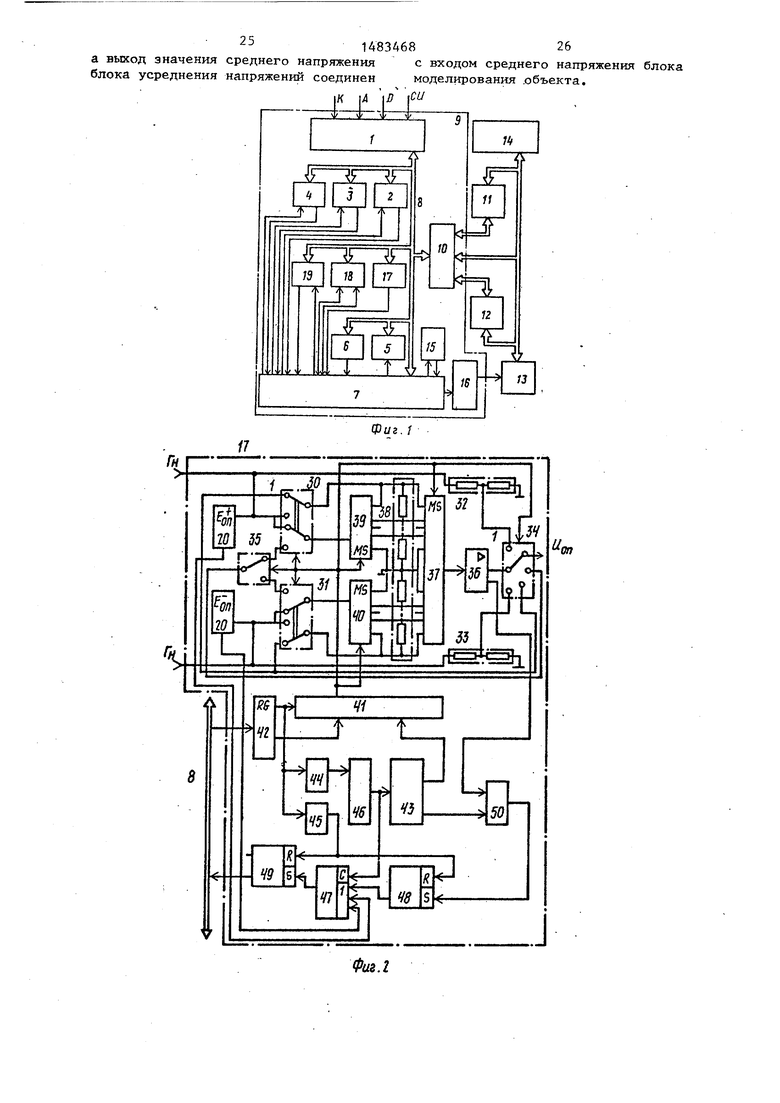

На фиг. 1 приведена функциональная схема системы; на фиг. 2 и 3 - схема блока 17 эталонных напряжений; на фиг. 4 - схема блока 18 сравнения напряжений; на фиг. 5 - схема блока

19усреднения напряжений; на фиг.6 - выходная характеристика источника

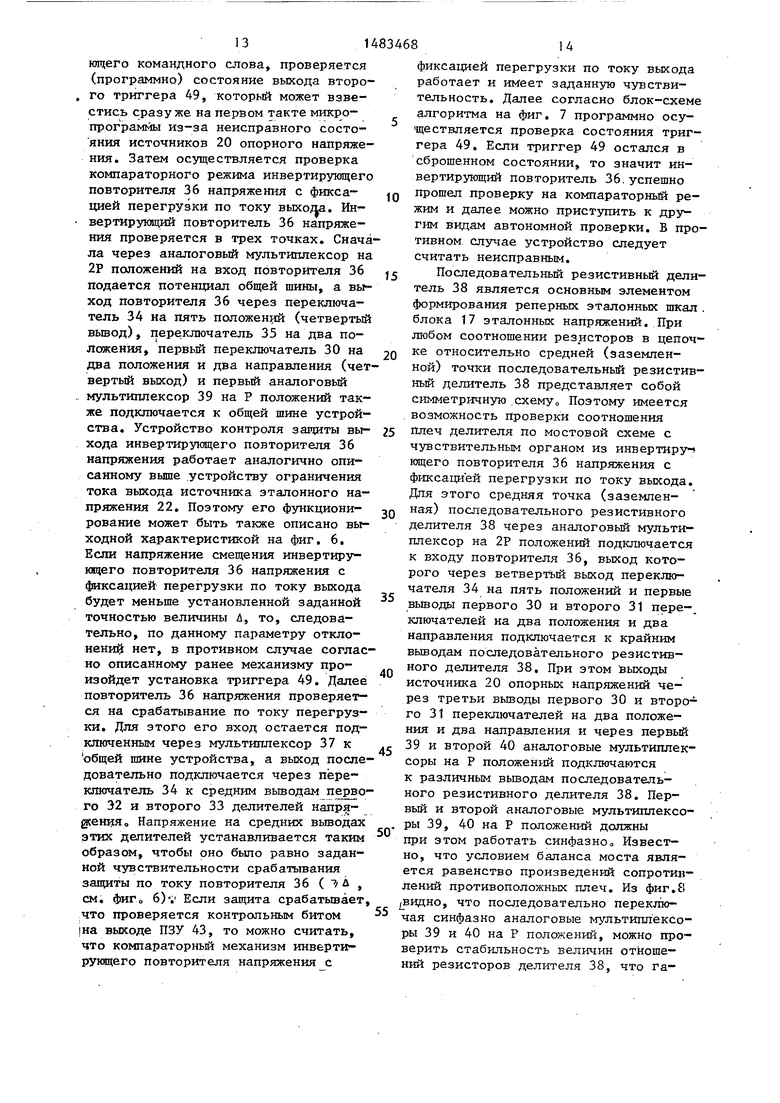

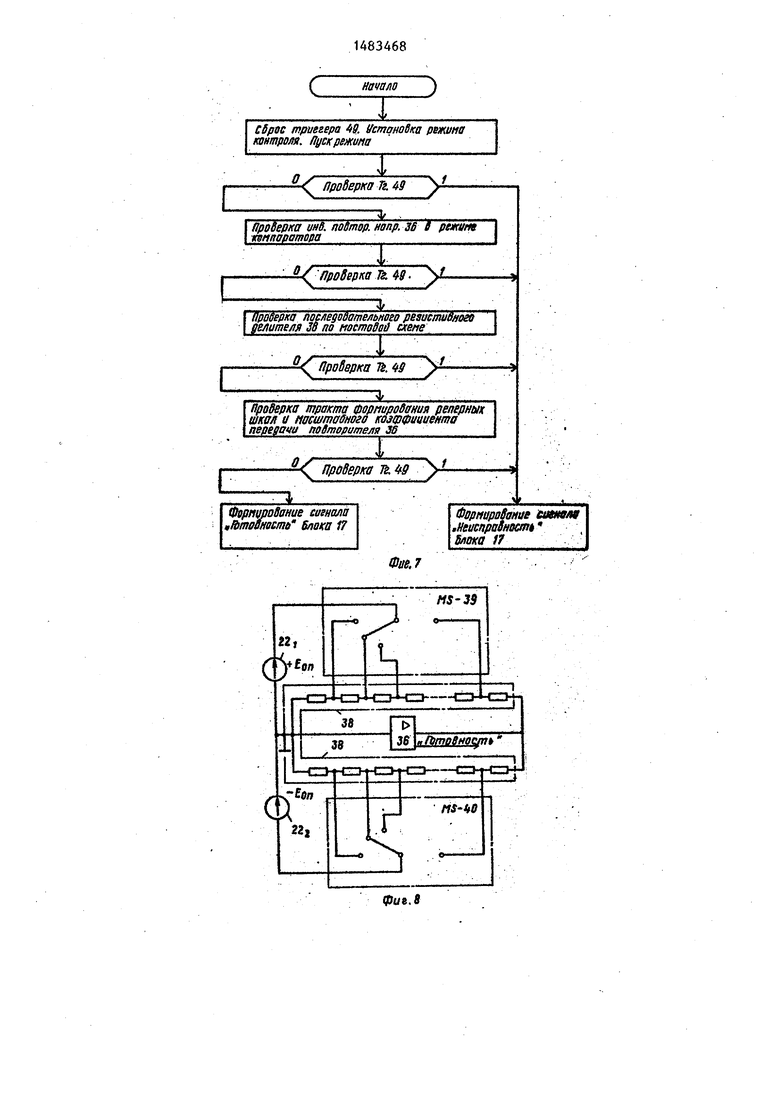

20эталонного напряжения; на фиг.7- блок-схема алгоритма автономной поверки блока 17 эталонных напряжений; на фиг. 8 - мостовая схема для поверки соотношения плеч резистивного делителя 38; на фиг. 9 - поверочная

схема блока аналого-цифровых преоб- разователей 5; на фиг. 10 - поверочная схема блока 6 цифроаналоговых преобразователей; на фиг. 11 - поверочная схема блока 15 сумматоров; на фиг. 12 - поверочная схема блока 2 масштабирования или блока 3 нелинейных операционных схем или блока 4 интеграторов.

Система содержит блоки начальной установки и пуска 1, масштабирова- « ния 2, нелинейных операционных схемЗ, интеграторов 4, аналого-цифровых преобразователей (А1Щ) 5, цифроаналоговых преобразователей (ЦАП) 6, аналоговый коммутатор 7, приборную магистраль 8, устройство 9 аналоговой обработки и вычислений, блок 10 сопряжения, контроллер 11 прямого доступа, контроллер 12 передачи данных, контроллер 13 прерываний, ЦВМ 14, блоки сумматоров 15, компараторов 16, ,эталонных напряжений 17, сравнения

Я

ооОЗ4 О 00

напряжений 18, усреднения Напряжений 19, причем блоки 1-8, 15,16 объединены понятием блок моделирования объекта и вместе с блоками 17-19 составляют устройство 9 аналоговой обработки и вычислений, а блоки 11-14 объедине- ны понятием устройство цифровой обработки и вычислений.

Блок 17 эталонных напряжений содержит положительный и отрицательный источники 20 опорных напряжений, содержащие n-входовой элемент ИЛИ-НЕ 21 и п источников 22 эталонного напряжения, содержащих параметрический источник 23 напряжения, резистивный делитель 24 связи, мостовой вьшгоями тель 25, дифференциальный усилитель 26, ограничивающий резистор 27, поро15 ми, так и группами цепей. Состояние аналогового коммутатора 7 определяется содержанием его программно доступных регистров. Ввод начальных условий, а также пуск решения и вывод

происходит через блоки аналого-цифровых 5 и цифроаналоговых 6 преобразователей. Кроме того, блоки маоштаговый элемент 28 и эмиттерный повто-2Q данных из решающих блоков устройства

ритель 29, первый 30 и второй 31 аналоговой обработки и вычислений реключатели на два положения и два направления, первый 32 и второй 33 делители напряжения, переключатель 34

на пять положений, переключатель 3525 бирования 2, нелинейных операционных на два положения, инвертирующий по-схем 3 и интеграторов 4 имеют неповторитель 36 напряжения с фиксациейсредственное цифровое управление, перегрузки по току выхода, аналоге-Входы и выходы блока 15 сумматоров вый мультиплексор 37 на. 2Р положений,,определены состоянием цепей аналоге- последовательный резистивиый делитель30 вого коммутатора 7. Блок 16 комлара- 38, первый 39 и второй -40 аналоговыеторов предназначен для вызова пре- мультиплексоры на Р положений, муль-рывания через контроллер 13 прерыва- типлексор 41, регистр 42 состояния,,ния в случае превышения сигнала в постоянное запоминающее устройство 43, выбранных точках схемы решения задан- стартстопный генератор 44, одновибра- ного уровня (например, превышение тор 45, счетчик 46, элемент 1-3-ИЛИ-2И(диапазона изменения сигнала). Все 47, первый 48 и второй 49 RS-тригге- блоки устройства 9 аналоговой обра- ры, элемент НЕЭКВИВАЛЕНТНО 50. Блокботкй и вычислений программируемы 18 сравнения напряжений содержит диф- и программно доступны через систем- ференциальный усилитель 51 с кодоуп-до У10 приборную магистраль 8 (наприравляемым коэффициентом передачи, эмиттерный повторитель 52 с кодоуп- равляемым уровнем ограничения тока выхода, дифференциальный усилитель 53, резистор 54, элемент 55 выделения модуля сигнала, пороговьй элемент 56, RS-триггер 57, регистр 58 состояния.

Блок 19 усреднения напряжений содержит регистр 59 состояния, модуль усилителей формирователей 60„ tn ключевых устройств 61 с ограничением коммутируемого тока, дифференциаль- ный сумматор 62s источник 63 напряжения смещения.

Система работает следующим обра- Вом.,

В рабочем режиме аналого-цифровая задача может решаться как с программно управляемой процедурой формирования моделей и установки начальных условий со стороны устройства цифровой обработки и вычислений, так и с выполнением указанной процедуры через блок 1 начальной установки и пуска. Формирование схемы решения в устройстве 9 аналоговой обработки

и вычислений осуществляется посредством аналогового коммутатора 7, который позволяет осуществлять коммутацию любого из его входов на любой из его выходов как одиночными цепями, так и группами цепей. Состояние аналогового коммутатора 7 определяется содержанием его программно доступных регистров. Ввод начальных условий, а также пуск решения и вывод

происходит через блоки аналого-цифровых 5 и цифроаналоговых 6 преобразователей. Кроме того, блоки маошта9 аналоговой обработки и вычислений

бирования 2, нелинейных операционных схем 3 и интеграторов 4 имеют непосредственное цифровое управление, Входы и выходы блока 15 сумматоров определены состоянием цепей аналоге- вого коммутатора 7. Блок 16 комлара- торов предназначен для вызова пре- рывания через контроллер 13 прерыва- ния в случае превышения сигнала в выбранных точках схемы решения задан ного уровня (например, превышение (диапазона изменения сигнала). Все блоки устройства 9 аналоговой обра- боткй и вычислений программируемы и программно доступны через систем- У10 приборную магистраль 8 (например} типа шина крейта КАМАК). Связь с ЦВМ 14 осуществляется через блок 10 сопряжения связи, который может с помощью контроллеров 11 прямого до5 ступа в память и контроллера 12 передачи данных осуществлять два типа обмена - процессорный и прямого доступа в память.

Процесс решения гибридной задачи осуществляется обычным образом с синхронизацией от таймера ЦВМ-14 и может осуществляться полностью автоматически, начиная с этапа набора схемы решения аналоговой части, отлад5 ки, масштабирования, непосредственно решения и вывода результатов решения полностью автоматически по заложенной в ЦВМ программе. В случае необходимости возможно вмешательство опе0

ратора через блок 1 начальной установки и пуска 1.

Одним из возможных контрольных режимов цифроаналоговой вычислительной системы является режим поверки метрологических характеристик решающих и преобразовательных блоков. Для осуществления этого режима в состав цифроаналоговой вычислительной системы введены программно доступные блок 17 эталонных напряжений, блок 18 сравнения напряжений и блок 19 усреднения напряжения.

Назначением этих блоков является создание на базе принципов автономной поверки, имитационного моделирования, рандомизации поверочного эксперимента инструментальной базы поверочной схемы без привлечения сложных, дорогостоящих и медленно работающих поверочных установок.

В задачу блока.7 эталонных напряжений входит преобразование простой, эталонной величины (в данном случае напряжения) в систему шкал, носящих характер реперных отметок. При этом должно выполняться два условия: стабильность хранения эталонной величины должна быть контролируема, а Процедура преобразования должна достоверно проверяться средствами самой системы (принцип автономности); система реперных отметок ,. должна находиться в соответствии с моделью функционирования поверяемых устройств (принцип имитационного моделирования), что должно обоснованно определить число поверяемых точек рабочих шкал приборов и законность имитационного моделирования величины погрешности в промежуточных точках.

В задачу блока 18 сравнений напряжений входит выполнение функции чувствительного элемента поверочной схемы. При этом поскольку поверочные схемы строятся по дифференциальному принципу, то требования к метрологическим характеристикам чувствительного элемента ослабляются, так как погрешность порога срабатывания при подаче на вход усиленной разности величин становится величиной второго порядка малости.

В задачу блока 19 усреднения напряжений входит рандомизация измерительного эксперимента, которая основывается на том факте, что в состав устройства аналоговой обработки и

0

5

0

5

0

5

0

5

0

5

вычислений входит достаточно много решающих и преобразующих блоков, систематические погрешности которых имеют слабую корреляцию. Это позволяет методом усреднения перевести систематические погрешности в разряд случайных и таким образом в значительной мере избавиться от них.

Прежде чем перейти к процессу описания поверки устройств цифроаналоговой вычислительной системы в составе устройства, необходимо рассмотреть работу блока 17 эталонных напряжений, блока 18 сравнения напряжений, блока 19 усреднения напряжений.

Основными элементами блока 17 эталонных напряжений являются положительный и отрицательный источники 20,-20г опорных напряжений. В задачу этих элементов входит сохранение эталонной меры в межповерочный период с наперед заданной достоверностью. Кроме того, блок позволяет выявлять состояние угрозы стабильности метрологических параметров и своевременно производить поверку и отладку. В качестве первичных источников напряжения блока эталонных напряжений с самоконтролем используется параметрический источник 23 о Использование твердотельных элементов значительно улучшает эксплуатационные характеристики устройства, но температурные и временные дрейфы этих элементов еще значительно превышают аналогичные параметры химических нормальных элементов, которые используются в настоящее время в качестве рабочих эталонов напряжения. В целях улучшения этих параметров в источниках 20, и 202ф опорных напряжений применено усреднение п выходных напряжений источников 22 эталонного напряжения, входящих в состав каждого источника 20 опорных напряжений. Известно, что, например, для нормального закона распределения погрешности любого временного среза ансамбля реализаций напряжений выхода каждого из п источников эталонного напряжений дисперсия уменьшается в /п раз. Объединение выходов девяти источников 22 эталонного напряжения позволяет сформировать опорное напряжение с характеристиками, достаточными для поверки устройств на аналогичной элементной базе. Для этого, чтобы было возможным объединение выходов источников 22 эталонного напряжения, они выполнены по схеме с ограничением тока выхода.

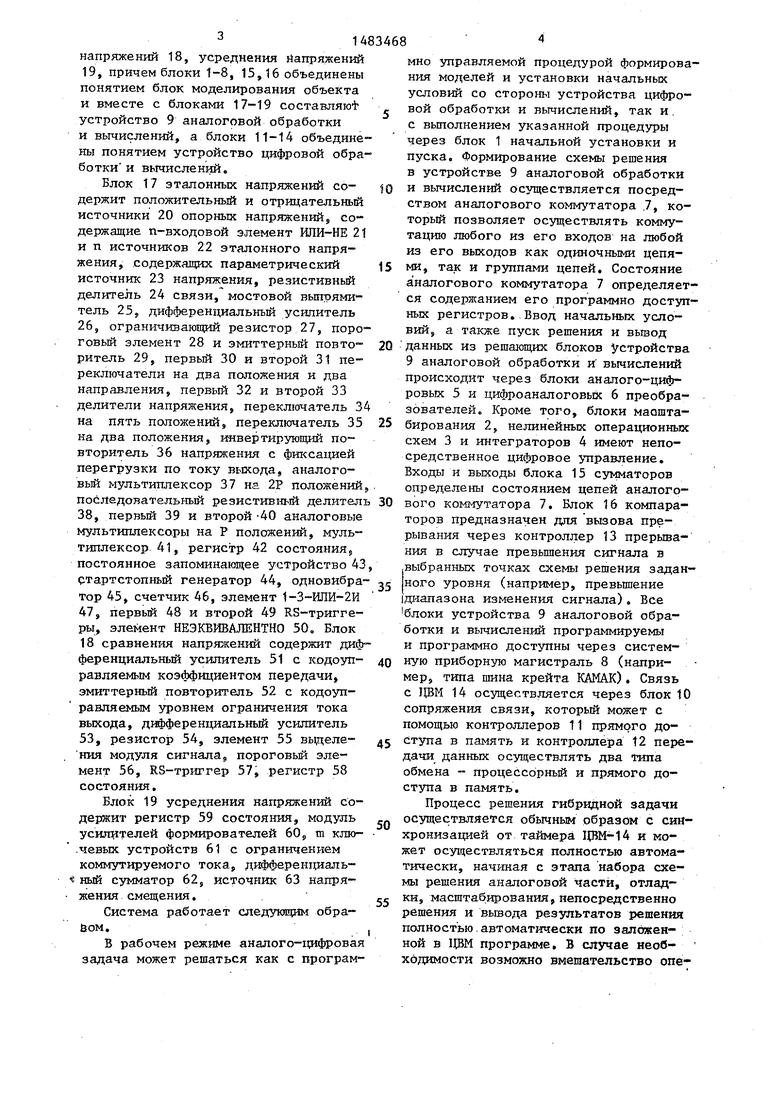

На фиг. 6 обозначено: Л огр - ток ограничения источника 22 эталонного напряжения; ± д статизм системы слежения.

Действительно, доя источника 22 эталонного напряжения при идеальном дифференциальном усилителе 26 для напряжения на выходе справедливо выражение :

К7

IK

1 + ч«4-к„ ЧцКп

JL. р N ..

К JT ) /Sj, 7

Ц.ЭЯЭ q

(D

де U6rt - напряжение на выходе источника 22 эталонного напряжения;

Е - напряжение на среднем выводе параметрического источника 23 напряжения

К 4i - коэффициент усиления разомкнутого дифференциального усилителя 26;

q -4 - коэффициент деления резис- тивного делителя 24 обратной связи; .

I - ток нагрузки источника 22 эталонного напряжения;

R3 - сопротивление резистора

защиты в цепи эмиттерного повторителя 29 с защитой по току перегрузки; - статический коэффициент

усиления транзистора эмиттерного повторителя 29;

, - сопротивление ограничивающего резистора 27;

U)ff{s- падение напряжения на участке эмиттер - база транзистора эмиттерного повторителя с защитой по току перегрузки, которое при номинальных рабочих токах упрощенно можно считать постоянным.

Из фиг. 6 и выражения (1) можно записать:

1пф) + I о

,) ,(2)

f

-f I

«la,

(RS

где VT температурный, потенциал ( 1/т 25 тВ),

14834688

1в - тепловой ток р-n перехода.

Следовательно, ограничивая величину выражения в квадратных скобках

равенства (2) на уровне 1В при q }4 1 и К а 104, получаем величину А 100 мкВ. При (IHRj) 0,4В начинает срабатывать защита эмиттерного повторителя с защитой по току

перегрузки. Так как при этом через ограничивающий резистор 27 начинает протекать часть тока нагрузки, то напряжение на нем должно расти, что и происходит до окончания линейной

зоны дифференциального усилителя 26. После входа дифференциального усилителя 26 в режим насыщения наступает резкое ограничение тока выхода, которое при обычном соотношении R зт

можно определить по приближенной формуле}

5

т К н - U к -is - Ц Оп

Д, и Ј .1 . j

R

(3)

5 i

г

где Е н - напряжение насыщения на выходе дифференциального усилителя .

Учитывая, что при отпирании тран зистора защиты эмиттерного повтори- 0 теля 29 с защитой по току перегрузки нарастание тока через R$T носит экспоненциальный характер, то излом графика на фиг. 6 происходит в очень узкой зоне изменения тока нагрузки. 5 В свою очередь, для линейной области при параллельном соединении источников напряжения имеем:

и Л

П 4. 2г Л

0 % Я

где U е„ - напряжение на выходе системы из параллельно включенных источников напряжения; Е; - ЭДС 1-го источника напряжения;q. - внутренняя проводимость 1-го

источника напряжения; q ь - проводимость нагрузки.

г

Q Величина q . определяется из выражения:

(4)

5

Ч

q-i4Klfc

(5)

VPM RV

где R Ј - омическое сопротивление области базы выходного транзистора эмиттерного повторителя с защитой по току перегрузки.

Из (5) следует, что q. « qw, поэтому (4) можно переписать в сле- . дующем виде:

U.

ЛЕ;д,- Нч

Следовательно, Ucn является средневзвешенным значением Е;„ Если Е . и q; распределены по нормальному закону соответственно с дисперсией 6е и Ц , то дисперсия для U„„ будет определяться из выражения:

t &i+&4

J- in

Первоначальной настройкой источников 22 эталонного напряжения в источниках 20 опорных напряжений мож- но добиться малых значений бси 6 , таких, что дополнительный ток несмотря на малые значения q; не превысит величины I огр о

Действительно, если q ; Ј 100 См, §. разность (U оп - Е,) 100 мкВ, то дополнительный ток ветви будет менее 10 мА. Установив I Огр 20 мА для каждого источника 22 эталонного напряжения, источника 20 опорных напря жений, получаем линейный режим работы для параллельного включенных источников 22 эталонного напряжения для отклонений Е ; от U Oi в пределах +100 мкВ и разбросе значений q. в пределах 100%. При этом стабильность Uor по сравнению со стабильностью параметрических источников 23 напряжений возрастает в Vn раз.

Настройка источников 22 эталонно- го напряжения производится методом сравнения напряжения на выходе каждого с рабочим эталоном, который может быть простейшей мерой напряжения с мостовым компараторным узлом. Та- кие меры доступны и легко могут доставляться на место эксплуатации гибридной вычислительной системы.

После настройки с точностью до 2-5 мкВ все источники 22 эталонного напряжения работают в линейном режиме „ Однако в ходе эксплуатации вследствие временных и температурных дрейфов элементов источников 22 эталонного напряжения напряжение на вы- ходе каждого из них начинает уходить от первоначально установленного значения. Если распределение величин

10

15

™35 40$ 5055дрейфов симметрично, то всегда с заданной вероятностью можно определить п такое, что хотя бы один из источников 22 эталонного напряжения будет дрейфовать противоположно всем остальным. Для обеспечения симметричного распределения дрейфов необходимы технические приемы рандомизации. Например, использование стабилитронов из разных партий, резисторов с равновероятным знаком температурного дрейфа и из разных партий и т.д. В процессе расхождения напряжений на выходах источников 22 эталонного напряжения источник 20 опорных напряжений сохраняет значение на выходе Uon в Vn раз более стабильное. Наконец, вследствие расхождения напряжений на выходах источников 22 эталонного напряжения наступает такой момент, когда один из источников 22 эталонного напряжения переходит в режим ограни- чения тока. Так как значение U 0„ при этом изменится мало, а напряжение на выходе дифференциального усилителя 26 резко возрастает до напряжения насыщения, то ко входу порогового элемента 28 через выпрямитель 25 будет приложен скачок напряжения. При срабатывании пороговый элемент 28 выдает сигнал на элемент ИЛИ-НЕ 21, который объединяет аналогичные сигналы со всех источников 22 эталонного напряжения источника 20 опорных напряжений. Появление сигнала на выходе элемента I ИПИ-НЕ 21 не обязательно свидетельствует об отклонении Uon от заданного значения, но наличие сигнала говорит об угрожающей ситуации для метрологических параметров или о катастрофическом отказе одного из источников 20 эталонных напряжений. Во всяком случае отсутствие сигнала на выходе элемента ИЛИ-НЕ 21 с наперед заданной вероятностью гарантирует нахождение Uon в заданных пределах. Появление сигнала на выходе элемента ИЛИ-НЕ 21 такой гарантии не дает и, следовательно, источник 22 эталонных напряжений нуждается в поверке и настройке.

Поскольку источник 22 эталонных напряжений является связующим звеном в системе обеспечения автономной поверки устройств цифроаналоговой вычислительной системы с государственными эталонными эталонами напряжения, то следует отметить следующее: для

поверки источника 22 эталонных напряжений требуется простейший рабочий эталон; состояние источника 22 эта-, лонных напряжений самоконтролирует- ся. Эти два положения отвечают требованиям, которые должны быть обеспечены техническими средствами автономной поверки. Далее техническими средствами блока 17 эталонных напряже- ний и программными средствами ЦВМ 14 обеспечивается создание автономной многоэталонной меры.

Порождение системы шкал реперного характера блоком 17 эталонных налря- жений осуществляется с помощью последовательного резистивного делителя 38, напряжение с выходов которого через мультиплексор 37 на 2Р положений и через повторитель 36 напряжения с фиксацией перегрузки по току выхода поступает на выход блока 17. Все остальные устройства блока эталонных напряжений предназначены для автономной поверки и управления функцио- нированием.

Алгоритм поверки осуществляется с помощью аппаратных средств блока 17 под управлением ЦВМ 14. Процедура поверки начинается с записи в регистр 42 состояния командного слова, один из битов которого установит мультиплексор 41 в положение связи его выхода с первым выходом постоянного запоминающего устройства 43. Состоянием этого же бита запускается старт стопный генератор 44 и на выходе одновибратора 45 генерируется импульс {тачальной установки первого 48 и второго 49 RS-триггеров. С выхода старт- стопного генератора 44 последовательно во времени заполняется счетчик 46, параллельный выход которого формирует адресную шину постоянного запоминающего устройства 43. Младший бит этой адресной шины поступает на че- тырехвходовый элемент 1-3-ИПИ-2И 47 для стробирования. Каждое многоразрядное выходное слово постоянного запоминающего устройства 43 состоит из . двух -частей - адресной и контрольной. В адресной части содержится управление состоянием переключателей и мультиплексоров, а в контрольной - бит контроля состояния выхода Перегрузка инвертирующего повторителя 36 напряжения с фиксацией перегрузки по току выхода. В свою очередь, адресная часть выходного слова постоянного

Q 5

5

запоминающего устройства 43 состоит из отдельных адресных полей управления первым 30 и вторым 31 переключателями на два положения и два направления, переключателем 34 на пять положений, переключателем 35 на два положения, первым 39 и вторым -1 40 аналоговыми мультиплексорами на Р положений и аналоговым мультиплексором на 2Р положений. Таким образом, имеется всего семь адресных полей различной разрядности, каждое из которых определяет положение соответствующих переключателей на каждом такте автономной поверки блока эталонных напряжений. Бит контроля состояния выхода Перегрузка инверти- рующего повторителя 36 зашивается в ПЗУ такого значения, каким должен быть выход Перегрузка повторителя 36 в случае исправной работы проверяемых устройств. Тогда на выходе элемента НЕЭКВИВАЛЕНТНО 50 не будет сформирован установочный сигнал для первого RS-триггера 48. В противном случае, т.е. если сигнал на выходе Перегрузка инвертирующего повторителя 36 напряжения с фиксацией перегрузки по току выхода не совпадает со значением контрольного бита на выходе ПЗУ 43, сигналом с выхода элемента НЕЭКВИВАЛЕНТНО первый RS-триггер 48 будет установлен в единичное состояние, что свидетельствует об обнаружении неисправности. Четырехвходовый элемент 1-3-ИЛИ-2И 47 объединяет сигнал Неисправность, который поступает или с выхода первого RS-триггера 48 или с выходов источников 20 опорных напряжений. На каждом такте процедуры поверки осуществляется стробирование этих сигналов и, если они появляются, то с выхода четырехвходового элемента 1-ЗИЛИ-2И 47 происходит установка второго RS-триггера 49. Состояние выхода второго RS-триггера 49 опрашивается ЦВМ 14 для анализа исправности блока эталонных напряжений с самоконтролем. Таким образом, после записи командного слова в регистр 42 состояния контроль исправности блока 1 7 осуществляется по микропрограмме защитой в ПЗУ 43. Последовательность контроля следующая (см. блок- схему алгоритма на фиг. 7). После пуска режима, осуществленного записью в регистр 42 состояния соответствунщего командного слова, проверяется (программно) состояние выхода второго триггера 49, который может взвестись сразу же на первом такте микропрограммы из-за неисправного состояния источников 20 опорного напряжения. Затем осуществляется проверка компараторного режима инвертирующего повторителя 36 напряжения с фиксацией перегрузки по току выхода. Инвертирующий повторитель 36 напряжения проверяется в трех точках. Сначала через аналоговый мультиплексор на 2Р положений на вход повторителя 36 подается потенциал общей шины, а выход повторителя 36 через переключатель 34 на пять положений (четвертый вывод), переключатель 35 на два положения, первый переключатель 30 на два положения и два направления (четвертый выход) и первый аналоговый мультиплексор 39 на Р положений также подключается к общей шине устройства. Устройство контроля защиты выхода инвертирующего повторителя 36 напряжения работает аналогично описанному выше устройству ограничения тока выхода источника эталонного напряжения 22. Поэтому его функционирование может быть также описано выходной характеристикой на фиг. 6, Если напряжение смещения инвертирующего повторителя 36 напряжения с фиксацией перегрузки по току выхода будет меньше установленной заданной точностью величины д, то, следовательно, по данному параметру откло- нени$ нет, в противном случае согласно описанному ранее механизму произойдет установка триггера 49. Далее повторитель 36 напряжения проверяется на срабатывание по току перегрузки. Для этого его вход остается подключенным через мультиплексор 37 к общей шине устройства, а выход последовательно подключается через переключатель 34 к средним выводам первого Э2 и второго 33 делителей напря- дсения. Напряжение на средних выводах этих делителей устанавливается таким образом, чтобы оно было равно заданной чувствительности срабатывания защиты по току повторителя 36 ( Д , см. фиг„ 6)% Если защита срабатывает, что проверяется контрольным битом |на выходе ПЗУ 43, то можно считать, что компараторный механизм инвертирующего повторителя напряжения с

0

5

0

5

0

5

0

5

0

5 7

фиксацией перегрузки по току выхода работает и имеет заданную чувствительность. Далее согласно блок-схеме алгоритма на фиг. 7 программно осуществляется проверка состояния триггера 49. Если триггер 49 остался в сброшенном состоянии, то значит инвертирующий повторитель 36 успешно прошел проверку на компараторный режим и далее можно приступить к другим видам автономной проверки. В противном случае устройство следует считать неисправным.

Последовательный резистивный делитель 38 является основным элементом формирования реперных эталонных шкал блока 17 эталонных напряжений. При любом соотношении резисторов в цепочке относительно средней (заземленной) точки последовательный резистивный делитель 38 представляет собой симметричную схему„ Поэтому имеется возможность проверки соотношения плеч делителя по мостовой схеме с чувствительным органом из инвертиру ющего повторителя 36 напряжения с фиксацией перегрузки по току выхода. Для этого средняя точка (заземленная) последовательного резистивного делителя 38 через аналоговый мультиплексор на 2Р положений подключается к входу повторителя 36, выход которого через ветвертый выход переключателя 34 на пять положений и первые выводы первого 30 и второго 31 пере-. ключателей на два положения и два направления подключается к крайним выводам последовательного резистивного делителя 38, При этом выходы источника 20 опорных напряжений через третьи выводы первого 30 и второго 31 переключателей на два положения и два направления и через первый 39 и второй 40 аналоговые мультиплексоры на Р положений подключаются к различным выводам последовательного резистивного делителя 38. Первый и второй аналоговые мультиплексоры 39, 40 на Р положений должны при этом работать синфазное Известно, что условием баланса моста является равенство произведений сопротивлений противоположных плеч. Из фиг.& ,видно, что последовательно переключая синфазно аналоговые мультиплексоры 39 и 40 на Р положений, можно проверить стабильность величин отношений резисторов делителя 38, что гарантирует стабильность отношений ре- перных шкал. Точность соблюдения отношений величин резисторов обеспечивается проверенной уже к данному -моменту чувствительностью инвертирующего повторителя 36 напряжения. В случае срабатывания чувствительного элемента по контрольному биту данного такта это событие будет выявлено и осуществится взведение триггера 49. Поэтому согласно блок-схеме алгоритма на фиг. 7 необходима проверка состояния триггера 49.

Далее осуществляется проверка тракта формирования реперных шкал и масштабного коэффициента передачи . инвертирующего повторителя 36 напряжения с фиксацией перегрузки по току выхода. Для этого переключатель 34 на пять положений устанавливается на замыкание входа с третьим выходом первый и второй переключатели на два положения и на два направления устанавливаются на связь с переключателем на два положения. При такой конфигурации целей положительное и отрицательное опорные напряжения подаются на крайние выводы последовательного резистивного делителя 38, любые первые Р выводов делителя 38 через первый аналоговый мультиплексор 39 могут быть поданы на выход повторителя 36, а любые Р последних выводов делителя 38 при условии переключения переключателя 35 на два положения через второй аналоговый мультиплексор 40 на Р положений также могут быть поданы на выход повторителя 36. В то же время любой вывод последовательного резистивного дели- теля.38 через аналоговый мультиплексор 37 может быть подключен к входу инвертирующего повторителя 36 напряжения с фиксацией перегрузки по току выхода. Следовательно, имеется возможность любое положительное напряжение с выхода делителя 38 замкнуть на равное по модулю отрицательное напряжение того же делителя через инвертирующий повторитель 36. С учетом инверсии эти напряжения должны быть равны при условии заданного коэффициента передачи повторителя 36, равенства по модулю Е, источников 20, равного соотношения плеч делителя 38 и исправной работы переключателей в пределах установленной чув

ствительности компараторного узла повторителя 36.

Результат проверки на каждом такте контролируется контрольным битом, который на данньй такт генерирует ПЗУ 43. По завершению этого вида проверки осуществляется контроль состояния триггера 49 и, если он остается сброшенным, блок 17 эталонных напряжений следует считать исправным и готовым к функционированию.

Следует отметить, что схема управ5 ления автономной проверкой блока не останавливается по завершению всего цикла проверок, а переходит на следующий цикл по заполнению и самосбросу счетчика 46, что позволяет без допол0 нительных команд управления постоянно держать блок 17 в режиме самоконтроля.

Для перехода в рабочий режим необходимо в регистр 42 состояния запи5 сать командное слово рабочего режима. При этом битом управления мультиплексор 41 будет переведен на связь его выхода с выходом адресной части регистра 42 состояния. Адресная часть регистра 42 состояния аналогично первому выводу ПЗУ 43 содержит отдельные поля управления каждым из переключателей и мультиплексоров устройства. Следовательно, все описанные процедуры за исключением контрольного бита могут выполняться и программно. Однако в рабочем режиме переключатель 34 на пять положений устанав-- ливается на связь с выходом устрой0 ства (второй выход переключателя), переключатели 30 и 31 устанавливаются на связь выходов источников 20 с крайними выводами последовательного резистивного делителя 38, а управление в основном осуществляется аналоговым мультиплексором 37 на 2Р положений, через который на выход устройства подаются эталонные напряжения, соответствующие системе реперных шкал, принятой для осуществления поверки решающих и преобразовательных блоков цифроаналоговой вычислительной системы. Положение переключателя 35 на два положения и первого 39 и второго 40 аналоговых мультиплексоров на Р положений в рабочем режиме безразлично.

Следует отметить, что блок 17 эталонных напряжений позволяет перейти

0

5

5

0

5

от простой меры напряжения к шкале напряжений с заданной и контролируемой степенью точности.

Входом устройства является неинвертирующий вход измерительного дифференциального усилителя 51.

Кодоуправляемый резистор в цепи Обратной связи первого каскада дифференциального усилителя позволяет в широких пределах регулировать коэффициент передачи усилителя 51. Выход измерительного дифференциального усилителя 51 через резистор 54 подключен к входу эмиттерного повторителя 52 с кодоуправляемым уровнем ограничения тока. Выход эмиттерного повторителя является выходом устройства, а также подключен х инвертирующему входу дифференциального усилителя 51. Следовательно, система охвачена 100%-ной обратной связью и имеет коэффициент передачи, равный 1 с точностью до погрешности статиз- ма. Дифференциальный усилитель 53 усиливает падение напряжения на резисторе 54 и подает сформированный сигнал на вход элемента 55 выделения модуля сигнала. Сигнал с выхода элемента 55 поступает на вход порогового элемента 56, на выходе которого формируется сигнал рассогласования, этим сигналом взводится триггер 57. Функционирование блока 18 сравнения напряжений заключается в передаче сигнала с входа на выход с коэффициентом передачи, равным единице, с ограничением тока выхода. Управление блоком программируемого модуля сравнения напряжений осуществляется от программно доступного регистра 58 состояния, в который записывается управляющее слово, состоящее из двух полей - поля управления кодоуправляемым резистором измерительного дифференциального усилителя 51 и поля управления кодоуправляемым резистором эмиттерного повторителя 52. Механизм ограничения тока выхода аналогичен механизму ограничения тока выхода в источниках 20 опорных напряжений и описан ранее. Выходная характеристика блока 18 аналогична характеристике, приведенной на фиг. 6, Однако благодаря тому, что имеется возможность программно изменять разомкнутый коэффициент усиления измерительного дифференциального усилителя 51 и уровень защиты по току эмиттерногс

0

0

повторителя 52, появляется возможность менять величину л и I огр на фиг. 6. Это означает, что если блок 18 используется в качестве элемента сравнения, то имеется возможность изменять его чувствительность (если длительность линейной зоны д) и мощность выхода I огр , что имеет значение для организации схемы упорядоченного выбора при параллельном включении источников напряжения.

В поверочной схеме цифроаналого- вой. вычислительной системы блок 18

5 (Сравнения напряжений до его применения нуждается в проверке и контроле. Эта процедура осуществляется путем заземления второго информационного входа блока через аналоговый коммутатор 7 и подаче на его первый информационный вход с блока эталонных напряжений уровней напряжения заданной величины и . Так как и зависит как от коэффициента усиления инстру5 ментального дифференциального усилителя, так и от выбранной величины lorp то проверку следует осуществлять отдельно по двум регулируемым параметрам. Изменение чувствительности компараторной схемы проверяется по факту несрабатывания от предыдущего поверочного уровня и срабатывания от следующего поверочного уровня. Факт срабатывания определяется по состоянию триггера 57. Т.е. зона неопределенности при поверке блока 18 сравнения напряжении составляет 50% от кванта регулирования, но так как блок используется только как чувствительный элемент, это становится достаточным для организации поверочной схемы. Поверка передаточной характеристики блока 18 сравнения напряжений основывается на линейной модели дифференциального усилителя с глубокой отрицательной обратной связью. Поскольку смещение нуля блока определяется при проверке его работы в компараторном режиме с заземленным выходом, то далее проверяется коэффициент передачи только в двух крайних точках характеристики,

0

5

0

5

0

т.е. 411

Маис

и -U иак. о Для этого вто5

рой информационный вход блока 18 подключается последовательно во времени через аналоговый коммутатор 7 к выходным поверочным гнездам блока 17 эталонных напряжений, а на первый информационный вход блока 18 подается соответствующее напряжение +Uon, при этом устанавливается наивысшая чувствительность компараторной схемы Если схема защиты по току не сраба-1 тьгеает, то можно считать линейность коэффициента передачи блока удовлетворительной.

Блок 19 усреднения напряжений содержит m ключевых устройств 61 с ограничением коммутируемого тока. Дифференциальный усилитель 62 совместно с источником 63 напряжения смещения образуют схему формирования сигнала U..,v + Е г.„ . где U.

ьых см s м « вых - напряжение на выходе устройства, Е см- напряжение источника 63 смещения. Этот сигнал используется в ключевых устройствах 61 для управления током нагрузки ключа независимо от величины на- пряжения на выходе. При этом предполагается, что ток выхода блока 19 усреднения напряжений пренебрежимо мал. Управление ключевыми устройствами 61 осуществляется с выхода программно доступного регистра 59 состояния через блок 60 усилителей формирователей по радиальной схеме. При положительном потенциале на каждой управляющей шине соответствующей ключ открыт, при отрицательном - закрыт. Отличительной особенностью блока 19 усреднения напряжений является работа со всеми или подавляющим большинством открытых ключей, так как ток каждого ключа ограничен по величине, то очевидно, что схема не будет повреждена. Напряжение на выходе будет следующим.

Если упорядочить напряжение на входах ключей соответственно U 1$ U,

г

и, где U , 7 U7 7 U з ...

U

.Um, при условии I erf, I ores

Ior.3 „.. I Ofp w , часть ключей

войдет в насыщение с отрицательным

током ограничения (для ключей с

ь, Ј У ьмх ) а часть ключей войдет

в насыщение с положительным током

насыщения (для ключей с U 6t , U Ь4()1 )

только один ключ, находящийся по

величине Ugx где-то в середине, буде

работать в линейном режиме, а его

входной сигнал будет соответствовать

сигналу U ftblt устройства При этом

(-1 orp had l I огР ич«|+ Т1 ГДе Ве

личина -Y формируется ключом, находящимся в линейном режиме. Следовательно, если на входы блока 19 усреднения напряжений подать мало отлича

0

ющиеся сигналы, то на выходе будет сформирован сигнал, равный медиане распределения входовых сигналов, т.е. величина, близкая к среднему значению,, Этот факт позволяет понизить дифференциальную погрешность ЦДЛ методом объединения группы ЦДЛ через блок 19 усреднения напряжений. Поверка блока осуществляется в нескольких точках характеристики на основании линейной модели устройства. Поверка осуществляется методом эталонного сигнала от блока эталонных на5 пряжений с самоконтролем. Сравнение осуществляется с помощью блока 18 сравнения напряжений. Поверочная схема формируется с помощью аналогового коммутатора 7. Следует отметить, что должны поверяться как каждый канал блока 19, так и режим усредне

ния, для чего на объединенные входы коммутатора подается эталонный сигнал, все каналы открываются и осу- ществляется сравнение выходного сигнала с выходным с помощью блока 18 1сравнения напряжений.

Ио завершении контрольных прове- рок блока 17 эталонных напряжений, блока 18 сравнения напряжений и блока 19 усреднения напряжений можно переходить непосредственно к поверке метрологических характеристик решающих и преобразовательных блоков цифреаналоговой вычислительной системы. В процессе проверки необходимо исходить из модели поверяемого устройства. Так, для поверки суммирующих усилителей, интеграторов и других устройств с линейными характеристиками достаточно осуществить поверку в нескольких точках характеристики, для чего достаточно набора эталонных мер, содержащихся в блоке 17 эталонных напряжений. Измерительная схема для поверки таких устройств реализуется с помощью аналогового коммутатора 7.

Напротив, модели таких устройств, как ЦДЛ и АЦП, нелинейные операционные схемы, блоки масштабирования, кодоуправляемые интеграторы, содержат резко выраженные нелинейности, что вынуждает осуществлять поверку таких устройств в числе точек характеристики, гораздо превышающем количество эталонных мер в блоке 17. Для поверки таких устройств необходим

источник достаточно плавно меняющейся эталонной меры.

В устройстве такая мера формируется с помощью блока ЦАП 6 и блока 19 усреднения напряжений. Это осуществляется следующим образом. Сначала все ЦАП блока 6 поверяются в точках эталонных мер, имеющихся в блоке 17 эталонных напряжений. Поверяемый ЦАП подключается через блок 19 усреднения напряжений на первый информационный вход блока 18 сравнения напряже ний, второй информационный вход которого подключен к выходу блока 17 эталонных напряжений. Ток насыщения блока 18 устанавливается меньше тока насыщения инвертирующего повторителя напряжения блока 17. Увеличивая (или уменьшая) коэффициент усиления блока 18 сравнения напряжений, определяется момент срабатывания защиты или в соответствии с графиком на фиг. 6 величина Д , которая в данном случае является абсолютной погрешностью поверяемого ЦАП. Если определенная таким образом величина Л меньше лАСп то считается, что ЦАП годен для формирования непрерывной эталонной меры. В противном случае ЦАП выбраковывается. Канал аналогового коммутатора выделения среднего, к которому подключен через коммутатор 7 вы .бракованный ЦАП, отключается, а все

ЦАП блока 6, удовлетворяющие заданным требованиям в поверяемых точках, .подключаются к открытым каналам блока 19 усреднения напряжений. При этом на выходе блока 19 формируется величина, близкая к среднему значению напряжений на выходах группы ЦАП. Если ча входы всех ЦАП подать один и тот же код, то на выходе блока 19 будет напряжение, близкое к значению среднего, следовательно в г раз более точное, чем для отдельного ЦАП. Учитывая, что в блоке 6 число независимых ЦАП велико, можно добиться значительного повышения точности установки сигнала.. Эксперимент усреднения можно считать рандонизирован- ным, так как в настоящее время блок 6 ЦАП обычно выполняется по параллельной схеме, т.е. состоит из набора независимых ЦАП. Кроме того, изменяя на небольшую величину в сторону увеличения или уменьшения входные коды некоторых ЦАП можно менять выходное значение сигнала на выходе аналогового коммутатора выделения среднего, следовательно, имеется возможность устранять систематическую погрешность в поверяемой точке.

Если поверяемые точки ЦАП выбраны таким образом, что совпадают с моментами наиболее резкого изменения в структуре ЦАП, то, основываясь на

модели формирования погрешности этих устройств, можно утверждать, что в промежуточных точках погрешность ЦАП не превысит определенную в поверяемых. Следовательно, имеется возмож5 ность формирования непрерывной эталонной меры на выходе блока 19. Регулирование эталонной меры в пределах кванта сигнала ЦАП осуществляется путем увеличения или уменьшения кода

на входах ряда ЦАП группы.

Используя непрерывную эталонную меру на основе блока 6 ЦАП, блока 19 усреднения напряжений, блока 18 сравнения напряжений, имеется возмож5 ность осуществлять поверку методом эталонного сигнала всех решающих и преобразовательных блоков цифроаня- логовой -вычислительной системы.

Поверочная схема формируется ана-

0 логовым коммутатором 7. Эталонный сигнал создается блоком 6 ЦАП и блоком 19 усреднения напряжений. Сравнение сигналов осуществляется в цифровой форме процессором ЦВМ-14. При

5 одинаковой разрядности ЦАП и АЦП соответственно блоков 6 и 5 погрешность установки эталонного сигнала на входе АЦП составляет:

d JT

0

1 ц An

А 2 & НОМ

/ V, (8)

где &цдп и & ком - дисперсия распределения случайной составляющей погрешности соответственно канала ЦАП и канала аналогового коммутатора вы- 5 ведения среднего;

г - число задействованных каналов аналогового коммутатора выделения среднего.

Из (8) видно, что при г 16 и одинаковой точности каналов ЦАП и АЦП устройством формируется поверочный сигнал достаточной точности.

Поверка каждого ЦАП осуществляется по разностной схеме. В качестве чувствительного элемента используется блок 18 сравнения напряжений. Эталонный сигнал формируется блоком 6 ЦАП и блоком 19 усреднения напряже0

5

2314

ний. Причем поверяемый ЦАП из блока подключается не к входу блока 19 усреднения напряжений, а к второму информационному входу блока 18 сравнения напряжений. Следует помнить, что все ЦАП модуля 6 на данной стадии уже прошли допусковый контроль в ре- перных точках вырабатываемых блоком 17 эталонных напряжений. Для поверки в промежуточных точках по значению среднего группы уровень срабатывания защиты по току блока 18, выход которого соединен с выходом блока 19, устанавливается ниже уровня срзбаты- вания защиты по току каналов блока 1 что приводит к насыщению его выхода при несовпадении значений напряжений на входе и выходе. Уменьшая коэффициент усиления блока 18, находится точка, в которой защита уже не срабатывает, т.е. определяется Л (см0 фиго 6), которая равна абсолютной погрешности поверяемого ЦАП. Анало

8

24

ционные схемы, интеграторы в некоторых режимах) могут поверяться по схеме с двойным преобразованием, для чего в поверочную схему включен блок АЦП 5. Формируется поверочная схема аналоговым коммутатором 7.

Следует отметить, что формирование эталонного сигнала от блока ЦАП 6 с помощью блока 19 усреднения напряжений позволяет осуществлять поверку блоков в динамическом режиме. Дей- ствительно, формируя сигнал заданной частоты и осуществляя опрос блока 18 с учетом фазового запаздывания, можно осуществлять поверку устройств на рабочих частотах.

Формула изобретения

Цифроаналоговая вычислительная система, содержащая устройство цифро- вой обработки и вычислений, блок сопряжения и устройство аналоговой,об-

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПУЛЬСОВОГО ОКСИМЕТРА | 2001 |

|

RU2201139C1 |

| Устройство для поверки электрических и механических секундомеров | 1982 |

|

SU1123018A1 |

| Универсальный калибратор тока | 1985 |

|

SU1308969A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1986 |

|

SU1425698A2 |

| ШИРОКОДИАПАЗОННЫЙ КАЛИБРАТОР, УПРАВЛЯЕМЫЙ ДИФФЕРЕНЦИАЛЬНЫМ ВОЛЬТМЕТРОМ | 2006 |

|

RU2333505C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2010 |

|

RU2499237C2 |

| Устройство для контроля параметров электронных схем | 1982 |

|

SU1112324A1 |

| СПОСОБ КОНТРОЛЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ УСИЛИТЕЛЯ, АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ УСИЛИТЕЛЯ | 2002 |

|

RU2212674C1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| Магазин сопротивления-калибратор напряжения | 1991 |

|

SU1797078A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования динамических систем. Цель изобретения - повышение надежности устройства. Цифроаналоговая вычислительная система содержит устройство цифровой обработки и вычислений, блок сопряжения, устройство аналоговой обработки и вычислений, в состав которого входит блок моделирования объекта, блок эталонных напряжений, блок сравнения напряжений, блок усреднения напряжений. В системе осуществляется автоматическая поверка всех метрологически нормируемых блоков. 12 ил.

гичным образом поочередно осуществля - 25 работки и вычислений, содержащее блок

ется поверка всех остальных ЦАП блока 6 „

Сумматоры АВМ являются устройствами с линейной характеристикой. Одна™ ко большое число возможных коэффициентов суммирования, значений общего множителя приводит к необходимости поверять как сам суммирующий усилитель, так и рабочие операционные схемы. Поэтому в поверочной схеме предусмотрена возможность поверки операционного усилителя при К 1 от блока 17 эталонных напряжений в реперных точках по разностной схеме, описанной выше. Для поверки рабочих схем используется режим масштабирования сумматора с объединенными входами, на которые подается сигнал блока 17, а выходной сигнал сравнивается с сигналом, полученным расчетным путем и устанавливаемым на выходе блока 19от блока ЦАП 6.

Поверка устройств блоков осу- ществля ется также по разностной схеме. В качестве эталонного сигнала используется сигнал либо с выхода блока 17 эталонных напряжений, либо с выхода блока 19 усреднения напряжений (для поверки нелинейных операционных; схем в контрольных точках). В качестве чувствительного устройства используется блок 18 сравнения напряжений. Часть блоков пониженной точности (например, нелинейные опера5

моделирования объекта, причем входы- выходы адреса, синхронизации и данных устройства цифровой обработки и вычислений соединены с соответству0 ющими первыми входами-выходами блока сопряжения, а входы-выходы адреса, синхронизации и данных блока моделирования объекта устройства аналоговой обработки и вычислений соединены с соответствующими вторыми входами-выходами блока сопряжения, отличающаяся тем, что, с целью повышения надежности, в устройство аналоговой обработки и вычис0 лений введены блок эталонных напряжений, блок сравнения напряжений и блок усреднения напряжений, причем входы-выходы адреса, синхронизации и данных блока эталонных напряжений,

д блока сравнения напряжений, блока усреднения напряжений соединены с со4- ответствующими вторыми входами-выходами блока сопряжения, выходы эталонного напряжения блока эталонных на- пряжений соединены с. входом эталонного напряжения блока моделирования объекта, первый и второй информацион- ные выходы блока моделирования объекта соединены с первым и вторым информационными входами блока сравнения напряжений группа информационных вы ходов блока моделирования объекта соединена с группой информационных входов блока усреднения напряжений,

5

25

148346826

а выход значения среднего напряжения с входом среднего напряжения блока блока усреднения напряжений соединен моделирования объекта.

К А |/ си

Фиг 1

Фиг. 3

VU09- ность

+1огр

-А

Т

Фиг. 5

+д

-lorp

Фиг. 6

С

Сброс триггера 49. Установка режима контроля. Лук режима

I - проверка Тг. 49 yi

Проверка умв. повтор, напр, зв S ракит -щааратвра

-Л ЯроВеркаfe 4ff. Ni

Проверка последовательного резистивного делителя За по мостовой схепеj

I Проверка ЪЛ§

проверка тракта форпиробания релерных шкал а масштабного коэффициента передачи повторителя 36

Ч Прй&ерка Те. 4ff

ФорпироВание согнала иКтооиостй блока 17

начало

J

V/

ФорнароВанш ы&юм .Heucnpalrtocmt Блока i7

8

Фиг. 3

(риг. 10

Фиг. ff

8

v

Фиг. 12

| Патент США № 3761689, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-30—Публикация

1987-03-18—Подача