му входу -го блока элементов И-НЕ четвертой группы, к. второму входу которого подсоединен инверсный выход i-го регистра второй группы, выход -го блока элементов И-НЕ четвертой группы подсоединен к второму Ьходу i -го элементов ИЛИ первой группы, к второму входу ( -го элемента И второй группы подсоединен третий выход 1 -и сравнения Группы, второй выход которой подсоединен к второму входу i -го блока элементов И-НЕ второй группы, выход элемента НЕ подсоединен к третьему бходу блока регистров, второй выход Которого подсоединён к входам сброса регистров первой и второй групп.

третий выход блока регистров подсоединен к первым входам триггеров второй группыр к вторым входам которых подсоединен выход второго блока элементов И, второй вход которого подсоединен.к выходу первого узла поиска максимального кода и к четвертому входу блока регистров, инверсные выходы -X регистров первой группы соединены с вторыми входами -X блоков элементов И-НЕ третьей групшл, тактовый вход и вход запуска устройства соединены соотв етственно с первым и вторьгм входами элемента И, третьи выходы i -х схем сравнения группы соединены с третьими входами элементов И третьей группы./

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исследования путей в графе | 1982 |

|

SU1076909A1 |

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Устройство для моделирования сетевых графов | 1982 |

|

SU1065858A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1126963A1 |

| Устройство для исследования путей в графах | 1981 |

|

SU1005066A2 |

| Устройство для распределения заданий вычислительной системе | 1982 |

|

SU1100623A1 |

| Устройство для распределения заданий в сетях электронных вычислительных машин | 1982 |

|

SU1075261A1 |

| Устройство для моделирования сетевых графов | 1984 |

|

SU1251099A1 |

| Устройство для распределения заданий | 1980 |

|

SU903876A1 |

| Устройство для распределения заданий процессорам | 1985 |

|

SU1283764A1 |

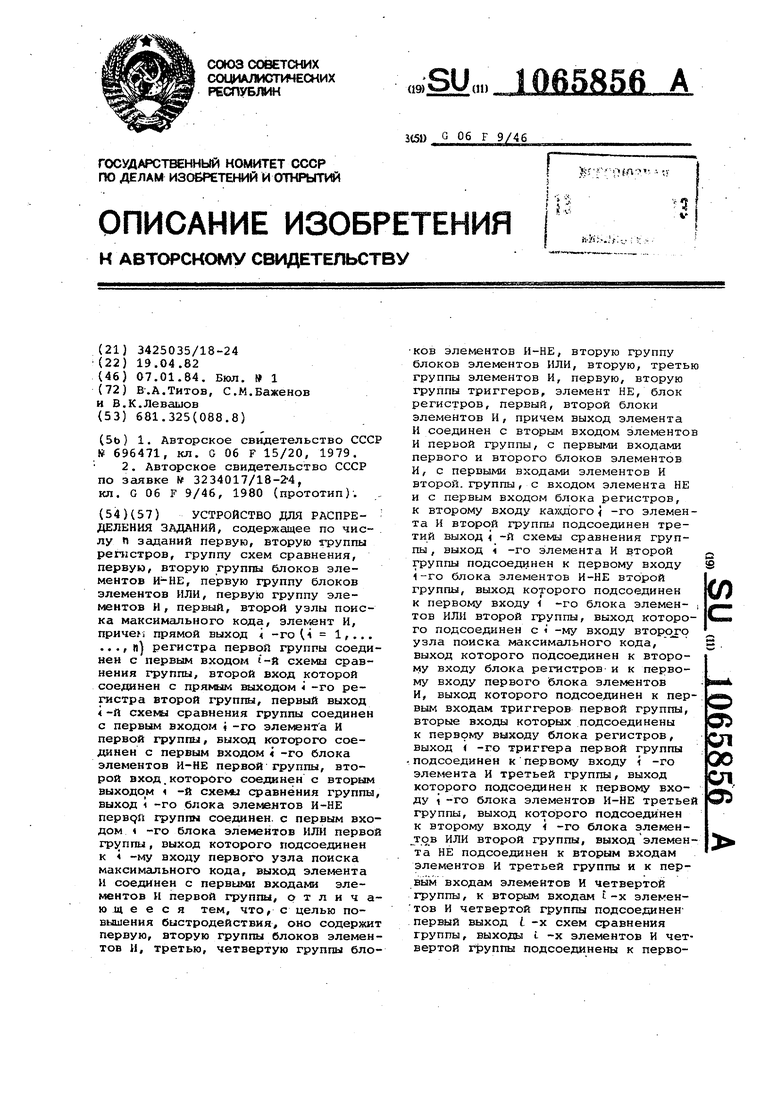

УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ ЗАДАНИЙ, содержащее по числу П заданий первую, вторую труппы ретстров, группу схем сравнения, первую, вторую группы блоков элементов и-НЕ, первую группу блоков элементов ИЛИ, первую группу элементов И, первый, второй узлы поиска максимального кода, элемент И, приче прямой выход -го ( 1, ... ..., и) регистра первой группы соединен с первым входом i-й схемы сравнения группы, второй вход которой соединен с прямым выходом -то регистра второй группы, первый выход i-и схемы сравнения группы соединен с первым входом -го элемента И первой группы, выход которого соединен с первым входом -го блока элементов И-НЕ первой группы, второй вход.которого соединен с вторым выходом 1 -и cxeMj сравнения группы, выход 1 -го блока элементов И-НЕ nepBQJi группы соединен, с первым входом 1 -го блока элементов ИЛИ первой , выход которого подсоединен к -му входу первого узла поиска максимального кода, выход элемента И соединен с первыми входами элементов И первой группы, отличающееся тем, что, с целью повышения быстродействия, оно содержит первую, вторую группы блоков элементов И, третью, четвертую группы блоков элементов И-НЕ, вторую группу блоков элементов ИЛИ, вторую, третью группы элементов И, первую, вторую группы триггеров, элемент НЕ, блок регистров, первый, второй блоки элементов И, причем выход элемента И соединен с вторым входом элементов И первой группы, с первыгФ входами первого и второго блоков элементов И, с первыми входами элементов И второй, группы, с входом элемента НЕ и с первым входом блока регистров, к второму входу каходого -го элемента И второй группы подсоединен третий выход i -и схемы сравнения группы , выход i -го элемента И второй о S группы подсоединен к первому входу 1-го блока элементов И-НЕ второй (Л группы, выход которого подсоединен к первому входу -го блока элемен- , тов ИЛИ второй группы, выход которого подсоединен с -му входу второго узла поиска максимального кода, выход которого подсоединен к второму входу блока регистров- и к первому входу первого блока элементов И, выход которого подсоединен к первым входам триггеров первой группы, : ел вторые входы которых подсоединены к первому выходу блока регистров, выход -го триггера первой группы 00 .подсоединен кпервому входу i -го О1 элемента И третьей группы, выход которого подсоединен к первому вхоСГ) ду i -го блока элементов И-НЕ третьей группы, выход которого подсоединен к второму входу i -го блока элеменjroB ИЛИ второй группы, выход элемента НЕ подсоединен к вторым входам элементов И третьей группы и к первым входам элементов И четвертой группы, к вторым входам i-х элементов И четвертой группы подсоединен первый выход L -х схем сравнения группы, выходы L -X элементов И четвертой группы подсоединены к перво

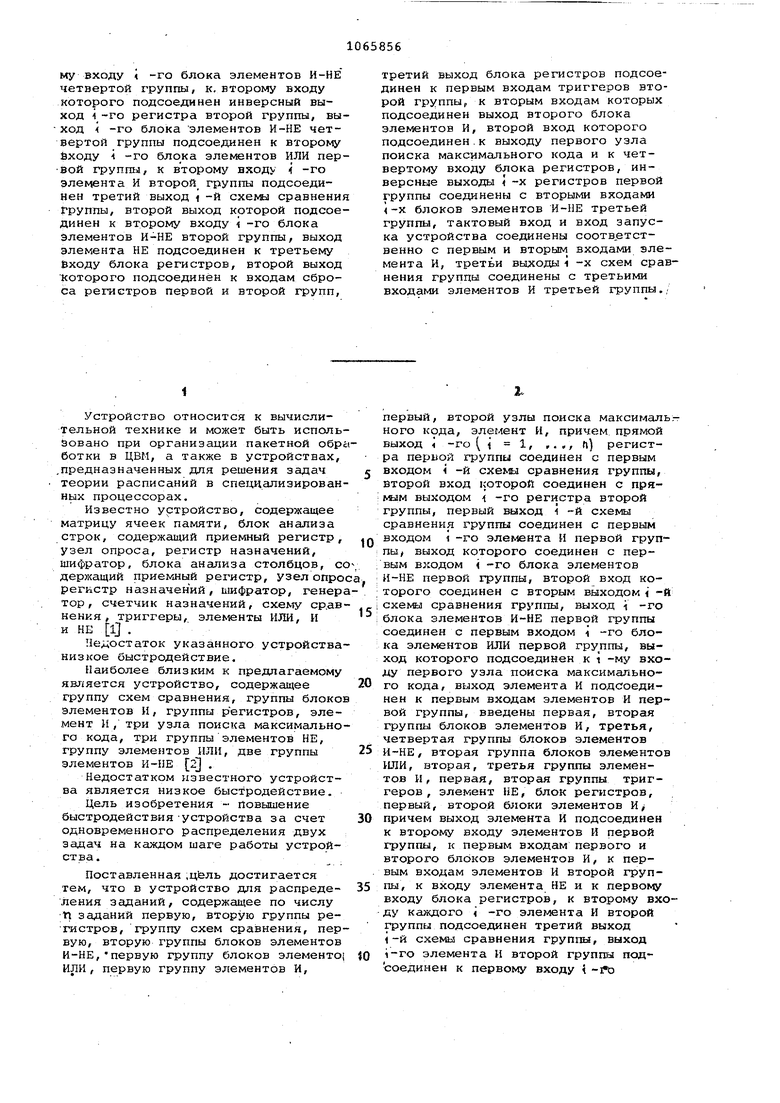

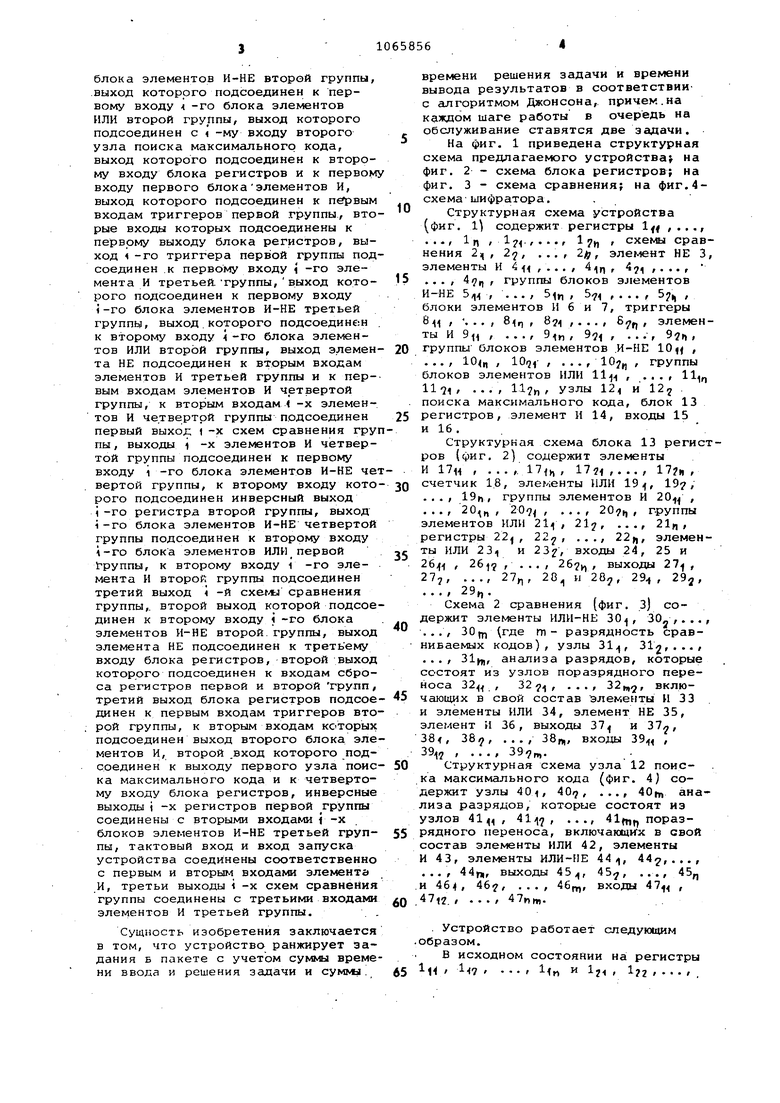

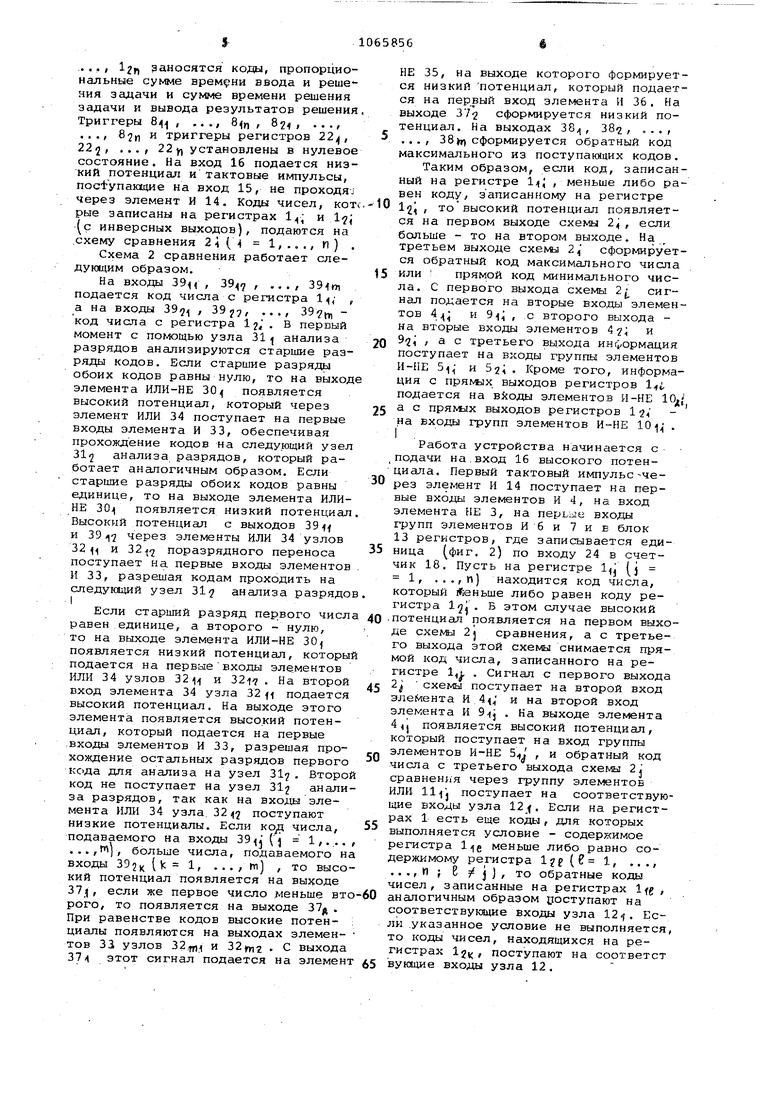

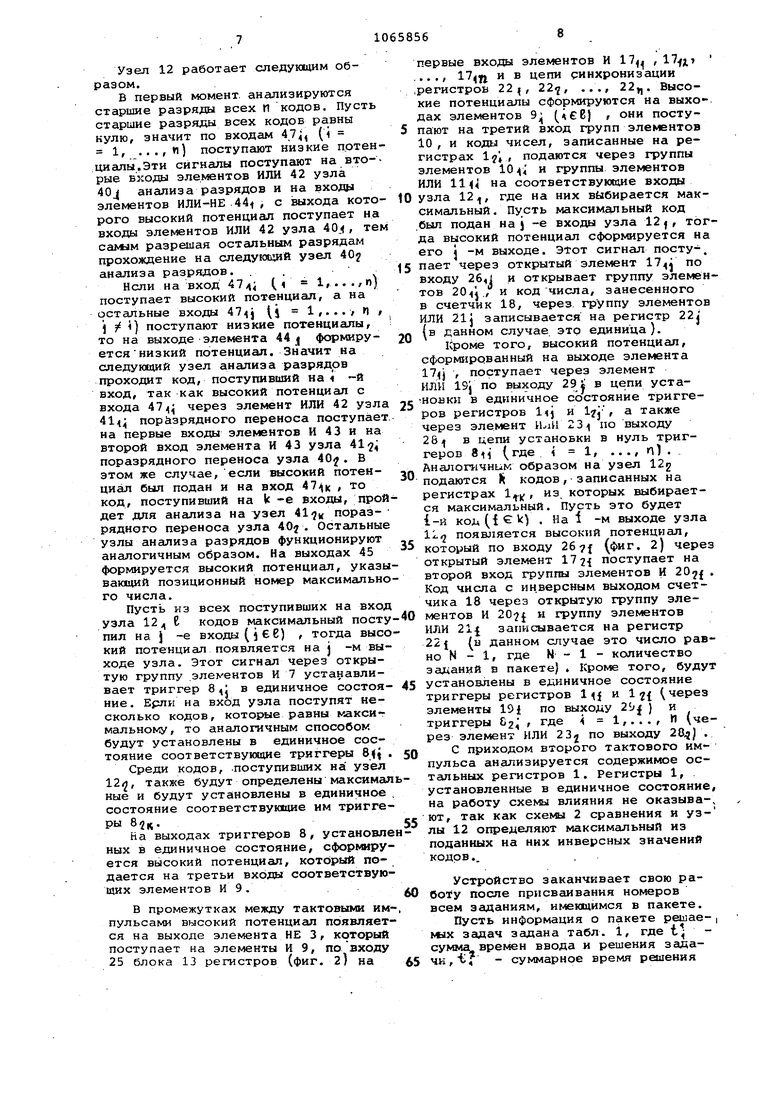

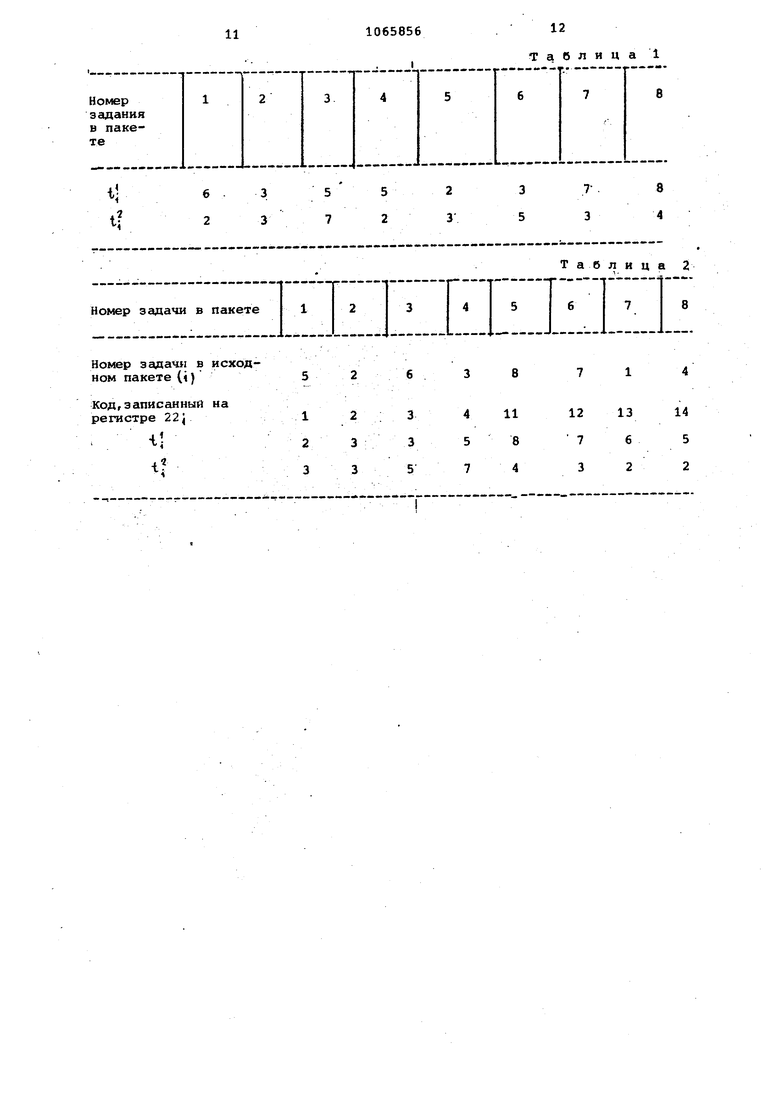

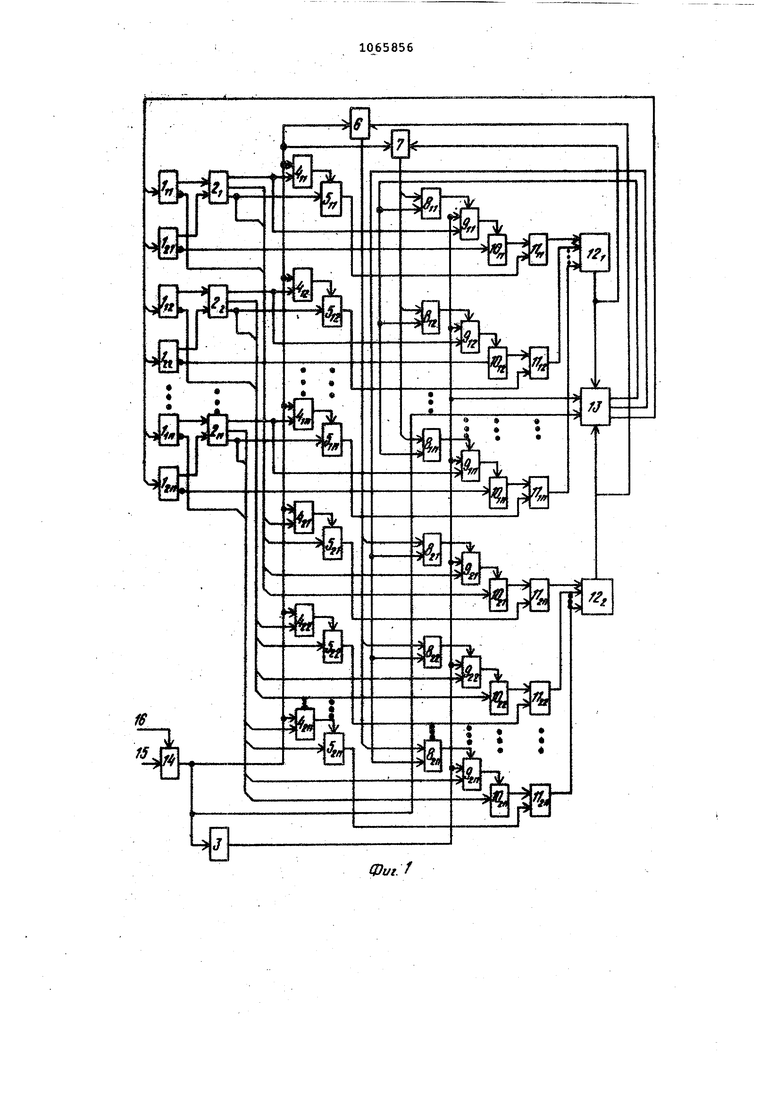

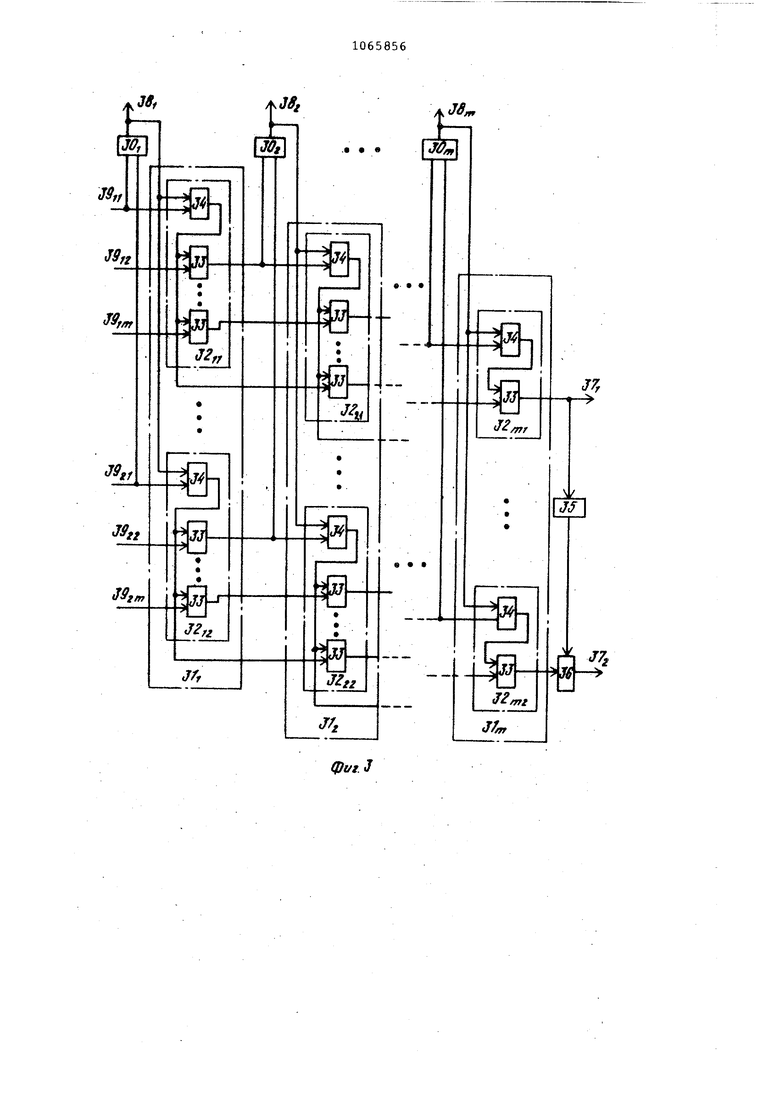

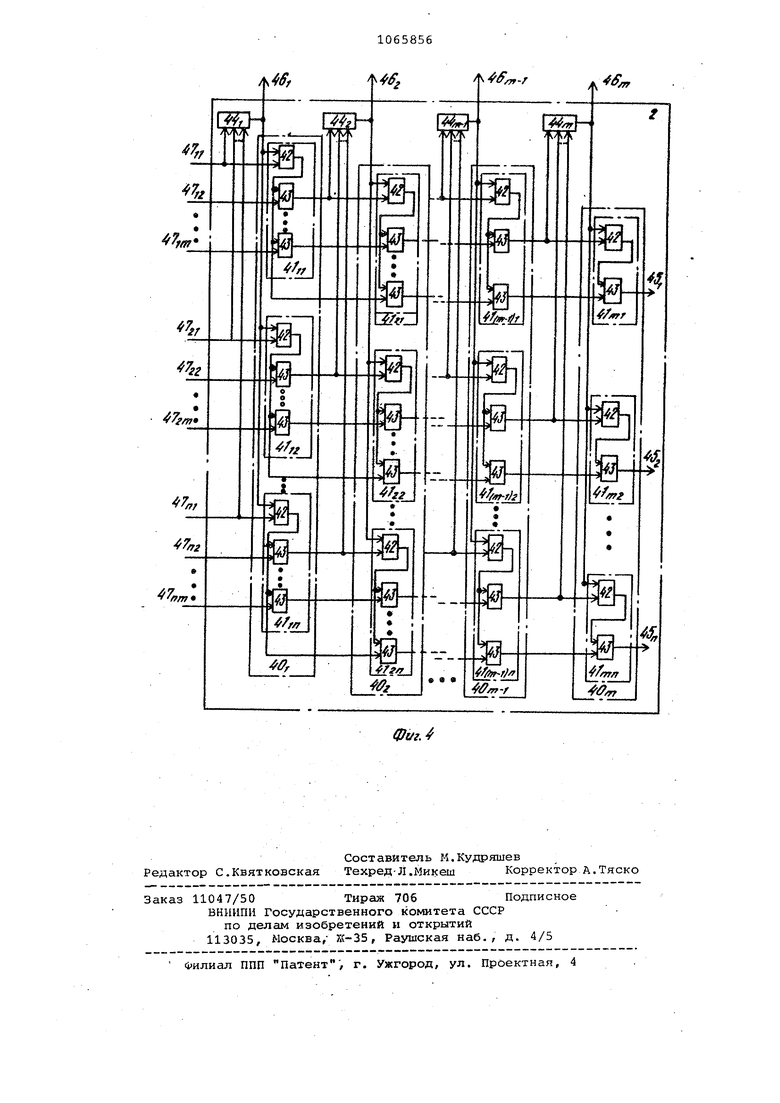

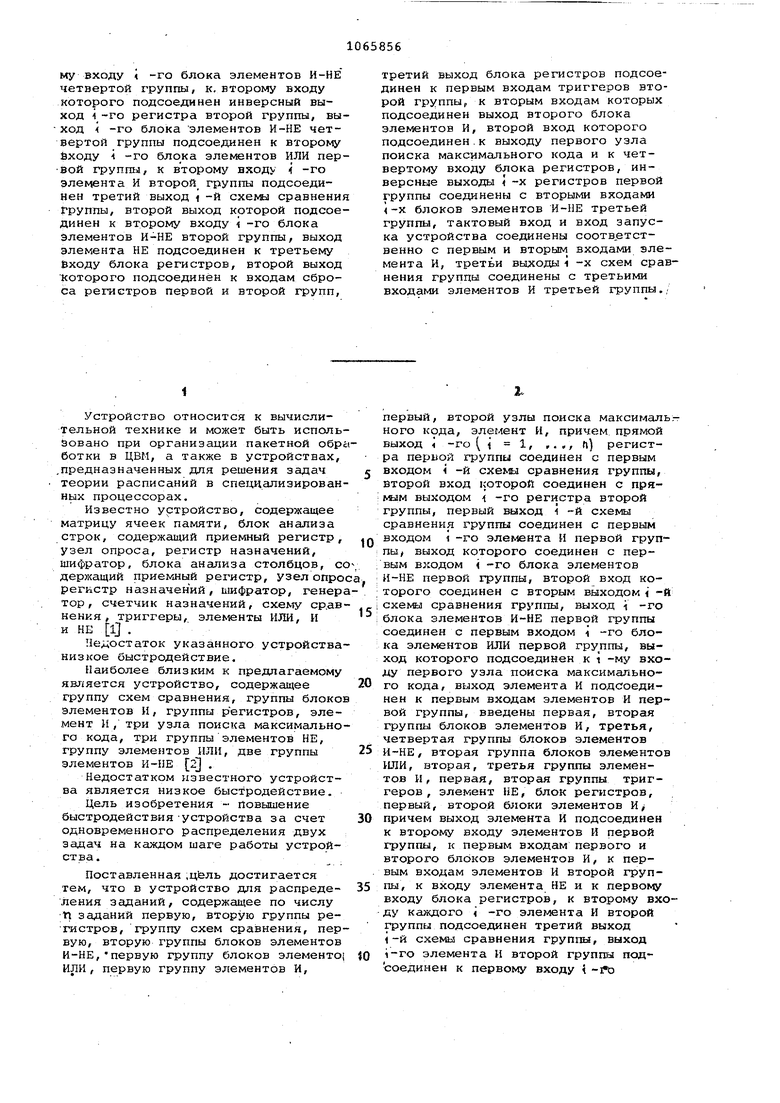

Устройство относится к вычислительной технике и может быть использовано при организации пакетной o6pc ботки в ЦВМ, а также в устройствах, .предназначенных для решения задач теории расписаний в специализирован ных процессорах. Известно устройство, содержащее матрицу ячеек памяти, блок анализа строк, содержащий приемный регистр, узел опроса, регистр назначений, шифратор, блока анализа столбцов, со держащий приемный регистр, узел опро регистр назначений, шифратор, генер тор, счетчик назначений, схему ср.ав нения, триггеры, элементы ИЛИ, И и НЕ 1 . Недостаток указанного устройстванизкое быстродействие. Наиболее близким к предлагаемому является устройство, содержшцее группу схем сравнения, группы блоков элементов И, группы регистров, элемент И , три узла поиска максимально го кода, три группы элементов НЕ, группу элементов ИЛИ, две группы элементов И-НЕ 2 . Недостатком известного устройства является низкое быстродействие. Цель изобретения - Повышение быстродействияустройства за счет одновременного распределения двух задач на каждом шаге работы устройства. Поставленная ,цёль достигается тем, что в устройство для распределения заданий, содержащее по числу П заданий первую, вторую группы регистров, группу схем сравнения, первую, вторую группы блоков элементов И-НЕ,первую группу блоков элементо| ИЛИ, первую группу элементов И, первый, второй узлы поиска максималь:ного кода, элемент И, причем прямой выход i -го ( i 1, ,.,, ft регистра первой группы соединен с первым входом -и схемл сравнения группы, второй вход которой соединен с пряMJM выходом -го регистра второй группы, первый выход i -и схемы сравнения группы соединен с первым входом 1 -го элемента И первой группы/ выход которого соединен с первым входом -го блока элементов И-НЕ первой группы, второй вход которого соединен с вторым выходом -и сравнения группы, выход i -го блока элементов И-НЕ первой группы соединен с первым входом i -го блока элементов ИЛИ первой , выход которого подсоединен к i -му входу первого узла поиска максимального кода, выход элемента И подсоединен к первым входам элементов И первой группы, введены первая, вторая группы блоков элементов И, третья, четвертая группы блоков элементов И-НЕ, вторая группа блоков элементов 1ШИ, вторая, третья группы элементов И, первая, вторая группы триггеров, элемент НЕ, блок регистров, первый, второй блоки элементов И/ причем выход элемента И подсоединен к второму входу элементов И первой rpynnfjj, к первым входам первого и второго блоков элементов И, к первым входам элементов И второй группы, к входу элемента НЕ и к первому входу блока регистров, к второму входу каждого i -го элемента И второй группы подсоединен третий выход -и схемы сравнения группы, выход i-ro элемента И второй rpynnia подсоединен к первому входу { -fo блока элементов И-НЕ второй группы, .выход которого подсоединен к первому входу ч -го блока элементов ИЛИ второй группы, выход которого подсоединен с i -му входу второго узла поиска максимального кода, выход которого подсоединен к второму входу блока регистров и к первом входу первого блокаэлементов И, выход которого подсоединен к входам триггеров первой группы, вто рые входы которых подсоединены к первому выходу блока регистров, выход 1 -го триггера первой группы под соединен .к первому входу j -го элемента И третьей, труппы, выход которого подсоединен к первому входу i-го блока элементов И-НЕ третьей группы, выход.которого подсоединен к второму входу 4-го блока элементов ИЛИ второй группы, выход элемен та НЕ подсоединен к вторым входам элементов И третьей группы и к первым входам элементов И четвертой группы, к вторым входам -х элементов И четвертой группы п.одсоединен первый выход 1 -X схем сравнения гру пы , выходы 1 -X элементов И четвертой группы подсоединен к первому входу i -го блока элементов И-НЕ че вертой группы, к второму входу кото рого подсоединен инверсный выход i-го регистра второй группы, выход i-го блока элементов И-НЕ четвертой группы подсоединен к второму входу д-го блока элементов ИЛИ первой Группы, к второму входу 1 -го элемента И второй группы подсоединен третий выход -и сравнения группы,, второй выход которой подсое динен к второму входу i -го блока элементов И-НЕ второй.группы, выход элемента НЕ подсоединен к третьему входу блока регистров, второй выход которого подсоединен к входам сброса регистров первой и второй групп, третий выход блока регистров подсое динен к первым входам триггеров вто рой группы, к вторым входам которых подсоединен выход второго блока эле ментов И, второй .вход которого подсоединен к выходу первого узла поис ка максимального кода и к четвертому входу блока регистров, инверсные выходы i -X регистров первой групгш соединены с вторыми входами f -х блоков элементов И-НЕ третьей группы, тактовый вход и вход запуска устройства соединены соответственно с первым и вторым входами элемента И, третьи выходы i -х схем сравнения группы соединены с третьими входами элементов И третьей группы, . Сущность изобретения заключается в том, что устройство ранжирует задания Б пакете с учетом сумкм време ни ввода и решения задачи и суммы. времени решения задачи и времени вывода результатов в соответствии с алгоритмом Джонсона, причем.на каждом шаге работы в очередь на обслуживание ставятся две задачи. На фиг, 1 приведена структурная схема предлагаемого ycтpoйcтвa на фиг, 2 - схема блока регистров; на фиг. 3 - схема сравнения; на фиг.4схемашифратора. Структурная схема устройства (фиг. 1 содержит регистры 1 ,..,, ..., Ifl , l v/-f 17ц t схемы сравнения 2,, 2, . .. , 2)j7, элемент НЕ 3, элементы И 4 , .. . , 4 , 471 , . .. , ., . , 4i7 , группы блоков элементов И-НЕ 5/, , . . . , , 571 t I 5,, , блоки элементов И 6 и 7, триггеры 811 / . .. , 8,, , 871 ., ь, элементы И 9,1 , . . ., 9,„ , 97 , ..., 9,, группы блоков элементов .И-НЕ 10 ) , . .. , , 10,- , . . . , 102„ , группы блоков элементов ИЛИ ll , ..., 11-21/ / / узлы 12 и 12 2 . поиска максимального кода, блок 13 регистров, элемент И 14, входы 15 и 16.. Структурная схема блока 13 регистров {фиг. 2 содержит элементы И 17ц , ...,. , 1771,..., , счетчик 1.8, элементы ИЛИ 19 , 19, ..., 19ц, группы элементов И 20 , ..., , 20 , ..., 207,,, группы элементов ИЛИ 21, 21, ..,, 21, регистры 22,, 22, ..., 22ц, элементы ИЛИ 23, и 23f, входы 24, 25 и 26;f , 26)1 , . . . , 2б7ц выходы 27 , 27,, ..., 27, 2Q и 28, 29 , 29, ..., 29,. Схема 2 сравнения (фиг. 3) содержит ИЛИ-НЕ 30, 30,..., ..., т- разрядность сравниваемых кодов), узлы 31, З,.., ..., 31, анализа разрядов, которые состоят из узлов поразрядного переноса 32, 32 , .,., 32,2/ включающих в свой состав элементы И 33 и элементы ИЛИ 34, элемент НЕ 35, элемент И 36, выходы 37 и 37, 38, 38, ..., 38п|, входы 39, , 39, , ..., 39,. Структурная схема узла 12 поиска максимального кода (фиг. 4) содержит узлы 401, 407, 40 анализа разрядов, которые состоят из узлов 411,,, 41, ..., 41fn поразрядного переноса, включающкх в свой состав элементы ИЛИ 42, элементы И 43, элементы ИЛИ-НЕ 44, 442,..., ..., 44п|, выходы 45 , 45, ..., 45„ и 4б4, 46, ..., 46f, входы 47 , irtiУстройство работает следующим бразом. В исходном состоянии на регистры И 7 f Ifn и 1 , Ij2 I , ..,, , заносятся коды, пропорциональные сумме времени ввода и решения задачи и времени решения задачи и вывода результатов решения Триггеры 8 , ,.., г 21 I ..., и триггеры регистров 22, 222 ..,, 22 У) установлены в нулевое состояние. На вход 16 подается низкий потенциал и тактовые импульсы, посФупакщие на вход 15, не пpoxoдяj через элемент И 14. Коды чисел, кот рые записаны на регистрах и с инверсных выходов), подаются на .схему сравнения 2(4 1,..., п) . Схема 2 сравнения работает следующим образом. На входы 39( , / подается код числа с регистра , а на входы 39/ , 39yj, ..., код числа с регистра 1г . в первый момент с помощью узла 31 анализа разрядов анализируются старшие разряды кодов. Бели старшие разряды обоих кодов равны нулю, то на выход элемента ИЛИ-НЕ 30 появляется высокий потенциал, который через элемент ИЛИ 34 поступает на первые входы элемента И 33, обеспечивая прохождение кодов на следукиций узел 31 анализа разрядов, который работает аналогичным образом. Если старшие разряды обоих кодов равны единице, то на выходе элемента ИЛИНЕ 30 появляется низкий потенциал Высокий потенциал с выходов и 39-Ij через элементы ИЛИ 34 узлов 32 1 и 32 поразрядного переноса поступает на первые входы элементов И 33, разрешая кодам проходить на следующий узел 31 анализа разрядо Если старший разряд первого числ равен единице, а второго - нулю, то на выходе элемента ИЛИ-НЕ 30 появляется низкий потенциал, которы подается на первыевходы элементов ИЛИ 34 узлов 321 и 3217 На второй вход элемента 34 узла 32 fi подается высокий потенциал. На выходе этого элемента появляется высокий потенциал, который подается на первые входы элементов И 33, разрешая прохождение остальных разрядов первого кода для анализа на узел 31. Второ код не поступает на узел 312 анали за разрядов, так как на входы элемента ИЛИ 34 узла 32 i(i поступают низкие потенциалы. Если числа, подаваемого на входы 39 j ( 1,. .. ...,м, больше числа, подаваемого н входы (1с 1, . .. , m , то высо кий потенциал появляется на выходе 37)( , если же первое число меньше вт рого, то появляется на выходе 37д. При равенстве кодов высокие потенциалы появляются на выходах элементов 33 узлов 32,fn,i и 32 . С выхода 37(1 этот сигнал подается на элемен НЕ 35, на выходе которого формируется низкий потенциал, который подается на первый вход элемента И 36. На выходе 37 сформируется низкий потенциал. На выходах 38, 38, ..., ..., 38) сформируется обратный код максимального из поступаквдих кодов. Таким образом, если код, записанный на регистре , меньше либо равен коду, записанному на регистре Ij , товысокий потенциал появляется на первом выходе схемы 2 , если больше - то на втором выходе. На . третьем выходе схеки сформируется обратный код максимального числа или прямой код минимального числа. С первого выхода схемы 2 сигнал подается на вторые входы элементов 4 и 9i , с второго выхода на вторые входы элементов 4, и 9-2, , а с третьего выхода информация поступает на входы группы элементов И-ПЕ 5,- и 52i . Кроме того, информация с прямых выходов регистров , подается на элементов И-НБ 10, а с прямых выходов регистров 12ч на входы групп элементов И-НЕ . Работа устройства начинается с подачи на.вход 16 высокого потенциала. Первый тактовый импульс-через элемент И 14 поступает на первые входы элементов И 4, на вход элемента НЕ 3, на перьые входы групп элементов И 6 и 7 и в блок 13 регистров, где записывается единица (фиг. 2) по входу 24 в счетчик 18. Пусть на регистре j 1, ...,n} находится код числа, который Леньше либо равен коду регистра iq, . В этом случае высокий потенциал появляется на первом выходе 2j сравнения, а с третьего выхода этой схемы снимается прямой код числа, записанного на регистре 1, . Сигнал с первого выхода 2f схемы поступает на второй вход элемента H.4i; и на второй вход элемента И 9ij . На выходе элемента появляется высокий потенциал, который поступает на вход группы элементов И-НЕ 5. , и обратный код числа с третьего выхода cxeivsj 2i сравнения через группу элементов ИЛИ 111J поступает на соответствующие входы узла . Если на регистрах 1 есть еще коды, для которых выполняется условие - содержимое регистра 1 меньше либо равно содержимому регистра , ..., ., ,,И ; В j }, то обратные коды чисел, записанные на регистрах Ifg , аналогичным образом соступают на срответствукядие входы узла 12. Если .указанное условие не выполняется, то коды чисел, находящихся на регистрах Ijj- , поступают на соответст вукадие входы узла 12. Узел 12 работает следующим образом. В первый момент анализируются старшие разряды всех И кодов. Пусть старшие разряды всех кодов равны кулю, значит по входам 47, (i 1, .,.,«) поступают низкие пртен циалы.Эти сигналы поступают на вторые Бко№ элементов ИЛИ 42 узла 40 анализа разрядов и на вкопл элементов ИЛИ-НЕ 44, с выхода кото рого высокий потенциал поступает на входы элементов ИЛИ 42 узла 40 , те самлм разрешая остальным разрядам прохождение на следукж ий узел 40 анализа разрядов. . . Ноли на вход 47 i 1,. ..,п) поступает высокий потенцигш, а на остальные входы j 1 ,. .. , Г) j j i поступают низкие потенциалы, то на выходе элемента 44j формируетсянизкий потенциал. Значит на следующий узел анализа разрядов проходит код, поступивший на -и вход, так как высокий потенциал с входа 474 через элемент ИЛИ 42 узла 41;{ порс13рядного переноса поступает на первые входы элементов И 43 и на второй вход элемента И 43 узла поразрядного переноса узла 40j. В этом же случае,если высокий потенциал был подан и на вход , то код, поступивший на k -е входы, прой дет для анализа на узел 417к поразрядного переноса узла 40j. Остальные узлы анализа разрядов функционируют аналогичным образом. На выходах 45 формируется высокий потенциал, указы вающий позиционный номер максимгшьно го числа. Пусть из всех поступивших на вход узла 12 С кодов максимальный посту пил на J -е входы (JEE) , тогда высо кий потенциал появляется на j -м выходе узла. Этот сигнс1Л через открытую группу элементов И 7 устанавливает триггер 8 : в единичное состояние. Ерли на вход узла поступят несколько кодов, равны максимальному, то аналогичным способом будут установлены в единичное состояние соответствую1цие триггеры Среди кодов, поступивших на узел 12i2, также будут определены максимсш ные и будут установлены в единичное состояние соответствующие им триггеры выходах триггеров 8, установле ных в единичное состояние, сформируется высокий потенциал, который подается на третьи входы соответствующих элементов И 9.. В промежутках между тактовыкш им пульсами высокий потенциал появляется на выходе элемента НЕ 3, который поступает на элементы И 9, по входу 25 блока 13 регистров (фиг. 2) на первые входы элементов И 17. , 17 ..., и в цепи синхронизации регистров 22i, 22, ..., 22. Высокие потенциалы сформируются на выходах элементов 9 (icB) , они поступают на третий вход групп элементов 10 , и коды чисел, записанные на регистрах Iji, подаются через группы элементов 10 и группы элементов ИЛИ 1114 на соответствуюгцие входы узла 12 , где на них выбирается максимальный. Пусть максимальный код .был подан на j -е входы узла 12 f, тогда высокий потенциал сформируется на его I -м выходе. Этот сигнал посту-. пает через открытый элемент по входу 26л и открывает группу элементов ., и код числа, занесенного в счетчик 18, через группу элементов ИЛИ 21j записывается на регистр 22j (в данном случае это единица). Кроме того, высокий потенциал, сформированный на выходе элемента 174J , поступает через элемент ИЛИ 19j по выходу 29i в цепи установки в единичное состояние триггеров регистров lij и lyj , а также через элемент 23i no выходу 2Ьц в цепи установки в нуль триггеров (где 1 1, .. ., п1 . Аналогичным образом на узел 12 подаются It кодов, записанных на регистрах l, , из которых выбирается максимальный. Пусть это будет i-й Ko(iCk) . На 1 -м выходе узла 11 появляется высокий потенциал, который по входу 267{ (фиг. 2) через открытый элемент 172i поступает на второй вход группы элементов И 202 . Код числа с инверсным выходом счетчика 18 через открытую группу элементов И 207{ и группу элементов ИЛИ 2l записывается на регистр 22J (и данном случае это число равно N - 1, где N - 1 - количество заданий в пакете) Кроме трго, будут установлены в единичное состояние триггеры регистров и I ц (через элементы 19f по выходу ) и триггеры C2i где 1,..., М (через элемент ИЛИ 232 ° выходу 28) . С приходом второго тактового импульса анализируется содержимое остальных регистров 1. Регистры 1, установленные в единичное состояние, на работу схемы влияния не оказыва-, ют, так как схеуы 2 сравнения и узлы 12 определяют максимальный из поданных на них инверсных значений кодов.. Устройство заканчивает свою рабоНу после присваивания номеров всем заданиям, имеющимся в пакете. Пусть информация о пакете решаеbtax задач задана табл. 1, где t сумма времен ввода и решения зада4H,t - суммарное время раиения

и вывода результатов решения задачи, Для обеспечения правильной работы счетчик 18 имеет разрядность.

В исходном состоянии времена занесены и. хранятся на регистрах 1,; (где ( « 1, ,.., 0, а времена t - на регистрах ij . Состояние J схем 2 сравнения следующее: высокий поте11циал появляется на втором выхо;де 2 сравнения, так как ij -tJ, на третьем выходе данной схемы - код числа 3, схема 2g сравне;ния - высокий потенцизл на первом выходе, а на третьем - код числа 3,схема 2 сравнения - высокий потен:циал на первом выходе, на третьем выходе - код числа 5 и т.д. С подачей разрешающего потенциала на вход 16 открывается элемент И 14 и первый тактовый импульс поступает на первые входы элементов И и 4 (i 1, ..., 8), блок элементов И 6 и 7. :При этом высокий потенциал появляется на выходах элементов 4 , 4, 415 и 4(6 (т.е. на выходах тех эле;ментов, на вход которых поступает высокий потенциал с первых выходов схем 2J сравнения, где j 6 {2 , 3, 5, 6 . Высокий потенциал появляется и на выходах элементов f , 4j4; и 42g. Этими сигналами открываются группы блоков элементов И-НЕ 64 5П / 5j5 , 516, , , и 52Й , Ц, коды с Т етьих выходов схем 2 сравнения через соответствуюдие группы блоков элементов И-НЕ 5 и группы блоков элементов ИЛИ 11 подаются на вход узла 12. Причем на входы узла 12 будут поданы коды времен i (i е f 2, 3, 5, 6), номера задач для которых } ё tj , а на входы узла 12 - BpeMeHatUie 1, 4, 7, 8). На вход узла 12 подаются обратные коды следукших чисел 3, 5, 2, 3. Так как, i-J 2 - минимальный код, то высокий потенциал появится на пятом выходе шифратора. Этот сигнал через группу элементов И 7 установит в единичное состояние триггер 8)5 f с выхода которого высокий потенциал подается на третий вход элемента И S 15 .

На входы узла 12 подаются обратные кода следуккдих чисел 2, 2, 3, 4. В данном случае высокие потенциалы сформируются на первом и четвертом выходах узла. Эти сигналы через группу элементов И 6 установят в единичное состояние триггеры Вг и 874 f выходов которыхвысокие потенциалы поступают на третьи входы элементов И 9у и 9 Кроме того, первый тактовый импульс записывает единицу в счетчик 18 (фиг. 2).

jjo окончании первого тактового и ульса высокий потенциал появляется на выходе элемента НЕ 3. По этому С1(гналу на входы узлов, подаются коды чисел через группы блоков элементов И-НЕ 10 и группу элементов ИЛИ (где i 1,4,5 . При этом на узел 12 подается обратный код числа tj 3, на узел 12 - обратные коды t 6HlJi 5.

Hei пятые входы узла 12 .( поступает код числа 3, на остальные входы поступают нулевые коды, тогда на пятом выходе узла появляется высокий потенциал. Этот сигнал поступает на вход 26,5- блока 13 (фиг. 2) и в регистр 22f запишется единица, это говорит о том, что пятое згщание должно быть первым выбрано для обслуживания на многопрограммный ЭВМ.

Кроме того высокий потенциал с выхода элемента И 17)5 через элемент ИЛИ 195 поступает в цепи установки в единичное состояние триггеров регистров lif и и через элемент ИЛИ 23 поступает в цепи сброса триггеров 8| (( 1, ... 8).

На первый и четвертый входы узла 12 поступают обратные коды чисел 6 и 5. Высокий потенциал сфор1умруется на четвертом выходе узла 12. Этот сигнсш поступает по входу 26/ в блок 13 регистров (фиг. 2). В результате этого в регистр 22 за пишется число 14, которое будет максимальным, это означает, что четвертая задача должна быть выбрана для обслуживания последней. Кроме того, будут установлены в единичное состояние триггеры регистров I,j4 и сброшены триггеры 8, (i 1, .. ., 8) .

,

Далее устройство работает аналогичным образом.

В результате устройство для распределения заданий преобразует исходный пакет аадач в последовательность задач, представленных в т абл. 2 .

На обслуживание задачи выбирают ся по лданимальному коду на регистрах 22.

Применение изобретения позволяет повысить быстродействие устройства.

Таблица 1

Z9i 29 фиг. I

Фиг, 4 -f

Авторы

Даты

1984-01-07—Публикация

1982-04-19—Подача