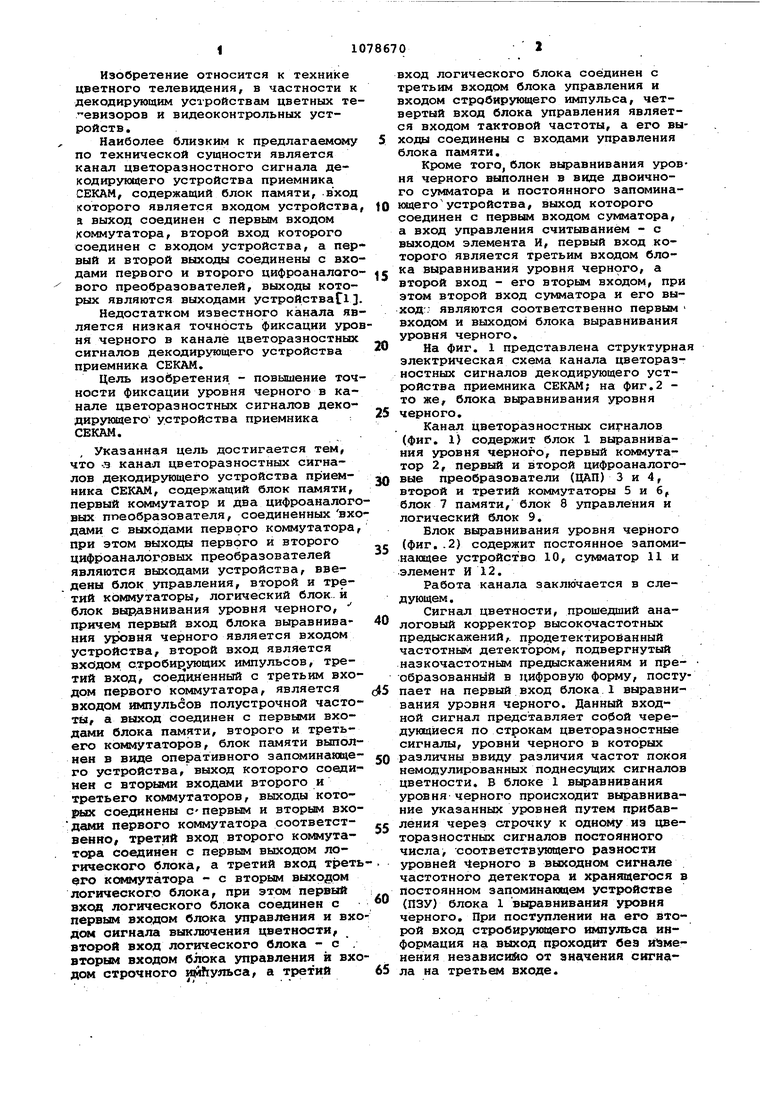

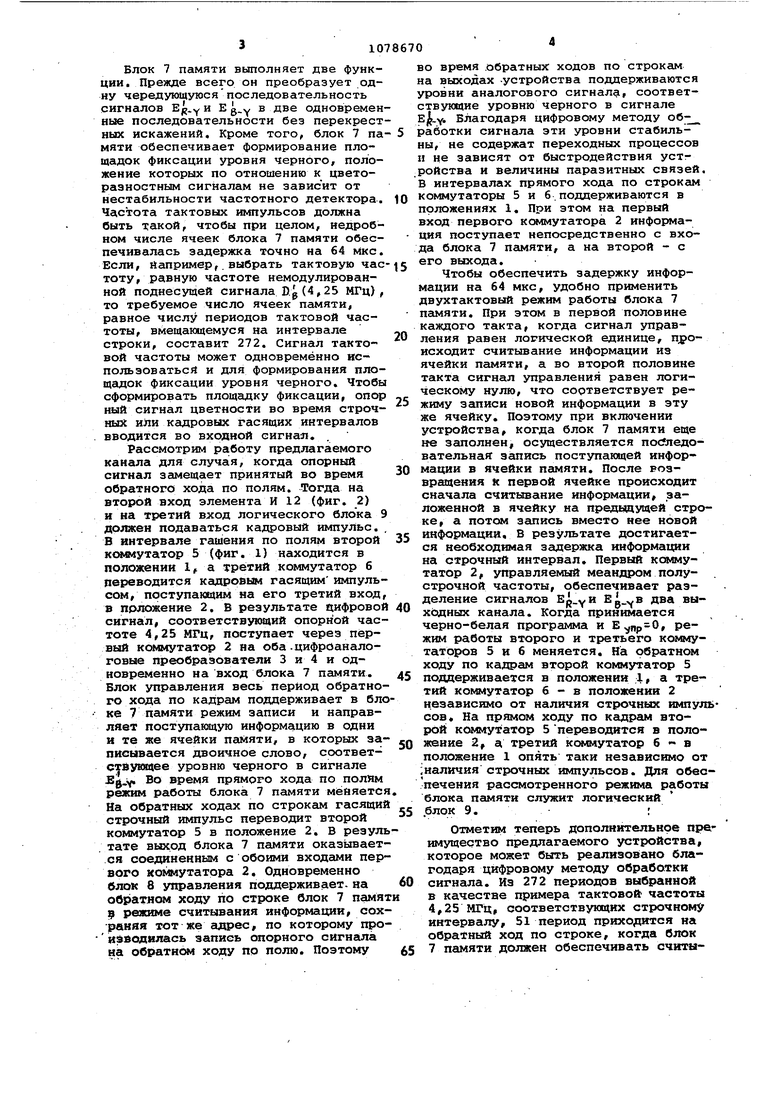

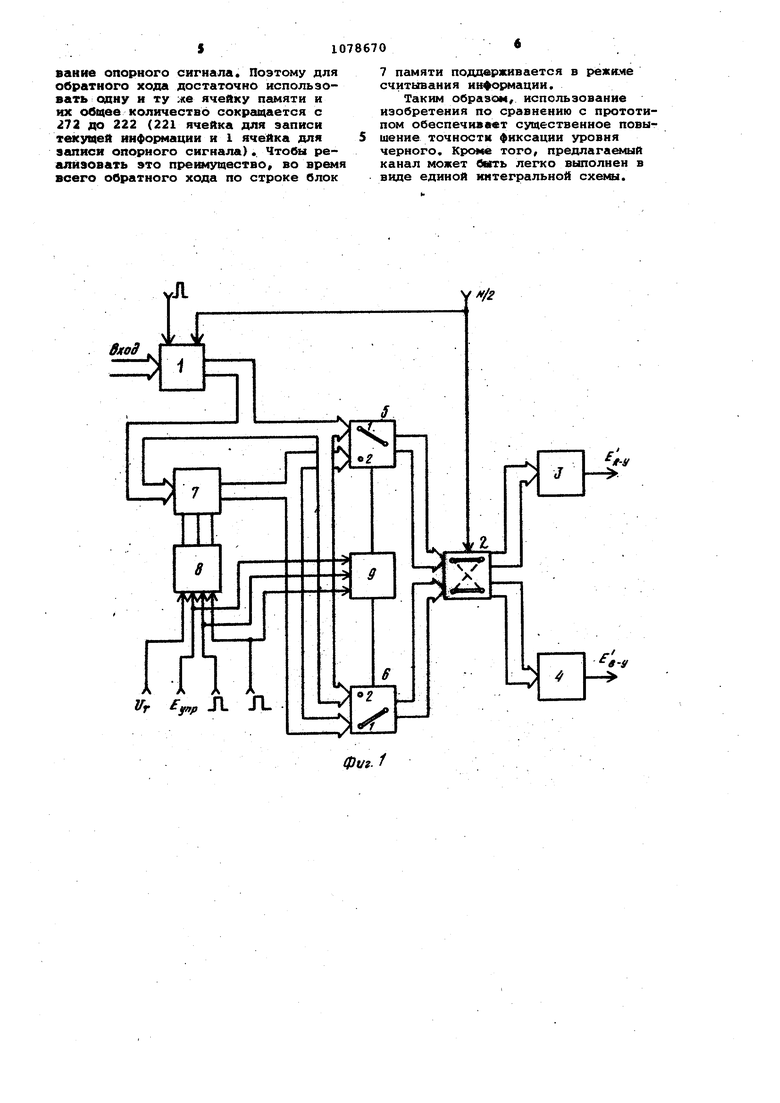

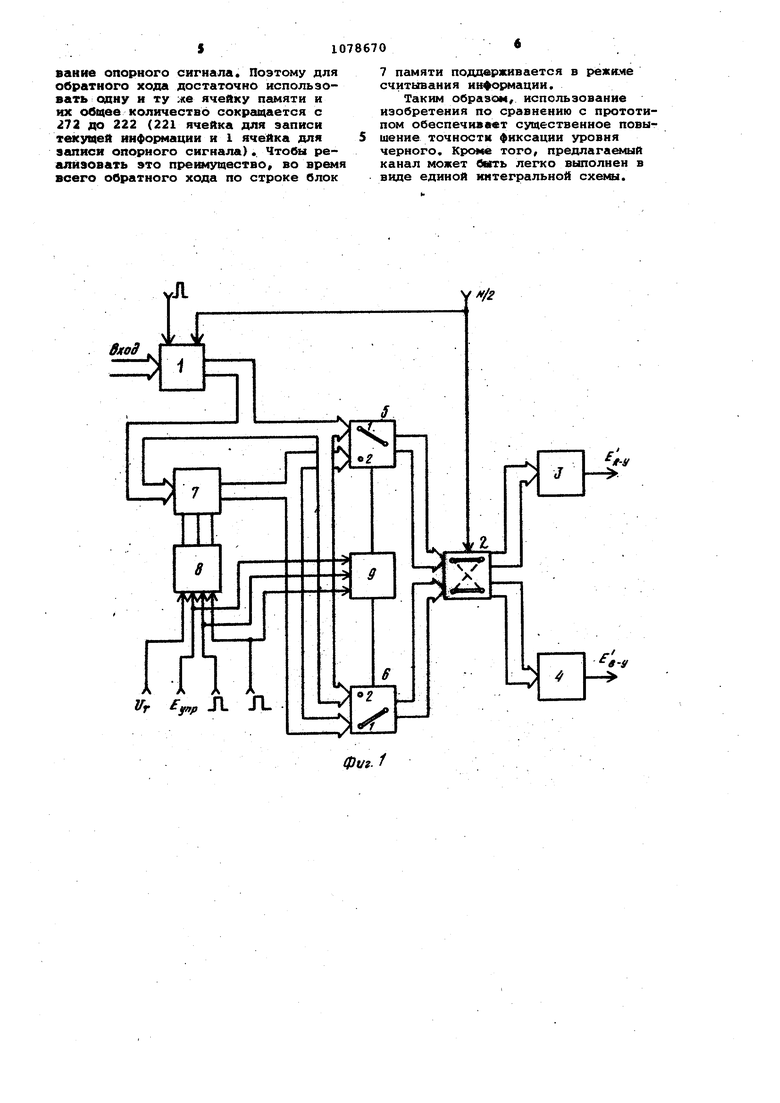

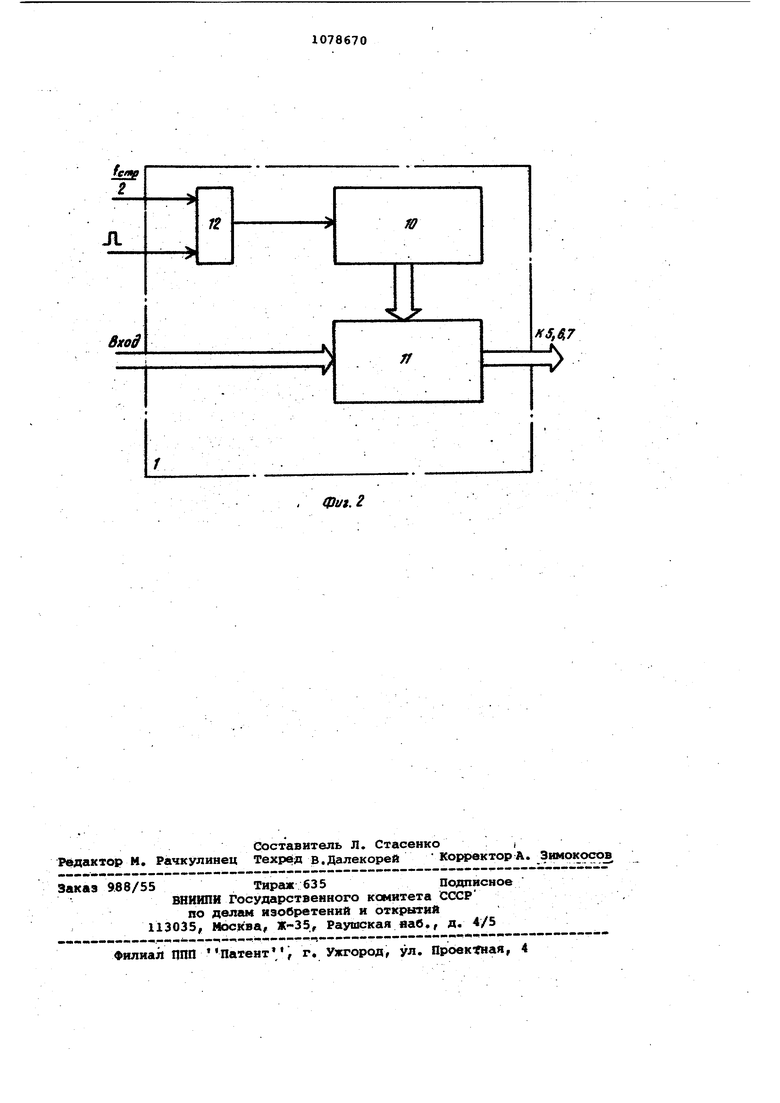

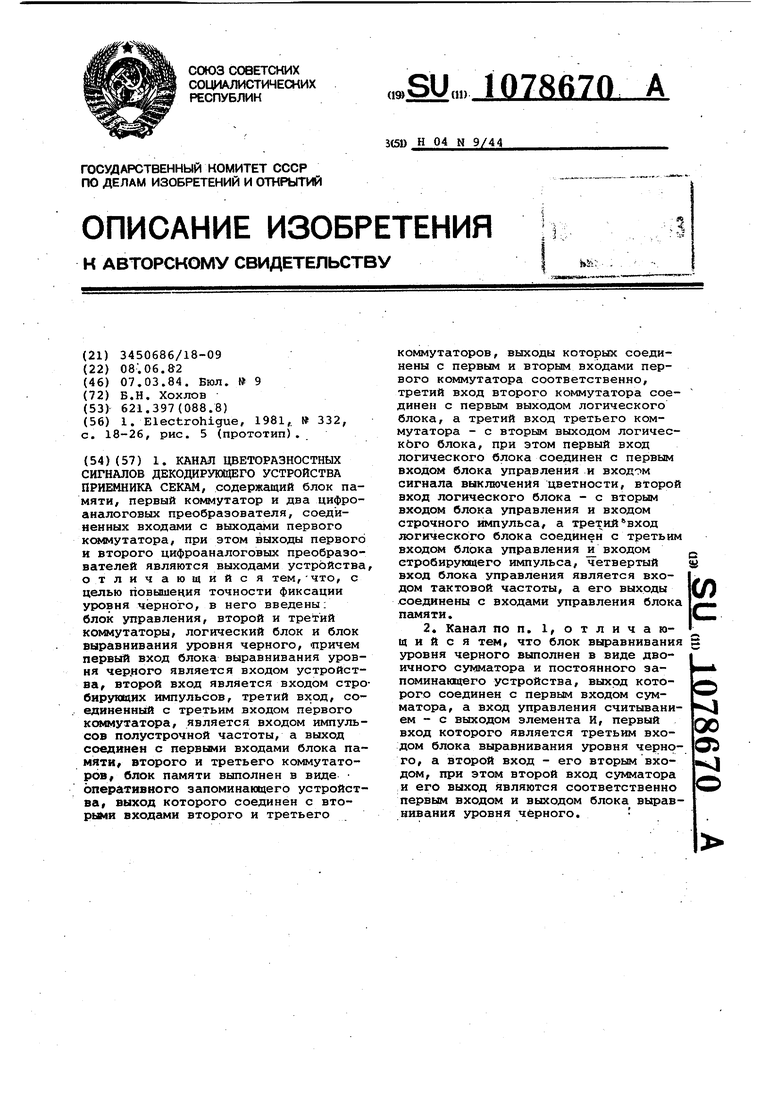

Изобретение относится к технике цветного телевидения, в частности к декодирующим устройствам цветных те евиэоров и видеоконтрольных устройств, , Наиболее близким к предлагаемому по технической сущности является канал цветоразностного сигнала декодирующего устройства приемника СЕКАМ, содержащий блок памяти, вход которого является входом устройства я выход соединен с первым входом коммутатора, второй вход которого соединен с входом устройства, а пер вый и второй выходы соединены с вхо дами первого и второго цифроаналого - вого преобразователей, выходы которых являются выходами устройства J Недостатком известного канала яв ляется низкая точность фиксации уро ня черного в канале цветоразностных сигналов декодирующего устройства приемника СБКАМ. Цель изобретения - повышение точ ности фиксации уровня черного в канале цветоразностных сигналов декодирукадего устройства приемника СЕКАМ. Указанная цель достигается тем, что -3 канал цветоразностных сигналов декодирующего устройства пр иемника СЕКАМ, содержащий блок памяти, первый коммутатор и два цифроаналого вых ппеобразователя, соединенных вхо дами с выходами первого коммутатора при этом выходы первого и второго цифроаналогрвых преобразователей являются выходами устройства, введены блок управления, второй и третий коммутаторы, логический блок.и блок вырдвнивания уровня черного, причем первый вход блока выравнивания уровня черного является входом устройства, второй вход является входом с.троби ующих импульсов, третий вход, соединенный с третьим входом первого коммутатора, является входом импульсов полустрочной частоты, а выход соединен с первыми входами блока памяти, второго и третьего коммутаторов, блок памяти выполнен в виде оперативного запоминаяяцего устройства, выход которого соединен с вторшш входами второго и третьего коммутаторов, выходы которых соединены С первым и вторым входами первого коммутатора соответствемно, третий вход второго коммутатора соединен с первым выходом логического блока, а третий вход треть его ксянмутатора - с вторым выходом логического блока, при этом первый вход, логического блока соединен с первым входом блока управления и вхо дом сигнала выключения цветности, второй вход логического блока - с . вторым входом блока управления и вхо дом строчного им гуяьса, а третий вход логического блока соединен с третьим входом блока управления и входом стрдбирующего импульса, четвертый вход блока управления является входом тактовой частоты, а его выходы соединены с входами управления блока псшяти. Кроме того, блок выравнивания уровня черного выполнен в виде двоичного сумматора и постоянного запоминающего устройства, выход которого соединен с первым входом сумматора, а вход управления считыванием - с выходом элемента И, первый вход которого является третьим входом блока выравнивания уровня черного, а второй вход - его вторым входом, при этом второй вход сумматора и его выход:; являются соответственно первым входом и выходом блока выравнивания уровня черного. На фиг, 1 представлена структурная электрическая схема канала цветоразностных сигналов декодирующего устройства приемника СЕКАМ; на фиг,2 то же, блока выравнивания уровня черного. Канал цветоразностных сигналов (фиг, 1) содержит блок 1 выравнивания уровня черного, первый коммутатор 2, первый и второй цифроаналоговые преобразователи (ЦАП) 3 и 4, второй и третий коммутаторы 5 и б, блок 7 памяти, блок 8 управления и логический блок 9, Блок выравнивания уровня черного (фиг, .2) содержит постоянное запоми.нагадее устройство 10, сумматор 11 и элемент И 12, Работа канала закл1очается в следующем. Сигнал цветности, прошедший аналоговый корректор высокочастотных предыскажений,. продетектированный частотным детектором, подвергнутый назкочастотным предыскажениям и пре- образованный в цифpoвsпo форму, поступает на первый вход блока 1 выравнивания уровня черного. Данный входной сигнал представляет собой чередующиеся по строкам цветоразностные сигналы, уровни черного в которых различны ввиду различия частот покоя немодулированных поднесущих сигналов цветности, В блоке 1 выравнивания уровня черного происходит выравнивание указанных уровней путем прибавления через строчку к однок1у из цветоразностных сигналов постоянного числа, соответствующего разности уровней верного в выходном сигнале частотного детектора и храиткегося в постоянном запоминающ устройстве (ПЗУ) блока 1 выравнивания уровня черного. При поступлении на его второй вход стробируквдего импульса информация на выход проходит без изменения независи1йо от энг чения сигнала на треть04 входе.

Блок 7 памяти выполняет две функции. Прежде всего он преобразует одну чередунмцуюсяпоследовательность сигналов Е.уИ Е g.y в две одновременные последовательности без перекрестных искажений. Кроме того, блок 7 памяти обеспечивает формирование площадок фиксации уровня черного, положение которых по отношению к цветораэиостным сигналам не зависит от нестабильности частотного детектора. Частота тактовых импульсов должна быть такой, чтобы при целом, недробном числе ячеек блока 7 памяти обеспечивалась задержка точно на 64 мкс. Если, иапример,. выбрать тактовую частоту, равную частоте немодулированной поднесущей сигнала Kg(4,25 МГц), то требуемое число ячеек памяти, равное числу периодов тактовой частоты, вмещающемуся на интервале строки, составит 272. Сигнал тактовой частоты может одновременно использоваться и для формирования площадок фиксации уровня черного. Чтобы сформировать площадку фиксации, опор ный сигнал цветности во время строчных или кадровых гасящих интервалов вводится во входной сигнал.

Рассмотрим работу предлагаемого канала для случаен, когда опорный сигнал замещает принятый во время обратного хода по полям. Тогда на второй вход элемента И 12 (фиг. 2} и на третий вход логического блока 9 должен подаваться кадровый импульс. .

8интервале гашения по полям второй коммутатор 5 (фиг. 1) находится в положении If а третий коммутатор 6 переводится кадровым гасящим импульсом, поступающим на его третий вход,

в положение 2. В результате цифровой сигнал, соответствующий опорной частоте 4,25 МГц, поступает через первый коммутатор 2 на оба.цифрОаналоговые преобразователи 3 и 4 и одновременно на вход блока 7 памяти. Блок управления весь период обратного хода по кадрам поддерживает в блоке 7 памяти режим записи и направляет поступающую информацию в одни и те же ячейки памяти, в которых записывается двоичное слово, соответствукедее уровню черного в сигнале 6-4 ° время прямого хода по полим режим работы блока 7 памяти меняется На обратных ходах по строкам гасящий строчный импульс переводит второй коммутатор 5 в положение 2. В результате выход блока 7 памяти оказывается соединенным с обоими входс1ми первого коммутатора 2, Одновременно блок 8 управления поддерживает, на обратном ходу по строке блок 7 памят

9режиме считывания информации, сохраняв тот же адрес, по которому производилась запись опорного сигнала на овратном ходу по полю. Поэтому

во время .обратных ходов по строкам на выходах -устройства поддерживаются уровни аналогового сигнала, соответствующие уровню черного в сигнале Е(.у, Благодаря цифровому методу об- работки сигнала эти уровни стабильны, не содержат переходных процессов и не зависят от быстродействия устг ройства и величины паразитных связей В интервалах прямого хода по строкам кокмутаторы 5 и 6.поддерживаются в положениях 1. При этом на первый вход первого ксилмутатора 2 информация поступает непосредственно с входа блока 7 памяти, а на второй - с его выхода.

Чтобы обеспечить задержку информации на 64 МКС, удобно применить двухтактовый режим работы блока 7 памяти. При этом в первой половине каждого такта, когда сигнал управления равен логической единице, происходит считывание информации иэ ячейки памяти, а во второй половине такта сигнал управления равен логическому нулю, что соответствует режиму записи новой информации в эту же ячейку. Поэтому при включении устройства, когда блок 7 памяти еще ае Зсшолнен, осуществляется пос5ледовательная запись поступающей информации в ячейки памяти. После возвращения к первой ячейке происходит сначала считывание информации, заложенной в ячейку на предьщущей строке, а потом запись вместо нее новой информации, В результате достигается необходимая задержка ииформащ1И на строчный интервал. Первый коммутатор 2, управляемый меанщюм полустрочной частоты, обеспечивает разделение сигналов Е.уИ два выходных канала. Когда принимается черно-белая программа и , режим работы второго и третьего коммутаторов 5 и 6 меняется. На обратном ходу по кадрам второй коммутатор 5 поддерживается в положении 1, а третий коммутатор 6 - в положении 2 независимо от наличия строчньк импулсов. На прямом ходу по кадрам второй коммутатор 5 переводится в положение 2f а третий коммутатор 6 в положение 1 опять таки независимо от ;наличия строчных импульсов. Для обеспечения рассмотренного режима работы блока пгиляти служит логический блок 9.:

Отметим теперь дополнительное примущество предлагаемого устройства, которое может быть реализовано благодаря цифровому методу обработки сигнала. Иэ 272 периодов выбранной в качестве примера тактовой частоты 4,25 МГц, соответствующих строчному интервалу, 51 период приходится на обратный ход по строке, когда блок 7 памяти должен обеспечивать считыванне опорного сигнала. Поэтому для обратного хода достаточно использовать одну и ту же ячейку памяти и их общее количество сокращается с 272 до 222 (221 ячейка для записи текущей информации и 1 ячейка для записи опорного сигнала). Чтобы реализовать это прею«ущество, во время всего обратного хода по строке блок

7 памяти поддерживается в режиме считывания и ормации.

Таким образом, использование изобретения по сравнению с прототипом обеспечивает существенное повышение точности фиксации уровня черного. того, предлагаемый канал может бить легко выполнен в виде единой интегральной схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Канал цветоразностного сигналацВЕТНОгО ТЕлЕВизиОННОгО пРиЕМНиКАСиСТЕМы CEKAM | 1979 |

|

SU832778A1 |

| Устройство цветовой синхронизации телевизионного приемника системы "СЕКАМ | 1980 |

|

SU985975A1 |

| Декодирующее устройство | 1972 |

|

SU437251A1 |

| Декодирующее устройство приемника системы СЕКАМ | 1985 |

|

SU1356264A1 |

| Стереоцветная телевизионная система | 1983 |

|

SU1188910A1 |

| Устройство для воспроизведения дополнительных цветных телевизионных изображений | 1989 |

|

SU1817257A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU333888A1 |

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1385327A1 |

| Декодирующее устройство приемника цветного телевидения системы "секам" | 1976 |

|

SU743228A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1987 |

|

SU1495845A1 |

1. КАНАЛ ЦВЕТОРАЗНОСТНЫХ СИГНАЛОВ ДЕКОДИРУЮЩЕГО УСТРОЙСТВА ПРИЕМНИКА СЕКАМ, содержащий блок памяти, первый коммутатор и два цифроаналоговых преобразователя, соединенных входами с выходами первого кс |мутатора, при этом выходы первого и второго цифроаналоговых преобразователей являются выходами устройства, отличающийся тем,что, с целью повышения точности фиксации уровня чёрного, в него введены; блок управления, второй и третий коивлутаторы, логический блок и блок выравнивания уровня черного, причем первый вход блока выравнивания уровня чер.ного является входом устройства второй вход является входом стробирунщих импульсов, третий вход, соединенный с третьим входом первого коммутатора, является входом импульсов полустрочной частоты, а выход соединен с первьши входами блока памяти второго и третьего коммутаторов/ блок памяти выполнен в виде- операфивного запоминающего устройства, выход которого соединен с вторыми входами второго и третьего коммутаторов, выходы которых соединены с первым и вторым входами первого коммутатора соответственно, третий вход второго коммутатора соединен с первым выходом логического блока, а третий вход третьего коммутатора - с вторым выходом логическЬго блока, при этом первый вход логического блока соединен с первым входом блока управления и входом сигнала выключения цветности, второй вход логического блока - с вторым входом блока управления и входом строчного импульса, а третий вход логического блока соединен с третьим входом блока управления ii входом о стробируквдего импульса, четвертый вход блока управления является вхо(Л дом тактовой частоты, а его выходы соединены с входами управления блока с памяти. 2. Канал по п. 1, отличающий с я тем, что блок выравнивания уровня черного выполнен в виде двоичного сумматора и постоянного за поминающего устройства, выход которого соединен с первым входом сум матора, а вход управления считыванием - с выходом элемента И, первый 00 вход которого является третьим вхоо: дом блока выравнивания уровня черного, а второй вход - его вторым дом, при этом второй вход сумматора и его выход являются соответственно первым входом и выходом блока выравнивания уровня чёрного.

фиг. 1

12

Л

Вход

. фиг. 2

Ю

f(S,S,7

ff

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Electrohigue, 1981, | |||

| Приспособление, обнаруживающее покушение открыть замок | 1910 |

|

SU332A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1984-03-07—Публикация

1982-06-08—Подача