00 00

ел

СА:

N5

1 1

Изобретение относится к технике телевидения и может быть использовано в устройствах коррекции телевизионных изображений.

Цель изобретения - упрощение устройства.

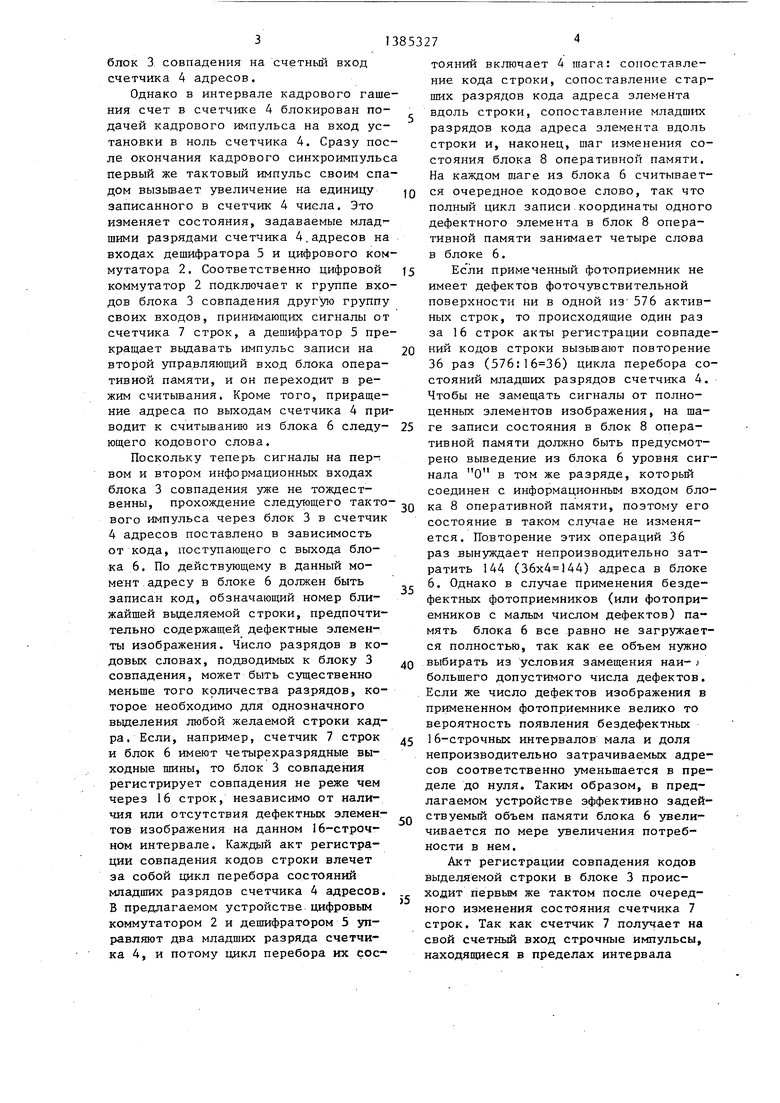

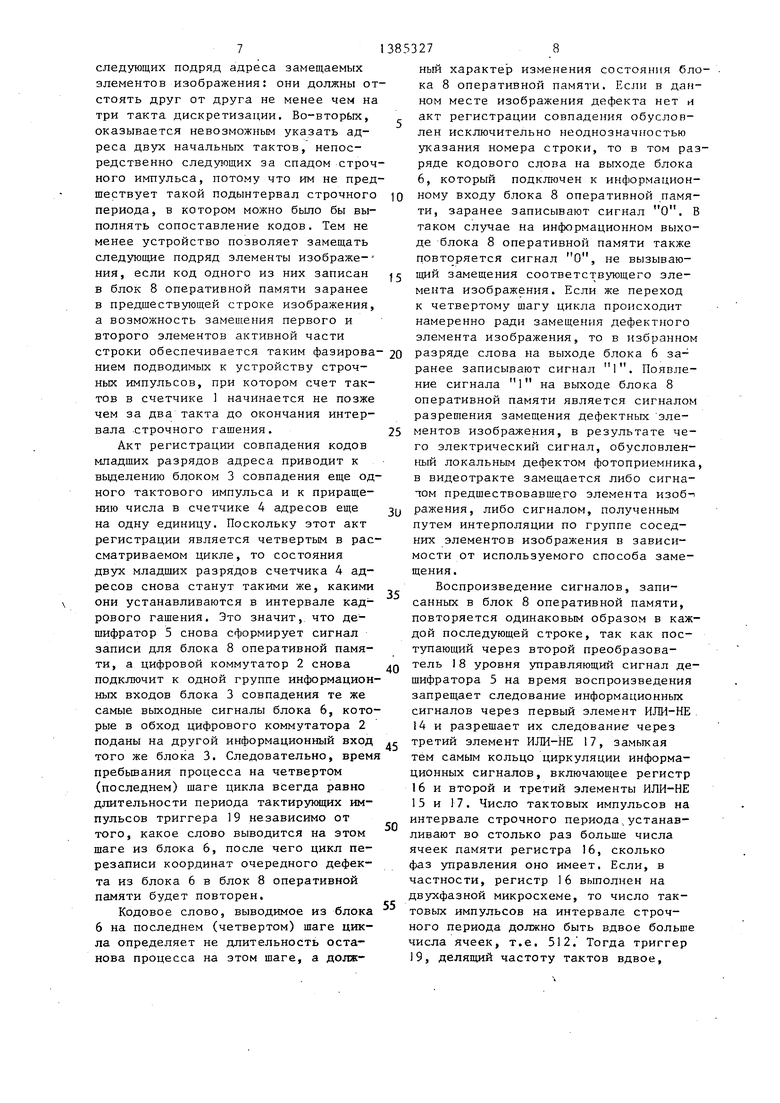

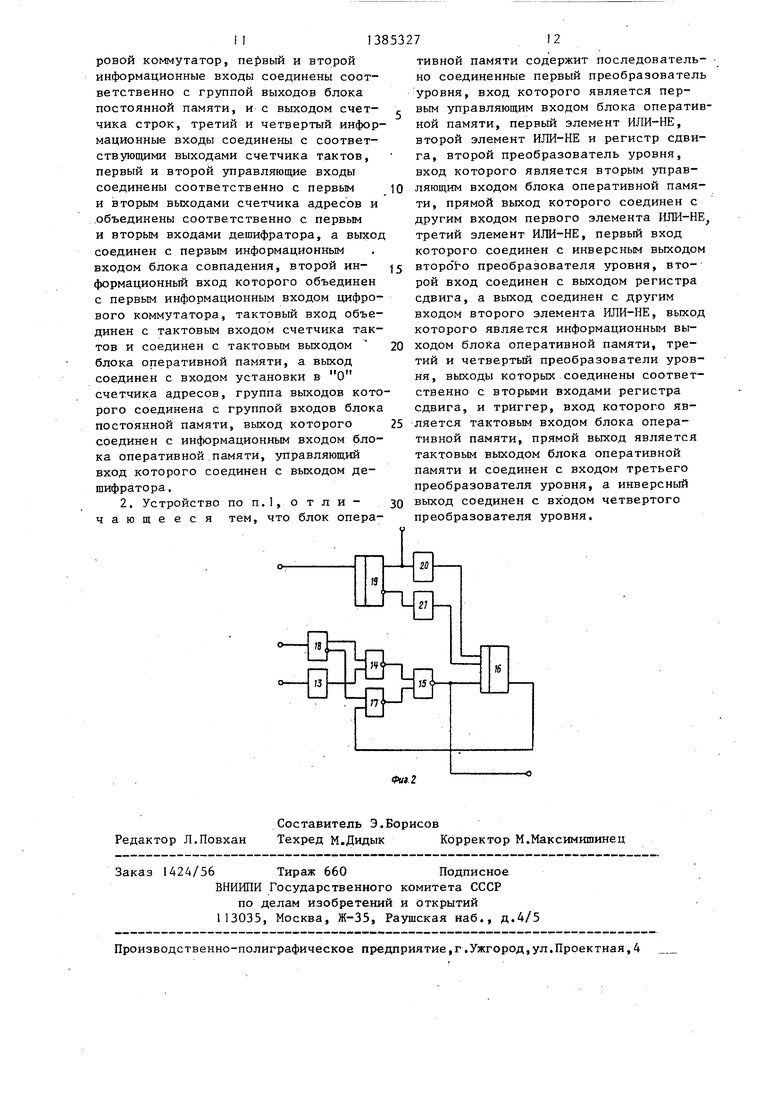

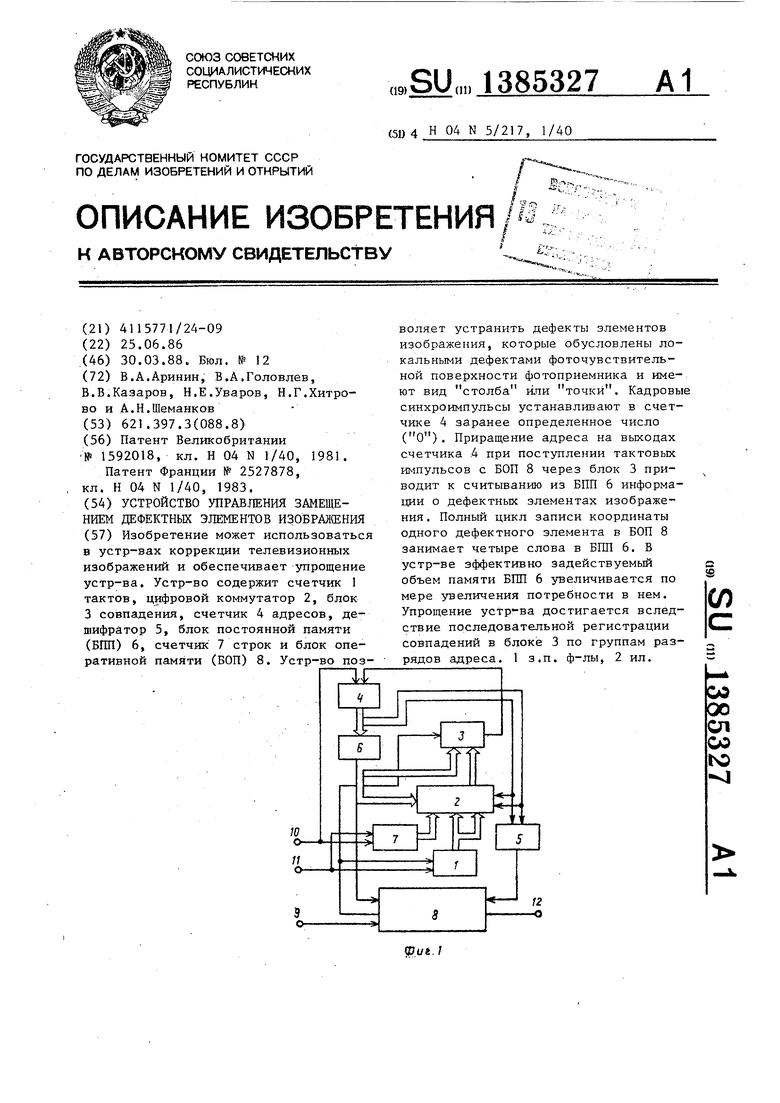

На фиг.1 представлена электрическая структурная схема устройства управления- замещением дефектных элементов изображения; на фиг.2 - блок оперативной памяти.

Устройство управления замещением дефектных элементов изображения (фиг.1) содержит счетчик 1 тактов, цифровой коммутатор 2, блок 3 совпадения, счетчик 4 адресов, дешифратор 5, блок 6 постоянной памяти,счетчик 7 строк, блок 8 оперативной памяти, вход 9 тактовых импульсов, вход 10 кадровых синхроимпульсов, вход 11 строчных синхроимпульсов, выход 12 устройства управления замещением дефектных элементов изображения.

Блок 8 оперативной памяти (фиг.2) содержит первый преобразователь 13 уровня, первый и второй элементы ИЛИ-НЕ 14 и 15, регистр 16 сдвига, третий элемент ИЛИ-НЕ 17, второй преобразователь 18 уровня, триггер 19, третий и четвертый преобразователи 20 и 21 уровня.

Устройство управления замещением дефектных элементов изображения .рабо та ет следующим образом.

Под действием кадровых синхроимпульсов, поступающих на вход 10 в ин тервалах кадрового гашения, происходит обнуление счетчика 7 и запись в счетчик 4 адресов заранее определенного числа, например нуля. Соответствующие этому числу состояния двух младщих разрядов счетчика 4 адресов приводят к формированию на выходе дешифратора 5 импульса, переводящего блок 8 оперативной памяти в режим записи. В частности, если выделению подлежат нулевые состояния младщих разрядов счетчика 4 адресов, то функция дешифратора 5 сводится к логической операции ИЛИ-НЕ.

В блоке 8 оперативной памяти (фиг.2) выходной сигнал дешифратора 5 преобразуется в два взаимно инверс ных сигнала с помощью второго преоб разователя 18 уровня. Преобразование к другим уровням не обязательно, но необходимо, если регистр 16 по уровням сигналов несовместим с микросхе

853272

мами управления. Выходные сигналы второго преобразователя 8 уровня воздействуют на первый и третий элементы ИЛИ-НЕ 14 и 17, разрешая прохожде-. ние сигналов через первый из них и запрещая - через второй. Тем самьм выходной сигнал одного из разрядов блока 6 через первый преобразо1Q ватель 13 уровня и первый и второй элементы ИЛИ-НЕ 14 и 15 начинает поступать к информационному входу регистра 16. Этот сигнал предопределен заранее, так как в интервале кадроIf вого гашения в счетчик 4 адресов за-г писано заранее определенное число, задающее конкретный адрес для блока 6, и по этому адресу в соответствующем разряде блока 6 заранее записан

20 сигнал с уровнем О. Таким образом, в интервале кадрового гащения к информационному входу регистра 16 постоянно подводится уровень О.

В то же время тактовые импульсы с

25 входа 9 продолжают переключать триггер 19, формируемые фазные напряжения, вдвое более низкой частоты, через третий и четвертый преобразова- тели 20 и 21 уровня воздействз/ют на

30 фазные входы регистра 16 и вызьтают сдвиг записанной в нем информации. Поскольку число фазных импульсов в интервале кадрового гашения заведомо превосходит число ячеек в регистре

35 16, то к концу интервала гашения

уровень О записьшается во все ячейки памяти регистра 16. Следовательно, к началу активной части кадрового периода все прежние записи в блоке 8

40 оперативной памяти оказьшаются стерты, а счетчики 4 и 7 приведены в свои исходные состояния.

Исходное состояние младщих разря- 45 дов счетчика 4 адресов передается на первый и второй управляющие входы цифрового коммутатора 2, чем задается подключение к одной группе входов блока 3 совпадений тех же самых сиг- 50 налов с выхода блока 6, которые подводятся к другой группе входов блока 3 непосредственно (т.е. в обход цифрового коммутатора 2). Вследствие тождественности сигналов на первом 55 и втором информационных входах блока 3, он регистрирует совпадение кодов независимо от состояния блока 6. Поэтому тактирующие фазные импульсы с выходов триггера 19 проходят через

3

блок 3 совпадения на счетньш вход счетчика 4 адресов.

Однако в интервале кадрового гашния счет в счетчике 4 блокирован подачей кадрового импульса на вход установки в ноль счетчика 4. Сразу поле окончания кадрового синхроимпуль первый же тактовый импульс своим спдом вызьшает увеличение на единицу записанного в счетчик 4 числа. Это изменяет состояния, задаваемые младшими разрядами счетчика 4.адресов н входах дешифратора 5 и цифрового комутатора 2. Соответственно цифровой коммутатор 2 подключает к группе вхдов блока 3 совпадения другую групп своих входов, принимающих сигналы о счетчика 7 строк, а дешифратор 5 пркращает вьщавать импульс записи на второй управляюпщй вход блока оперативной памяти, и он переходит в режим считывания. Кроме того, приращение адреса по выходам счетчика 4 прводит к считыванию из блока 6 следующего кодового слова.

Поскольку теперь сигналы на первом и втором информационных входах блока 3 совпадения уже не тождественны, прохождение следующего тактвого импульса через блок 3 в счетчи 4 адресов поставлено в зависимость от кода, поступающего с выхода блока 6. По действующему в данный момент адресу в блоке 6 должен быть записан код, обзначающий номер ближайшей выделяемой строки, предпочти тельнб содержащей дефектные элементы изображения. Число разрядов в кодовых словах, подводимых к блоку 3 совпадения, может быть существенно меньше того количества разрядов, которое необходимо для однозначного вьоделения любой желаемой строки кадра. Если, например, счетчик 7 строк и блок 6 имеют четырехразрядные выходные П1ИНЫ, то блок 3 совпадения регистрирует совпадения не реже чем через 16 строк, независимо от наличия или отсутствия дефектных элементов изображения на данном 16-строчном интервале. Каждый акт регистрации совпадения кодов строки влечет за собой цикл перебора состояний младших разрядов счетчика 4 адресов В предлагаемом ycтpoi cтвe цифровым коммутатором 2 и дешифратором 5 управляют два младших разряда счетчика 4, и потому цикл перебора их сос

10

5

з 0

0

5

0

5

0

тояний включает 4 шага: сопоставление кода строки, сопоставление старших разрядов кода адреса элемента вдоль строки, сопоставление младших разрядов кода адреса элемента вдоль строки и, наконец, шаг изменения состояния блока 8 оперативной памяти. На каждом шаге из блока б считывается очередное кодовое слово, так что полный цикл записи координаты одного дефектного элемента в блок 8 оперативной памяти занимает четыре слова в блоке 6.

Ес ли примеченный фотоприемник не имеет дефектов фоточувствительной поверхности ни в одной из 576 активных строк, то происходящие один раз за 16 строк акты регистрации совпадений кодов строки вызьшают повторение 36 раз (576:16 36) цикла перебора состояний младших разрядов счетчика 4. Чтобы не замещать сигналы от полноценных элементов изображения, на шаге записи состояния в блок 8 оперативной памяти должно быть предусмотрено выведение из блока 6 уровня сигнала О в том же разряде, который соединен с информационным входом блока 8 оперативной памяти, поэтому его состояние в таком случае не изменяется. Повторение этих операций 36 раз вынуждает непроизводительно затратить 144 () адреса в блоке 6. Однако в случае применения бездефектных фотоприемников (или фотоприемников с малым числом дефектов) память блока 6 все равно не загружается полностью, так как ее объем нужно выбирать из условия замещения наи-; большего допустимого числа дефектов. Если же число дефектов изображения в примененном фотоприемнике велико то вероятность появления бездефектных 16-строчных интервалов мала и доля непроизводительно затрачиваемых адресов соответственно уменьшается в пределе до нуля. Таким образом, в предлагаемом устройстве эффективно задей- ствуемый объем памяти блока 6 увеличивается по мере увеличения потребности в нем.

Акт регистрации совпадения кодов выделяемой строки в блоке 3 происходит первым же тактом после очередного изменения состояния счетчика 7 строк. Так как счетчик 7 получает на свой счетный вход строчные импульсы, находящиеся в пределах интервала

строчного гашения, акт регистрации совпадения кодов строки может происходить либо в первом такте активной части строки, либо за несколько тактов до ее начала,

В обоих случаях выделенный тактовый импульс через блок 3 совпадения поступает на счетный вход счетчика 4 адресов и увеличивает записанное в нем число на единицу. Тем самым начинается, второй шаг цикла. Этот шаг не регистрируется дешифратором 5, но приводит к выводу нового кодового слова из блока 6 и к переключению цифрового коммутатора 2, поэтому к входам блока 3 совпадения начинают поступать сигналы от старших разрядов -счетчика тактов. Состояния эти сигналов выражают код какого-либо одного из подынтервалов, которые все вместе составляют длительность активной части строчного периода. Если, в частности, регистрация совпадений производится группами по 4 разряда, то активная часть строки оказьюается разделенной на 16 подынтервалов по 16 тактирую цих фазных импульсов в. каждом.

В то же время на вход блока 3 сов падения выводится из блока 6 очередное кодовое слово, определяющее выбор одного из подынтервалов активной части строчного периода, причем не обязательно того, в котором находит- ся подлежаш ш замещению дефектный элемент изображения. Поскольку в данном устройстве упрощение достигается вследствие последовательной регистрации совпадений по группам разрядов адреса, постольку код старших разрядов адреса по строке, записываемый в блок 6, должен соответствовать адресу, который на две единицы меньше фактического адреса дефектного элемента изображения. Благодаря такому опережению блок 3 совпадения зарегистрирует совпадение кодов старших разрядов не позднее, чем за два тактирующих фазных импульса до момен та сканирования подлежащего замещению дефектного элемента изображения.

Акт регистрации совпадения кодов старших разрядов вызывает приращение на единицу числа в счетчике 4 адре- сов, что влечет за собой вьгеод очередного слова из блока 6 и подключе кие цифровым коммутатором 2 к входам

блока 3 совпадения следующей группы сигналов от младших разрядов счетчика 1 тактов. Код, выводимый в это время из блока 6, должен соответствовать младшим разрядам того адреса, которьй на единицу меньше фактичес- , кого адреса дефектного элемента изображения. Такое опережение позволяет закончить процедуру регистрации совпадения адресов до момента сканирования подлежащего замещению элемента изображения.

Запись заранее скорректированных кодов адреса дефекта в блоке 6 не препятствует указанию любого желаемого адреса и не вызьшает неоднозначности при его регистрации, причем это очевидно для случая замещения в подынтервале любого элемента изображения за исключением первого и второго, которым соответствуют коды младших разрядов 0000 и 0001. Для замещения первого элемента данного подынтервала в качестве кода старших разрядов надо указьшать код предшествующего подынтервала, а в качестве кода младших разрядов - число 1111, что обеспечивает завершение процедуры регистрации адресов за один такт до момента появления кода 0000 в младших разрядах счетчика 1 тактов.

Для замещения второго элемента в данном подыинтервале в качестве кода старших разрядов надо также указывать код предшествовавшего подыинтер- вала, а в качестве кода младших разрядов - число 0000. В таком случае регистрация совпадения кодов старших разрядов происходит в самом начале сканирования предшествовавшего подынтервала, когда младшие разряды счетчика 1 тактов находятся в состоянии 0000. Однако цифровой коммутатор 2 подключает, сигналы от этих разрядов к блоку 3 совпадения не в том же такте, а в следующем, когда их состояние уже изменится на 0001. Поэтому регистрация совпадения по младшим разрядам происходит не в предшествовавшем подынтервале, а в начальном такте следующего, т.е. также за один такт до момента сканирования подлежащего замещению элемента изображения.

Описанный порядок записи адресных кодов накладывает на них два ограничения. Во-первых, оказьгоается невозможным в одной строке указывать два

следующих подряд адреса замещаемых элементов изображения: они должны отстоять друг от друга не менее чем на три такта дискретизации. Во-вторЬпс, оказывается невозможным указать адреса двух начальных тактов, непосредственно следующих за спадом строчного импульса, потому что им не предшествует такой подынтервал строчного периода, в котором можно было бы выполнять сопоставление кодов. Тем не менее устройство позволяет замещать следующие подряд элементы изображе- ния, если код одного из них записан в блок 8 оперативной памяти заранее в предшествующей строке изображения, а возможность замещения первого и второго элементов активной части

ньгй характер изменения состояния блока 8 оперативной памяти. Если в данном месте изображения дефекта нет и акт регистрации совпадения обусловлен исключительно неоднозначностью указания номера строки, то в том разряде кодового слова на выходе блока 6, который подключен к информацион0 ному входу блока 8 оперативной памяти, заранее записывают сигнал О. В таком случае на информационном выходе блока 8 оперативной памяти также повторяется сигнал О, не вызываю5 щий замещения соответствующего элемента изображения. Если же переход к четвертому шагу цикла происходит намеренно ради замещения дефектного элемента изображения, то в избранном

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления замещением дефектных элементов изображения | 1986 |

|

SU1394462A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1986 |

|

SU1427412A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Устройство для цветовой коррекции кинофильмов,передаваемых по телевидению | 1984 |

|

SU1233162A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

| Устройство для отображения и редактирования информации на экране электронно-лучевой трубки | 1989 |

|

SU1695288A1 |

| Устройство компенсации сигнала царапин кинопленки | 1988 |

|

SU1536521A2 |

| Устройство для отображения информации | 1987 |

|

SU1441451A1 |

Изобретение может использоваться в устр-вах коррекции телевизионных изображений и обеспечивает упрощение устр-ва. Устр-во содержит счетчик 1 тактов, цифровой коммутатор 2, блок 3 совпадения, счетчик 4 адресов, дешифратор 5, блок постоянной памяти (БШ1) 6, счетчик 7 строк и блок оперативной памяти (БОП) 8. Устр-во позволя.ет устранить дефекты элементов изображения, которые обусловлены локальными дефектами фоточувствительной поверхности фотоприемника и имеют вид столба или точки. Кадровые синхроимпульсы устанавливают в счетчике 4 заранее определенное число (О). Приращение адреса на выходах счетчика 4 при поступлении тактовых импульсов с БОП 8 через блок 3 приводит к считыванию из БПП 6 информации о дефектных элементах изображения . Полный цикл записи координаты одного дефектного элемента в БОП 8 занимает четыре слова в БШ1 6. В устр-ве эффективно задействуемый объем памяти БПП 6 увеличивается по мере увеличения потребности в нем. Упрощение усТр-ва достигается вследствие последовательной регистрации совпадений в блоке 3 по группам разрядов адреса. 1 з.п. ф-лы, 2 ил. S (Л

строки обеспечивается таким фазирова- 20 разряде слова на выходе блока 6 за

нием подводимых к устройству строчных импульсов, при котором счет тактов в счетчике 1 начинается не позже чем за два такта до окончания интервала .строчного гашения.

Акт регистрации совпадения кодов младших разрядов адреса приводит к вьщелению блоком 3 совпадения еще одного тактового импульса и к приращению числа в счетчике 4 адресов еще на одну единицу. Поскольку этот акт регистрации является четвертым в рассматриваемом цикле, то состояния двух младших разрядов счетчика Д адресов снова станут такими же, какими они устанавливаются в интервале кадрового гашения. Это значит, что дешифратор 5 снова сформирует сигнал записи для блока 8 оперативной памяти, а цифровой коммутатор 2 снова подключит к одной группе информационных входов блока 3 совпадения те же самые выходные сигналы блока 6, которые в обход цифрового коммутатора 2 поданы на другой информационный вход того же блока 3. Следовательно, врем пребьшания процесса на четвертом (последнем) шаге цикла всегда равно длительности периода тактирующих импульсов триггера 19 независимо от того, какое слово выводится на этом шаге из блока 6, после чего цикл перезаписи координат очередного дефекта из блока 6 в блок 8 оперативной памяти будет повторен.

Кодовое слово, выводимое из блока 6 на последнем (четвертом) шаге цикла определяет не длительность останова процесса на этом шаге, а долж

5

и

5

0

0

5

ранее записывают сигнал 1 . Появление сигнала 1 на выходе блока 8 оперативной памяти является сигналом разрешения замещения дефектных элементов изображения, в результате чего электрический сигнал, обусловленный локальным дефектом фотоприемника, в видеотракте замещается либо сигна- oм предшествовавшего элемента изоб- ражения, либо сигналом, полученным путем интерполяции по группе соседних элементов изображения в зависимости от используемого способа замещения.

Воспроизведение сигналов, записанных в блок 8 оперативной памяти, повторяется одинаковым образом в каждой последующей строке, так как поступающий через второй преобразователь 18 уровня управляющий сигнал дешифратора 5 на время воспроизведения запрещает следование информационных сигналов через первый элемент ИЛИ-НЕ

14и разрешает их следование через третий элемент ИЛИ-НЕ 17, замыкая тем самым кольцо циркуляции информационных сигналов, включающее регистр 16 и второй и третий элементы ИЛИ-НЕ

15и 17. Число тактовых импульсов на интервале строчного периода,устанавливают во столько раз больше числа ячеек памяти регистра 16, сколько фаз управления оно имеет. Если, в частности, регистр 16 выполнен на двухфазной микросхеме, то число тактовых импульсов на интервале строчного периода должно быть вдвое больше числа ячеек, т.е. 512, Тогда триггер 19, делящий частоту тактов вдвое.

сформирует точно 256 фазных импульсов на интервале строчного периода, вследствие чего фаза циркуляции информационных записей в кольце из регистра 16 и второго и третьего элементов И-НЕ 15 и 17 сохраняется неизменно й в каждой последующей строке. Поэтому в результате однократной записи 1 в одну из ячеек блока 8 оператив- 10 ой памяти замещается не только деектный элемент изображения в той троке, в которой запись произведена, о и элементы изображения во всех слеующих строках, имеющие такой жeaдpect5 по горизонтали. Все замещаемые.элементы вместе составляют столбец, начинащийся в той точке растра, где произведена запись в блок 8 оперативной памяти, и продолжающийся до нижней 20 кромки растра. Именно такое расположение типично для дефектов типа столб в твердотельных фотоприемниках, причем направленность столбов к нилсней кромке растра принципиально 25 обусловлена направлением перемещения фотогенерированных зарядов по поверхности фотоприемника, которое, в свою .очередь, задано стандартизованным порядком разложения изображения, Следо- 30 вательно, для замещения дефектов типа столб в предлагаемом устройстве достаточно выполнить один акт перезаписи из блока 6 в блок 8 оперативной памяти, затратив на это. 4 четырех- -зг разрядных кодовых слова или 4 адреса в блоке 6 форматом .

Если локальный дефект фотоприемника не препятствует перемещению фотогенерированных зарядов, то он прояв- 40 ляется на изображении не в виде черного столба, а в виде точки (черной или белой). Чтобы уменьшить субъективную заметность выполненного замещения таких дефектов, желательно д не замещать весь следующий за ними столбец элементов. Для этого ранее записанную в блок 8 оперативной памяти 1 необходимо стереть в одной из ближайщих последующих строк. Опера- CQ ция стирания производится в предлагаемом устройстве подобно операции записи с той лишь разницей, что на четвертом шаге цикла записи по избранному разряду блока 6, соединенному с информационным входом блока 8 оперативной памяти, выводится не сигнал I, а сигнал О. При необходимости выполнения стирания затраты памяти

55

5 0 5 0 г

0 Q

5

на замещение одного дефектного элемента изображения увеличиваются вдвое, т.е. до 8 четырехразрядных слов или до 8 адресов четырехразрядного блока 6 постоянной памяти. Следовательно, блок 6 постоянной памяти, обладающий минимальным объемом памяти (256 слов по 4 разряда), способен обеспечить замещение двух дефектов типа столб и до 30 дефектов типа точка, что примерно соответствует показателю годности выпускаемых твердотельных фотоприемников.

Сопоставление текущих адресов с адресными кодами, хранимыми в блоке 6, производится последовательно грзш- пами разрядов неполного формата в течение активной части строчного периода. Это позволяет строить блок 8 оперативной памяти на сдвиговых регистрах, в том числе с использованием элементов матричного фотоприемника телевизионной системы вместе со средствами его импульсного обеспечения без нарушения исполнения ими своей основной функции - формирования сигнала изображения. Это позволяет избежать применения полноразрядных схем процессирования адресных кодов, а также вьтолнить регистрацию разных адресных кодов с помощью одной и той же совокупности элементов. Все три отмеченных фактора ведут к сокращению объема оборудования и к упрощению устройства. Формула изобретения

1, Устройство управления замещением дефектных элементов изображения, содержащее счетчик адресов, информационный вход которого является входом кадровых синхроимпульсов, счетчик строк, информационный вход которого является входом строчных синхроимпульсов, а вход установки в О объединен с информационным входом счетчика адресов, блок оперативной памяти, тактовым вход которого является вход тактовых импульсов, а информационный выход является выходом устройства управления замещением дефектных элементов изображения, а также блок постоянной памяти, блок совпадения, дешифратор и счетчик тактов, установочный вход которого соединен с информационным входом счетчика строк, отличающееся тем, что, с целью упрощения, введен цифФаг. 2

| Патент Великобритании № 1592018, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| ПНЕВМАТИЧЕСКАЯ ШИНА ТРАНСПОРТНОГО СРЕДСТВА | 2011 |

|

RU2527878C1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-03-30—Публикация

1986-06-25—Подача