ки соединен с выходом измерителя среднего значения периода сигнала, вход которого соединен с сигнальным

и кольцевого пересчетного блока соединены с выходными клеммами генератора стробирующик сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР ОГИБАЮЩЕЙ СИГНАЛА ТРЕХФАЗНОЙ СЕТИ | 1989 |

|

RU2046356C1 |

| Цифровой измеритель фазовых флуктуаций сигналов | 1986 |

|

SU1368805A1 |

| Цифровой измеритель характеристик фазовых флуктуаций | 1981 |

|

SU993148A1 |

| Цифровой компенсационный фазометр | 1980 |

|

SU920563A1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ФАЗОВЫХ ФЛЮКТУАЦИЙ | 1991 |

|

RU2023272C1 |

| Устройство для геоэлектроразведки | 1982 |

|

SU1045192A1 |

| Автоматический измеритель параметров радиотехнических элементов и устройств | 1987 |

|

SU1681278A1 |

| Цифровой фазометр | 1976 |

|

SU664120A1 |

| Устройство для измерения расстояния до места повреждения проводов и кабелей | 1982 |

|

SU1081571A1 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ФОРМЫ ОДНОКРАТНЫХ ОПТИЧЕСКИХ И ЭЛЕКТРИЧЕСКИХ ИМПУЛЬСНЫХ СИГНАЛОВ | 1995 |

|

RU2100815C1 |

1. ИЗМЕРИТЕЛЬ ФАЗОВШ; ФЛУКТУАЦИИ СИГНАЛОЕГ, содержапцй первый и второй масштабно-временные преобразователи, фазоизмерительный блок, генератор считывакщих сигналов, генератор стробирующих сигналов, ;причем выходы масштабно-временных преобразователей соединены с входами фазоизмерительного блока, сигнальный вход генератора стробирукнцих сигналов соединен с входом первого масштабно-временного преобразователя, выхо генераторе считывающих сигналов Соединены с входами считывания масштабно-временных щ}еобразова-. телей, выходы генератора стробирующих сигналов соединены; со стробирзгнщиг ми входами масштабно-временных преобразователей, отличающийс я тем, что, с целью повышения точности измерения в широком частотном диапазоне, в него введен блок обработки результатов измере НИИ, а входы масштабно-временных преобразователей соединены между собой и с входной клеммой измерителя, выход фазоизмерительного блока соединен с входом блока обработки результатов измерения, вход опорного сигнала генератора стробирующих :сигналов и вход генератора считывающих сигналов соединены с входной клеммой опорного сигнала. «И. Измеритель по п.1, о т л ич а ю щ и и с я тем, что генератор стробирующих сигналов содержит перйый и второй делители частоты,фор мироватёль коротких импульсой зйё(Л .мент ИЛИ, измеритель среднего Значения периода сигнала, управляе|Мую линию задержки , первый и второй элементы И, инвертор, кольцевой ;Пересчетный блок и триггер, причем |вход первого делителя частоты роеди|нен с входом генератора считывающих :импульсов и входной клеммой опорного :сигнала, с выходом первого-делителя 00 |частоты последовательно соединены формирователь коротких импульсов, ел ел элемент ИЛИ, упдавляемаялиния задержки, второй делитель частоты, ин00 вертор и первый элемент И, выход первого элемента И соединен с вторым входом элемента ШШ, вход триггера соединен с выходом первого делителя частоты, первый вход второго элемента И соединен с .выходом второго делителя частоты, а вторые входы обоих элементов И соединены с выходом управляемой линии и входом кольцевого пересчетного

1

Изобретение относится к измерительной технике и может быть использовано при измерении фазовых и частотных флуктуации сигналов.

Известно устройство для измерения фазовых флуктуации сигналов путем сравнения частоты исследуемого сигнала с частотой опорного сигнала с помощью фазового детектора или электронно-счетного частотомера lj .

Однако известное устройство от- личается недостаточно высокой точностью, так как для их реализации в диапазоне частот исследуемого сигнала необходим перестраиваемый в таком же диапазоне опорный генератор стабильность которого значительно хуже стабильности кварцевых генераторов фиксированных частот.

Наиболее близким к изобретению по технической сущности является фазометр, содержащий первый и второй масштабно-временные преобразователи, генератор стробирующего сигнала, генератор считывающего сигнала, фазоизмерительный блок, арифметический блок, блок управления, цифровой отсчетйый блок, формирователь импульсов , причем входы обоих масштабно-временных преобразователей соединены с входными клеммами исследуемого и опорного сигнала соответственно, выходы масштабно-временных преобразователей соединены с входами фазоизмерительного блока, выход,которого соединен с входом арифметического блока, выходы последнего соединены с входами цифрового отсчетного блока и блока управления, выходы блока управления соединены с входами генератора стробирующих сигналов, выходы генератора считывающих сигналов соединены с входами считывания масштабно-временных преобразователей, сигнальный вход генера-тора считывающих сигналов соединен

с входной клеммой исследуемого сигнала, выходы генератора стробирующих сигналов соединены со стробирующими входами масштабно-временных преобразователей, вход формирователя импульсов соединен с входной клеммой исследуемого сигнал, и выход - с вторым входом блока управления 1.2J .

При измерении фазовых флуктуации в диапазоне частот исследуемого сигнала известным фазометром необходим перестраиваемый опорный генератор, с таким же частотным диапазоном. В генераторах с широкой полосой перестройки флуктуации, возникающие благодаря наличию цепей перестройки, снижают точность измерений.

Цель изобретения - повышение точное ти измерения в широком частотном диапа зоне.

Поставленная цель достигается тем, что в измеритель фазовых флуктуации, содержащий первый и второй масштабно-временные преобразователи фазоизмерительный блок, генератор считываюшр х сигналов, генератор стробирую11Ц1х сигналов, причем выходы масштабно-временных преобразователей соединены с входами фазоизмерительного блока, сигнальный вход генератора стробирующих сигналов соединен с входом первого масштабно-временного преобразователя, выходы генератора считывающих сигналов соединены с входом считьюания масштабно-временных преобразователей, выходы генератора стробирующих сигналов соединены с стробирующими входами масштабно-временных преобразователей, введен блок обработки результатов измерений, а входы масштабно-временньк преобразователей соединены между собой и с входной клеммой измерителя, выход фазоизмерительно,го блока соединен с входом блока обработки результатов измерения,вход

опорного сигнала генератора стробирующих сигналов и вход генератора считывающих сигналов соединены с входной клеммой опорного сигнала.

Генератор стробирующих сигналов содержит первый и второй делители частоты, формирователь коротких импульсов, элемент ИЛИ, измеритель среднего значения периода сигнала, управляемую линию задержки, первый и второй элементы И, инвертор,кольцевой пересчетный блок и триггер, причем вход первого делителя частоты соединён с генератором счетных импульсов и входной клеммой опорног сигнала, с выходом первого делителя частоты последовательно соединены формирователь коротких импульсов, элемент ИЛИ, управляемая линия задержки, второй делитель частоты, инвертор и первый элемент И, выход первого элемента И соединен с вторы входом элемента ИЛИ, вход триггера соединен с выходом первого делителя частоты, первый вход второго элемен та И соединен с выходом второго делителя частоты, а вторые входы обоих элементов И соединены с выходом управляемой линии задержки и входом кольцевого пересчетного блок управляющий вход линии задержки сое динен с выходом измерителя среднего значения периода сигнала, вход которого соединен с сигнальным входом генератора, выходы триггера и кольцевого пересчетного блока соединены с выходнымиКлеммами генератора стробирующих сигналов.

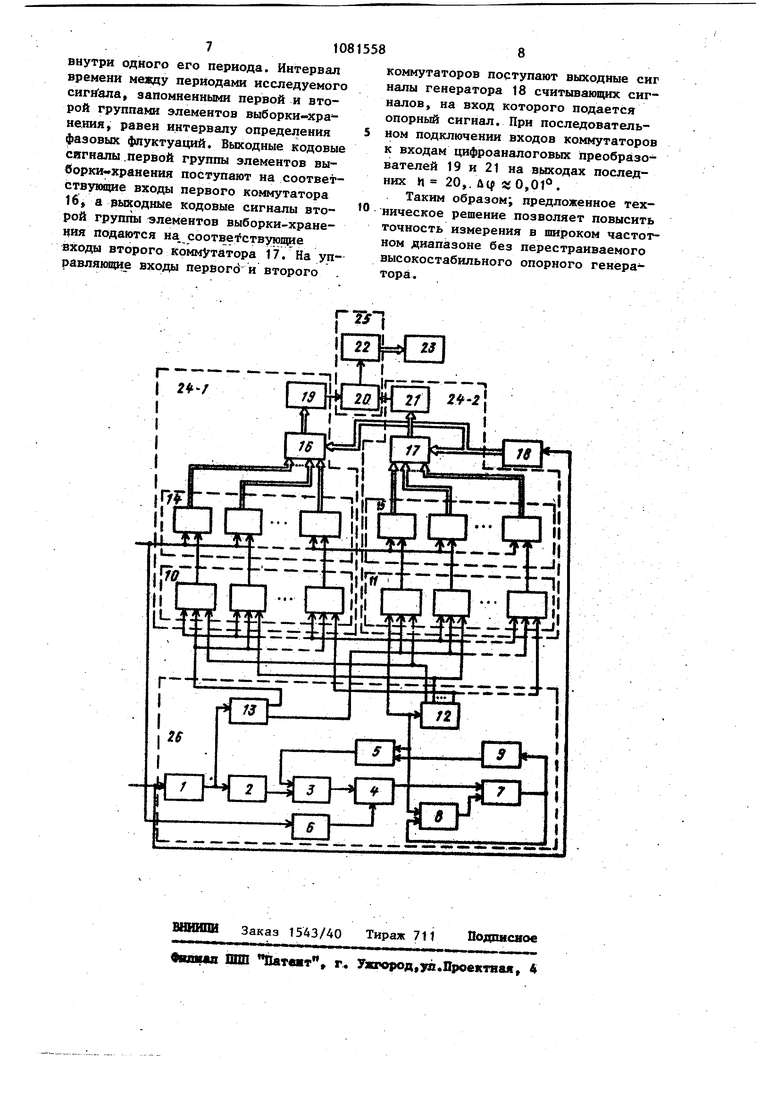

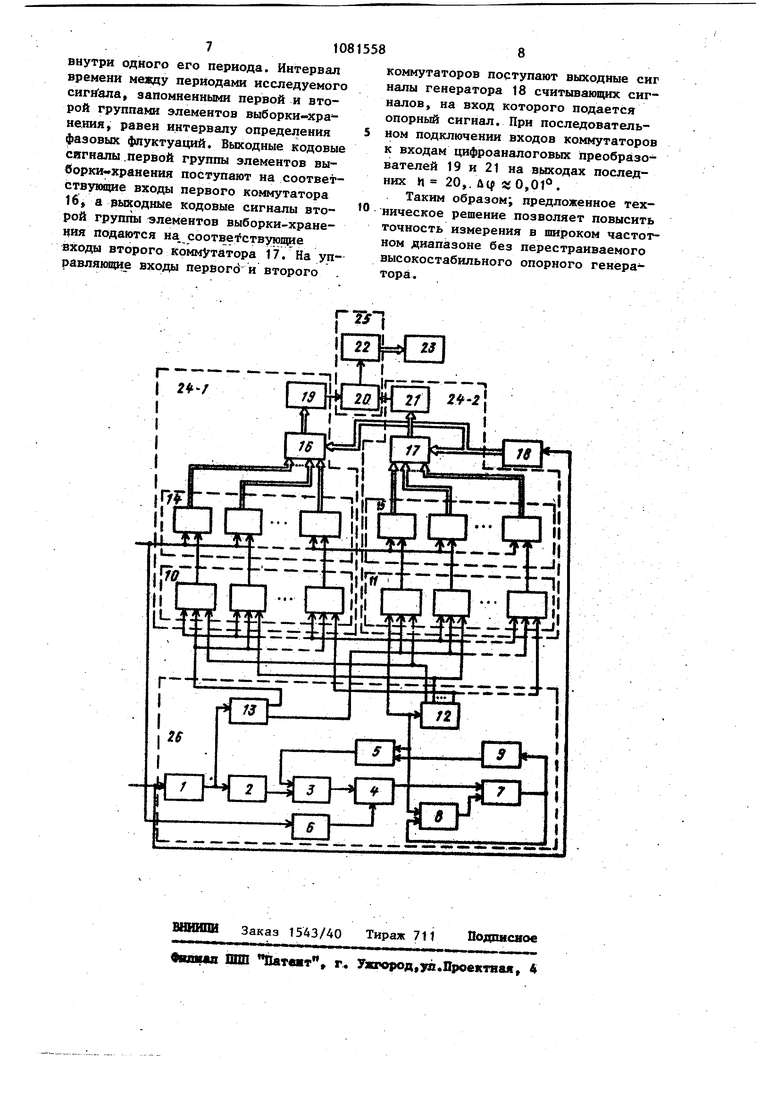

На чертеже приведена .структурная схема устройства.

Устройство содержит первый делитель 1. частоты, формирователь 2 коротких импульсов, элемент 3 ИЛИ, уйравляемую линию 4 задержки первый элемент 5 И, измеритель 6.среднего значения периода сигнала,второй делитель 7 частоты, второй элемент 8 И, инвертор 9, блоки 10 и 11 элементов И, кольцевой.пересчетный блок 12, триггер 13, блоки 14 и 15 элементов выборки-хранения, коммутаторы 16 и 17, генератор 18 считывающих сигналов, первый цифроаналоговый преобразователь 19, фазовый детектор 20, второй цифроаналоговый преобразователь 21, аналогоцифровой преобразователь 22,блок 23 обработки результатов измерения, масштабно-временные преобразователи

24-t и 24-2, фазоизмерительный блок 25 генератор 26 стробирующих сигналов.

Фазовый детектор 20 и АЦП 22 обрзуют фазоизмерительный блок 25,блоки 10 и 14, коммутатор 16 и АЦП 19 образуют первый масйтабно-временный преобразователь} блоки 11 и 15, коммутатор 17 и АЦП 21 входят во второ масштабно-временный преобразователь

Вход блока 23 обработки результатов измерения соединен с выходом аналого-цифрового преобразователя (АЦП) 22, вход которого соединен с выходом фазового детек-тора 20,а входы последнего соединены с выходами цифроаналоговых преобразователей (ЦАП) 19 и 21. Входы ЦАП 19 и 21 соединены с выходами коммутаторов 16 и 17. Входы коммутатора 16 соединены с выходами блока 14 элементов выборки-хранения, а входы коммутатора 17 соединены с выходами блока 15 элементов выборки-хранения,сигнальные входы блоков 14 и 15 элементов выборки-хранения соединены между собой и с входной клеммой устройства. Управляющие входы блоков элементов выборки-храпения 14 и 15 соединены с выходами элементов И блоков 10 и 11 соответственно, первые входы элементов И блоков 10 и 11 соединены между собой и выходом кольцевого пересчетного блока 12. Вторые входы элементов И блока 10 соединены между собой и с первым выходом триггера 13, а вторые входы элементов И блока 11 соединены между собой и с вторым выходом триггера 13. Третьи входы одноименньрс элементов И блоков 10 и 11 попарно соединены между собой и с вьгходами кольцевого пересчетного блока 12. Первый делитель 1 частоты, формирователь 2 коротких импульсов, элемент ИЛИ 3, управляемая линия 4 задержки, второй делитель 7 частоты, инвертор 9 и первьй элемент И 5 соединены последовательно. Второй вход элемента ИЛИ 3 соединен с выходом первого элемента И 5, а второй вход последнего соединен с входом второго элемента И 8, выходом управляемой линии задержки и входом кольцевого пересчетного блока 12. Второй ёход второго элемента И 8 соединен с выходом делителя 7 частоты. Управляющий вход линии 4 задержки соединен с выходом измерителя, среднего значения периода сигнала 6, вход которого соединен с входной клеммой исследуемого сигнала. Вход генератора считывающего сигнала 18 соединен с входной клеммой опорного сиг;нала, а выход - с входами коммутатора 16 и 17. Устройство работает следующим образом. Из BbicoKoci-aeKnbHoro сигнала фиксированной частоты, -в качестве которого может быть взят выходной сигнал стандарта частоты, с помощью первого делителя частоты 1 и форми.рователя коротких 2 импульсов форьшруют импульсы, период следования которых равен требуемому интервалу определения фазовых флуктуахщй.Каждый сформированный короткий импульс проходит через элемент ИЛИ 3, управ ляемую линию 4 задержки, первый элемент И 5 на другой вход элемента ИЛИ 3. В результате многократной рециркуляции короткого импульса в указанном контуре на выходе управ ляемой линии задержки получают последовательность коротких импульсов с периодом следования ,i-tg- -t, где t - значение задержки сигнала в управляемой линии 4 задержки, ta значение задержки сигнала в первом элементе Л 5, t. - значение задержки сигнала в элементе ИЛИ 3. Выходным кодом измерителя 6 . среднего значения периода сигнала ус анавливается значение задержки, вносимое управляемой линией задержки, при котором значение периода следования рециркулированных импул сов поддерживается равным Т п где Т ср - среднее значение периода исследуемого сигнала за время T;i.T(ip. Второй делитель частоты 7, второй элемент И 8 и инвертор 9 служат для вьщеления из последователь ности рециркулированных импульсов серии из п импульсов и срыва посл этого процесса рециркуляции. При поступлении п-1 рециркулированных импульсов на вход второго делителя 7 частоты на его выходе устанавливается потенциал, разрешакиций прохождение п-го короткого импульса через второй элемент И 8 на вход установки в О второго делителя частоты. Выходной сигнал второго 8« делителя 7 частоты инвертируется инвертором 9 и поступает на второй зход первого элемента И .5, запрещая при этом прохождение через нее п-го короткого импульса. Последний п-ый короткий импульс полученной серии импульсов проходит через второй элемент И 8 и устанавливает второй делитель частоты в исходное, нулевое состояние. Сформированные серии из п импульсов поступают на первое входы элементов И первого 10 и.второго 11 блоков элементов И а также на вход кольцевого п-разрядного пересчетного блока 12, у которого один из разрядов установлен в состояние логической единицы, а остальные - в состояние логического нуля. При воздействии серии коротких импульсов на вход кольцевого пересчетного блока разрешающий уровень логической единицы появляется последовательно на выходе каждого его разряда и поступает последовательно на третий вход каждого из п элементов И первого и второго блоков элементов И 10 и 11. На вторые входы элементов И первого и второго блоков 10 и 11 поступает сигнал соответственно с прямого или инверсного выходов триггера 13, на вход которого подается выходной сигнал первого делителя частоты. При этом каждый импульс из серии коротких импульсов проходит через один из элементов И блоков 1О и 11 на управлянщий вход соответствующего элемента выборки хранения первого 14 или второго 15 блоков элементов в зависимости от состояния триггера. Таким образом триггер, кольцевой пересчетный блок, первый и второй блоки элементов И 10 и 11 образуют распределитель коротких импульсов каждой серии на управлякицие входы первого или второго блоков элементов выборкихранения. Для устранения погрещности запоьшнания элементы выборки хранения могут быть выполнены цифровыми. Исследуемьй сигнал поступает на сигнальные входы всех элементов выборки-хранения, которые осуществляют запоминание значений исследуемого сигнала в моменты прихода на их управляющие входы коротких импульсов. Первая и вторая группы элементов выборки хранения производят запоминание п значений исследуемого сигнала, равномерно распределенных

внутри одного его периода. Интервал времени между периодами исследуемого сигнала, запомненными первой и вто рой группами элементов выборки-хра нения, равен интервалу определения фазовых флуктуации. Выходные кодовые сигналы.первой группы элементов вы0орки хранения поступают на соответствующие входы первого коммутатора 16V а выходные кодовые сигналы второй группы элементов выборки-хранения подаются на, соответСствующие входы второго коммутатора 17. На управляющие входы первогб и второго

коммутаторов поступают выходные сиг налы генератора 18 считывающих сигналов, на вход которого подается опорный сигнал. При последовательном подключении входов коммутаторов к входам цифроаналоговых преобразователей 19 и 21 на выходах последних И 20,. й(| «0,01.

Таким образом; предложенное техническое решение позволяет повысить точность измерения в широком частотном диапазоне без перестраиваемого высокостабильного опорного генератора.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Благов В.А | |||

| и др | |||

| Аппаратура для частотных и временных измерений, М., Советское радио, 1971, с | |||

| Котел | 1921 |

|

SU246A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Фендриков А.И | |||

| Исследование и разработка методов аппаратуры для измерения фазового сдвига | |||

| Автореферат диссертации, Киев, КПИ, 1978, с | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1984-03-23—Публикация

1981-07-27—Подача