(54) ЦИФРОВОЙ КОМПЕНСАЦИОННЫЙ ФАЗОМЕТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой компенсационный фазометр | 1980 |

|

SU924611A1 |

| Цифровой автокомпенсационный фазометр | 1984 |

|

SU1196777A1 |

| Цифровой автокомпенсационный фазометр | 1980 |

|

SU901937A2 |

| Цифровой автокомпенсационныйфАзОМЕТР | 1978 |

|

SU808967A1 |

| Цифровой автокомпенсационный фазометр | 1980 |

|

SU892346A2 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Цифровой фазометр для измерения фазовых сдвигов между переменными напряжениями | 1973 |

|

SU478264A1 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Цифровой автокомпенсационный фазометр | 1983 |

|

SU1166010A1 |

| ЦИФРОВОЙ АВТОКОМПЕНСАЦИОННЫЙ ФАЗОМЕТР | 1969 |

|

SU245913A1 |

1

Изобретение относится к фазоизмерительной технике и предназначено для измерения разности фазодвухпеременных напряжений.

Известен цифровой фазометр, содержащий смесители, входы которых соединены с источником сигнала, а выходы через фильтры нижних частот связаны со входами формирователей импульсов, выходы одного из которых соединены со входами трех схем совпадения, и триггера, выходы которого соединены со входами двух других схем совпадения, выходы которых связаны со входами пересчетных схем, при этом входы пересчетных схем соединены через элемент И с выходами генератора импульсов и управляющего триггера, а выходы пересчетных схем . связаны со входами смесителей, причем выходы одной из пересчетных схем соединены со входом регистра памяти, выходы которого связаны со

входами цифрового отсчетного устрЪиства l .

К недостаткам этого фазометра можно отнести наличие погрешности измерения вследствие применения в трактах преобразования частоты нелинейных элементов-смесителей и погрешность измерения из-за нёидентичности каналов фазометра.

Известен также цифровой фазометр,

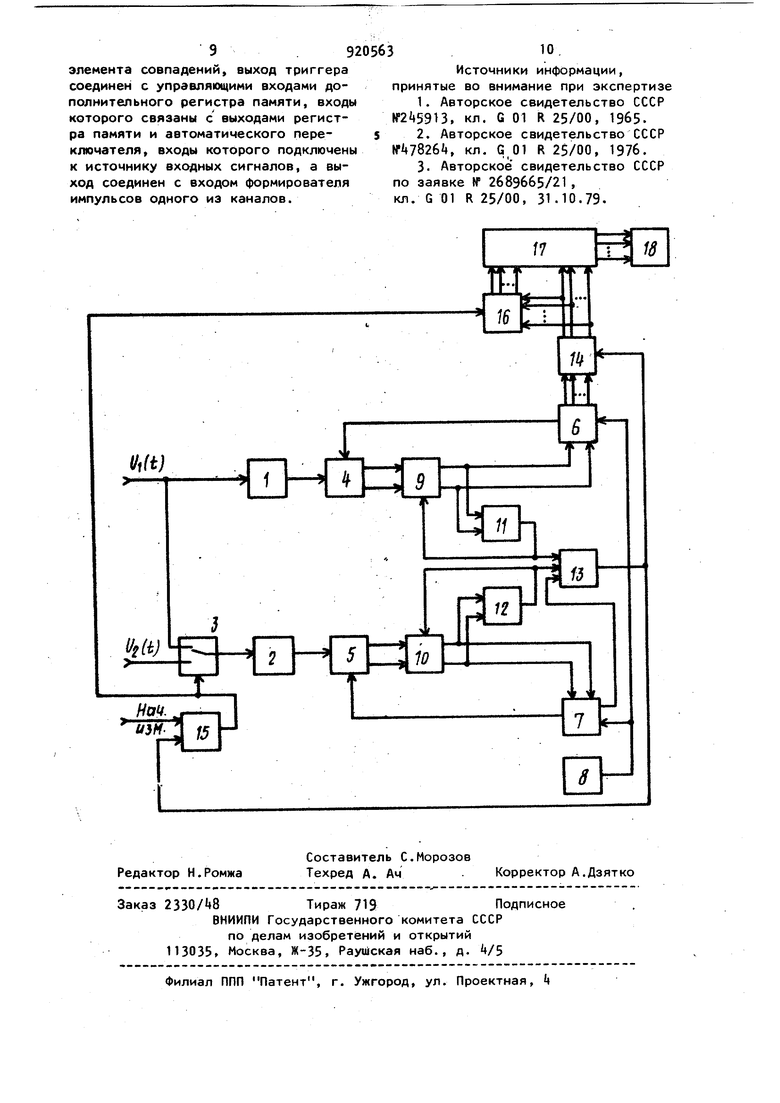

to содержащий двухканальный преобразователь частоты, индикатор нулевого фазового сдвига, дискретные фазовращатели со схемой их управления, устройство смещения частоты входных наISпряжений и формирователи коротких импульсов, выходы которых подключены к раздельным входам триггера, выход которого через мостовую схему задержки связан с одним из входов управ20ления ключевой схемы, второй вход управления которой связан с выходом реверсивного счетчика, а импульсный вход соединен с выходом генератора 39 импульсов, который также связан с первым входом реверсивного счетчика через временной селектор, второй вход временного селектора подключен к выходу мостовой схемы задержки, а выход ключевой схемы подключен к второму входу реверсивного счетчика и ко входу управляемого дискретного фазовращателя, при этом между входом схемы совпадения, управляющей этим фазовращателем, и выходом соответствующего формирователя коротких импульсов включен элемент задержки 2. Недостатками этого устройства являются дополнительные погрешности из-за нелинейных преобразований в каналах фазометра и дополнительные фазовые набеги в каналах из-за их неидентичности. Наиболее близким .к предлагаемому является цифровой автокомпенсационный фазометр, содержащий формирователь импульсов, индикатор нулевого фазового сдвига, реверсивный счетчик импульсов и элемент ИЛИ в каждом канале, а также элемент совпадений и импульсный генератор, выход которого связан со входами двух пересчет ных схем, регистр памяти, входы кото рого соединены с выходами одной из пересчетных схем, а выходы подключе ны ко входам цифрового отсчетного устройства, при этом вхЬды индикато ров нулевого фазового сдвмга связаны с выходами формирователей импульсов и пересчетных схем, а выходы - со входами реверсивных счетчиков, выхо ды которых соединены с управляющими входами пересчетных схем и входами элементов ИЛИ, выходы которых связа ны с установочными входами реверсив ных счетчиков и двумя входами элемента совпадений, третий вход котор го связан с выходом заполнения одной из пересчетных схем, а выход элемента совпадений соединен с управляющим входом регистра памяти. В этом фазометре отсутствуют нелинейные звенья в трактах преобразова ния и поэтому точность измерения у него выше, чем у рассмотренных устройств з. Недостатком этого фазометра является наличие погрешности измерения из-за дополнительных фазовых набегов вследствие неидентичности каналов фазометра. Цель изобретения - повышение точности измерения. Поставленная цель достигается тем, что цифровой компенсационный фазометр, содержащий формирователь импульсов, индикатор нулевого фазового сдвига, реверсивный счетчик импульсов и элемент ИЛИ в каждом канале, а также элемент совпадений и импульсный генератор, выход которого, связан со входами первой и второй пересчетных схем, цифровой отсчетный блок и регистр памяти, входы которого соединены с выходами первой пересчетной схемы, при этом входы индикаторов нулевого фазового сдвига связаны с выходами формирователей импульсов и пересчетных схем, а выходы - с входами реверсивных счетчиков, выходы которых соединены с управляющими входами пересчетных схем и входами элементов ИЛИ, выходы которых связаны с установочными входами реверсивных счетчиков двумя входами элемента совпадений, третий вход которого связан с выходом заполнения второй пересчетной схемы, а выход элемента совпадений соединен с управляющим входом регистра памяти, снабжен дополнительным регистром памяти, триггером, автоматическим переключателем и блоком вычитания, входы которого соединены с выходами регистров памяти, а выхо-. ды связаны со входами цифрового отсчетного блока, при этом вход установки в единицу триггера соединен с клеммой Начало измерения, а вход установки в нуль связан с выходом элемента совпадений, выход триггера соединен с управляющими входами дополнительного регистра памяти, входы которого связаны с выходами регистра памяти и автоматического переключателя, входы которого подключены к источнику входных сигналов, а выход соединен со входом формирователя импульсов одного из каналов. I На чертеже приведена блок-схема п редла га емо го фа зомет ра. Схема содержит формирователи 1 и 2 импульсов, на вход первого из которых подается один из исследуемых сигналов, а вход второго формирователя связан с выходом автоматического переключателя 3, входы которого соединены с источником иссле5дуемых сигналов. Выходы формировате лей 1 и 2 импульсов соединены с одним из входов индикаторов k и S нул вого фазового сдвига, вторые входы которых связаны с выходами пересчет ных схем 6 и 7 входы которых связаны с выходом генератора 8 имгтульсов, а выходы индикаторов и 5 нулевого фазового сдвига соединены с соответствующими входами реверсив ных счетчиков 9 и 10 импульсов, выходы которых связаны с управляющими входами пересчетных схем 6 и 7 и че рез элементы ИЛИ 11 и 12 - с устано вочными входами реверсивных счетчиков 9 и 10 и двумя входами элемента 13 совпадений, третий вход которого связан с выходом заполнения пересчетной схемы 7. Выход элемента 13 совпадений соединен с управляющим входом регистра И памяти и входом . установки в нуль .триггера 15, вход установки в единицу которого соединен с клеммой Начало измерения, а выход соединен с управляющими входа ми автоматического переключателя 3и регистра 16 памяти, выходы кото рого связаны с одними из входов бло ка 17 вычитания, другие входы которого соединены с выходами регистра памяти, которые также связаны со входами регистра 16 памяти, причем входы регистра 1 памяти подключены к выходам пере счетной схемы 6-, а выходы блока 17 вычитания соединены со входами цифрового отсчетного блока 18. Фазометр работает сяедук)щим образом. По команде Начало измерения короткий положительный импульс посту пает на вход уставки в единицу триггера 15 и на его выходе возникает положительный потенциал, соответствующий уровню логической 1. Этим сигналом автоматический, переключатель устанавливается в верхнее положение (как изображено на чертех{е) и разрешается запись информации в ре гистр 16 памяти. Входной сигнал U(t) поступает на входы формирователей 1 и 2, формирующие короткие импульсы в моменты, например, положи тельных переходов через нулевые значения исследуемых сигналов. Выходные импульсы формирователей 1 и 2 поступают на входы индикаторов 4и 5 нулевого фазового сдвига, на вторые входы которых подаются выход-i 63 ные напряжения автоматических дискретных фазовращателей, представляющие собой кольцевые пересчетные схемы. Коэффициент пересчета этих схем выбирается равным ЗбО«10, где п число из-ряда 0,1,2,3,... в зависимости от требуемой дискретности изменения компенсирующих сдвигов. Так, при необходимости получения дискретности в 0,01° п 2 (коэффициент пересчета равен ЗбООО). Изменение угла сдвига фаз входных напряжений, при подаче на оба входа фазометра одного сигнала сдвиг фаз возникает за счет неидентичности каналов и уравновешивается компенсирующим сдвигом между выходными напряжениями пересчетных схем. Фазовый сдвиг выходных напряжений пересчетных схем 6 и 7 осуществляющих деление частоты импульсного генератора 8, может быть установлен в пределах О-ЗбО с дискретностью 10 изменением временного положения момента заполнения одной пересчетной схемы по отношению к другой, Уравновешивание происходит следующим образом.. Импульсы с выхода индикаторов t и 5 нулевого фазового сдвига в зависимости от временного положения приходящих на их входы импульсов поступают на входы сложения или вычитания реверсивных счетчиков 9 и 10 импульсов, где происходит накопление кода нарастающим или убывающим . шагом, соответственно. Емкость ,счетчиков выбирается равной 2N, причем исходное значение кода соответствует N. При суммарном приращении кода счетчиков N или -N, что соответствует результирующему коду 2Мили О, на выходных шинах реверсивных счетчиков 9 и 10 импульсов формируются импульсы, используемце для управления пересчетными схемами 6 и 7 При достижении в реверсивном счетчике импульсов результирующего кода 2 производится подача на вход пересчетной схемь дополнительного импульса, не совпадающего во времени с импульсами генератора 8, а при достижении результирующего кода О производится Зсзпрет прохождения импульса с генератора 8. Эти же импульсы через элементы ИЛИ 11 и 12 устанавливают начальный код реверсивных счетчиков и 10, после чего цикл накопления повторяется. При равенстве нулю среднего значения фазового сдвига между сигналами с выходов формирователей и пересчетных схем выходные импульсы индикаторов 5 и нулевого фазового сдвига равновероятно проходят на сум мирующий и вычитающий входы реверсив ных счетчиков 9 и 10, в результате чего импульсы на их выходах отсутствуют. Это соответствует достижению компенсации. Результирующий код, соответствующий измеряемому фазовому сдвигу, считывается с одной из пересчетных схем, например 6, при полном заполнении другой. Индикатором заполнения второй пересчетной схемы, например 7 служит элемент 13 совпадений. При достижении компенсации (импульсы на выходах элементов ИЛИ 11 и 12 отсутствуют) и при полном заполнении пересчетной схемы 7. на выходе элемента 13 совпадений появл ется импульс, который подается на регистр 1A памяти, осуществляя пере пись кода, установленного положения ми триггеров пересчетной схемы 6. Этот же код одновременно записывается и в регистр 16 памяти, а им{пульс с выхода элемента 13 совпаде1ний устанавливает триггер 15 в нуле рое положение. Этим сигналом осуществляется переключение автоматического переключателя 3 в нижнее положение и запрещается дальнейшая запись информации в регистр 16 памяти Таким образом, в регистрах Щи 16 памяти записан код фазового сдвига, соответствующий набегу в каналах фазометра вследствие их неидентично ти. В блоке вычитания. 17 осуществляется вычитание кодов, записанных в регистрах Т и 16, и в цифровом отсчетном блоке 18 появляется нулевое показание. При переключении автоматического переключателя 3 в нижнее положение на входы формирователей 1 и 2 импульсов поступают сигналы и (t) и Uj(t), фазовый сдвиг между которыми необходимо измерить. Процесс измерения происходит в той же последовательности, как описано. При достижении компенсации измеряемого фазового сдвига компенсирующий сдвиг равен суммарному фазовому сдвигу между исследуемыми сигналами и фазовому набегу в каналах фазометра из-за их неидентичности. В регистре 1б памяти хранится код, соответствующий фазовому набегу в каналах фазометра. В блоке 17 вычитани происходит вычитание кодов, записан чых в регистрах 1 и 16 памяти, а результирующий код, соответствующий фазовому сдвигу между исследуемыми сигналами, дешифрируется и регистрируется на цифровом отсчетном блоке 18. Таким образом, введение указанных дополнительных признаков позволяет повысить точность измерения компенсационных фазометров за счет исключения погрешности измерения, возникающей из-за неидентичности каналов фазометра, а это позволяет значительно расширить сферу применения предлагаемых фазометров и получить существенный экономический эффект. Формула изобретения Цифровой компенсационный фазометр, содержащий формирователь импульсов, индикатор нулевого фазового сдвига, реверсивный счетчик импульсов и элемент ИЛИ в каждом канале, а также элемент совпадений и импульсный генератор, выход которого связан с входами первой и второй пересчетных схем, цифровой отсчетный блок и регистр памяти, входы которого соединены с выходами первой пересчетной схемы, при этом входы индикаторов нулевого фазового сдвига связаны с выходами формирователей импульсов и пересчетных схем, а выходы - с входами реверсивных счетчиков, выходы которых соединены с управляющими входами пересчетных схем и входами элементов ИЛИ, выходы которых связаны с установочными входами реёерсивных счетчиков и двумя выходами элемента совпадений, третий вход которого связан с выходом заполнения второй пересчетной |схемы, а выход элемента совпадений соединен с управляющим входом регистра памяти, отличающийся тем, что, с целью повышения точности измерения, он снабжен дополнительным регистром памяти, триггером, автоматическим переключателем и блоком вычитания, входы которого соединены с выходами регистров памяти, а выходы связаны с входами цифрового оТсчетного блока, при этом вход установки в единицу триггера соединен с клеммой Начало измерения, а вход установки в нуль связан с выходом 992 элемента совпадений, выход триггера соединен с управляющими входами дополнительного регистра памяти, входы которого связаны с выходами регистра памяти и автоматического переключателя, входы которого подключены к источнику входных сигналов, а выход соединен с входом формирователя импульсов одного из каналов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №2it5913, кл. G 01 R 25/00, 19б5. 2.Авторское свидетельство СССР , кл. G,01 R 25/00, 1976. 3.Авторское свидетельство СССР по заявке № 2689665/21, кл. G 01 R 25/00, 31.10.79.

Авторы

Даты

1982-04-15—Публикация

1980-07-22—Подача