группу элементов ИЛИ-НЕ, включающую N элементов ИЛИ-НЕ, группу элементов ИЛИ и группу элементов задержки по N (N-1)(N-2)/3 соответствующих элементов в каждой, причем выход тго элемента И-НЕ первой группы, где , 2,..N(N-1)/2, соединен с первым входом i-го элемента И-НЕ второй группы, выход которого соединен с первым входом 1-го элемента И-НЕ первой группы, в каждой паре входов из всех N(N-1)72 па входов блока динамического приоритета, где , и т-й входы соединены соответственно с входами двух (2М-1с) ()/2 )-х элементов И-НЕ первой и второй групп, входы j-ro элемента ИЛИ-НЕ группы элементов ШШ-НЕ, где 1, 2, ., .,N , соединены соответственно с выходами (N-l)-x элементов И-НЕ первой и второй групп, вторые входа которь х соединены с J-м входом блока динамического приоритета, выход j-fo элемента ИЛИ-НЕ соединен с j-м выходом блока динамического приоритета, для каждой тройки входов , /5-го и у-го входов блока динамического приоритета, из всех возможных N(N-1)(N-2)/3 Троек входов, где I4flt :p y f4, выход ()(oC-1)/2+/S-oi ro элемента И-НЕ пе рвой группы, выход. ( 2 N-ot) i -1) / 2 +|-ЫЬго элемента И-НЕ второй группы,

выход (2N-fs)Q5-l)/2+f-/5/-ro элемента И-НЕ первой группы соединены соответственно с первым, вторым,третьим

входами I .

(2(у-р.(г«4(гм-.). ,(1(р-.,-.,)-.)-го

,

элемента ИЛИ группы элементов ИЛИ, а выход (2N-oL)(oC-1)/2+/STji;)-ro элемента И-НЕ второй группы, выход (2N-oC) (()/2 -Т 0-го элемента И-НЕ первой группы, выход {2N-|3) (p-1)/2+j-p)-ro элемента И-НЕ второй группы соединены соответственно с первым, вторым и третьим входами

(N2-N-f(2NM)4(5H

fU- W-oL-ft

(p-ei-f|-ro 2

элемента ИЛИ группы элементов И.ПИ,. выход С-го элемента ИЛИ, где в 1, 2,., .-,N(N-1) (1Ч-2)/3, через элемент задержки соединен с третьим входом соответствующего элемента И-НЕ первой и второй групп, выход которого соединен с первым входом Р-го элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обслуживания запросов | 1987 |

|

SU1437864A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU978150A1 |

| Устройство для группового обслуживания запросов | 1984 |

|

SU1196868A1 |

| Устройство циклического приоритета | 1986 |

|

SU1411746A1 |

| Устройство для обслуживания запросов | 1983 |

|

SU1141412A1 |

| Устройство динамического приоритета | 1980 |

|

SU926659A1 |

| Устройство для обслуживания групповых приоритетных запросов | 1990 |

|

SU1753473A1 |

| Устройство динамического приоритета | 1986 |

|

SU1315977A1 |

| Устройство для управления обменом информации | 1982 |

|

SU1081638A1 |

| Устройство управления сегментированной памятью многопроцессорной системы | 1990 |

|

SU1753477A1 |

1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МАКСИМАЛЬНОГО ЧИСЛА, содержащее N узлов анализа, каждый из которых содержит триггер, элементы И и НЕ, отличающееся тем, что, с целью увеличения быстродействия, в него введены блок динамического приоритета, а в каждый узел анализа - второй триггер, первый и второй элементы задержки, согласукмций элемент, блок сравнения, группу элементов И, причем информационные входы устройства подключены к первым информационным входам соответствукщих узлов анализа, вторые информационные входы которых подключены через общую магистраль к выходам устройства, в каждом узле анализа первые информационные входа соединены с информационными входами элементов И группы и с первыми информационными входами блока сравнения, выходы элементон И группы, являющиеся информационными выходами узла анализа, соединены с вторыми информационными входами блока сравнения, авыход блока срав/ , -/э нения соединен с первьм входом первого элемента ИШ и через согласующий элемент - с входом установки в нулевое состояние первого триггера, с входом элемента НЕ и через общую шину с выходами согласующих элементов всех узлов анализа, выход первого элемента ИЛИ, являкяцийся выxoдoмJCt т нала запроса узла анализа, подключен к соответствукщему входу блока динамического приоритета, выход элемента НЕ в каждом узле анализа подключен к первому входу элемента И, выход которого соединен с входом-установки в единичное состояние первого S триггера, выход которого подключен к первому входу второго элемента ИЛИ, выход которого соединен с управляющими элементов И группы, вход разревейня анализа узла анализа § соединен с соответствующим выходом блока динамического приоритета, а в узле анализа - с входом установки в единичное состояние второго триг00 СО СЛ гера, через первый элемент задержки - с вторым входом элемента И, и через второй элемент задержки с вхо дом установки в нулевое состояние 4 второго триггера, вьгход которого подключен к вторым входам первого и «второго элементов ИЛИ, шина установ ки начального состояния устройства соединена с входами установки в единичное состояние первого м второго триггеров всех узлов анализа. 2. Устройство по п. 1, о т л и чающееся тем, что блок динамического- приоритета содержит первую и вторую группы элементов И-НЕ по N ()/2 элементов И-НЕ в каждой.

Изобретение относится к вычислительной технике, в частности к построению узлов цифровых вычислительних машин, а также сисТем автоматики и управлякяф1х систем

Известно устройство для определения экстремального числа, которое содержит два регистра, блок сравнения, элементы И и равнозначности i J.

Недостатком указанного устройства является низкое быстродействие, вы, званное последователЁ11Ы{« сравнениетп чисел, причем период сравнения равен времени срабатывания регистров сравнения.Наиболее близким к предлагаемому является устройство для определения

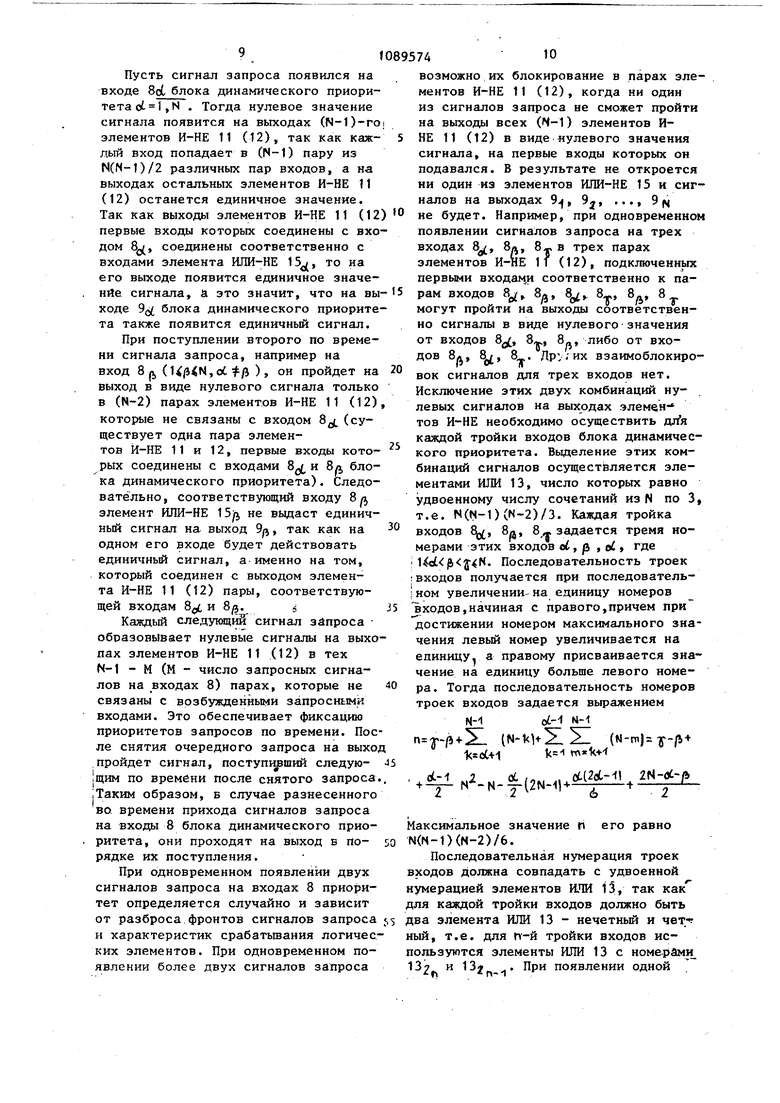

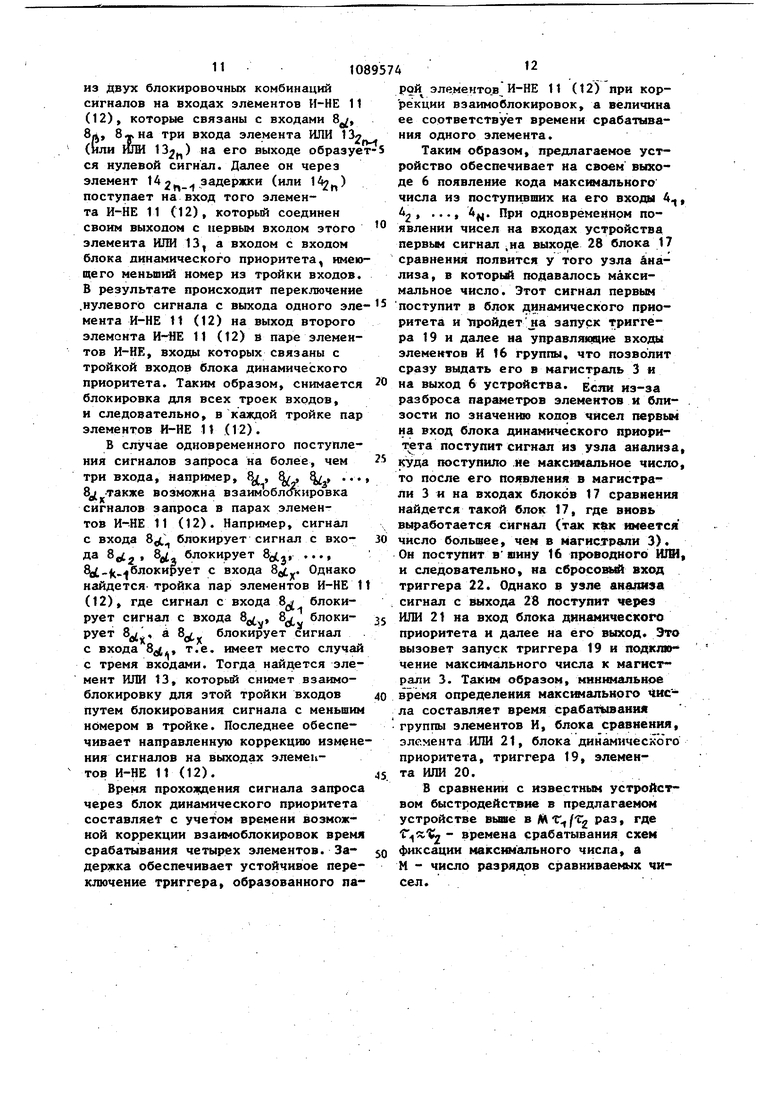

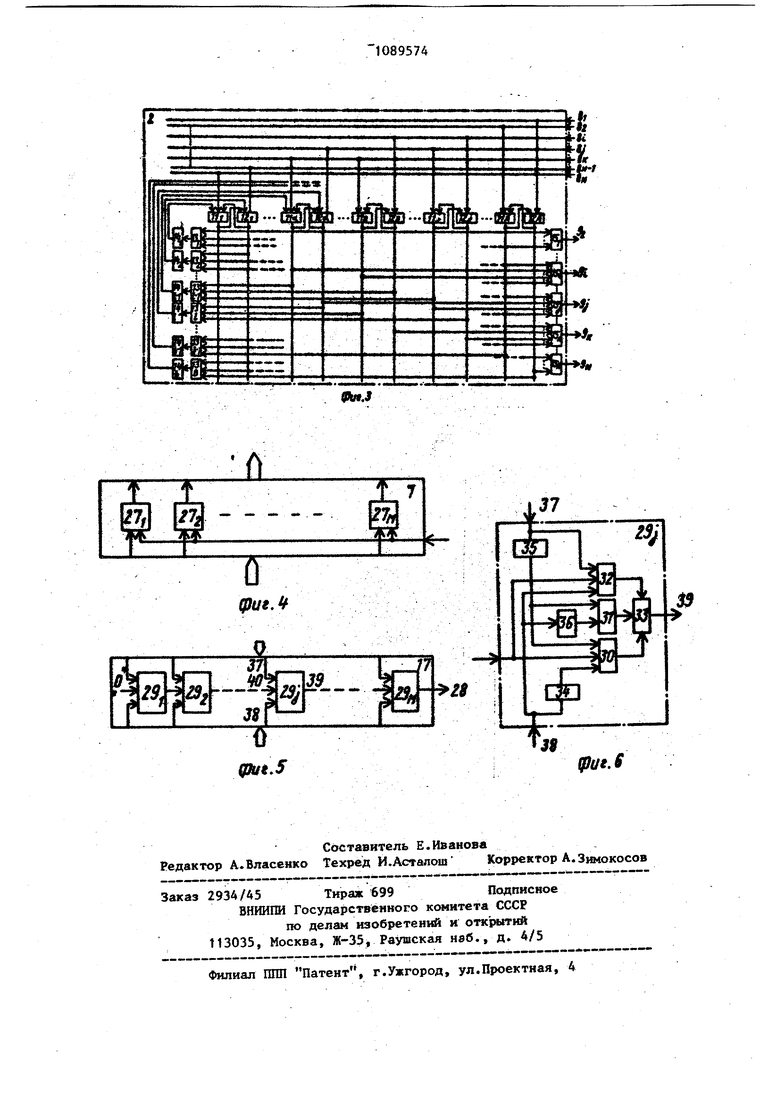

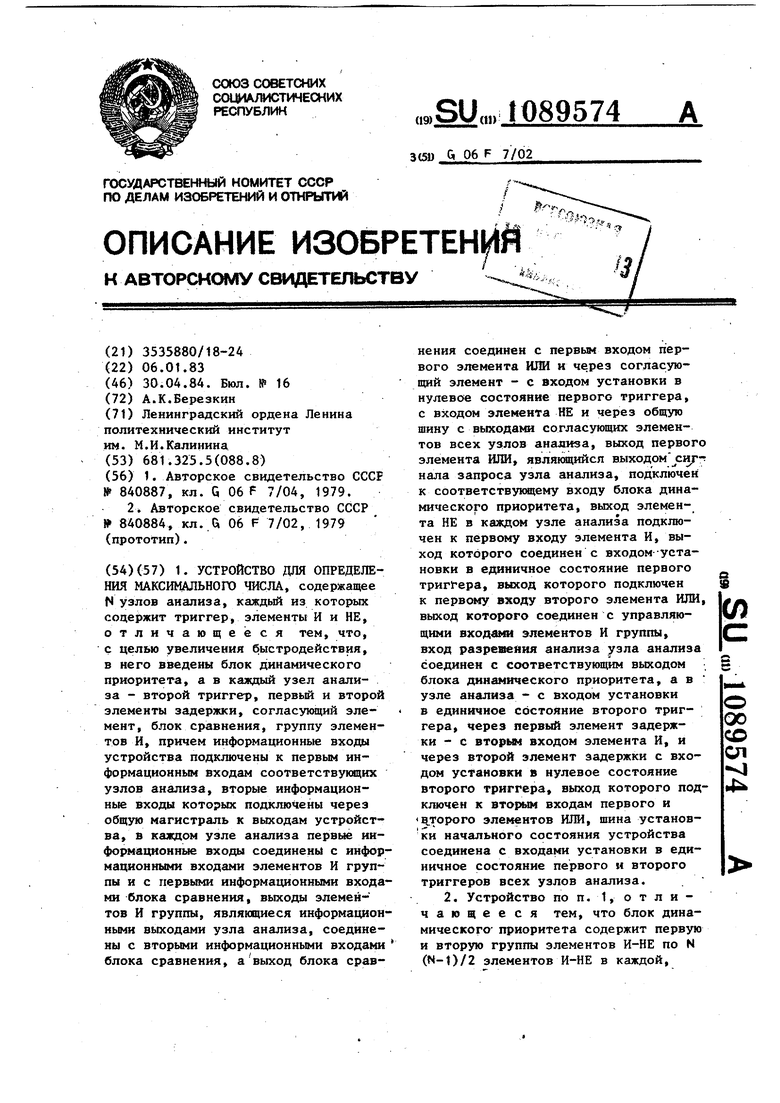

максимального числа, содержащее элемент Ши1 и п узлов анализа, каждый из которых состоит из триггера и первого элемента И, причем первый вход первого элемента И каждого -го узла анализа, где ,2,...п, соединен с i-M информационным входом устройства, а выход первого элемента И подключен к 1-у входу элемента Ш1И, прямой выход триггера i-ro узла анализа соединен с вторым входом первого элемента И того же узла анализа, входы установки в единичное состояние триггеров всех узлов анализа подключены к шине начальной установки, каждый узел анализа содержит также второй элемент И и элемент НЕ, выход первоГО элемента И каждого узла анализа соединен через элемент НЕ с первым входом второго элемента И, второй вход которого подключен к выходу элемента Jtlffl, а выход - к входу установки в нулевое состояние триггера того же уэла анализа Г 2.: Недостатком известного устройства является ниэкое быстродействие, вызванное последовательным поступлением сравниваемых чисел в устройство, а также отсутствие значения выбранного числа. Цель изобретения - увеличение быстродействия устройства, а также расширение функциональных возможностей путем выдачи кода числа. Поставленная цель достигается тем, что в устройство для определени максимального числа, содержащее N узлов анализа, каждый из которых содержит триггер, элементы И и НЕ, вве дены блок динамического приоритета, а в каждый узел анализа - второй три гер, первый и второй элементы задерж ки, согласующий элемент, блок сравне ния, группу элементов И, причем информационные входы устройства подклю чены к первым информационным входам соответствующих узлов анализа, вторы информационные входы которых подключены через общую магистраль к выходам устройства, в каждом узле анализа первые информационные входы соеди нены с информационными входами элементов И группы и с первыми информационными входами блока сравнения, выходы элементов И группы,.являющие ся информационными выходами узла ана лиза, соединены с вторыми информационными входами блока сравнения, а выход блока сравнения соединен с пер вым входом первого элемента ИЛИ и через согласующий элемент - с входом установки в нулевое состояние первог триггера, с входом элемента НЕ и через общую шину с выходами согласую щих элементов всех узлов анализа, вы ход первого элемента ИЛИ, являющийся выходом сигнала запроса узла анализа, подключен к соответствующему входу блока динамического приоритета выход элемента НЕ в каждом узле анализа подключен к первому входу элемента И, выход которого соединен с входом установки в единичное состояние первого триггера, выход которого подключен к первому входу второго 10 4 элемента ИЛИ, выход которого соединен с управляющими входами элементов И группь, вход разрешения анализа узла анализа соединен с соответствукицим выходом блока динамического приоритета, а в узле анализа - с входом установки в единичное состояние второго триггера, через первый элемент задержки - с вторым входом элемента И, и через второй элемент задержки с входом установки в нулевое состояние второго триггера, выход которого подключен к вторым входам первого и второго элементов ИЛИ, шина установки начального состояния устройства соедииена с входами установки в единичное состояние первого и второго триггеров всех узлов ан4пиза. Блок динамического приоритета содержит первую и вторую группы элементов И-НЕ по N(H-1)/2 элементов И-НЕ в каждой, группу элементов Ш1И-НЕ, включающую N элементов ИПИ-НЕ, группу элементов ИЛИ и группу элементов задержки по K(N-1)(N-2)/3 соответствующих элементов в каждой, причем выход l-ro элемента И-НЕ первой группы, где , 2, ...,N(N-1)72, соединен с первым входом i-ro элемента И-НЕ второй группы, выход которого соединен с первым входом t-ro элемента И-НЕ первой группы, в каждой паре 1(,т входов из всех N(N-1)/2 пар входов блока данамического приоритета, где , 1(-й и т-й входы соединены соответственно с втогшми входами двух (2N-lc)(k-1)/24iTr-lc)-x элементов И-НЕ первой и второй групп, ЛХОды i-ro элемента ИЛИ-НЕ группы элементов ИЛИ-НЁ, где 1, 2,. iW, соединены соответственно с выходами (N-l)-x элементов И-НЕ первой и второй группы, вторые входы которых соединены с J-M входом блока динамического приоритета, выход /-го элемента ШШ-НЕ соединен с j -м выходом блоКа динамического приоритета, для каждой тройки входов -ot-ro, -го и f-ro входов блока динамического приоритета, из всех возможных N(N-1)(N-2)/ /3 троек входов, где , выход () (a-)/2+f +Ts-d}-ro элемента И-НЕ первой группы, выход (2N-o) (ci-1)/2 элемента И-НЕ второй группы, выход (2N-)(|5-1)/2+)-ro элемента И-НЕ первой группы соединены соотS : 1 ветственно с первым, вторым, третьим входами Иг-/ ot(2ot-1| (2N-()4 .-1),..,,).„ элемента ИЛИ группы элементов ИЛИ, а выход (2N-e)4i-1)/2+/S-ef)-ro элемен та И-НЕ второй группы, выход (2N-o() (ct-t)/2 -Trf/-ro элемента первой группы, выход (2N-/J)(-t)/2+y-/5)-ro элемента И-НЕ второй группы соединены соответственно с первым, вторым и третьим входами 2 ((N2-N-f )(NH)ff (2ММ 4(2,/MHlbt|l L(;j-,,.,o элемента ИЛИ группы элементов ШШ, выход -гоэлемента ИЛИ, где , 2 ..., N(N-1)(N-2)/3, через элемент задержки соединен с третьим входом соответствующего элемента И-НЕ первой и второй групп, выход которого соединен с первьш входом t-ro элемен та ИЛИ. На фиг. 1 представлена схема пред лагаемого устройства; на фиг. 2 схема блока анализа; на фиг. 3 - схе ма блока динамического приоритета; на фиг. 4 - схема группы элементов И на фиг. 5 - схема блока сравнения; на фиг. 6 - схема поразрядного сравнения. Устройство содержит узлы анализа Ц 2 « 2 динамическог приоритета, общую магистраль 3, информационные входы , 4,, ..., 4f( устройства, общую шину 5, информацио ный выход 6 устройства, шину 7 начал ной установки, входы 8 блока динамического щ иоритета, выходы блока 9 динамического приоритета, информационные входы tO узлов анализа. Блок динамического приоритета содержит группу элементов И-НЕ 1 Ц, 112, 11д, группу элементов И-НЕ 12, 12j ..., 12д..| где А N(N-1)/2, груп пу элементов ИЖ 13, 13, 13, груп пу элементов 14, 142, ... I4g задержки, где (N-1)(N-2)/3, группу элементов Ш1И-НЕ 15-,, 15 Уэел анализа содержит группу элементов И 16, блок 17 сравнения, элемент И 18, триггер 19, элементы ШШ 20 и 21, триггер 22, элещий вход блока элементов И. Группа элементов И пропускает код числа на выход 10 в магистраль 3 на время, А мент 23 задержки, элемент НЕ 24, согласующий элемент 25, элемент 26 задержки. Группа элементов И содержит элементы И 27 , 27, ..., 27, где М - число разрядов сравниваемых чисел. Блок сравнения содержит выход 28 и М схем поразрядного сравнения 29 29д. Схема поразрядного сравнения содержит элементы И-НЕ 30 33, элементы НЕ 34 и 35, элементы 36 задержки, выходы 37 и 38, выход 39. Устройство работает следующим образом. Числа в параллельных кодах, среди которых выделяется максимальное, выставляются на информационных входах 4, 4, .,., 4ц ycTpoHCTEfa.. В каждом узле анализа, например 1., число поступает на информационные входы группы элементов И 16 и блока 17 сравнения. На второй информационный вход блока 17 сравнения поступает код числа из магистрали 3, общей для всех узлов анализа. В результате блок 17 сравнения вырабатывает единичный сигнал на выходе 29 если число на входе 4 больше выставленного в магистрали 3. При этом этот сигнал поступает через согласующий элемент 25, пропускающий сигнал только в ддном направлении, на выход 5 в общую шину, которая реализует функцию проводного ИЛИ. Сигнал из общей шины поступает на сбросовьй вход второго триггера 22 и через элемент НЕ 24 на вход элемента И 18. Поэтому, если в каком-либо узле анализа число на входе 4 больше, чем в магистрали 3, то триггер 22 во всех узлах будет сбрасываться. В то же время сигнал с выхода 28 блока 17 сравнения через элемент ИЖ 21 поступает на вход 8 блока динамического приоритета, который пропускает на свои выходы 9, 9, .., 9 HI только один из поступивших на входы сигналов в порядке времени поступления. В результате блок динамического приоритета выдает единичный сигнал только в один из узлов анализа, который выработал сигнал на выходе 28 блока 17 сравнения ранее других. Этот сигнал запускает триггер 19, сигнал с которого через элемент ШШ 20 поступает на управляю7определяемое задержкой 23, сигнал с выхода которой сбрасывает триггер 19, и является задержанным сигналом запуска триггера.. Задержка в элементе 23 равна времени срабатьгаания блока сравнения и выработки сигнала на выходе 28, и следователь но, на выходе 8д. Кроме того, сигна с выхода триггера 19 через элемент ИЛИ 21 также поступает в блок динамического приоритета, чтобы на время выработки новых сигналов в бл ках 17 сравнения в схемах фиксации максимального числа не произошло .подключение к магистрали 3 более од ного числа. Сигнал с выхода задержки 26 поступает на вход элемента И 18. В случае отсутствия сигнал в шине проводного ИЛИ на второй вход зпемента И 18 поступает единичный сигнал. Тогда запускается триггер 22 (сигнала сброса на нем в этом случае нет), сигнал с которо го, проходя через элемент ИЛИ 20 на управляющие входы группы элементов И 16, обеспечивает прохождение максимального числа (сигналов в шин проводного ИЛИ нет) в магистраль 3 до появления на входах устройства большего числа. При появлении большего числа на одном из входов устройства 4, 4., ..., 4|ц сигнал в шине проводного ИЛИ сбросит триггер 22. Задержка в элементе 26 мень ше задержки в элементе 23 на величи ну, необходимую для запуска триггера 22 и выставлении им сигнала на вход элемента ИЛИ 20 до сброса триг геря 19. . 1руппзэлемектов И 16 осуществляет передачу при действии единичного сигнала на управляющем входе кода числа через элементы И 27, 27, ..., 27, где М - число разрядов числа. При этом элементы И 27 должны обеспечивать согласование с магистралью при нулевом значении управлякмцего сигнала, т.е. иметь при этом большое выходное сопротивление, которое изолирует выход от источников единичного и нулевого сигнала. Блок 17 сравнения содержит М яче ек поразрядного сравнения 29j, 29.. ..., 29дд, каждая из которых осущест ляет функцию, обеспечивающую единич ное значение на выходе 39 при условии А.. , где А значение i-ro раз 4 ряда,поступившего на вход числа, и В,- - значение {-го разряда числа в магистрали. Кроме того, единичное значение выхода 39 будет при единичном значении на входе 40. Эту функцию реализуют элементы И-НЕ 30 - 33 и элементы НЕ 34 и 35. Задержка 36 необходима для того, чтобы при одновременном появлении единичного сигнала на входах 37 и 38 (т.е. В и А) не было единичного сигнала на выходе 39 на время задержки в элементе НЕ 34. Блок динамического приоритета работает сперукацяи образом. Входы блока динамического приоритета 8, 82, ..., .едены на все возможные N (М-1)/2 пары входов. Каждая пара входов В., 8 задается двумя номерами входов к и т,-а последовательность пар задается последовательным увеличением правого номера на единицу и при достижении им максимального значения - увеличением левого номера на единицу. При этом начальное значение правого номера на единицу больше левого номера. Сквозная нумерация всех возможных пар входов задается выражением k-1 (W-j1+«- - T -( - . где , a :i - номер пары входов. Максимальное значение номера i совпадает с выражением (4-1)/2 при и , т.е. с числом элементов И-НЕ 11 и И-НЕ 12. Отсюда следует, что два входа блока дина1мического приоритета, входящие в i-ю пару входов, соединяются соответственно с первыми входами -х элементов И-НЕ 11,и И-НЕ 12 , т.е. первой и второй групп. Каждая пара i-x элементов И-НЕ 1Ц, 12j образует триггер, который при отсутствии сигналов на своих входах на обоих выходах выставляет единичное значение сигнала. При появлении единичного сигнала на входе одного элемента И-НЕ пары на его выходе образуется нулевое значение сигнала, в то время как на выходе второго элемента пары присутствует единичный сигнал. Появление одновременно двух единичных с1игналов на вхоДах обоих, элементов И-НЕ 11 t Ч пары приведут к случайному выставлению единичного сигнала на выходе одно го- из элементов И-НЕ. Пусть сигнал запроса появился на входе 8oL блока динамического приоритета ,N . Тогда нулевое значение сигнала появится на выходах (N-l)-ro элементов И-НЕ 11 (12), так как каждый вход попадает в (N-1) пару из N(N-1)/2 различных пар входов, а на выходах остальных элементов И-НЕ 11 (12) останется единичное значение. Так как выходы элементов И-НЕ 11 (12 первые входы которых соединены с вхо дом 8д, соединены соответственно с входами элемента ИЛИ-НЕ 15, то на его выходе появится единичное значение сигнала, а это значит, что на вы ходе 9о( блока динамического приорите та также появится единичный сигнал. При поступлении второго по времени сигнала запроса, например на вход 8 р, (,ot f/i ), он пройдет на выход в виде нулевого сигнала только в (N-2) парах элементов И-НЕ 11 12) KOTopttiie не связаны с входом 8 (существует одна пара элементов Й-НЕ 11 и 12, первые входы которых соединены с входами 8 и 8А блока динамического приоритета). Следовательно, соответствующий входу 8л элемент Ш1И-НЕ не выдаст единичный сигнал на выход 9/, так как на одном его входе будет действовать единичный сигнал, а-именно на том, который соединен с выходом элемента И-НЕ 11 (12) пары, соответствующей входам 8д(, и 8/3. « Каждьй следующий сигнал запроса образовывает нулевые сигналы на выхо дах элементов И-НЕ 11 (12) в тех N-1 - М (М - число запросных сигналов на входах 8) парах, которые не связаны с возбужденными запросными входами. Это обеспечивает фиксацию приоритетов запросов по времени. Пос ле снятия очередного запроса на выход пройдет сигнал, поступивший следую|щим по времени после снятого запроса 1Таким образом, Б случае разнесенного во времени прихода сигналов запроса на входы 8 блока динамического приоритета, они проходят на выход в порядке их поступления. При одновременном появлении двух сигналов запроса на входах 8 приоритет определяется случайно и зависит от разброса фронтов сигналов запроса ,5 два

и характеристик срабатьтания логических элементов. При одновременном появлении более двух сигналов запроса

ный, т.е. для П-й тройки входов используются элементы ИЛИ 13 с номерами

13 и 13 . При появлении одной fi -1 возможно их блокирование в парах элементов И-НЕ 11 (12), когда ни один из сигналов запроса не сможет пройти на выходы всех (N-1) элементов ИНЕ 11 (t2) в виде нулевого значения сигнала, на первые входы которых он подавался. В результате не откроется ни один из элементов ИЛИ-НЕ 15 и сигналов на выходах 9-(, 9, .... 9 (ц не будет. Например, при одновременном появлении сигналов запроса на трех входах 8, 8л, 8 в трех парах элементов И-НЕ IT (12), подключенных первыми входам и соответственно к парам входов 8 8yj, 8д,„ 8-р, 8, 8 могут пройти на выходы соответственно сигналы в виде нулевого значения от входов 8д(, 8«., 8, либо от входов 8д, 8, 8 . ДР:;ИХ взаимоблокироI Д вок сигналов для трех входов нет. Исключение этих двух комбинаций нулевых сигналов на выходах элемен- тов И-НЕ необходимо осуществить каждой тройки входов блока динамического приоритета. Выделение этих комбинаций сигналов осуществляется элементами ИЛИ 13, число которых равно удвоенному числу сочетаний из N по 3, т.е. N(N-1)(N-2)/3. Каждая тройка входов , 8д, 8- задается тремя номерами этих входов ci, ) 0 где . Последовательность троек ВХОДОВ получается при последовательном увеличении- на единицу номеров входов,начиная с правого,причем при достижении номером максимального значения левый номер увеличивается на единицу, а правому присваивается значение на единицу больше левого номера. Тогда последовательность номеров троек входов задается выражением N-1 ot-l N-t n T-/it.$l ( (N-ni)-j-/i + 1 soC4l k ,,..г.,,m,: аксимальное значение n его равно (N-1)(N-2)/6. Последовательная нумерация троек ходов должна совпадать с удвоенной умерацией элементов ИЛИ 13, так как ля каждой тройки входов должно быть элемента ИЛИ 13 - нечетный и чет-« из двух блокировочных комбинаций сигналов на входах элементов И-НЕ 11 (12), которые связаны с входами 8, 8л, S-jpHa три входа элемента ИЛИ 13 (или ШШ 13,) на его выходе образуе ся нулевой сигнал. Далее он через элемент 14 2 задержки (или 14) поступает на вход того элемента И-НЕ 11 (12), который соединен своим выходом с первым входом этого элемента ИЛИ 13, а входом с входом блока динамического приоритета имею щего меньший номер из тройки входов. В результате происходит переключение .нулевого сигнала с выхода одного эле мента И-НЕ 11 (12) на выход второго элемента 11 (12) в паре элементов И-НЕ, входы которых связаны с тройкой входов блока динамического приоритета. Таким образом, снимается блокировка для всех троек входов, и следовательно, в каждой тройке пар элементов И-НЕ 11 (12). В случае одновременного поступления сигналов запроса на более, чем три входа, например, 8, . 1им1эбл ж 8 также возможна взаимоблокировка сигналов запроса в парах элементов И-НЕ 11 (12). Например, сигнал с входа 8 блокирует сигнал с входа 8et2 . . .блокирует с входа . Однако найдется тройка пар элементов И-НЕ И (12), где сигнал с входа 8 блоки рует сигнал с входа 8 , 8 блокирует 8д4, а Од, блокирует сигнал с входа 8., т.е. имеет место случай с тремя входами. Тогда найдется элемент ИЛИ 13, который снимет взаимоблокировку для этой тройки входов путем блокирования сигнала с меньшим номером в тройке. Последнее обеспечивает направленную коррекцию измене ния сигналов на выходах элементов И-НЕ 11 (12). Время прохождения сигнала запроса через блок динамического приоритета составляет с учетом времени возможной коррекции взаимоблокировок время срабатывания четырех элементов. Задержка обеспечивает устойчивое переключение триггера, образованного парой элементов И-НЕ 11 (12) при коррекции взаимоблокировок, а величина ее соответствует времени срабатывания одного элемента. Таким образом, предлагаемое устройство обеспечивает на своем выходе 6 появление кода максимального числа из поступивших на его входы 4 4, ..., 4. При одновременном появлении чисел на входах устройства первьм сигнал ,на выходе 28 блока 17 сравнения появится у того узла Анализа, в который подавалось максимальное число. Этот сигнал первым поступит в блок динамического приоритета и пpoйдeтJla запуск триггера 19 и далее на управля1ощие входы элементов И 16 группы, что позволит сразу выдать его в магистраль 3 и на выход 6 устройства. ЕСЛИ из-за разброса параметров элементов и близости по значению кодов чисел первым на вход блока динамического приорит,ета поступит сигнал из узла анализа, куда поступило не максимальное число, то после его появления в магистрали 3 и на входах блоков 17 сравнения найдется такой блок 17, где вновь выработается сигнал (так к&к Ю4еется число большее, чем в магистрали 3). Он поступит в шину 16 проводного ШШ, и следовательно, на сбросовьй вход триггера 22. Однако в узле анализа сигнал с пмхода 28 поступит через 21 на вход блока динамического приоритета и далее на его выход Это вызовет запуск триггера 19 и подклю чение максимального числа к магистрали 3. Таким образом, минимальное время определения максимального tKcла составляет время срабаташани группы элементов И, блока сравнения, элемента ИЛИ 21, блока динамического приоритета, триггера 19, элемента ИЛИ 20. В сравнении с известным устройством быстродействие в предлагаемом устройстве вьше в раз, где времена срабатывания схем фиксации faкciO4aльнoгo числа, а М - число разрядов сравниваемых чисел.

(put,1

(J3ui. Z

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения экстремальныхчиСЕл | 1979 |

|

SU840887A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| С | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-04-30—Публикация

1983-01-06—Подача