непосредственного движения потока управляющей информации в системе.

Проблема обработки множества одновременных .запросов от группы процессоров и устройства ввода-вывода, реализующих процедуру внутрисистемных обменов информации двух указанных уровней может стать острой, в то время как на- л ичие ненулевого списка запросов от локальных процессов обработки допускает некоторую степень свободы при назначении приоритета доступа активным элементам МПС, при которой число возможных конфликтов при обращении к памяти могло быть существенно снижено.

Блок управления памяти к множеству по числу процессоров в системе, сегментов памяти включает соответствующее множество hap независимых коммутаторов связи. Первый из пары коммутаторов включен к магистральным усилителям локальной шины привилегированного процессора, а второй, объединенный по входам с другими в пределах упомянутого множества, упорядочено связан со стробирующим выходом бло- ка арбитра стандартной шины и оконечными коммутаторами процессоров и устройств ввода-вывода.

Под управлением задающего слова цикла процессора допустим непосредственный выбор первого из пары упомянутых коммутаторов для доступа в собственный сегмент памяти (вход с предпочтением) либо через состояния обобществленного выхода оконечных коммутаторов - монопольный об- мен задающими сигналами процессоров и устройств ввода-вывода с линиями стандартной общей шины, реализуется установкой традиционных операций (формирование запроса шины, прием подтверждения захвата шины, отпускание шины) активных элементов с блоком арбитра шины, чьи состав, организация взаимодействия и совокупность используемых входных флагов являются общепринятыми - доступ в произвольно адре- суемый сегмент памяти (вход по запросу). Установление обращения через выбранный коммутатор связи входа по запросу без временных потерь имеет место только при отсутствии одновременного цикла от входа с предпочтением в указанный сегмент памяти.

Диалоги информационными сообщениями памяти С активными элементами МПС при динамическом планировании и подза- писи пакетов программ и данных находятся в ведении условий текущего состояния процесса с учетом факторов: глубина списка отобранных в память активных свободных заданий при достаточно большой информа-

ционной связности программных сегментов не может быть значительной, а число элементов списка частных задач на отдельных участках обработки уступает числу локальных процессов; прогнозирование очередности завершения локальными процессами своих текущих заданий затруднительно.

Как следствие, локальному процессу обработки, завершившему текущее задание и не получившему возможность захвата программы подготовленной ветви задачи из собственного сегмента памяти, предопределены либо длительный интервал ожидания размещения активного шага работы при сохранении приоритетного режима обращения, либо при захвате очередной свободной ветви задачи из несобственного сегмента многократные взаимодействия с памятью с использованием входа по запросу. Информационные обмены посредством шины связываются с ростом задержек на разрешение конфликтов одновременного доступа к сегментам памяти и отягощаются временными издержками реализации независимых по сути процедур обработки и подзаписи ин- формацинных пакетов планируемых задач в последовательном канале общей шины.

Основным недостатком известного блока управления сегментированной памяти следует считать низкое быстродействие при инициализации локальным процессом обработки программного пакета и пакета дан- ных свободной ветви задачи, распределенных в несобственный сегмент памяти, вытекающее из условий динамического планирования сопряженным процессом активных свободных ветвей задачи, а также асинхронности в реализации связанных заданных заданий и выражающихся в согласовании опережающего распределения по сегментам памяти списка заданий в соответствии с реально устанавливающимся порядком завершения локальных процессов обработки.

Наиболее близким к предлагаемому являются блоки управления сегментированной памяти, включающие в себя группы коммутаторов связи для обращений в подобласти хранения с функционально однородных входов.

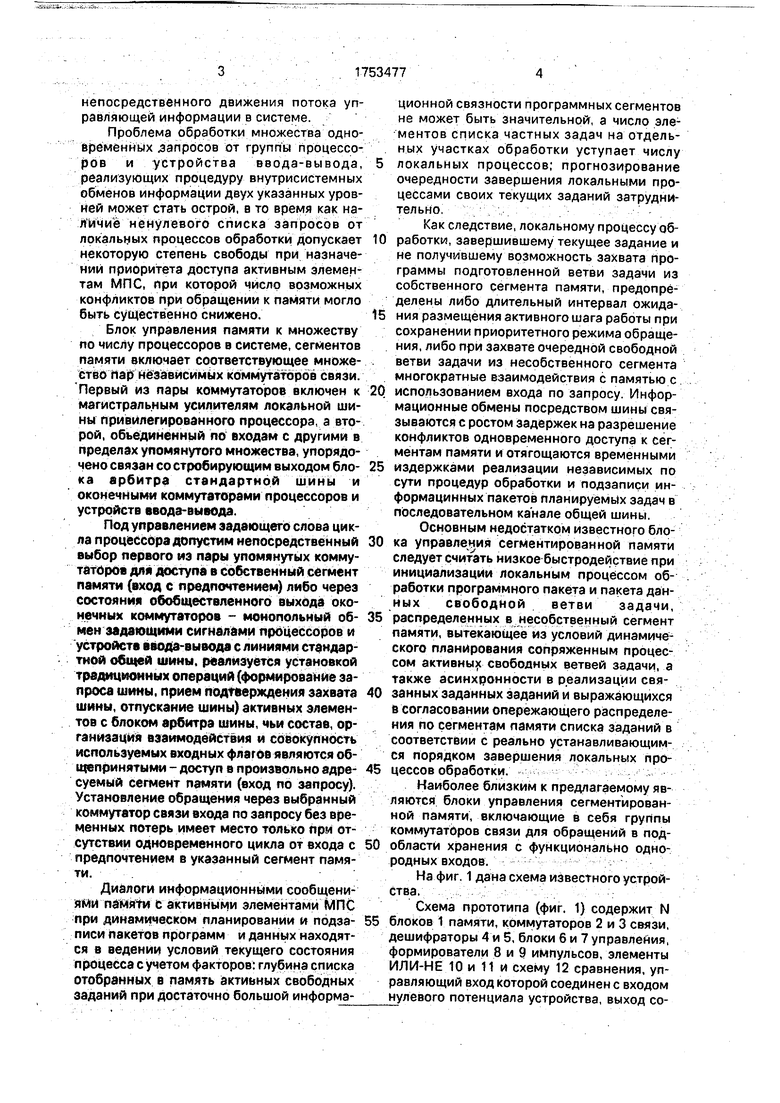

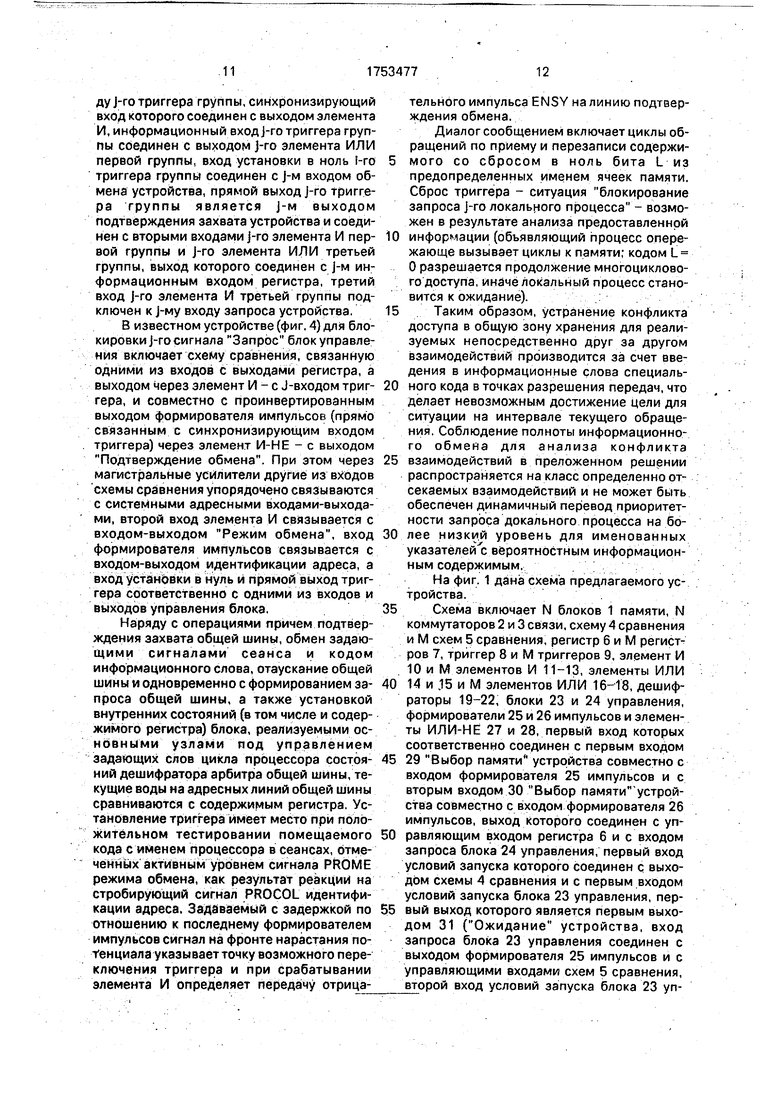

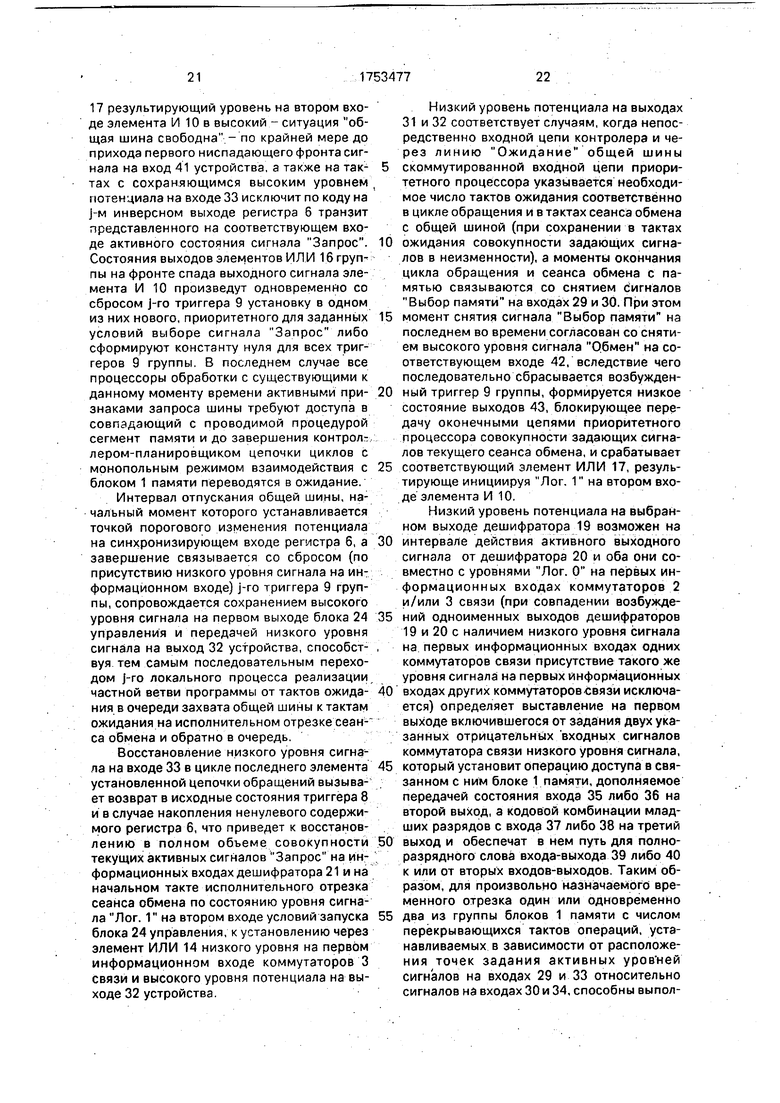

На фиг. 1 дана схема известного устройства.

Схема прототипа (фиг. 1) содержит N блоков 1 памяти, коммутаторов 2 и 3 связи, дешифраторы 4 и 5, блоки 6 и 7 управления, формирователи 8 и 9 импульсов, элементы ИЛИ-НЕ 10 и 11 и схему 12 сравнения, управляющий вход которой соединен с входом нулевого потенциала устройства, выход соединен с первыми входами условий запуска блока 6 управления и блока 7 управления, первый выход которых является соответственно первым 13 и вторым 14 выходами Ожидание устройства, вход запроса блоков 6 и 7 управления соединен соответственно с выходом формирователя 8 или 9 импульсов, первые информационный вход и второй информационный вход схемы 12 сравнения соединены соответственно с первым входом 15 Адрес и с вторым входом 16 Адрес старших разрядов устройства совместно с информационными входами дешифраторов 4 и 5, i-e выходы которых соединены с управляющим входом соответственно 1-го первого коммутатора 2 связи и 1-го второго коммутатора 3 связи, которые первым информационным входом соединены соответственно с вторыми выходами блоков 6 и 7 управления, вторым информационным входом соединены соответственно с первым входом 17 Чтение-запись и вторым входом 18 Чтение-запись и вторым входом 18 Чтение-запись и вторым входом 18 Чтение-запись устройства, третьим информационным входом соединены соответственно с одноименными позициями первого входа 15 Адрес и второго входа 16 Адрес младших разрядов устройства, а первым входом-выходом - с одноименными позициями первого входа-выхода 19 Данные и второго входа- выхода 20 Данные 20 устройства. Вход формирователя 8 импульсов соединен с первым входом 21 Выбор памяти устройства и с первым входом элемента ИЛИ-НЕ 10, вход формирователя 9 импульсов соединен с вторым входом 22 Выбор памяти устройства и с первым входом элемента ИЛИ-НЕ 11, выход элементов ИЛИ-НЕ 10 и 11 соединен с вторым входом условий запуска соответственно блоков 6 и 7 управления совместно с вторым входом элемента ИЛИ- НЕ 11 и элемента ИЛИ-НЕ 10, а i-й блок 1 памяти соединен первым входом обращения с первым выходом соответствующего коммутатора 2 связи, вторым входом обращения - с первым выходом соответствующего коммутатора 3 связи, первым входом чтения-записи - с вторым выходом соответствующего коммутатора 2 связи, вторым входом чтения-записи - с вторым выходом соответствующего коммутатора 3 связи, первым адресным входом - с одноименными позициями третьего выходам соответствующего коммутатора 2 связи, вторым адресным входом - с одноименными позициями третьего выхода соответствующего коммутатора 3 связи, первым информационным входом-выходом - с одноименными

позициями второго входа-выхода соответствующего коммутатора 2 связи и вторым ин- формационным входом-выходом - с одноименными позициями второго входа- выхода соответствующего коммутатора 3 связи.

Двоичные состояния кодовых комбинаций, поступающих на входы 15, 17 и 21, устанавливаются уровнями задающих сиг0 налов, например, цепей контроллера планирования частных задач, а на входах 16, 18 и 22 - от линий стандартной шины, связывающей процессоры обработки (не показаны) Прототип работает следующим обра

5 зом.

При обращении к памяти каждый процессор обработки производит операции с шиной и, получив подтверждение на захват, устанавливает на многопозиционном входе

0 16 код, на входе 18 - состояние, определяющее направление передачи информации (с входа-выхода 20 в блок 1 памяти для Лог. О, из блока на вход-выход 20 для Лог. 1 последнего), а на входе 22 - задающий сиг5 нал низкого уровня потенциала, интерпретирующий указанный код в качестве адреса ячейки.

Для начинающего обращения код адреса старших разрядов с входа 16 воздейству0 ет на информационный вход дешифратора 5 и на второй информационный вход схемы 12 сравнения, устанавливая один из уровней счигнала на выходе ее и производя инициализацию (выставление низкого уровня на

5 выходе) определенного выхода дешифратора 5. Установление сигнала Выбор памяти на входе 22 приводит к срабатыванию формирователя 9 импульсов и при Лог. О на выходе элемента ИЛИ-НЕ 10 к появлению

0 Лог. 1 на выходе элемента ИЛИ-НЕ 11. Этот уровень независимо от состояния выхода схемы 12 сравнения определит собой подтверждение действия выского уровня сигнала на выходе 14 устройства и прекра5 щение действия высокого уровня на втором выходе блока 7 управления - ситуация доступ к памяти - на интервале активного состояния (Лог. О сигнала) на входе запроса блока 7 управления.

0 Другим определяющим уровнем, однозначно влекущим за собой беспрепятственное установление ситуации доступ к памяти, является сигнал Лог 1 на выходе схемы схемы 12 сравнения.

5 В цикле обращения, в случае одновременного присутствия Лог. О на обоих входах условий запуска блока 7 управления (для другого обращения, вызванного заданием инициализирующего сигнала на входе 21 блока 6 управления) - результат присутствия идентичных кодовых комбинаций на одноименных позициях первого и второго информационных входов схемы 12 сравнения при установлении сигнала Выбор памяти на интервале продолжающегося доступа к памяти от запроса на симметричном входе 21 (22) - блок 7 управления (6) оказывается заблокированным и на первом выходе его будет выставлен уровень Лог. О, а на втором выходе - уровень Лог. 1.

Сигнал Лог. О воздействует на первые информационные входы коммутаторов 3 связи и в 1-м на них с установленным низким уровнем сигнала на управляющем входе собственно определит выставление Лог. О на второй вход обращения передачи кодовой комбинации позиций входа 16 младших разрядов на второй адресный вход, а состояния входа 18 - на второй вход чтения-записи hro блока 1 памяти, задав при этом поступление данных с входа-выхода 20 на второй информационный вход-выход блока либо в противоположном направлении соответственно состоянию на втором информационном входе коммутатора 3 связи.

Продолжительность цикла обращения связывается с состоянием сигнала Ожидание, который активным (низким) уровнем на выходе 14(13) укажет через линию общей шины процессору обработки (непосредственно контроллеру планировщику заданий и ввода-вывода) необходимое число тактов ожидания при сохранении в этих тактах совокупности задающих сигналов в неизменности. Момент окончания цикла определяется приоритетным процессором обработки посредством снятия с Сгнала Выбор памяти на входе 22 (соответственно контроллером через вход 21), вследствие чего последовательно переключаются формирователь 9(8) импульсов и блок 7(6) управления, закрывая 1-й коммутатор 3(2) связи, и восстанавливается низкий уровень сигнала на выходе элемента ИЛИ-НЕ 11(10),

В отсутствии любого из симметричных обращений к памяти оба сигнала входов 21 и 22 находятся в состоянии Лог. 1 и обеспечивают через первые входы одновременное присутствие Лог. О на выходах элементов ИЛИ-НЕ 10 и 11. Опережающее изменение одного из сигналов Выбор памяти совместно с сохранением ЛОг. О на втором входе элемента ИЛИ-НЕ вызовет передачу Лог. 1 на его выход, которая сохранится на всем интервале обращения и обеспечит Лог. О на выходе другого плеча в связке двух элементов ИЛИ-НЕ 10 и 11.

Восстановление на выходе элемента ИЛИ-НЕ 10 уровня Лог. О на интервале задержанного обращения по активному сигналу Выбор памяти с входа 22 создает условия формирования на выходе элемента ИЛИ-НЕ 11 уровня Лог. 1 и предоставляет в ситуациях одновременно либо с неболь5 шим смещением во времени существующих обращений к ячейкам, расположенным в одном и том же блоке 1 памяти, чередующиеся доступы в ту же самую область хранения от совокупностей активных уровней сигналов

0 на симметричных входах 15, 17, 21 и 16, 18, 22.

Указанный режим коммутации в доступах к памяти, устанавливаемых по уровням задающих сигналов от входов 15, 17 и 21,

5 выполняется аналогично.

При динамическом распределении программных сегментов (когда свободные процессоры самостоятельно назначают себе для реализации готовые к исполнению вет0 ви общей программы в отсутствие принудительной синхронизации текущих обменов) допустима ситуация, при которой блок управления сегментированной памятью получает следующую одновременно либо

5 непосредственно друг за другом пару обращений в совпадающую область памяти, одно из которых сформировано независимо от условий возможного конфликта доступа из имеющейся совокупности запросов локаль0 ных процессов.

Недостатком прототипа является невысокое быстродействие при динамическом назначении локальными процессами программных сегментов, поскольку текущие ус5 ловия для возможного предотвращения конфликта по обращениям в пересекающиеся области памяти при назначении приоритета запросов в одном из асинхронных потоков информационных обменов не могут

0 быть учтены и использование монопольного режима в каких-либо сеансах обмена для другого потока затруднительно.

Целью изобретения является повышение быстродействия.

5 Поставленная цель достигается тем, что в устройство управления сегментированной памятью многопроцессорной системы, содержащее группу блоков памяти, две группы коммутаторов связи, два дешифратора,

0 два блока управления, два формирователя импульсов, два элемента ИЛИ-НЕ и схему сравнения, выход которой подключен к первым входам условий запуска первого и второго блоков управления, первые выходы

5 первого и второго блоков управления подключены соответственно к первому и второму выходам ожидания устройства, входы запроса первого и второго блоков управления соединены соответственно с выходом дервого и второго формирователя импульсов, входы которых соединены соответственно с первыми входами первого и второго элементов ИЛИ-НЕ и соответственно с первым и вторым входами выбора памяти устройства, выход первого элемента ИЛИ-НЕ подключен к второму входу условий запуска первого блока управления и к второму входу второго элемента ИПИ-НЕ, выход второго элемента ИЛИ-НЕ подключен к второму входу условий запуска второго блока управления и к второму входу первого элемента ИЛИ-НЕ, первый информационных вход схемы сравнения соединен с первым адресным входом старших разрядов устройства и с информационным входом первого дешифратора, i-й выход которого соединен с управляющим входом i-ro коммутатора связи первой группы (i 1, N, N- количество сегментов памяти), второй выход первого блока управления, первый вход чтения-записи устройства, первый адресный вход младших разрядов устройства и первый вход-выход данных устройства подключены соответственно к первому, второму, третьему информационным входам и первому входу-выходу коммутаторов связи первой группы, первой, второй, третий выходы и второй вход-выход i-ro коммутатора связи первой группы подключены соответственно к первому входу обращения, первому входу чтения-записи, первому адресному входу и первому информационному входу-выходу i-ro блока памяти группы, второй информационный вход схемы сравнения соединен с вторым адресным входом старших разрядов устройства и с информационным входом второго дешифратора, 1-й выход которого соединен с управляющим входом 1-го коммутатора связи второй группы, первые информационные входы коммутаторов связи второй группы соединены между собой, второй вход чтения-записи устройства, второй адресный вход младших разрядов устройства и второй вход-выход данных устройства подключены соответственно к второму, третьему информационным входам и первому входу-выходу коммутаторов связи второй группы,первый, второй и третий выходы и второй вход-выход i-ro коммутатора связи второй группы подключены соответственно к второму входу обращения, второму входу чтения-записи, второму адресному входу и второму информационному входу-выходу 1-го блока памяти группы, дополнительно введены группа регистров, группа триггеров, две группы элементов И, три группы элементов ИЛИ, группа схем сравнения, регистр, триггер, два дешифратора, элемент И, два элемента ИЛИ, причем первые информационные входы схем сравнения

группы соединены с первым адресным входом старших разрядов устройства, управляющие входы схем сравнения группы соединены с входом запросов первого бло- 5 ка управления, второй выход которого подключен к входу синхронизации триггера, соединенного информационным входом с входом нулевого потенциала устройства, входом установки в единицу с входом при0 оритетного обмена устройства и с входом установки в ноль регистра, инверсный выход триггера соединен с третьим входом второго элемента ИЛИ-НЕ, второй информационный вход j-й схемы сравнения груп5 пы соединен с выходом j-ro регистра группы (j 1, М, М - количество источников, передаваемых для обмена слов), подключенного синхронизирующим входом к входу синхронизации устройства и к первому входу эле0 мента И, информационный вход j-ro регистра группы подключен к второму входу-выходу данных устройства, управляющий вход j-ro регистра группы подключен к выходу j-ro элемента И первой группы, пер5 вый вход которого соединен с входом режима обмена устройства, с управляющим входомосхемы сравнения и в первым входом первого элемента ИЛИ, выход и второй вход которого соединены соответственно с

0 первым информационным входом 1-го коммутатора связи второй группы и с вторым выходом второго блока управления, вход запроса и третий выход которого соединены соответственно с синхронизирующим и с

5 управляющим входами регистра, выход j-й схемы сравнения группы соединен с первым входом j-ro элемента И второй группы, выход которого соединен с j-м информационным входом третьего дешифратора, j-й

0 выход которого подключен к j-му входу второго элемента ИЛИ и к первому входу j-ro элемента ИЛИ первой группы, выход второго элемента ИЛИ соединен со стробирую- щим входом четвертого дешифратора,

5 второй вход j-ro элемента И второй группы соединен с Jv информационным входом четвертого дешифратора, j-й выход которого подключен к второму входу j-ro элемента ИЛИ первой группы, и с выходом j-ro эле0 мента И третьей группы, первый вход которого подключен к J-му инверсному выходу регистра, j-й прямой выход которого соединен с первыми входами j-x элементов ИЛИ второй и третьей групп, второй вход j-ro

5 элемента И третьей группы подключен к второму входу j-ro элемента ИЛИ второй группы, выход которого соединен с вторым входом элемента И и по схеме открытого коллектора подключен к входу высокого потенциала устройства, и к инверсному выходу J-ro триггера группы, синхронизирующий вход которого соединен с выходом элемента И, информационный вход j-ro триггера группы соединен с выходом J-ro элемента ИЛИ первой группы, вход установки в ноль 1-го триггера группы соединен с J-м входом обмена устройства, прямой выход j-ro триггера группы является j-м выходом подтверждения захвата устройства и соединен с вторыми входами j-ro элемента И первой группы и J-ro элемента ИЛИ третьей группы, выход которого соединен с j-м информационным входом регистра, третий вход j-ro элемента И третьей группы подключен к j-му входу запроса устройства.

В известном устройстве (фиг, 4) для блокировки j-ro сигнала Запрос блок управления включает схему сравнения, связанную одними из входов с выходами регистра, а выходом через элемент И - с J-входом триггера, и совместно с проинвертированным выходом формирователя импульсов (прямо связанным с синхронизирующим входом триггера) через элемент И-НЕ - с выходом Подтверждение обмена. При этом через магистральные усилители другие из входов схемы сравнения упорядочено связываются с системными адресными входами-выходами, второй вход элемента И связывается с входом-выходом Режим обмена, вход формирователя импульсов связывается с входом-выходом идентификации адреса, а вход установки в нуль и прямой выход триггера соответственно с одними из входов и выходов управления блока.

Наряду с операциями причем подтверждения захвата общей шины, обмен задающими сигналами сеанса и кодом информационного слова, отаускание общей шины и одновременно с формированием запроса общей шины, а также установкой внутренних состояний (в том числе и содержимого регистра) блока, реализуемыми основными узлами под управлением задающих слов цикла процессора состояний дешифратора арбитра общей шины, текущие воды на адресных линий общей шины сравниваются с содержимым регистра. Установление триггера имеет место при положительном тестировании помещаемого кода с именем процессора в сеансах, отмеченных активным уровнем сигнала PROME режима обмена, как результат реакции на стробирующий сигнал PROCOL идентификации адреса. Задаваемый с задержкой по отношению к последнему формирователем импульсов сигнал на фронте нарастания потенциала указывает точку возможного переключения триггера и при срабатывании элемента И определяет передачу отрицательного импульса ENSY на линию подтверждения обмена.

Диалог сообщением включает циклы обращений по приему и перезаписи содержимого со сбросом в ноль бита L из предопределенных именем ячеек памяти. Сброс триггера - ситуация блокирование запроса j-ro локального процесса - возможен в результате анализа предоставленной

0 информации (объявляющий процесс опережающе вызывает циклы к памяти; кодом L О разрешается продолжение многоциклового доступа, иначе локальный процесс становится к ожидание).

5 Таким образом, устранение конфликта доступа в общую зону хранения для реализуемых непосредственно друг за другом взаимодействий производится за счет введения в информационные слова специаль0 ного кода в точках разрешения передач, что делает невозможным достижение цели для ситуации на интервале текущего обращения. Соблюдение полноты информационного обмена для анализа конфликта

5 взаимодействий в преложенном решении распространяется на класс определенно отсекаемых взаимодействий и не может быть обеспечен динамичный перевод приоритетности запроса докального процесса на бо0 лее низкий уровень для именованных указателей с вероятностным информационным содержимым.

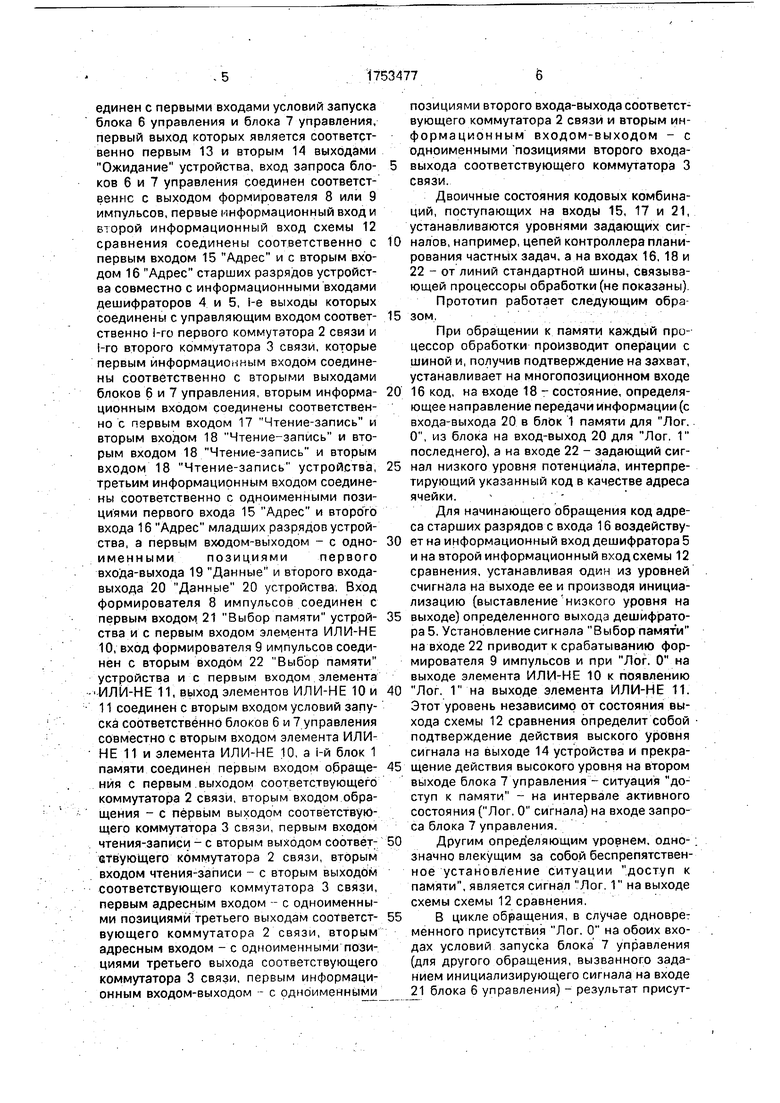

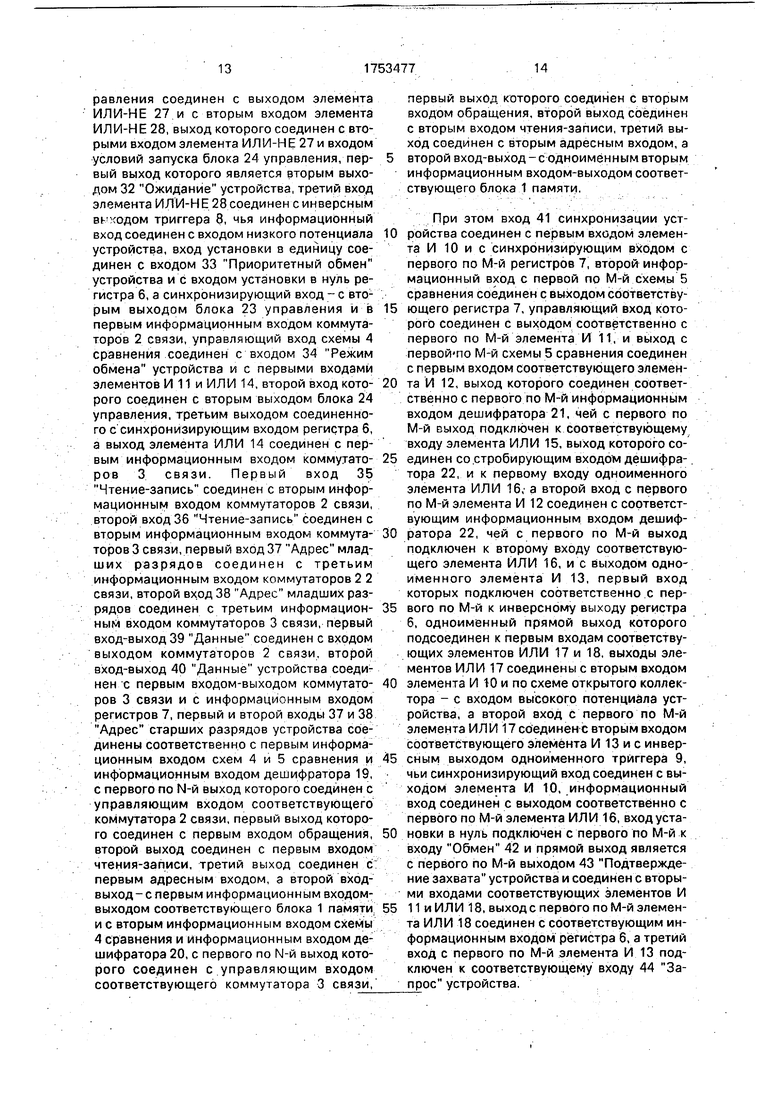

На фиг. 1 дана схема предлагаемого устройства.

5 Схема включает N блоков 1 памяти, N коммутаторов 2 и 3 связи, схему 4 сравнения и М схем 5 сравнения, регистр 6 и М регистров 7, триггер 8 и М триггеров 9, элемент И 10 и М элементов И 11-13, элементы ИЛИ

0 14 и „15 и М элементов ИЛИ 16-18, дешифраторы 19-22, блоки 23 и 24 управления, формирователи 25 и 26 импульсов и элементы ИЛ И-НЕ 27 и 28, первый вход которых соответственно соединен с первым входом

5 29 Выбор памяти устройства совместно с входом формирователя 25 импульсов и с вторым входом 30 Выбор памяти устройства совместно с входом формирователя 26 импульсов, выход которого соединен с уп0 равляющим входом регистра бис входом запроса блока 24 управления, первый вход условий запуска которого соединен с выходом схемы 4 сравнения и с первым входом условий запуска блока 23 управления, пер5 вый выход которого является первым выходом 31 (Ожидание устройства, вход запроса блока 23 управления соединен с выходом формирователя 25 импульсов и с управляющими входами схем 5 сравнения, второй вход условий запуска блока 23 управления соединен с выходом элемента ИЛИ-НЕ 27 и с вторым входом элемента ИЛИ-НЕ 28, выход которого соединен с вторыми входом элемента ИЛИ-НЕ 27 и входом условий запуска блока 24 управления, первый выход которого является вторым выходом 32 Ожидание устройства, третий вход элемента ИЛИ-НЕ 28 соединен с инверсным вь- содом триггера 8, чья информационный вход соединен с входом низкого потенциала устройства, вход установки в единицу соединен с входом 33 Приоритетный обмен устройства и с входом установки в нуль регистра 6, а синхронизирующий вход - с вторым выходом блока 23 управления и в первым информационным входом коммутаторов 2 связи, управляющий вход схемы 4 сравнения соединен с входом 34 Режим обмена устройства и с первыми входами элементов И 11 и ИЛИ 14, второй вход которого соединен с вторым выходом блока 24 управления, третьим выходом соединенного с синхронизирующим входом регистра б, а выход элемента ИЛИ 14 соединен с первым информационным входом коммутаторов 3 связи. Первый вход 35 Чтение-запись соединен с вторым информационным входом коммутаторов 2 связи, второй вход 36 Чтение-запись соединен с вторым информационным входом коммутаторов 3 связи, первый вход 37 Адрес младших разрядов соединен с третьим информационным входом коммутаторов 2 2 связи, второй вход 38 Адрес младших разрядов соединен с третьим информационным входом коммутаторов 3 связи, первый вход-выход 39 Данные соединен с входом выходом коммутаторов 2 связи, второй вход-выход 40 Данные устройства соединен с первым входом-выходом коммутаторов 3 связи и с информационным входом регистров 7, первый и второй входы 37 и 38 Адрес старших разрядов устройства соединены соответственно с первым информационным входом схем 4 и 5 сравнения и информационным входом дешифратора 19, с первого по N-й выход которого соединен с управляющим входом соответствующего коммутатора 2 связи, первый выход которого соединен с первым входом обращения, второй выход соединен с первым входом чтения-записи, третий выход соединен с первым адресным входом, а второй вход- выход-с первым информационным входом- выходом соответствующего блока 1 памяти и с вторым информационным входом схемы 4 сравнения и информационным входом дешифратора 20, с первого по N-й выход которого соединен с управляющим входом соответствующего коммутатора 3 связи,

первый выход которого соединен с вторым входом обращения, второй выход соединен с вторым входом чтения-записи, третий выход соединен с вторым адресным входом, а второй вход-выход-с одноименным вторым информационным входом-выходом соответствующего блока 1 памяти.

При этом вход 41 синхронизации устройства соединен с первым входом элемента И 10 и с синхронизирующим входом с первого по М-й регистров 7, второй информационный вход с первой по М-й схемы 5 сравнения соединен с выходом соответствующего регистра 7, управляющий вход которого соединен с выходом соответственно с первого по М-й элемента И 11, и выход с первой по М-й схемы 5 сравнения соединен с первым входом соответствующего элемента И 12, выход которого соединен соответственно с первого по М-й информационным входом дешифратора 21, чей с первого по М-й выход подключен к соответствующему входу элемента ИЛИ 15, выход которого соединен со стробирующим входом дешифратора 22, и к первому входу одноименного элемента ИЛИ 16, а второй вход с первого по М-й элемента И 12 соединен с соответствующим информационным входом дешифратора 22, чей с первого по М-й выход подключен к второму входу соответствующего элемента ИЛИ 16, и с выходом одноименного элемента И 13, первый вход которых подключен соответственно с первого по М-й к инверсному выходу регистра б, одноименный прямой выход которого подсоединен к первым входам соответствующих элементов ИЛИ 17 и 18, выходы элементов ИЛИ 17 соединены с вторым входом

элемента И 10 и по схеме открытого коллектора - с входом высокого потенциала устройства, а второй вход с первого по М-й элемента И Л И 17 соединен с вторым входом соответствующего элемента И 13 и с инверсным выходом одноименного триггера 9, чьи синхронизирующий вход соединен с выходом элемента И 10, информационный вход соединен с выходом соответственно с первого по М-й элемента ИЛИ 16, входустановки в нуль подключен с первого по М-й к входу Обмен 42 и прямой выход является с первого по М-й выходом 43 Подтверждение захвата устройства и соединен с вторыми входами соответствующих элементов И

11 и ИЛ И 18, выход с первого по М-й элемента ИЛИ 18 соединен с соответствующим информационным входом регистра 6, а третий вход с первого по М-й элемента И 13 подключен к соответствующему входу 44 Запрос устройства.

N блоков 1 памяти хранит наряду с ин: формационными блоками управляющих программ и таблиц системы совокупность информационных блоков данных и программ, представляющих собой очередь готовых к реализации задач общего задания,

Параметр N группы задается исходя из количества сегментов, которыми представляется общее поле хранения информации, а М - из числа включаемых в систему процессоров обработки.

Содержимое отдельного регистра 7 группы определяет номер блока 1 памяти, логически связываемого на текущем интервале обработки с приписанным по месту (с первого по М) локальным процессом обработки частной задачи.

Двоичные состояния кодовых комбинаций, поступающих на входы 29, 33, 35 и 37, устанавливаются уровнями задающих сигналов, например цепей контроллера планировщика частных задач, а на входы 30, 34, 36 и 38 - от линий общей шины, используемой процессорами обработки (не показаны) системы.

Предлагаемое устройство работает следующим образом.

В процессе реализации частных задач общего задания допустима ситуация, когда очередная ветвь программы из числа пассивных задач может быть переведена в разряд активных и информационный блок многоцикловой процедурой планировщика распределяется в заданный модуль памяти, Доступ последней в память организуется так, что отдельная цепочка циклов и, в частности, обмен в целом представляются неразрывной операцией обращения.

При всяком обращения контроллер ус- таналивает на многоразрядном входе 37 код, на входе 35-состояние, определяющее направление передачи информации (с входа-выхода 39 и блок 1 памяти - для сигнала Лог. О, из блока на вход выход 39 для Лог. 1 последнего), а на входе 29 - задающий сигнал низкого уровня потенциала, интерпретирующий указанный код в качестве адреса ячейки.

Для начинающегося обращения код адреса старших разрядов с входа 37 воздействует на информационный вход дешифратора 19, а также на первые информационные входы схем 4 и 5 сравнения, производя инициализацию (формирование низкого уровня сигнала на определенном выходе) указанного дешифратора и допуская на интервале присутствие пассивного (низкого) уровня сигнала на входе 34 для одной и возбуждения выхода формирователя 25 импульсов для других, установление

произвольных уровней на выходах - код Лог. О, определяется идентичностью состояний первых и вторых информационных входов - схем сравнения, задав код указателя конфликтности одновременных симметричных обращений (второе обращение - по условиям инициализации входов 30 и 38) и многопозиционную маскирующую константу приоритетности активных приемников0 источников общей шины.

Установление сигнала Выбор памяти на входе 29 воздействует на формирователь 25 импульсов и вызывает в точке, сдвинутой на задержку т (достаточную для фиксации

5 стабильного кода указателя конфликтности) от фронта спада входного уровня, на выходе формирователя импульсов сигнал низкого уровня, что при наличии Лог. 1 на выходе схемы 4 сравнения либо элемента

0 ИЛИ-НЕ27 приводит к срабатыванию блока 23 управления и передаче им низкого уровня сигнала на первые информационные входы коммутаторов 2 связи группы и на синхронизирующий вход триггера 8, наряду

5 с сохранением высокого уровня сигнала на выходе 31 устройства.

В описываемом цикле одновременное присутствие Лог. О на обоих входах условий запуска - ситуация назначения указан0 ным обращением совпадающего сегмента памяти на интервале продолжающегося или подготовленного доступа к блоку 1 памяти с входов 30 и 38 - при установлении низкого уровня на входе запроса блокирует блок 23

5 управления и переводит состояние первого выхода блока в Лог, 0 с фиксацией ранее присутствующего высокого уровня на втором выходе его.

Присутствие в совокупности задающих

0 сигналов цикла активного, т,е. высокого, уровня на выходе 33 для ранжирования симметричных обращений (приводящего к запрету доступа с разделением во времени фоновых обращений в совпадающий сег5 мент памяти) с целью непревышения допустимой величины ожидания для каждого элемента цепочки запросов и пресечения повторных операций над содержимым ячейки памяти в программной реализации функ0 ции защиты с помощью механизма семафоров, снятием запрещающего сигнала на входе установки в единицу допускает в точке спада высокого потенциала на втором выходе блока 23 управления переклю5 чение (по заданию константы нуля на информационном входе) в нулевое либо подтверждение нулевого состояния триггера 8.

В отсутствие любого из симметричных обращений к памяти или для сигнала Лог.

1 на входе 29 на интервале обнуленного триггера 8 обеспечивается через первые входы или через первый вход элемента ИЛ И-НЕ 27 и третий вход элемента ИЛ И-НЕ 28 одновременное присутствие Лог. О на их выходах. В дальнейшем, опережающее изменение к уровню Лог 0 одного из сигналов Выбор памяти совместно с сохрэне- н -эм Лог. О на втором входе элементов ИЛИ-НЕ 27 и 28 либо безусловно низкое состояние входа 29 на интервале обнуленного триггера 8 вызовет передачу Лог. 1 как признака предпочтительности доступа на выход соответствующего из элементов либо во втором случае на выход элемента ИЛИ-НЕ 27, которая сохранится на протяжении всего цикла и обеспечит присутствие Лог. О на выходе другого из связки элементов ИЛИ-НЕ 27 и 28

Восстановление на выходе одного из элементов ИЛИ-НЕ 27 или 28 уровня Лог. О при единичном состоянии триггера 8 создает условие на интервале прдолжающего- ся и симметричного к завершившемуся на входе 29 либо 30 активного сигнала Выбор памяти для формирования Лог. 1 на выходе невозбужденного ранее элемента ИЛИ-НЁ и в ситуациях исчезающего или периодически устанавливаемого уровня Лог. О на выходе схемы 4 сравнения представляет возможность для поочередного доступа в один и тот же блок 1 памяти для одновременно выставляем ix обоих сигналов Выбор памяти

Выставление высокого уровня потенциала на одном из (например j-м) выходе 43 для .разрешения оконченным цепям соответствующего процессора обработки коммутации внутренних его состояний на входы 30, 34, 36 и 38 устройства с целью монопольного доступа предворено, в отражение к сформированному на тактах задания низкого потенциала на выходе формирователя 25 иммульсов параллельному слову маскирующей константы, код в позиции с первой по М-ю которой установлен в зависимости от совпадения (нуль) связанного текущим доступом процедуры планировщика заданий номера блока 1 памяти с соответствующим именем подобласти памяти для обращений по месту от частной ветви программы обработки (процедурно допустимы представления отдельных операндов-приемников/источников в подобластях памяти, отличных от заявляемых именами ветвей), распознаванием в представленной совокупности активных сигналов на входах 44 группы запросов с предпочтением и резервируется осуществлением сброса выставленного сиг нала Подтверждение захвата в точках временного отрезка по действующему адресу реализуемого сеанса обмена процессором обработки инициируется доступ в

уже взаимодействующий по привилегиро ванному каналу с неразрывной цепочкой обменов блок 1 памяти, с последующим переводом j-ro процесса обработки ветви программы в ожидание.

0В отсутствие цикла обращения в j-м процессоре обработки пассивный сигнал (например, Лог. О) на соответствующем входе 42 утерживает j-й триггер 9 группы в нулевом состоянии Формируемый уровень

5 Лог 1 на втором входе одноименного элемента ИЛИ 17 группы допускает установление произвольного уровня одновременность присутствия условий передачи на выход состояний Лог. 1 во всех

0 элементах ИЛИ 17 группы сохранит Лог. 1 на обьединенном по схеме с открытым коллектором их выходе, иначе сформируется Лог. О на втором входе элемента И 10. Вхождение в цикл обращения к систе5 мой памяти для j-ro процессора обработки, наряду со снятием низкого уровня сигнала Обмен, сопровождается формированием потенциала высокого уровня на соответствующем входе 44. Появление высокого уров0 ня сигнала на третьем входе j-ro элемента И 13 группы на отрезке присутствия уровня Лог, 1 на инверсном выходе триггера 9 и на инверсном выходе регистра 6 этих же позиций групп вызываются передачу состо5 яния Лог 1 на соответствующий информационный вход дешифратора 22 и, при срабатывании (по несовпадению кодов информационных входов j-й схемы 5 сравнения группы) соответствующего элемента И

0 12 - на j-й информационный вход дешифратора 21. Таким образом идентификация содержимого одного из регистров 7 группы с текущим кодом старших разрядов на входе 37 вызовет исключение активного сигнала

5 на соответствующем информационном входе дешифратора 21 при сохранении его на одноименном информационном входе дешифратора 22.

Модифицированная маскирующей

0 константой приоритетности ненулевая кодовая комбинация входных сигналов дешифратора 21, инициируя его, вызывает формирование Лог. 1 на определенном выходе и передачей посредством элемента

5 ИЛИ 15 высокого уровня на стробирующий вход дешифратора 22 блокирует последний с сохранением уровней Лог. О на всех его выходах. Присутствие нулевой комбинации входных сигналов в дешифраторе 21 связывается с текущим кодом нуля его выходных

сигналов и способствует по условиям срабатывания цепочки элемент ИЛИ 15 - дешифратор 22 формированию Лог. 1 на одном из выходов последнего, что делает двоичный код выходов дешифратора 22 определяющим при передаче уровня Лог. 1 на выход одним из элементов ИЛИ 16 группы.

Лог, 1 на выходе j-ro элемента ИЛИ 16 на интервале установления высокого уровня на втором входе элемента И 10 в точке изменения сигнала на входе 41 от высокого к низкому уровню потенциала определит собой возбуждение соответствующего триггера 9 группы с последующими формированиями активного уровня на j-м выходе 43 устройства и результирующего совместно с ранее установленными позиционными отметками Лог, 1 в регистре 6 кода на информационных входах указанного регистра. Единичным состоянием j-ro триггера 9 обеспечиваются подготовка к положительной реакции на сигнал высокого уровня извне по входу 34 одноименным элементом И 11 группы, а также запрет прохождения соответствующего активного сигнала Запрос через j-й элемент И 13 группы и перевод по состоянию второго входа J-ro элемента ИЛИ 17 группы (Лог. О на первом входе j-ro элемента ИЛИ 17 перед и при вхождении в очередной сеанс обмена является одним из определяющих условий для конечной передачи активного сигнала j-м элементом ИЛИ 16) уровня сигнала на втором входе элемента И 10 в низкий.

Ответно высокому уровню сигнала на j-м входе 43 на линии общей шины вызываются код адресного слова, управляющие по- тенциалы текущего сеанса обмена и коммутируется путь прохождения слова данных согласно назначениям задающего цикла локального процесса.

В назначаемых кодовых комбинациях, поступающих на входы 30 и 36 с задержкой h г (обеспечивается условием включения оконечного коммутатора в процессоре обработки), а на входы 34 и 38 - непосредственно вслед за выставлением стробирующего сигнала, функции состояний сигналов первого из указанных входов аналогичны описанным для входа 29, а второго и последнего - для входов 35 и 37.

Реализация программ частных задач сочетается с записями кодов указателей блоков 1 памяти. Группа текущих указателей памяти системы информационно связывается с номерами локальных процессов незавершенных ветвей общего задания.

Для записи информации в j-й регистр 7 группы на входе 34 задается высокий уровень сопровождающего сигнала цикла, а на

входе-выходе 40 - код указателя, Уровень Лог, 1 на управляющем входе схемы 4 сравнения своим появлением безусловно устанавливает высокий уровень сигнала на

первых входах условий запуска блоков 23 и 24 управления, что подтвердит по цепочке ранее присутствующие высокий уровень на выходе 32 устройства и низкий уровень потенциала на управляющем входе регистра 6.

0 Присутствие низкого уровня потенциала на управляющем входе регистра 6 удержит его и режиме Хранение, а формируемый также на первом выходе блока 24 управления уровень Лог. О (при вхождении в интервал

5 задания формирователем импульсов 26 активного выходного сигнала) маскируется при передаче определяющего уровня сигнала на первые информационные входы коммутаторов 3 связи группы уровнем Лог. 1

0 на первом входе элемента ИЛИ 14. Таким образом, адресация записываемого слова указателя реализуется собственно срабатыванием по присутствию уровня Лог. 1) на первом входе соответствующего элемента

5 И 11 группы, вследствие чего на управляющий вход одноименного регистра 7 передается высокий уровень потенциала и по первому пришедшему фронту спада синхросигнала на входе 41 содержимое вход 41

0 содержимое входа-выхода 40 устройства копируется в J-м регистре 7, замещая в нем ранее используемую информацию об имени блока 1 памяти с минимальной (без дополнительных тактов ожидания) длительностью

5 сеанса обмена.

Для начинающегося сеанса обмена в сопровождении низкого уровня потенциала на входе 34, при сформированном уровне Лог. О на первых входах условий запуска

0 блоков 23 и 24 управления и удержании уровня Лог. О на выходе элемента ИЛИ-НЕ 28, с опережением на время т к фронту спада выходного сигнала формирователя 26 импульсов устанавливается высокий уро5 вень потенциала на третьем выходе блока 24 управления, что приводит совместно с уровнем Лог. 1 на входе установки в нуль регистра 6 в точке установления указанного фронта сигнала к фиксации в j-й позиции

0 содержимого регистра 6 отметки Лог, 1 активизированного триггера 9 группы с сохранением в других позициях регистра ранее представленной информации.

Установление уровня Лог. 1 на j-м пря5 мом выходе регистра 6 опережающе к точке сброса единичного состояния в одноименном триггере 9 группы (вследствие изменения уровня сигнала на его информационном входе) переведет посредством переключившегося по первому входу j-ro элемента ИЛИ

17 результирующий уровень на втором входе элемента И 10 в высокий - ситуация общая шина свободна - по крайней мере до прихода первого ниспадающего фронта сигнала на вход 41 устройства, а также на тактах с сохраняющимся высоким уровнем потенциала на входе 33 исключит по коду на j-м инверсном выходе регистра б транзит представленного на соответствующем входе активного состояния сигнала Запрос. Состояния выходов элементов И Л И 16 группы на фронте спада выходного сигнала элемента И 10 произведут одновременно со сбросом j-ro триггера 9 установку в одном из них нового, приоритетного для заданных условий выборе сигнала Запрос либо сформируют константу нуля для всех триггеров 9 группы. В последнем случае все процессоры обработки с существующими к данному моменту времени активными признаками запроса шины требуют доступа в совпадающий с проводимой процедурой сегмент памяти и до завершения контроллером-планировщиком цепочки циклов с монопольным режимом взаимодействия с блоком 1 памяти переводятся в ожидание.

Интервал отпускания общей шины, начальный момент которого устанавливается точкой порогового изменения потенциала на синхронизирующем входе регистра 6, а завершение связывается со сбросом (по присутствию низкого уровня сигнала на информационном входе) j-ro триггера 9 группы, сопровождается сохранением высокого уровня сигнала на первом выходе блока 24 управления и передачей низкого уровня сигнала на выход 32 устройства, способствуя тем самым последовательным переходом j-ro локального процесса реализации частной ветви программы от тактов ожидания в очереди захвата общей шины к тактам ожидания на исполнительном отрезке сеан- са обмена и обратно в очередь.

Восстановление низкого уровня сигнала на входе 33 в цикле последнего элемента установленной цепочки обращений вызывает возврат в исходные состояния триггера 8 и в случае накопления ненулевого содержимого регистра 6, что приведет к восстановлению в полном объеме совокупности текущих активных сигналов Запрос на информационных входах дешифратора 21 и на начальном такте исполнительного отрезка сеанса обмена по состоянию уровня сигнала Лог. 1 на втором входе условий запуска блока 24 управления, к установлению через элемент ИЛИ 14 низкого уровня на первом информационном входе коммутаторов 3 связи и высокого уровня потенциала на выходе 32 устройства

Низкий уровень потенциала на выходах 31 и 32 соответствует случаям, когда непосредственно входной цепи контролера и через линию Ожидание общей шины скоммутированной входной цепи приоритетного процессора указывается необходимое число тактов ожидания соответственно в цикле обращения и в тактах сеанса обмена с общей шиной (при сохранении в тактах

0 ожидания совокупности задающих сигналов в неизменности), а моменты окончания цикла обращения и сеанса обмена с памятью связываются со снятием сигналов Выбор памяти на входах 29 и 30. При этом

5 момент снятия сигнала Выбор памяти на последнем во времени согласован со снятием высокого уровня сигнала Обмен на соответствующем входе 42, вследствие чего последовательно сбрасывается возбужден0 ный триггер 9 группы, формируется низкое состояние выходов 43, блокирующее передачу оконечными цепями приоритетного процессора совокупности задающих сигналов текущего сеанса обмена, и срабатывает

5 соответствующий элемент ИЛИ 17, резуль- тирующе инициируя Лог. 1 на втором входе элемента И 10.

Низкий уровень потенциала на выбранном выходе дешифратора 19 возможен на

0 интервале действия активного выходного сигнала от дешифратора 20 и оба они совместно с уровнями Лог. О на первых информационных входах коммутаторов 2 и/или 3 связи (при совпадении возбужде5 ний одноименных выходов дешифраторов 19 и 20 с наличием низкого уровня сигнала на первых информационных входах одних коммутаторов связи присутствие такого же уровня сигнала на первых информационных

0 входах других коммутаторов связи исключается) определяет выставление на первом выходе включившегося от задания двух указанных отрицательных входных сигналов коммутатора связи низкого уровня сигнала,

5 который установит операцию доступа в связанном с ним блоке 1 памяти, дополняемое передачей состояния входа 35 либо 36 на второй выход, а кодовой комбинации младших разрядов с входа 37 либо 38 на третий

0 выход и обеспечат в нем путь для полноразрядного слова входа-выхода 39 либо 40 к или от вторых входов-выходов. Таким образом, для произвольно назначаемого временного отрезка один или одновременно

5 два из группы блоков 1 памяти с числом перекрывающихся тактов операций, устанавливаемых в зависимости от расположения точек задания активных уров ней сигналов на входах 29 и 33 относительно сигналов на входах 30 и 34, способны выполнять передачи информации через входы-выходы 39 и 40 с взаимодействующим с ним или с взаимодействующими с ними системными источниками/приемниками (например,соответственнос контроллером-планировщиком частных задач и с приоритетным процессором обработки) в течение требуемых циклами обращений времени активного обмена.

По завершению тактов передачи информации моменты окончания действия низкого уровня потенциала на входе 29 и/или 30 вызывают согласованное изменение выходных уровней цепочки элементов ИЛИ-НЕ 27 и 28 с прекращением действия активных сигналов на выходах формирователей 25 импульсов и/или 26 и связываются с прекращением удержания фиксированных состязаний на входе 35 и/или 36 и 38 (ввиду использования непосредственных связей источника/приемника с входом 37 устройства кодовые комбинации сигналов на них сохраняют стабильные значения завершившегося цикла вплоть до назначения нового).

Возврат формирователя 25(26) импульсов в исходное состояние предопределяет выставление блоком 23(24) управления высокого уровня потенциала на первом и втором его выходах; Лог. 1 на первом информационном входе способствует закрытию ранее включенного комумтатора 2(3) связи и переводит в высокий уровень состояний первых (вторых) входа обращения, входа чтения-записи и адресного входа сопряженного с данным коммутатором блока 1 памяти при восстановлении высокоим- педансного состояния первого (sfoporo) информационного входа-выхода блока.

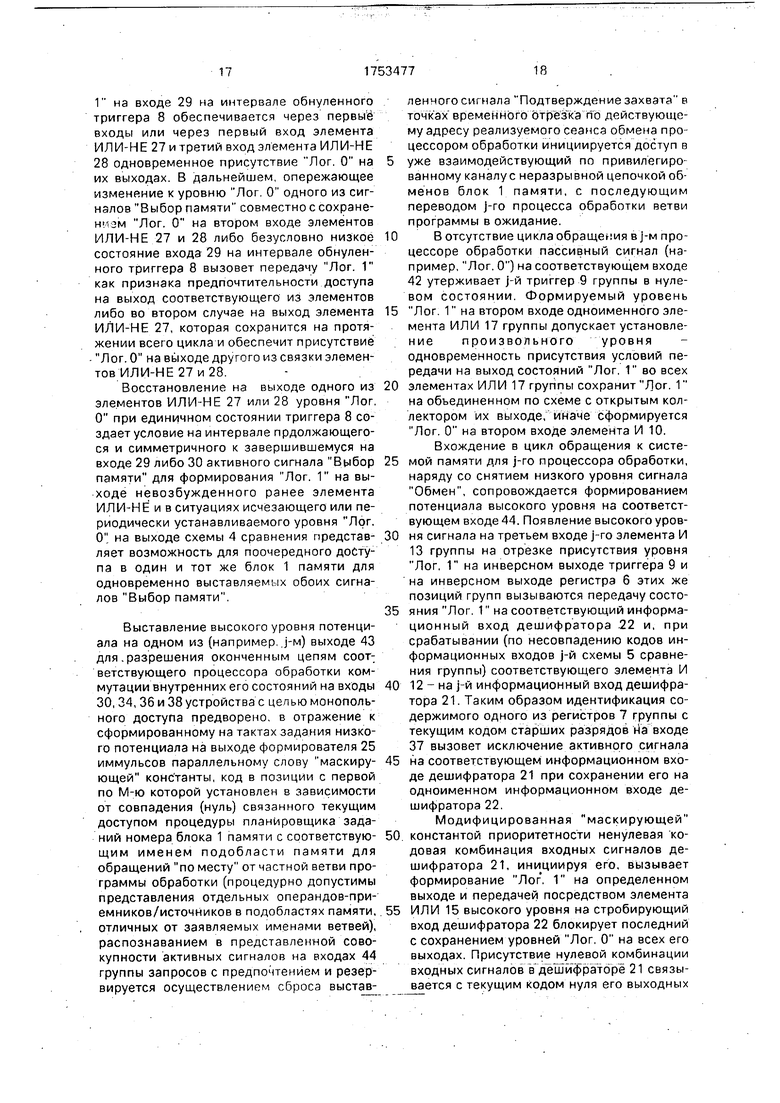

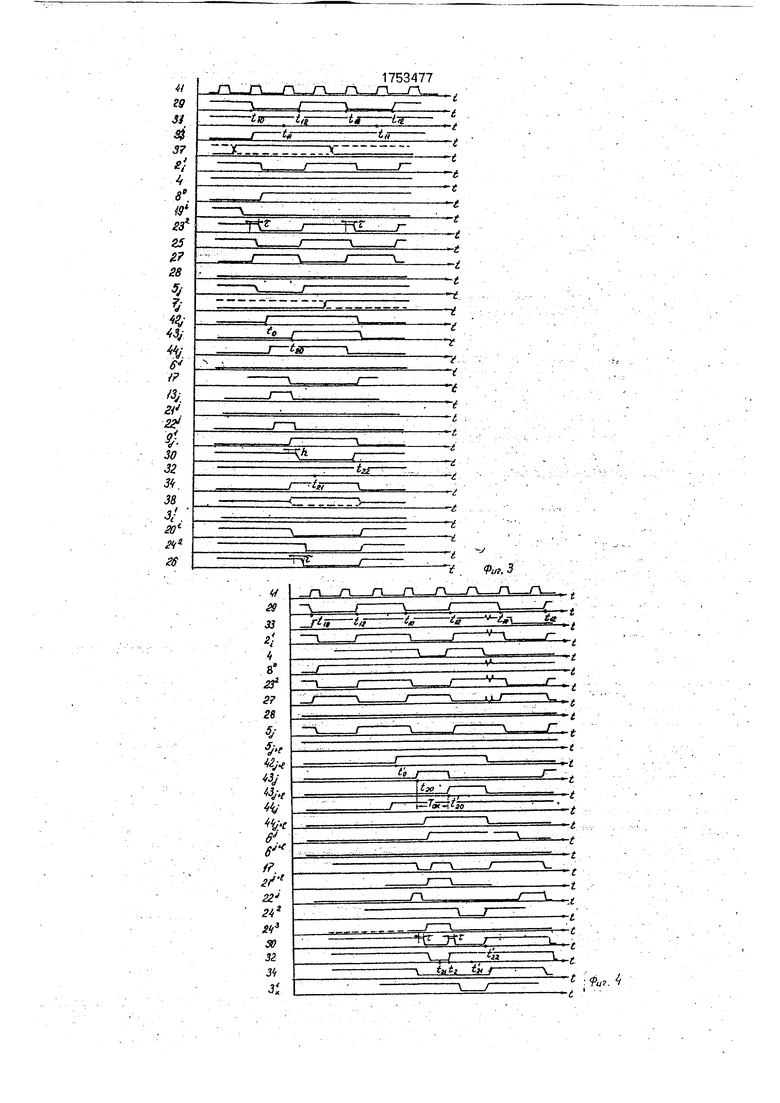

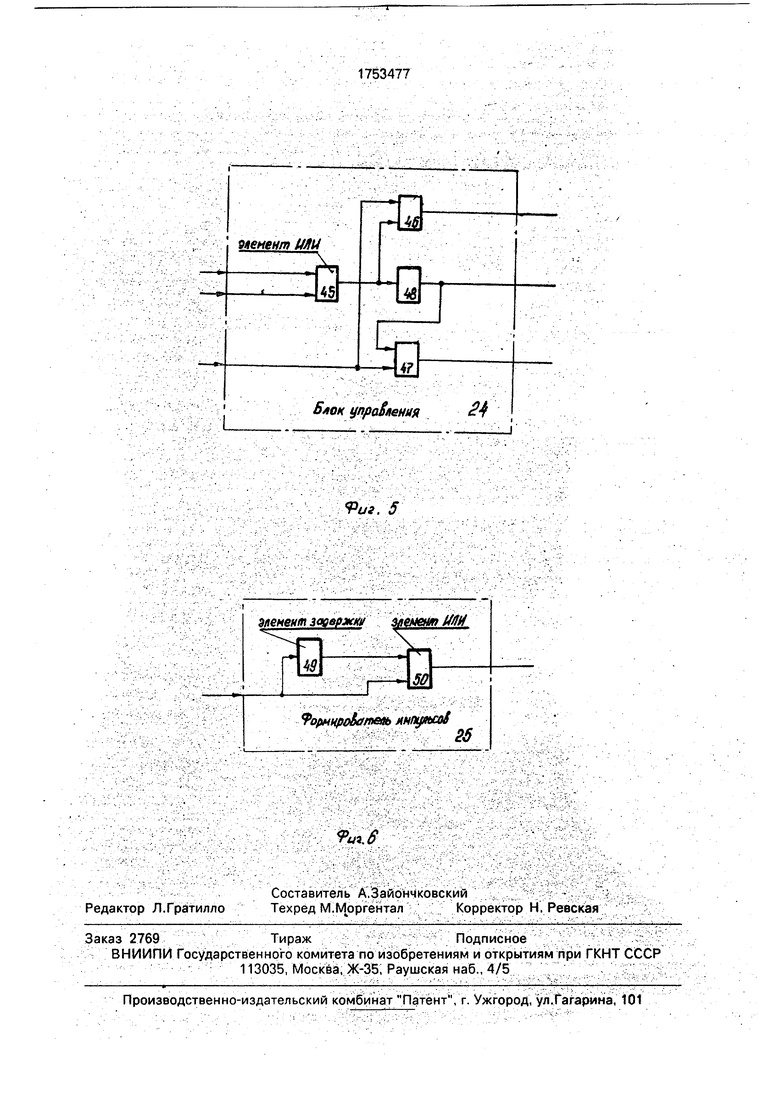

На фиг. 3 представлена временная диаграмма функционирования узлов устройства при записи указателя блока памяти для случая наложения цикла на такты реализации информационного обмена с блоком памяти; на фиг. 4 - то же, при восприятии устройством симметричных совместных обращений.

Значением времени to обозначена исходная точка обращения к системной памяти (цикла, используемого источниками коммутируемых посредством шины информации МпС для передачи указателя блока памяти для данных).

Значениями времени tio и t20 обозначены точки начала соответственно приема уведомления о доступе от коммутируемого непосредственными связями источника/приемника информации и выдачи уведомления приоритетному из группы источников/приемников информации для первоочередного контроля над общей шиной. Значениями времени ti 1 и tai обозначены точки анализа внешними цепями устройства готовности реализации передачи информационных слов

Интервал времени по состоянию

выхода 32 устанавливает незавершенный период ожидания Т0ж в случае перезахвата общей шины.

Значениями времени ti2 и t22 обозначены точки завершения устройством исполнительной фазы взаимодействий с первым и вторыми функционально разделенными источниками/приемниками системы.

Многоразрядный блок 1 памяти может быть выполнен в виде совокупности элемента памяти статического типа, двух элементов И, двух групп элементов И, двух элементов И-НЕ и трех групп буферных усилителей, способных устанавливать на выходе Лог. 1, Лог. О, а также высокоимпедансное состояние. Управляющие инверсные входы буферных усилителей объединяются в пределах групп и для первых двух групп соединяются с выходами соответствующих элементов И-НЕ, инверсный вход первого из которых связан с первым входом одного из элементов И и является первым входом обращения блока, инверсный вход второго элемента И-НЕ связан с вторым входом того же элемента И и является вторым входом обращения блока, а выход указанного элемента И соединен с управляющим инверсным входом третьих

буферных усилителей и с входом разрешения выбора элемента памяти, прямые входы первого и второго элементов И-НЕ связаны с входами другого элемента И, выход которого соединен с управляющим входом элемента памяти, и являются соответственно первым и вторым входами чтения-записи блока. При этом, выходы элемента памяти соединены согласно весам позиций со свободными входами буферных усилителей

первой и второй групп и выходы каждой связанной таким образом пары указанных буферных усилителей подключены к входам элемента И одной группы и точки их включения являются соответственно первым и

вторым информационными входами-выходами соответствующего разряда блока, входы данных элемента памяти соединены с выходами буферных усилителей третьей группы, свободные входы которых связаны

с выходами элементов И упомянутой группы, а адресные входы элемента памяти связаны с выходами элементов И другой группы, первые и вторые входы которых являются первым и вторым адресными входами блока 1 памяти.

Коммутатор 2(3) связи может быть выполнен в виде трех элементов ИЛИ, группы элементов ИЛИ и двух групп буферных усилителей, обладающих тремя возможными состояниями выхода, управляющие инверсные входы которых, а также первые входы элементов ИЛИ в пределах групп объединены и указанные точки объединения для пер- аой группы буферных усилителей связываются с выходом одного элемента ИЛИ, чей прямой вход соединен с первым входом другого элемента ИЛИ, с выходом третьего элемента ИЛИ, первый и второй входы которого соответственно являются управляющим и первым информационным входами узла, и с первым выходом узла, а инверсный вход первого из упомянутых элементов ИЛИ соединен с вторым входом второго из них, чей выход связывается с точками объединения управляющих инверсных входов второй группы буферных усилителей, и первых входов группы элементов ИЛИ и с вторым выходом узла, и с вторым информационным входом узла. При этом свободные входы и выходы группы элементов ИЛИ являются соответственно третьим информационным входом и третьим выходом узла, выходы первой группы буферных усилителей соединены со свободными входами второй группы буферных усилителей и с первым входом-выходом узла, а выходы второй группы буферных усилителей соединены со свободными входами первой группы буферных усилителей и с вторым входом- выходом коммутатора 2(3) связи.

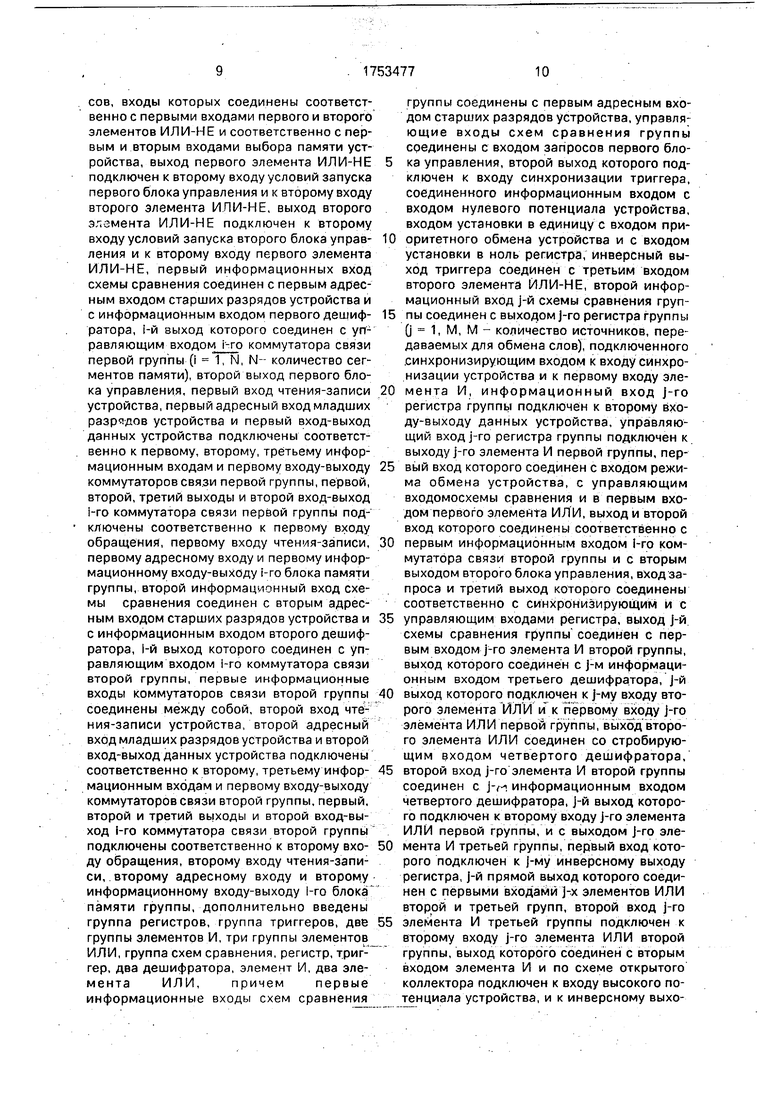

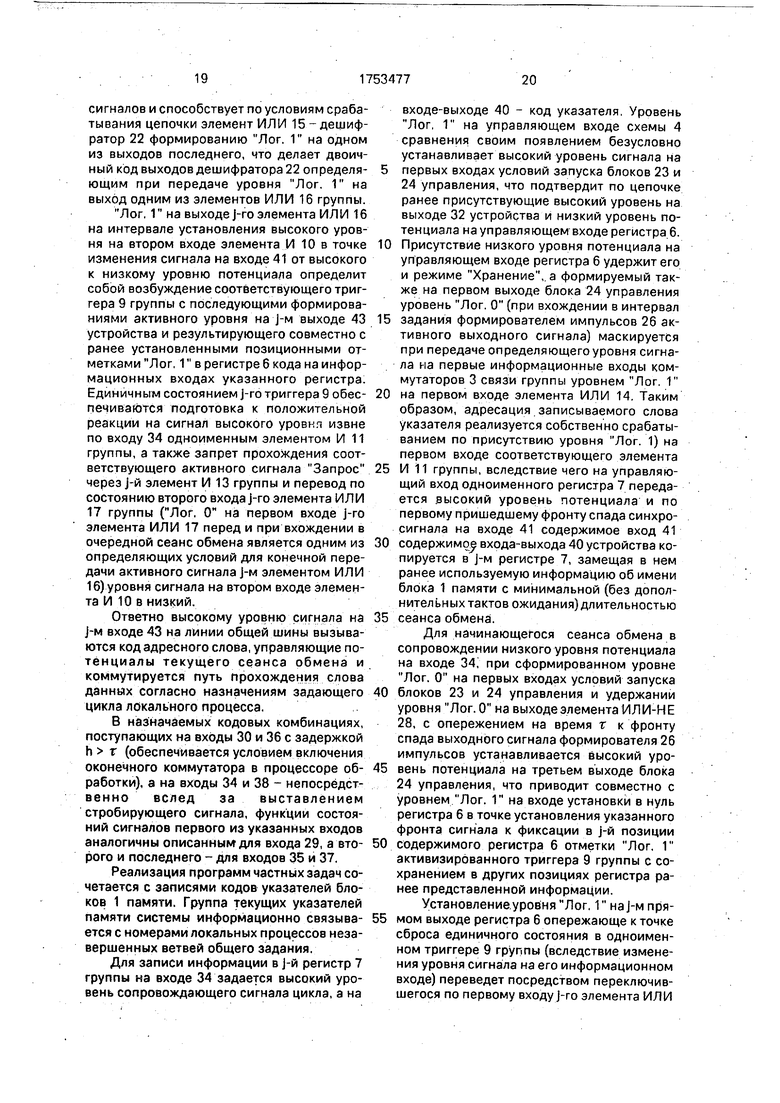

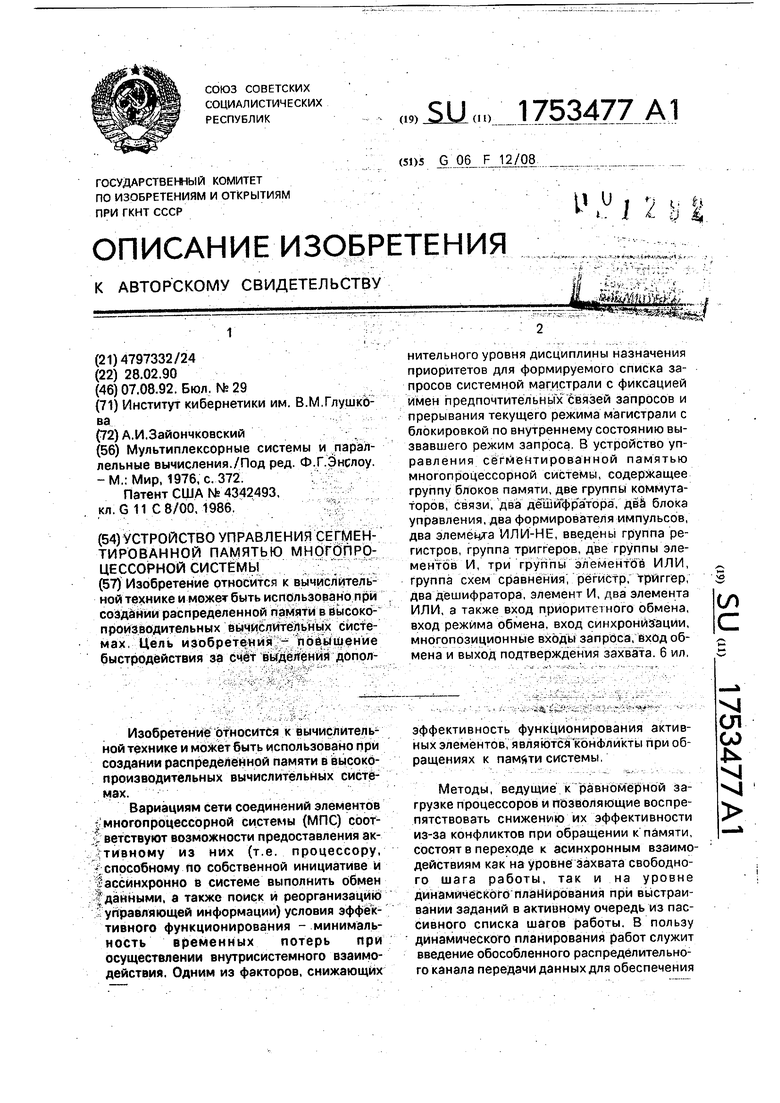

На фиг. 5 приведен вариант организации блока 24 управления, как и блока 23, включающего элементы ИЛИ 45-47 и элемент НЕ 48, вход которого связан с выходом элемента ИЛИ 45, чьи первый и. второй входы являются первым и вторым входом условий запуска блока, и с первым входом элемента ИЛИ 46, чей выход является первым выходом блока, а выход элемента НЕ 48 связан с первым входом элемента ИЛИ 47, чей выход является вторым выходом блока, и является третьим выходом (в блоке 23 не задействован) блока. При этом вторые входы элементов ИЛИ 46 и 47 объединены и подключены к входу запроса блока 24(23) управления.

При одновременном присутствии низкого уровня потенциала на первом и на втором входах условий запуска сигнала Лог. О передается с выхода элемента ИЛИ 45 непосредственно на первый вход элемента ИЛИ 46, тем самым подготавливая к формированию (при выставлении низкого уровня сигнала на входе запроса) по состоянию второго входа элемента ИЛИ 46 низкого

уровня потенциала на первом выходе блока, а с учетом инвертирования элементов НЕ 48 удерживает высокий уровень потенциала на втором, как результат срабатывания ИЛИ

47, и на третьем выходах блока.

На интервале сохранения высокого уровня потенциала на первом или на втором входе условий запуска транзит сигнала Лог. 1 на второй вход элемена ИЛИ 46

подтвердит высокий уровень потенциала на первом выходе блока, на вход элемента НЕ 48 - определит низкий уровень потенциала на третьем выходе блока на всем указанном интервале, а на втором выходе блока в точках задания низкого уровня сигнала на входе запроса (следствие выставления сигналов Лог. О на входах элемента ИЛИ 47).

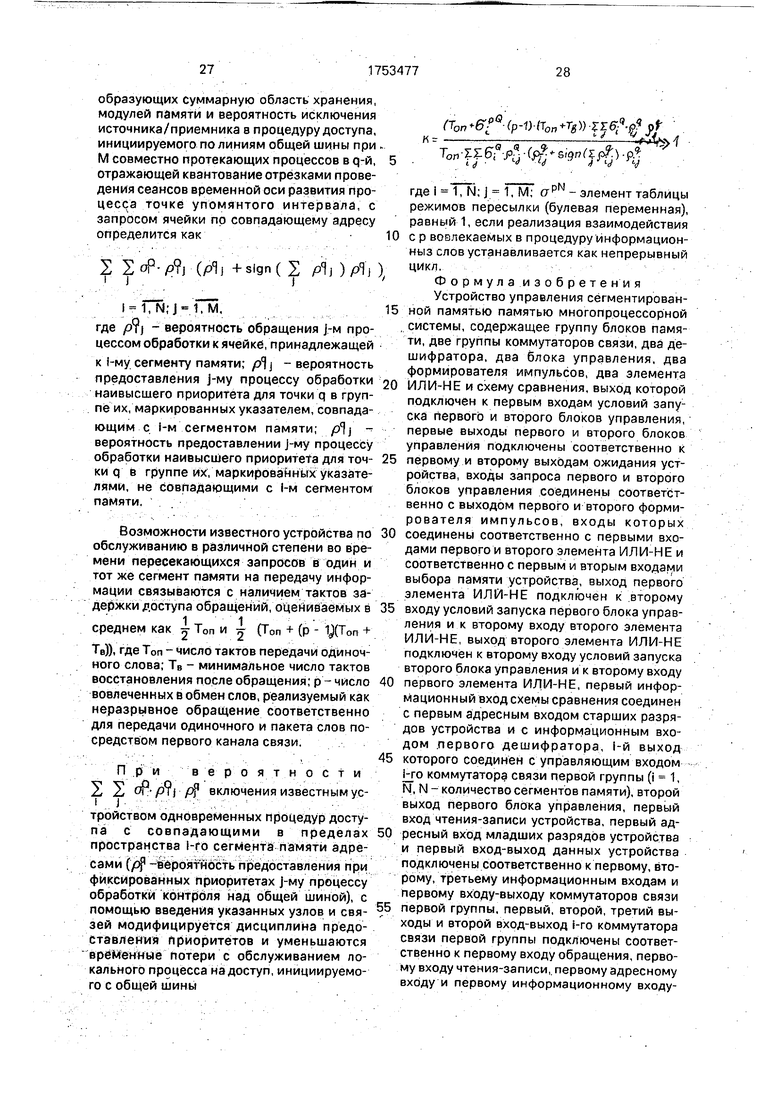

На фиг. 6 приведен вариант организации формирователя 25(26) импульсов, состо- ящего из элементов 49 задержки, вход которого связан с первым входом элемента ИЛИ 50 и с входом узла, а выход - с вторым входом элемента ИЛИ 50, чей выход является выходом узла.

При изменении состояния входного сигнала с высокого в низкий задаваемый фронт потенциала с временной задержкой, равной

г, передается на второй вход элемента ИЛИ 50, для которого состояние первого входа устанавливается (как и состояние входа элемента 49 задержки) в момент появления определяющего входного сигнала. Таким

образом, за точкой введенной задержки в течение действия низкого уровня потенциала обеспечивается передача его элементом ИЛИ 50 и на выходе формирователя 25(26) импульсов фиксируется Лог. О.

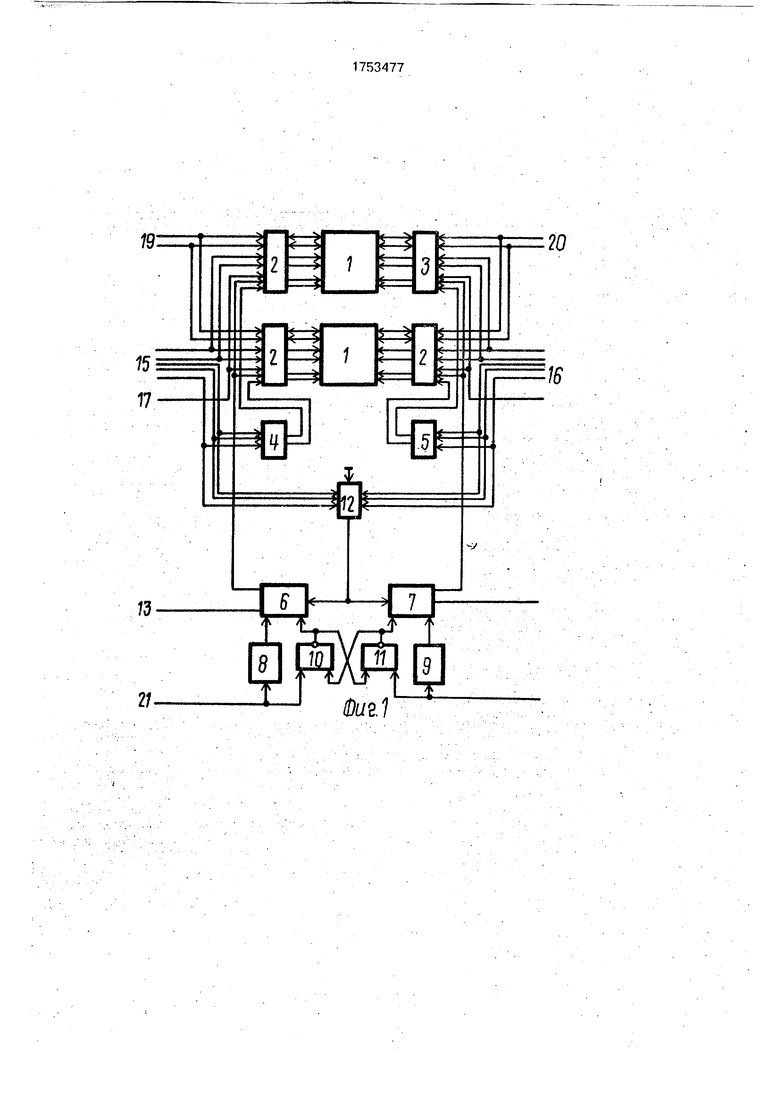

Положительный эффект от применения предлагаемого устройства в МпС по сравнению с известным можно характеризовать следующим.

Пусть в ходе процедуры передачи блоков информации и размещения записей в ячейках сегментированной общей памяти сопряженный с устройством управления непосредственными связями системный источник/приемник назначит себе к исполнению информационный обмен и в нем на определенном интервале времени Q инициирует доступ к памяти, адресуя при этом 1-й сегмент. Необходимость в проводимом для этого обращения укажет переменная оР - элемент таблицы пересылок (булевая переменная), равная 1, если по указанному каналу связи обуславливается взаимодействие с i-м из общего числа N,

образующих суммарную область хранения, модулей памяти и вероятность исключения источника/приемника в процедуру доступа, инициируемого по линиям общей шины при М совместно протекающих процессов в q-й, отражающей квантование отрезками проведения сеансов временной оси развития процесса точке упомянтого интервала, с запросом ячейки по совпадающему адресу определится как

I 2 °Р- Л (/tflj + sign (2 /flj)/ i JJ

I TTN; J ГМ,

где - вероятность обращения j-м процессом обработки к ячейке, принадлежащей к 1-му сегменту памяти; ff j - вероятность предоставления j-му процессу обработки наивысшего приоритета для точки q в группе их, маркированных указателем, совпадающим с 1-м сегментом памяти; р - вероятность предоставлении j-му процессу обработки наивысшего приоритета для точ- ки q в группе их, маркированных указателями, не совпадающими с i-м сегментом памяти.

Возможности известного устройства по обслуживанию в различной степени во времени пересекающихся запросов в один и тот же сегмент памяти на передачу информации связываются с наличием тактов задержки доступа обращений, оцениваемых в

среднем как Топ и + (р - 1ДТоп +

Тв)), где Топ - число тактов передачи одиночного слова; Тв - минимальное число тактов восстановления после обращения; р - число вовлеченных в обмен слов, реализуемый как неразрывное обращение соответственно для передачи одиночного и пакета слов посредством первого канала связи.

При вероятности

2) 2 °Г $ включения известным ус- i J

тройством одновременных процедур доступа с совпадающими в пределах пространства i-ro сегмента памяти адресами ($ -вероятность предоставления при фиксированных приоритетах j-му процессу обработки контроля над общей шиной), с помощью введения указанных узлов и связей модифицируется дисциплина предоставления приоритетов и уменьшаются временные потери с обслуживанием локального процесса на доступ, инициируемого с общей шины

К

on

К+e(p-1)tron+Tg))Srff.c4tf

.fXMfSN f

„9ч Ла

Ta.tftffrffSW.ff

0

5

0 5

0 5

0

5

0

5

где i 1, N; j 1, М; crpN - элемент таблицы режимов пересылки (булевая переменная), равный 1, если реализация взаимодействия с р вовлекаемых в процедуру информационные слов устанавливается как непрерывный цикл.

Формула изобретения Устройство управления сегментированной памятью памятью многопроцессорной системы, содержащее группу блоков памяти, две группы коммутаторов связи, два дешифратора, два блока управления, два формирователя импульсов, два элемента ИЛИ-НЕ и схему сравнения, выход которой подключен к первым входам условий запуска первого и второго блоков управления, первые выходы первого и второго блоков управления подключены соответственно к первому и второму выходам ожидания устройства, входы запроса первого и второго блоков управления соединены соответственно с выходом первого и второго формирователя импульсов, входы которых соединены соответственно с первыми входами первого и второго элемента ИЛИ-НЕ и соответственно с первым и вторым входами выбора памяти устройства, выход первого элемента ИЛИ-НЕ подключен к второму входу условий запуска первого блока управления и к второму входу второго элемента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ подключен к второму входу условий запуска второго блока управления и к второму входу первого элемента ИЛИ-НЕ, первый информационный вход схемы сравнения соединен с первым адресным входом старших разрядов устройства и с информационным входом первого дешифратора, 1-й выход которого соединен с управляющим входом hro коммутатора связи первой группы (1 1, N, N - количество сегментов памяти), второй выход первого блока управления, первый вход чтения-записи устройства, первый адресный вход младших разрядов устройства и первый вход-выход данных устройства подключены соответственно к первому, второму, третьему информационным входам и первому входу-выходу коммутаторов связи первой группы, первый, второй, третий выходы и второй вход-выход i-ro коммутатора связи первой группы подключены соответственно к первому входу обращения, первому входу чтения-записи, первому адресному входу и первому информационному входувыходу 1-го блока памяти группы, второй информационный вход схемы сравнения соединен с вторым адресным входом старших разрядов устройства и с информационным входом второго дешифратора, 1-й выход ко- торого соединен с управляющим входом 1-го коммутатора связи второй группы, первые информационные входы коммутаторов связи второй группы соединены между собой, второй вход чтения-записи устройства, вто- рой адресный вход младших разрядов устройства и второй вход-выход данных устройства подключены соответственно к второму, третьему информационным входам и первому входу-выходу коммутаторов связи второй группы, первый, второй и третий выходы и второй вход-выход i-ro коммутатора связи второй группы подключены соответственно к второму входу обращения, второму входу чтения-записи, второму ад- ресному входу и второму информационному входу-выходу i-ro блока памяти группы, от личающееся тем, что, с целью повышения быстродействия, в него введены группа регистров, группа триггеров, две группы элементов И, три группы элементов ИЛИ, группа схем сравнения, регистр, триггер, два дешифратора, элемент И, два элемента ИЛИ, причем первые информационные входы схем сравнения группы соединены с пер- вым адресным входом старших разрядов устрйоства, управляющие входы схем срав нения группы соединены с входом запросов первого блока управления, второй выход которого подключен к входу синхронизации триггера, соединенного информационным входом с входом нулевого потенциала устройства, входом установки в 1 - с входом приоритетного обмена устройства и с входом установки в О регистра, инверсный выход триггера соединен с третьим входом второго элемента ИЛИ-НЕ, второй информационный вход j-й схемы сравнения группы соединен с выходом j-ro регистра группы (j 1, М, М - количество источников переда- ваемых для обмена слов), подключенного синхронизирующим входом к входу синхронизации устройства и к первому входу элемента И, информационный вход j-ro регистра группы подключен к второму вхо- ду-выходу данных устройства, управляющий вход j-ro регистра группы подключен к

выходу j-ro элемента И первой группы, первый вход которого соединен с входом режима обмена устройства, с управляющим входом схемы сравнения и с первым входом первого элемента ИЛИ, выход и второй вход которого соединены соответственно с первым информационным входом 1-го коммутатора связи второй группы и с вторым выходом второго блока управления, вход запроса и третий выход которого соединены с синхронизирующим и с управляющим входами регистра, выход j-й схемы сравнения группы соединен с первым входом j-ro элемента И второй группы, выход которого соединен с j-м информационным входом третьего дешифратора, j-й выход которого подключен к j-му входу второго элемента ИЛИ и к первому входу j-ro элемента ИЛИ первой группы, выход второго элемента ИЛИ соединен со стробирующим входом четвертого дешифратора, второй вход j-ro элемента И второй группы соединен с j-м информационным входом четвертого дешифратора, j-й выход которого подключен к второму входу j-ro элемента ИЛИ первой группы, и с выходом j-ro элемента И третьей группы, первый вход которого подключен к j-му инверсному выходу регистра, j-й прямой выход которого соединен с первыми входами j-x элементов ИЛИ второй и третьей групп, второй вход j-ro элемента И третьей группы подключен к второму входу j-ro элемента ИЛИ второй группы, выход которого соединен с вторым входом элемента И и по схеме открытого коллектора подключен к входу высокого потенциала устройства, и к инверсному выходу J-ro триггера группы, синхронизирующий вход которого соединен с выходом элемента И, информационных вход j-ro триггера группы соединен с выходом j-ro элемента ИЛИ первой группы, вход установки в О j-ro триггера группы соединен с j-м входом обмена устройства, прямой выход j-ro триггера группы является j-м выходом подтверждения захвата устройства и соединен с вторыми входами j-ro элемента И первой группы и j-ro элемента ИЛИ третьей группы, выход которого соединен с j-м информационным входом регистра, третий вход j-ro элемента И третьей группы подключен к j-му входу запроса устройства.

79

15 17

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1605244A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Многопроцессорная система | 1989 |

|

SU1647597A1 |

| Устройство для обмена информацией | 1979 |

|

SU826330A1 |

| Устройство для связи процессоров | 1986 |

|

SU1481785A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство для сопряжения вычислительных машин и управляющей вычислительной машины | 1984 |

|

SU1257654A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения двух процессоров с общей памятью | 1988 |

|

SU1569840A1 |

iifrCSil

.

1

k

j сч сч еч гч f гч. г г с, «ч- Р1.

J

55

i

J

г, nl fi. ts.

fv fi

ti „1 ill Ч-ч ri с ,i

Фиг. 5

элемент задержку элемент МП W

t элемент j-Ш1

ФормфЖмевь мн/умсо/

элемент

t элемент j-Ш1

86

Авторы

Даты

1992-08-07—Публикация

1990-02-28—Подача