та ИЛИ, к первым входам четвертого пятого элементов И первой группы посоединен инверсный выход четвертого элемента ИЛИ, к вторым входам этих элементов подключены соответственно выходы регулятора длительности импульсов и второго элемента задержки первый вход пятого элемента ИЛИ подключен к выходу первого элемента И, а второй вход соединен с выходом эл мента ИЛИ блока коррекции, который соединен также с первым входом третьего элемента ИЛИ второй группы, в ход пятого элемента ИЛИ подсоединен к вторым прямому и инверсному входам соответственно шестого и седьмо го /элементов и, выходы этих элементов pf подключены к вторым входам соответственно шестого и седьмого элементов ИЛИ, причем первый вход шестого элемента ИЛИ соединен с инверсным выходом седьмого элемента ИЛИ, а первый вход седьмого элемента ИЛИ с инверсным выходом шестого элемента ИЛИ,- инверсный выход седьмого элемента ИЛИ подсоединен к инверсным первому и второму входам соответственно восьмого и девятого элементов и, к двум оставшимся входам этих элементов подключены соответственно выходы регулятора длительности импульсов и второго элемента задержки, первым входом первьтй элемент И второй группы через первый элемент ИЛИ подключен к второй и третьей ячейкам вспомогательного пересчетного . блока , вторым входом через второй элемент ИЛИ подключен к третьей, пятой, девятой и одиннадцатой ячейкам основного пересчетного блока, выход элемента И подсоединен к второму входу третьего элемента ИЛИ и вторым входам второго и третьего элементов И, выход третьего элемента ИЛИ подсоединен к вторым инверсным входам четвертого и пятого элементов И, первые входы второго и четвертого элементов И

подсоединены к выходу задающего генератора, выходы четвеГТого элемента И первой группы и второго элемента И второй группы через первый элемент ИЛИ третьей группы подключены к первого триггера блока управления предварительным инвертором, выходы пятого элемента И первой груп.пы и третьего элемента И второй группы через второй элемент ИЛИ третьей группы подключены к вторым инверсньви входам двух элементов И блока управления предварительными инвертором, первые входы которых подсоединены к выходам первого триггера этого блока выходы восьмого элемента И первой группы и четвертого элемента И второй группы череэ третий элемент ИЛИ третьей группы подсоединены к входу второго триггера блока управления предварительным инвертором, выходы девятого элемента И первой группы и пятого элемента И второй группы через четвертый элемент ИЛИ третьей группы подсоединены к вторым инверсным входам элементов И блока управления предварительным инвертором, первые входы которых подсоединены к выходам второго триггера этого блока .

2, Устройство по п. 1, отличающееся тем,что вспомогательный пересчетный блок выполнен с целым числом ячеек Л 3, а первые элементы ИДИ первой и второй групп выполнены с числом входов на единицу меньше числа ячеек вспомогательного пересчетного блока, причем входы первого элемента ИЛИ первой группы поочередно подключены к выходам с первой до предпоследней ячеек вспомогательного пересчетного блока, а входцзз первого элемента ИЛИ второй группы поочередно подключены к выходам с второй до последней ячеек вспомогательного пересчетного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления тиристорным однофазным инвертором | 1978 |

|

SU771850A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| УСТРОЙСТВО АНАЛИЗА ПЕРЕКРЫТИЙ КАНАЛОВ ПРИ РАЗМЕЩЕНИИ ПАРАЛЛЕЛЬНЫХ ПОДПРОГРАММ В МНОГОПРОЦЕССОРНЫХ СИСТЕМАХ | 2011 |

|

RU2460126C1 |

| Преобразователь переменного напряжения в постоянное | 1985 |

|

SU1325640A1 |

| Преобразователь переменного напряжения в постоянное | 1988 |

|

SU1577020A1 |

| Многоканальное устройство для управ-лЕНия -фАзНыМ иНВЕРТОРОМ | 1979 |

|

SU813669A1 |

| Устройство для измерения угла закручивания вращающегося вала | 1991 |

|

SU1795312A1 |

| Централизованная многоканальная счетная система | 1976 |

|

SU748425A1 |

| Устройство привязи к сигналам точного времени | 1987 |

|

SU1522146A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU1062713A1 |

1. УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОДНОФАЗНЫМ ТИРИСТОРНЫМ ИНВЕРТОРСМ, содержащее задающий генератор, к выходу которого последовательно подсоединены первый элемент задержки, регулятор длительности импульсов и второй элемент задержки, блок управления предварительным инвертором, основной пересчетнь блок, состоящий из двенадцати ячеек пересчета, основные и дополнительные элементы совпадения, при этом первые входы основных элементов совпадения подключены к соответствую 1;им выходам основного пересчетного блока, вторые их входы подключены к выходу регулятора длительности импульсов, первые входа дополнительных элементов совпадения соединены с выходами датчиков направления тока нагрузки, вторые их BxofHJ подключены к входу второго элемента эадерхскй, а третьи входы соответственно к выходам второй, третьей, восьмой и девятой ячеек основного пересчетного блока, блок коррекции, содержаний элемент ИЛИ, входы которого подключены к выходам первой и седьмой ячеек основного пересчетного блока, отличаю щ е е с .я тем, что, с целью расширения функциональных возможностей и улучшения гармонического спектра выходного напряжения при широком диапазоне регулирования, оно снабжено вспомогательный пересчетным блоком, состоящим, например, из трёх ячеек пересчета, блок управления предварительным инвертором выполнен на двух триггерах и четырех элементах И с прямьтмн и инверсными входами, в блок коррекции введены три группы логических элементов, первая группа логических элементов содержит семь элементов ИЛИ, один из которых шестивходовый, а остальные двухвходовые, и девять двухвходовых элементов И, вторая группа логических элементов содержит три элемента ИЛИ, из которых один четырехвходовый, а остальные двухвходовые, и пять двухвхоловых элементов И, третья группа содержит четыре двух входовых элемента ИЛИ, при этом (Л вспомогательнь-й пересчетный блок включен между вторым элементом задержки и основньм пересчетным блоком, вторым входом первый элемент И первой группы через первьй двухвходовый элемент ИЛИ подключен к первой и второй ячейкам дополнительного пересчетного блока, а первым входом через шестивходовый элемент сх ИЛИ - к выходам четных ячеек основного пересчетного блока, выход элесо мента И подключен к вторым прямому vl и инверсному соответственно входам второго и третьего элементов И перСЛ вой группы, к первым входам этих сл элементов и первым входам четвертого, пятого элементов первой группы и третьего, пятого элементов второй группы подсоединен выход второго элемента задержки, выходы второго и третьего элементов И первой группы подключены соответственно к вторым входам третьего и четвертого элемен.тов ИЛИ, причем первый вход третьего элемента ИЛИ соединен с инверсным выходом четвертого элемента ИЛИ, а первый вход четвертого элемента ИЛИ с инверсным выходом третьего элемен

t

Изобретение относится к электротехнике и может быть использовано в регулируемых вторичных источниках питания с кваэисинусоидальным выходHfcOM напряжением, в частности, относится к автономным тиристорным инвер торам, формируюш.им кривую выходного напряжения путем амплитудно-импульсной модуляции (АИМ) за счет коммутации вторичных o6MOTOj трансформатора.

Известно устройство для управления инвертором, содержащее задающий

генератор, триггер, элементы задержки, регулятор длительности импульсов, пересчетный блок, элементы совпадения и формирователи импульсов управления тиристорами. Это устройство позврляет регулировать ширину импульсос формируемых ступеней напряжения tl.

К недостатку этого устройства следует отнести ограниченные функциональные возможности, которые не позволяют формировать квазисинусоидальное напряжение путем улучшенной АИМ с нулевыми ступенями напряжения на тактовом интервале в начале каждой полуволны напряжения. Наиболее близким по технической сущности к изобретению является уст ройство для управления однофазным тиристорным инвертором, содержащее задающий генератор, первый элемент задержки, регулятор длительности импульсов управления тиристорами, второй элемент задержки, пересчетный блок, элементы совпадения, блок коррекции и блок управления предвар тельным инвертором С23. Недостатком известного устройства является низкое качество выходно электрической энергии при широком диапазоне регулирования. Цель изобретения - расширение фу циональных возможностей и улучшение гармонического спектра выходного на пряжения при широком диапазоне регу ирования. Поставленная иель достигается тем что в устройство для управления тиристорным однофазным инвертором, содержаш.ее задаюс ий генератор, к выходу которого последовательно подсоеди нены первый элемент задержки, регулятор длительности импульсов и второй элемент задержки, блок управления предварительным инвертором, основной перёсчетный блок, состоящий из двенадцати ячеек пересчета, odboB ные и дополнительные элементы совпадения, при этом первые входы основных элементов совпадения подключены к соответствующим выходам основного пересчетного блока, вторые их входы подключены к выходу регулятора длительности импульсов, первые входы дополнительных элементов совпадения соединены с выходами датчиков направления тока нагрузки, вторые их входы подключень к входу второго эле мента задержки, а третьи входы подключены соответственно к выходам второй, третьей, восьмой и девятой ячейкам основного пересчетного блока, блок коррекции, куда входит элемент ИЛИ, входы которого подключены к выходам первой и седьмой ячеек основного пересчетного блока, дополнительно введены вспомогательный пересчетный блок, состояний, например, из трех ячеек пересчета, и три группы логических элементов в блок коррекции, первая группа логических элементов содержит семь элементов ИЛИ, один из которых шестивходовый, а остальные двухвходовые, и девять двухвходовых элементов И, вторая . группа логических элементов содержит три элемента ИЛИ, из которых один четырехвходовый, а остальные двухвходовые, и пять двухвходовых элемен тов И, третья группа содержит четыре двухвходовкх элемента ИЛИ, блок управления предварительным инвертором выполнен на двух триггерах и четырех элементах И с прямыии и инверсными входами, вспомогательный пересчетный блок включен между вторым элементом задержки и основньви пересчетным блоком, вторым входом первый элемент И первой группы через первый двухвходовый элемент ИЛИ подключен к первой и второй ячейкам дополнительного пересчетного блока, а первым входом через шестивходовый элемент ИЛИ - к выходам четных ячеек основного пересчетного блока, выход элемента И подключен к STOptw прямому и инверсному соответственно входам второго и третьего элементов И первой группы, к первым входам этих элементов и первые входам четвертого, пятого элементов И первой группы и третьего, пятого элементов И второй группы подсоединен выход второго элемента задержки, выходы второго и третьего элементов И первой группы подключены соответственно к вторым входам третьего и четвертого элементов ИЛИ, причем первый вход третьего элемента ИЛИ соединен с инверсньм вьходом четвертого элемента ИЛИ, а первый вход четвертого элемента ИЛИ - с инверсным выходом третьего элемента ИЛИ к первые входам четвертого и пятого элементов И первой группы подсоединен инверсный выход четвертого элемента ИЛИ, к вторым входам этих элементов подключены соответственно выходы регулятора длительности импульсов и второго элемента задержки, первый вход пятого элемента ИЛИ подключен к выходу первого элемента И, а второй вход соединен с вьходом элемента ИЛИ блока коррекции, который соединен также с первьаи входом третьего элемента ИЛИ второй группы, выход пятого элемента ИЛИ подсоединен к вторым прямому и инверсному входам соответственного шестого и седьмого элементов И, выходы этих элементов И подключены к вторым входам соответственно шестого и седьмого элементов ИЛИ, причем первый вход шестого элемента ИЛИ соединен с инверсHbw выходом седьмого элемента ИЛИ, а первый вход седьмого элемента ИЛИ с инверсным выходом шестого элемента ИЛИ, инверсныр выход седьмого элемента ИЛИ подсоединен к инверсньм первому и второму входам соответственно восьмого и девятого элементов И, к двум оставшимся входам этих элементов подключены соответственно выходы регулятора длительности импульсов и второго элемента задержки, первым входом первый элемент И второй группы через первь.Г элемент ИЛИ подключен к второй и третьеР ячейкам дополнительного пересчетного блока, вторым входом через второй элемент ИЛИ подключен к третьей, пятой, девятой и одиннадцатой ячейкам основного пересчетного блока, выход элемента И подсоединен к второму входу третьего элемента ИЛИ и вторьам входам второго и третьего элементов И, выход третьего элемента ИЛИ подсоединен к вторым инверсным входам четвертого и пятого элементов И, пер вые входы второго и четвертого элементов И подсоединены к выходу эадаюшего генератора, выходы четвертого элемента И первой группы и второго элемента И второй группы через первый элемент ИЛИ третьей группы подключены к входу первого триггера блока управления предварительным инвертором, выходы пятого элемента И первой группы и третьего элемента И второй группы череэ второй элемент ИЛИ третьей группы подключены к вто,рым инверсным входам двух элементов И блока управления предварительным инвертором, первые входы которых подсоединены к выходам первого триггера этого блокаf выходы восьмого элемента И первой группы и четвертого элемента И второй группы череэ третий элемент ИЛИ третьей группы подсоединены к входу второго триггера блока управления предварительным инвертором, выходы девятого элемента И первой группы и пятого элемента И второй группы через четвертый элемент ИЛИ третьей группы подсоединены к вторым инверсньм входам дв-ух элементов И блока управления предварительным инвертором, первые входы которых подсоединены к выходам второго триггера этого блока.

Кроме того, дополнительный пересчетный блок выполняется с целым числом ячеек , а также увеличивается число входов первых логических элементов первой и второй групп на единицу меньие числа ячеек вспомогательного пересчетного блока, причем входы первого элемента ИЛИ первой группы- поочередно подключены к вьэсодам от первой до предпоследней ячеек вспомогательного пересчетного блока, а выходы первого элемента ИЛИ второй группы поочередно подключены к выходам от второй допоследней ячеек вспомогательного пересчетного блока,

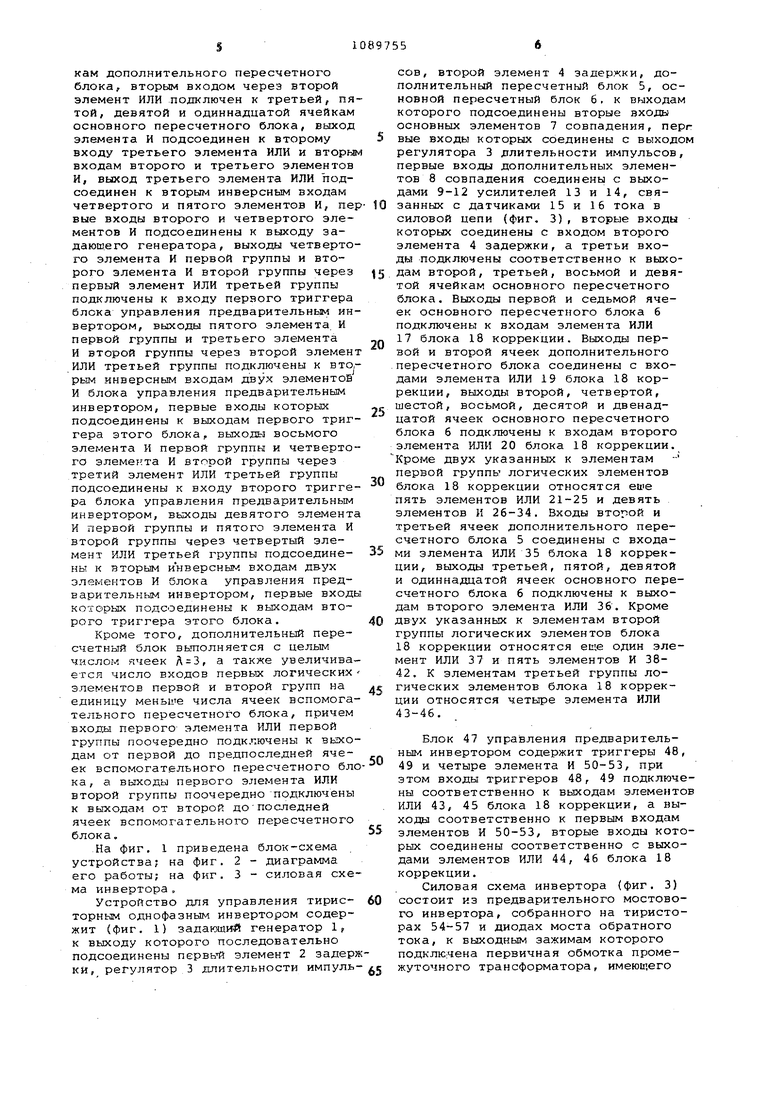

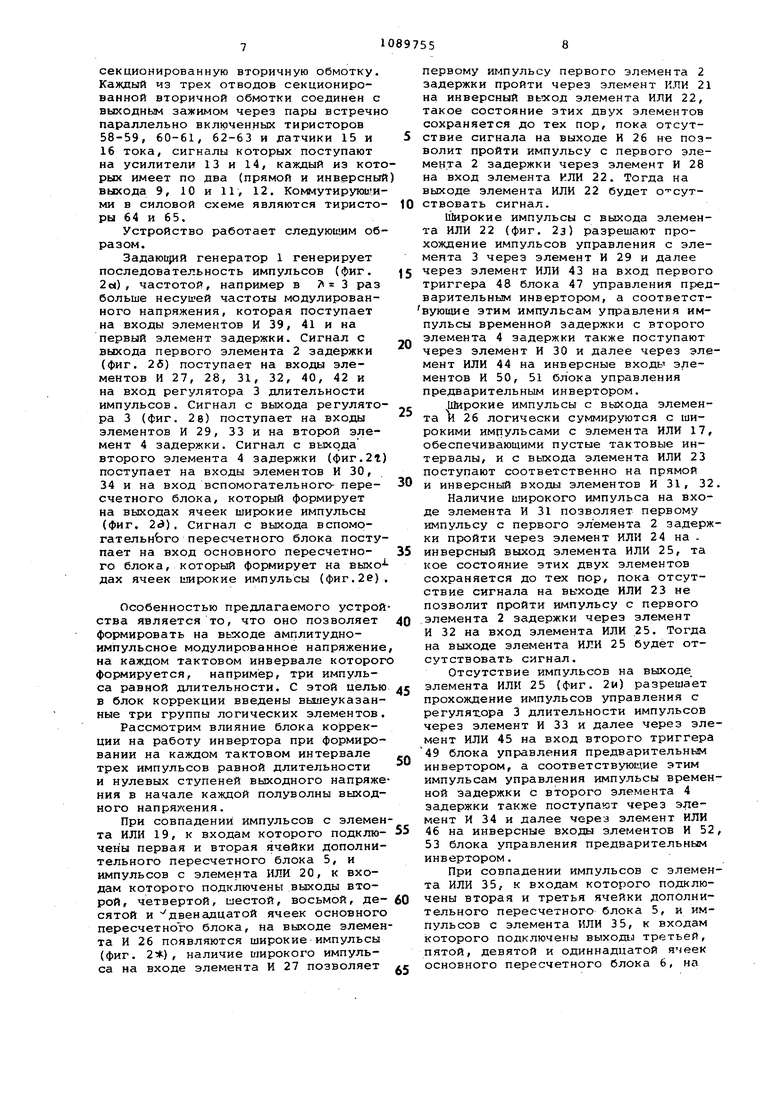

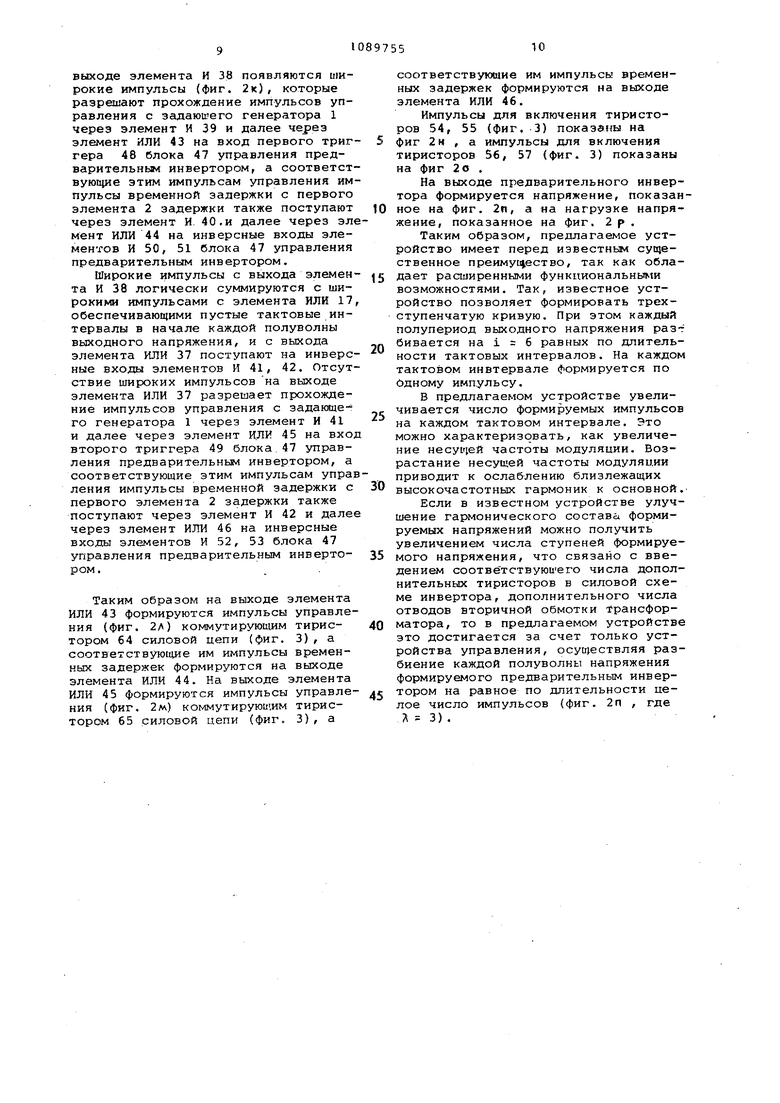

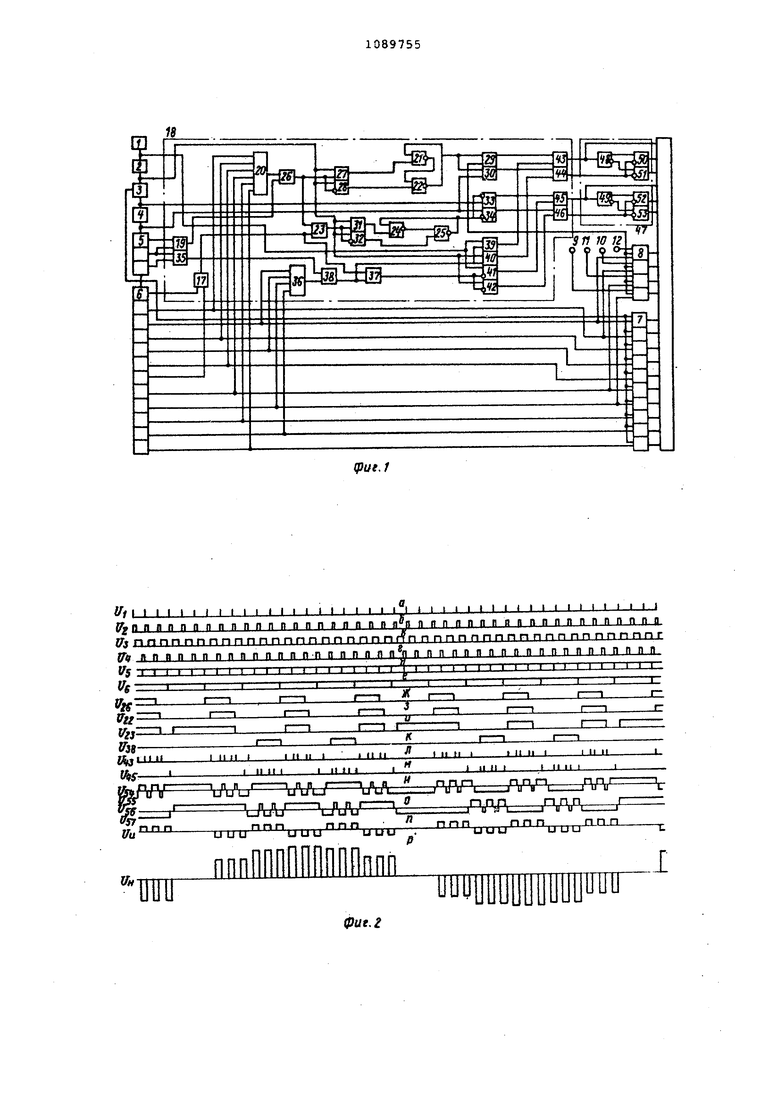

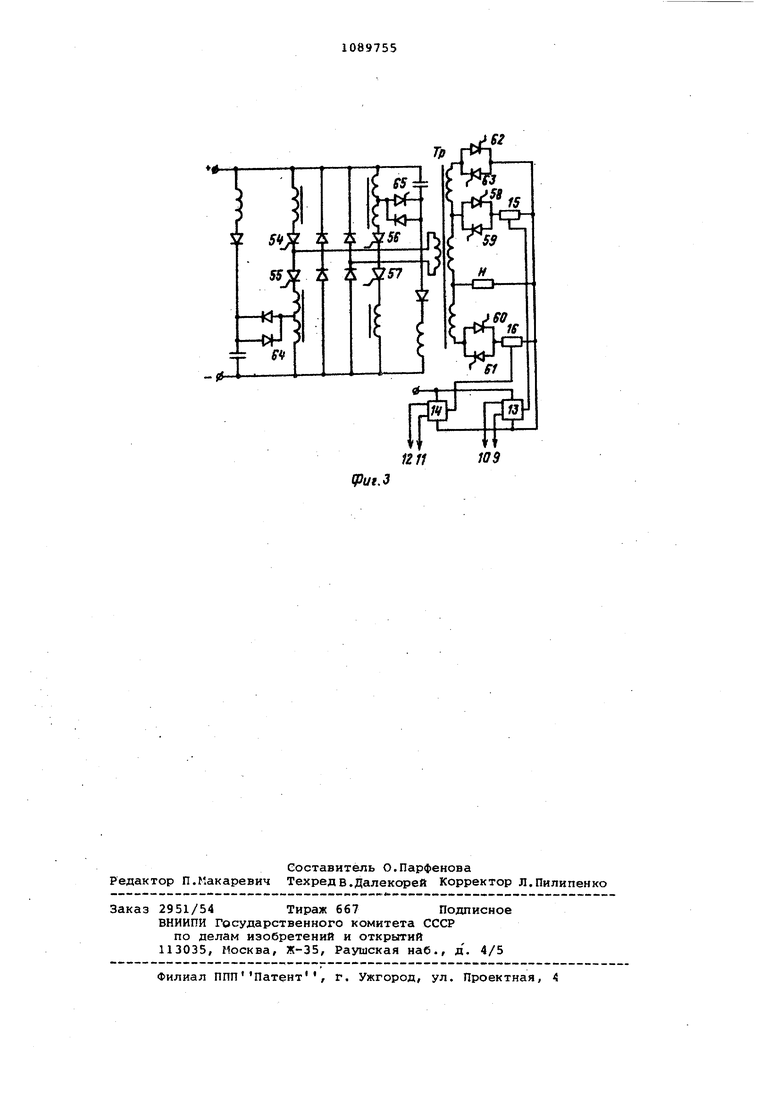

.На фиг. 1 приведена блок-схема устройства; на фиг. 2 - диаграмма его работы; на фиг. 3 - силовая схема инвертора,

Устройство для управления тиристорным однофаэнь 1 инвертором содержит (фиг, 1) задающий генератор 1, к выходу которого последовательно подсоединены первь элемент 2 задержки, регулятор 3 длительности импульсов, второй элемент 4 задержки, дополнительный пересчетный блок 5, основной пересчетный блок 6, к выходам которого подсоединены вторые входы основных элементов 7 совпадения, пер вые входы которых соединены с выходо регулятора 3 длительности импульсов, первые входы дополнительных элементов 8 совпадения соединены с выходами 9-12 усилителей 13 и 14, связанных с датчиками 15 и 16 тока в силовой цепи (фиг. 3), вторые входы которых соединены с входом второго элемента 4 задержки, а третьи входы подключены соответственно к выходам второй, третьей, восьмой и девятой ячейкам основного пересчетного блока. Выходы первой и седьмой ячеек основного пересчетного блока 6 подключены к входам элемента ИЛИ

17блока 18 коррекции. Выходы первой и второй ячеек дополнительного пересчетного блока соединены с входами элемента ИЛИ 19 блока 18 коррекции, выходы второй, четвертой, шестой, восьмой, десятой и двенадцатой ячеек основного пересчетного блока 6 подключены к входам второго элемента ИЛИ 20 блока 18 коррекции.

Кроме двух указанных к элементам первой группы логических элементов блока 18 коррекции относятся еше пять элементов ИЛИ 21-25 и девять элементов И 26-34. Входы второй и третьей ячеек дополнительного пересчетного блока 5 соединены с входами элемента ИЛИ 35 блока 18 коррекции, выходы третьей, пятой, девятой и одиннадцатой ячеек основного пересчетного блока 6 подключены к выходам второго элемента ИЛИ 36. Кроме двух указанных к элементам второй группы логических элементов блока

18коррекции относятся еще один элемент ИЛИ 37 и пять элементов И 3842, К элементам третьей группы логических элементов блока 18 коррекции относятся четыре элемента ИЛИ 43-46.

Блок 47 управления предварительным инвертором содержит триггеры 48 49 и четыре элемента И 50-53, при этом входы триггеров 48, 49 подключены соответственно к выходам элементо ИЛИ 43, 45 блока 18 коррекции, а выходы соответственно к первым входам элементов И 50-53, вторые входы которых соединены соответственно с выходами элементов ИЛИ 44, 46 блока 18 коррекции.

Силовая схема инвертора (фиг. 3) состоит из предварительного мостового инвертора, собранного на тиристорах 54-57 и диодах моста обратного тока, к выходным зажимам которого подключена первичная обмотка промежуточного трансформатора, имеющего секционированную вторичную обмотку. Каждый из трех отводов секционированной вторичной обмотки соединен с выходньам зажимом через пары встречно параллельно включенных тиристоров 58-59, 60-61, 62-63 и датчики 15 и 16 тока, сигналы которых поступают на усилители 13 и 14, каждый из кото рых имеет по два (прямой и инверсный выхода 9, 10 и 11, 12. Кокмутирукшнми в силовой схеме являются тиристоры 64 и 65. Устройство работает следующим образом. Задаю11р1й генератор 1 генерирует последовательность импульсов (фиг. ) , частотой, например в 7 3 раз больше несушей частоты модулированного напряжения, которая поступает на входы элементов И 39, 41 и на первый элемент задержки. Сигнал с выхода первого элемента 2 задержки (фиг. 25) поступает на входы элементов И 27, 28, 31, 32, 40, 42 и на вход регулятора 3 длительности импульсов. Сигнал с выхода регулятора 3 (фиг. 2в) поступает на входы элементов И 29, 33 и на второй элемент 4 задержки. Сигнал с выхода второго элемента 4 задержки (фиг.2т поступает на входы элементов И 30, 34 и на вход вспомогательного- пересчетного блока, который формирует на выходах ячеек широкие импульсы (фиг. ). Сигнал с выхода вспомогательнЬго пересчетного блока поступает на вход основного пересчетного блока, который формирует на выходах ячеек широкие импульсы (фиг.2е) Особенностью предлагаемого устрой ства является то, что оно позволяет формировать на вьзходе амплитудноимпульсное модулированное напряжение на каждом тактовом инвервале которог формируется, например, три импульса равной длительности. С этой целью в блок коррекции введены выиеуказанные три группы логических элементов. Рассмотрим влияние блока коррекции на работу инвертора при формировании на каждом тактовом интервале трех импульсов равной длительности и нулевых ступеней выходного напряже ния в начале каждой полуволны выходного напряжения. При совпадении импульсов с элемен та ИЛИ 19, к входам ксэторого подключены первая и вторая ячейки дополнительного пересчетного блока 5, и импульсов с элемента ИЛИ 20, к входам которого подключены выходы второй, четвертой, шестой, восьмой, десятой и двенадцатой ячеек основного пересчетного блока, на выходе элемен та И 26 появляются широкие импульсы (фиг. 2), наличие широкого импульса на входе элемента И 27 позволяет первому И1.1пульсу первого элемента 2 задержки пройти через элемент ИЛИ 21 на инверсный элемента ИЛИ 22, такое состояние этих двух элементов сохраняется до тех пор, пока отсутствие сигнала на выходе И 26 не позволит пройти импульсу с первого элемента 2 задержки через элемент И 28 на вход элемента ИЛИ 22. Тогда на выходе элемента ИЛИ 22 будет о- сутствовать сигнал. Широкие импульсы с выхода элемента ИЛИ 22 (фиг. 2з) разрешают прохождение импульсов управления с элемента 3 через элемент И 29 и далее через элемент ИЛИ 43 на вход первого триггера 48 блока 47 управления предварительным инвертором, а соответствующие этим импульсам управления импульсы временной задержки с второго элемента 4 задержки также поступают через элемент И 30 и далее через элемент ИЛИ 44 на инверсные входь элементов И 50, 51 блока управления предварительным инвертором. Широкие импульсы с выхода элемента И 26 логически суммируются с широкими импульсами с элемента ИЛИ 17, обеспечивающими пустые тактовые интервалы, и с выхода элемента ИЛИ 23 поступают соответственно на прямой и инверсный входы элементов И 31, 32. Наличие широкого импульса на входе элемента И 31 позволяет первому импульсу с первого элемента 2 задержки пройти через элемент ИЛИ 24 на инверсный выход элемента ИЛИ 25, та кое состояние этих двух элементов сохраняется до тех пор, пока отсутствие сигнала на выходе ИЛИ 23 не позволит прюйти импульсу с первого .элемента 2 задержки через элемент И 32 на вход элемента ИЛИ .25. Тогда на выходе элемента ИЛИ 25 будет отсутствовать сигнал. Отсутствие импульсов на выходе элемента ИЛИ 25 (фиг. 2и) разрешает прохождение импульсов управления с регулятора 3 длительности импульсов через элемент И 33 и далее через элемент ИЛИ 45 на вход второго триггера 49 блока управления предварительным инвертором, а соответствуюихие этим импульсам управления импульсы временной задержки с второго элемента 4 задержки также поступают через элемент И 34 и далее через элемент ИЛИ 46 на инверсные входы элементов И 52, 53 блока управления предварительным инвертором. При совпадении импульсов с элемента ИЛИ 35, к входам которого подключены вторая и третья ячейки дополнительного пересчетного блока 5, и импульсов с элемента ИЛИ 35, к входам которого подключены выходи третьей, пятой, девятой и одиннадцатой ячеек основного пересчетного блока 6, на

выходе элемента И 38 появляются широкие импульсы (фиг. 2к), которые разрешают прохождение импульсов управления с задаюшего генератора 1 через элемент И 39 и далее через элемент ИЛИ 43 на вход первого триггера 48 блока 47 управления предварительным инвертором, а соответствующие этим импульсам управления импульсы временной задержки с первого элемента 2 задержки также поступают через элемент И 40,и далее через элемент ИЛИ 44 на инверсные входы элементов И 50, 51 блока 47 управления предварительным инвертором.

Широкие импульсы с выхода элемента И 38 логически суммируются с широкими импульсами с элемента ИЛИ 17, обеспечивающими пустые тактовые интервалы в начале каждой полуволны выходного напряжения, и с выхода элемента ИЛИ 37 поступают на инверсные входы элементов И 41, 42. Отсутствие широких импульсов на выходе элемента ИЛИ 37 разрешает прохождение импульсов управления с задаквдего генератора 1 через элемент И 41 и далее через элемент ИЛИ 45 на вход второго триггера 49 блока 47 управления предварительным инвертором, а соответствующие этим импульсам управления импульсы временной задержки с первого элемента 2 задержки также поступают через элемент И 42 и далее через элемент ИЛИ 46 на инверсные входы элементов И 52, 53 блока 47 управления предварительным инвертором. .

Таким образом на выходе элемента ИЛИ 43 формируются импульсы управления (фиг. 2л) коммутирующим тиристором 64 силовой цепи (фиг. 3), а соответствующие им импульсы временных задержек формируются на выходе элемента ИЛИ 44. На выходе элемента ИЛИ 45 формируются импульсы управления (фиг. 2м) коммутирующим тиристором 65 силовой цепи (фиг. 3), а

соответствующие им импульсы временных задержек формируются на выходе элемента ИЛИ 46.

Импульсы для включения тиристоров 54, 55 (фиг. 3) показаны на фиг 2н , а импульсы для включения тиристоров 56, 57 (фиг. 3) показаны на фиг 2о .

На выходе предварительного инвертора формируется напряжение, показанное на фиг. 2п, а на нагрузке напряжение, показанное на фиг. 2 р .

Таким образом, предлагаемое устройство имеет перед известньм существенное преимущество, так как обладает расширенными функциональньтми возможностями. Так, известное устройство позволяет формировать трехступенчатую кривую. При этом каждый полупериод выходного напряжения разбивается на i 6 равных по длительности тактовых интервалов. На каждом тактовом инвтервале Формируется по Одн ому импул ь су.

В предлагаемом устройстве увеличивается число формируемых импульсов на каждом тактовом интервале. Это можно характеризовать, как увеличение несущей частоты модуляции. Возрастание несущей частоты модуляции приводит к ослаблению близлежащих высокочастотных гармоник к основной.Если в известном устройстве улучшение гармонического состава формируемых напряжений можно получить увеличением числа ступеней формируемого напряжения, что связано с введением соответствуюцего числа дополнительных тиристоров в силовой схеме инвертора, дополнительного числа отводов вторичной обмотки трансформатора, то в предлагаемом устройстве это достигается за счет только устройства управления, осуществляя разбиение каждой полуволны напряжения формируемого предварительным инвертором на равное по длительности целое число импульсов (фиг. 2п , где Д 3).

I/I I 1 I I 1 I I I I I 1 1 I j I I I ° I I I I I I I I y nnnnnnnnnnnnnnnnn Д n nnfl finnnnnnnnnnnnnnnnnnna У у п n nnnnpnnnnnpnnnnn пп nnnnnnnnnnnnnnnn n n П г

yaftnnnfnnnnnpnnnnnnnnnn nnnnnBnnnnnnnnnnnnnn

Лf,

I и и II It II II 11 tl

пппппврпппппппппПППП

L I I 1 I I I I I

V i I 1 III 1

I I « II II

MM II II II I1

J09

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для управления однофазным тиристорным инвертором | 1974 |

|

SU517133A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления тиристорным однофазным инвертором | 1978 |

|

SU771850A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-04-30—Публикация

1982-07-15—Подача