Изобретение относится к измерительной технике и может быть использовано для измерения угла закручивания вращающегося вала, например, коленчатого вала двигателя внутреннего сгорания, а также для исследования крутильных колебаний валов.

Известно устройство для измерения угла закручивания вращающегося вала, которое содержит две идентичные схемы включения датчиков, узел управления, сумматор.. Величина напряжения на выходе сумматора прямо пропорциональна углу закручивания.

Однако это устройство не обеспечивает достаточной точности измерений на переходных режимах работы вращающегося вала за счет аналоговой обработки сигнала, кроме того, точность измерений существенно зависит от стабильности выходного напряжений источника опорного напряжения, который входит в сумматор, при действии на него дестабилизирующих факторов, например, при изменении температуры.;

Известен цифровой измеритель крутящего момента, сбдержащий упругий вал, два закрепляемых на его концах измерительных диска, два датчика считывания, два усилителя-ограничителя, первую и вторую схемы совпадений, генератор счетных импульсов, а также триггер, делитель частоты, формирующие временной интервал измерения. счетчик импульсов.

Это устройство имеет неодинаковую погрешность дискретности на различных скоростях вращения вала. Коме того, устройство не позволяет производить измерения мгновенных значений угла закручивания на переходных режимах работы вращающегося вала за счет усреднения результата измерения за несколько периодов входной частоты измеряемого сдвига фаз.

Наиболее близким по технической сущности к заявляемому является устройство для измерения угла закручивания вращающегося вала.

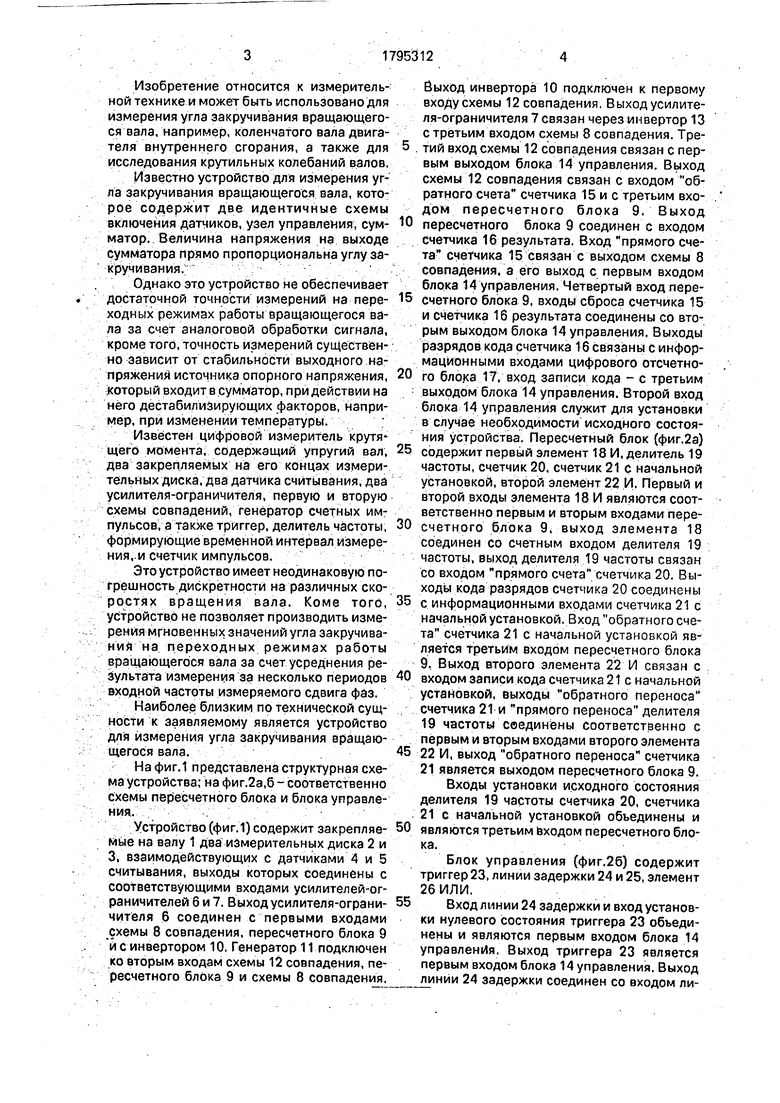

На фиг. 1 представлена структурная схема устройства; на фиг.2а,б - соответственно схемы пересчетного блока и блока управления. -.. .. -

Устройство (фиг. 1) содержит закрепляемые на валу 1 два измерительных диска 2 и 3, взаимодействующих с датчиками 4 и 5 считывания, выходы которых соединены с соответствующими входами усилителей-ограничителей б и 7. Выход усилителя-ограничителя 6 соединен с первыми входами схемы 8 совпадения, пересчетного блока 9 и с инвертором 10. Генератор 11 подключен ко вторым входам схемы 12 совпадения, пересчетного блока 9 и схемы 8 совпадения.

Выход инвертора 10 подключен к первому входу схемы 12 совпадения. Выход усилителя-ограничителя 7 связан через инвертор 13 с третьим входом схемы 8 совпадения. Тре. тий вход схемы 12 совпадения связан с первым выходом блока 14 управления. Выход схемы 12 совпадения связан с входом обратного счета счетчика 15 и с третьим входом пересчетного блока 9. Выход

0 пересчетного блока 9 соединен с входом счетчика 16 результата. Вход прямого счета счетчика 15 связан с выходом схемы 8 совпадения, а его выход с первым входом блока 14 управления. Четвертый вход пере5 счетного блока 9, входы сброса счетчика 15 и счетчика 16 результата соединены со вторым выходом блока 14 управления. Выходы разрядов кода счетчика 16 связаны с информационными входами цифрового отсчетно0 го блока 17, вход записи кода - с третьим : выходом блока 14 управления. Второй вход блока 14 управления служит для установки в случае необходимости исходного состояния устройства. Пересчетный блок (фиг,2а)

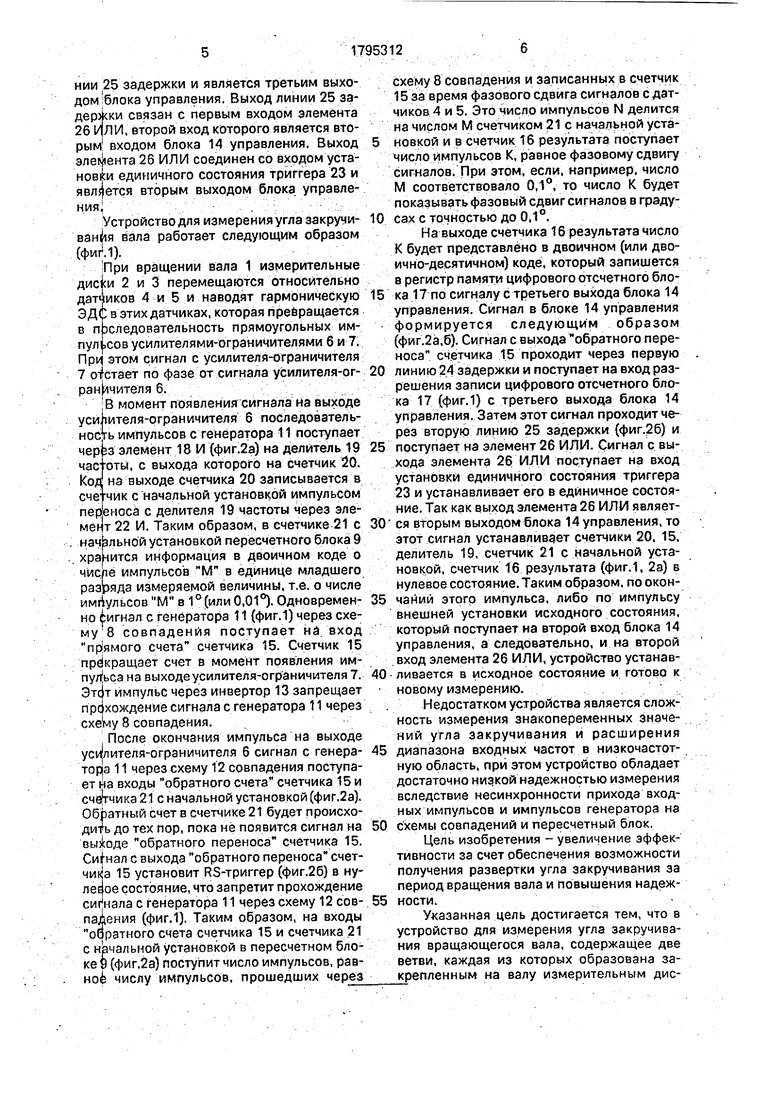

5 содержит первый элемент 18 И, делитель 19 частоты, счетчик 20, счетчик 21с начальной установкой, второй элемент 22 И, Первый и второй входы элемента 18 И являются соответственно первым и вторым входами пере0 счетного блока 9, выход элемента 18 соединен со счетным входом делителя 19 частоты, выход делителя 19 частоты связан со входом прямого счета счетчика 20. Выходы кода разрядов счетчика 20 соединены

5 с информационными входами счетчика 21 с начальной установкой. Вход обратного счета счётчика 21 с начальной установкой является третьим входом пересчетного блока 9, Выход второго элемента 22 И связан с

0 входом записи кода счетчика 21 с начальной

установкой, выходы обратного переноса

/счетчика 21 и прямого переноса делителя

19 частоты соединены соответственно с

первым и вторым входами второго элемента

5 22 И, выход обратного переноса счетчика

21 является выходом пересчетного блока 9.

Входы установки исходного состояния

делителя 19 частоты счетчика 20, счетчика

21 с начальной установкой объединены и

0 являются третьим входом пересчетного блока.

Блок управления (фиг.2б) содержит триггер 23, линии задержки 24 и 25, элемент 26 ИЛИ.

5 Вход линии 24 задержки и вход установки нулевого состояния триггера 23 объединены и являются первым входом блока 14 управления. Выход триггера 23 является первым входом блока 14 управления. Выход линии 24 задержки соединен со входом линии 25 задержки и является третьим выходом |блока управления. Выход линии 25 за- дерЖки связан с первым входом элемента 26 И|ЛИ, второй вход которого является вторым входом блока 14 управления. Выход элемента 26 ИЛИ соединен со входом уста- нов|Ы единичного состояния триггера 23 и является вторым выходом блока управления . ; . . . :. - ;- . ;.:Устройство для измерения угла закручивания вала работает следующим образом (фиг.1).

При вращении вала 1 измерительные диски 2 и 3 перемещаются относительно датчиков 4 и 5 и наводят гармоническую ЭДС в этих датчиках, которая пребращается в последовательность прямоугольных йм- усилителями-ограничителями б и 7. При этом сигнал с усилителя-ограничителя 7 отстает по фазе от сигнала усилителя-ог- ран|йчителя 6.

;В момент появления сигнала на выходе уси штеля-ограничителя 6 последовательность импульсов с генератора 11 поступает чер ;з элемент 18 И (фиг.2а) на делитель 19 , с выхода которого на счетчик 20. Код на выходе счетчика 20 записывается в счетчик с начальной установкой импульсом переноси с делителя 19 частоты через элемент 22 И. Таким образом, в счетчике 21 с начальной установкой пересчетного блока 9 хранится информация в двоичном коде о чисЬё импульсов М в единице младшего разряда измеряемой величины, т.е. о числе имАульсов М в 1°(или 0,01°). Одновременно игнал с генератора 11 (фиг.1) через схе- совпадения поступает на. вход прямого счета счетчика 15. Счетчик 15 прекращает счет в момент появления им- на выходе усилителя-ограничителя 7. Этс|т импульс через инвертор 13 запрещает прохождение сигнала с генератора 11 через схему 8 совпадения.

, После окончания импульса на выходе усилителя-ограничителя 6 сигнал с генератора 11 через схему 12 совпадения поступает ijia входы обратного счета счетчика 15 и счетчика 21 с начальной установкой (фиг.2а). Обратный счет в счетчике 21 будет происходить до тех пор, пока не появится сигнал на выводе обратного переноса счетчика 15. Сигнал с выхода обратного переноса счет- 15 установит RS-триггер (фиг.2б) в ну- состояние, что запретит прохождение сигнала с генератора 11 через схему 12 совпадения (фиг.1). Таким образом, на входы обратного счета счетчика 15 и счетчика 21 с начальной установкой в пересчетном блоке у (фиг.2а) поступит число импульсов, равной числу импульсов, прошедших через

схему 8 совпадения и записанных в счетчик 15 за время фазового Сдвига сигналов с датчиков 4 и 5. Это число импульсов N делится на числом М счетчиком 21 с начальной уста- 5 новкой и в счетчик 16 результата поступает число импульсов К, равное фазовому сдвигу сигналов. При этом, если, например, число М соответствовало 0,1°, то число К будет показывать фазовый сдвиг сигналов в граду10 сах с точностью до 0,1°.

На выходе счетчика 16 результата число К будет представлено в двоичном (или двоично-десятичном) коде, который запишется в регистр памяти цифрового отсчетного бло5 ка 17 по сигналу с третьего выхода блока 14 управления. Сигнал в блоке 14 управления формируется следующим образом (фиг.2а,б). Сигнал с выхода обратного переноса счетчика .1.5 проходит через первую

0 линию 24 задержки и поступает на вход разрешения записи цифрового отсчетного блока 17 (фиг.1) с третьего выхода блока 14 управления. Затем этот сигнал проходит через вторую линию 25 задержки (фиг.2б) и

5 поступает на элемент 26 ИЛИ. Сигнал с выхода элемента 26 ИЛИ поступает на вход установки единичного состояния триггера 23 и устанавливает его в единичное состояние. Так как выход элемента 26 ИЛИ являет0 ся вторым выходом блока 1.4 управления, то этот сигнал устанавливает счетчики 20, 15, делитель 19, счетчик 21 с начальной установкой, счетчик 16 результата (фиг.1, 2а) в нулевое состояние. Таким образом, по окон5 чаний этого импульса, либо по импульсу внешней установки исходного состояния, который поступает на второй вход блока 14 управления, а следовательно, и на второй вход элемента 26 ИЛИ, устройство устанав0 ливается в исходное состояние и готово к новому измерению.

Недостатком устройства является сложность измерения знакопеременных значений утла закручивания и расширения

5 диапазона входных частот в низкочастотную область, при этом устройство обладает достаточно низкой надежностью измерения вследствие несинхронности прихода входных импульсов и импульсов генератора на

0 схемы совпадений и пересчетный блок.

Цель изобретения - увеличение эффективности за счет обеспечения возможности получения развертки угла закручивания за период вращения вала и повышения надеж5 кости.

Указанная цель достигается тем, что в устройство для измерения угла закручивания вращающегося вала, содержащее две ветви, каждая из которых образована за крепленным на валу измерительным диском, установленным с возможностью взаимодействия с ним датчиком считывания и подключенным к последнему усилителем- ограничителем, первую схему совпадения с тремя входами и выходом, суммирующий счетчик со счетным входом, подключенным к выходу первой схемы совпадения, входом обнуления и выходами разрядов кода, вторую схему совпадения с тремя входами и выходом, блок управления с Двумя входами и тремя выходами; первым из которых соединенный с первым входом второй схемы совпадения, пересчетный блок с выходом и четырьмя входами, первым из которых соединенный с выходом второй схемы совпадения, а вторым - с вторым выходом блока управления, счетчик результата со счетным входом, подключенным к выходу пересчетного блока, входом обнуления, связанным с вторым выходом блока управления, и выходами разрядов кода, цифровой отсчетный блок с входами разрядов кода, связанными с выходами разрядов кода счетчика результата, и входом управления, подключенным к третьему выходу блока управления, и генератор с выходом введены блок выделения опорного сигнала с тремя входами, первый и второй из которых подключен к соответствующему усилителю-ограничителю, и тремя выходами, первый из которых соединен со вторыми входами первой и второй схем совпадения и входом обнуления суммирующего счетчика, а второй - с первым входом первойсхемы совпадения, блокавтоматичё- ского выбора диапазона измерения с входами разрядов кода, двумя входами управления, первый из которых подключён к первому выходу блока выделения опорного сигнала, а второй - к выходу генератора, и двумя выходами, первый из которых соединен с третьими входами блока выделения опорного сигнала, первой схемы совпа- . дения W пёресчетного блока, а второй - с третьим входом второй схемы совпадения, вычитающий счетчик импульсов с входами предварительной установки, подклгоченны- : . м.й к выходам разрядов кода суммирующего счетчика, входом записи кода, подключенным к первому, .выходу блока выделения опорного сигнала, счетным входом, соединенным с выходом второй схемы совпадения, и выходом, к которому подключен первый вход блока управления, цифро-аналоговый преобразователь с входами разрядов кода, подключенными к выходам разрядов кода счетчика результатов, двумя входами управления, первый из которых соединен с третьим выходом блока выделения опорного сигнала, а второй - с третьим выходом блока управления, и выходом, временной селектор с тремя входами, первый из которых подключен к первому выходу блока выделения опорного сигнала, а третий - к выходу цифро-аналогового преобразователя, и выходом, формирователь угловой метки с двумя входами, первый из которых соединен с первым выходом блока выделения опорного сигнала, и выходом, формирователь амплитудной метки с входами разрядов кода, связанными с выходами разрядов кода счетчика результата, входом управления, связанным с третьим выходом блока выделения опорного сигнала, и выходом, датчики верхней и нижней мертвых трчек, .каждый из которых имеет выход,

двигатель на два с входом, подключенным к

. выходу датчика нижней мертвой точки, и

.выходом, подключенным ко вторым входам

временного селектора и формирователя угловой,метки, телевизионный индикатор с семью входами, первый из которых соединен с первым выходом блока выделения опорного сигнала, второй - с выходом датчика верхней мертвой точки, третий -с выходом датчика нижней мертвой точки, четвертый - с выходом формирователя амплитудной метки, пятый - с выходом делителя на два, шестой - с выходом временного селектора, седьмой - с выходом формирователя угловой метки, и регистратор с двумя входами, первый из которых подключен к выходу датчика нижней мертвой точки а второй - к выходу временного селектора, при этом пересчетный блок снабжен выходами разрядов кода, подключенными к входам разрядов кода блока автоматического выбора Диапазона измерений, четвертый вход пересчетного блока соединен с первым выходом блока выделения опорного сигнала, а цифровой отсчетный блок снабжен вторым входом управления, соединенным с Третьим выходом блока выделения опорного сигнала.

Пересчетный блок содержит реверсивный счетчик импульсов со входом, подключенным к первому входу управления блока, входом установки исходного состояния, подключенным к второму входу установки исходного состояния, подключенным к второму входу управления блока, входами разрядов кода, входом записи и выходом, соединенным с входом блока, два элемента 2И с выходом и двумя входами каждый, выход первого из которых соединен со входом

записи реверсивного счетчика импульсов, первый вход первого элемента 21/1 подключен к выходу реверсивного счетчика импульсов, первый вход второго элемента 2И соединен с третьим входом управления пересчетного блока, а вторые входы элементов 2И соединены между собой и подключены к Четвертому входу управления пересчет- ного блока, линию задержки с входом, подключенным к четвертому входу управления пересчетного блока, и выходом, делитель Частоты импульсов со счетным входом, соединенным с выходом второго элемента 2И, входом установки исходного состояния, подключенным к выходу линии задержки, и выходом, счетчик импульсов со счетным входом, соединенным с выходом делителя частоты импульсов, входом установки исXOflf

ого состояния, соединенным с выходом

WI

задержки, и выходами разрядов кода, и регистр памяти с входом записи кода, соединенным с четвертым входом управления пересчетного блока, входами разрядов, подключенными к выходам разрядов кода счетчика импульсов, и выходами разрядов код, соединенными с входами разрядов кода реверсивного счетчика импульсов и входами разрядов кода пересчётного блока,

|Блок выделения опорного сигнала со- дер|жит первый и второй D-триггеры, инвер- снше выходы которых соединены с D-входами, а их С-входы соединены, соот- ветртвенно, с первым и вторым входом блока -выделения опорного сигнала, выходы подключены, соответственно, к первым входа первого и второго элементов 2И-НЕ, втфые входы которых соединены между собой и с третьим входом блока выделения опорного сигнала, выходы первого и второго элементов 2И-НЕ подключены к S-вхо- дай, соответственно, первого и второго ЯЗгтриггеров с инверсными входами, выход )вого и инверсный выход второго RS- irrepOB соединены, соответственно, с эвым и вторым входами первого элемента

, инверсный выход первого и выход вто-

пе тр пе

21/

pok RS-триггеров - соответственно, с пер- вы|м и вторым входами второго элемента 21/1, выходы первого и второго элементов 2И подсоединены, соответственно, к первому и втЬрому входам элемента ИЛИ и к R и S входам третьего RS-триггера, выход элемента ИЛИ подключен через формирователь ко- рфгких импульсов к R-входу четвертого инверсного RS-триггера и к входу линии заде ржки, выход которой соединен с S-входом четвертого RS-триггера, выход которого соединен с первым выходом блока выделения опорного сигнала, выходы первого и второ- гр RS-триггеров подключены, соответствен- нЬ. к первому и второму входам третьего элемента 2И, выход которого через форми- ррватель коротких импульсов соединен с Rj-входом пятого RS-триггера с инверсными вводами и к входу линии задержки, выход крторой подключен к входу пятого RS-триг

0

гера, выход пятого RS-триггера соединен с вторым выходом блока выделения опорного сигнала, к третьему выходу которого подключен выход третьего RS-триггера, при этом входы установки исходного состояния первых и вторых D- и RS-триггеров соединены с выходом пятого RS-триггера.

Блок автоматического выбора диапазона измерения содержит схемы И иИЛИ-НЕ,

0 входы которых поразрядно соединены между собой и с входами разрядов кода блока, линию задержки, вход которой подключен к первому входу блока автоматического выбора диапазона измерения, первый и второй

5 элементы 2И, первые входы которых подключены, соответственно, к выходам схем И и ИЛИ-НЕ, вторые входы объединены и соединены с выходом линии задержки, элемент 2 ИЛИ-НЕ, первый и второй входы

0 которого подсоединены, соответственно, к выходам схем И и ИЛИ-Н Е, реверсивный счетчик импульсов, вход прямого счета которого соединен с выходом первого элемента 2И, и вход обратного счета - с выходом

5 второго элемента 2И, первый и второй делители частоты импульсов и регистр памяти, причем входы разрядов кода первого делителя частоты подключены к выходам разрядов кода реверсивного счетчика импульсов,

0 а входы разрядов кода второго делителя частоты - к выходам разрядов кода реверсивного счетчика импульсов через регистр памяти, счетные входы первого и второго делителя частоты импульсов соединены

5 между собой и с вторым входом блока автоматического выбора диапазона измерения, вход записи кода регистра памяти соединен с выходом элемента 2 ИЛИ-НЕ, а выходы первого и второго делителей частоты импульсов соединены, соответственно, с первым и вторым выходами блока автоматического выбора диапазона измерения.

Формирователь амплитудной метки со5 держит блок сравнения с первыми и вторыми входами разрядов кода, входом управления и выходом и блок памяти с выходами разрядов кода, подключенными к вторым входам разрядов кода блока сравне0 ния, причем первые входы разрядов кода, вход управления и выход блока сравнения, соответственно, соединены со входами раз- рядов кода, входом управления и выходом формирователя амплитудной метки.

5 Формирователь угловой метки содержит измеритель угла поворота вала с выходами разрядов кода и с первым и вторым входами, соединенными соответственно с первым и вторым входами формирователя тловой метки, блок памяти с выходами разрядов кода и блок сравнения с выходом, подключенный к выходу формирователя угловой метки, и первыми и вторыми входами разрядов кода, соответственно подключенными к выходам разрядов измерителя угла поворота вала и блока памяти.

Сопоставительный анализ с прототипом показывает, что заявляемое устройство отличается наличием новых блоков: блока выделения опорного сигнала (БОС), блока автоматического выбора диапазона измерения (АВДИ), цифро-аналогового преобразователя (ЦАП), реверсивного счетчика, временного селектора, формирователей угловой и амплитудной меток, датчиков верхней и нижней мертвых точек (ВМТ, НМТ), делится на два, телевизионного индикатора, регистратора и их связями с остальными элементами и блоками устройства.

Сравнение заявляемого решения с другими техническими решениями в этой области и других технических решений в смежных областях науки и техники показывает, что устройства АВДИ, временной селектор, телевизионный индикатор, ЦАП, известны, при широкой известности датчиков ВМТ и НМТ, делителя на два, реверсивного счетчика.

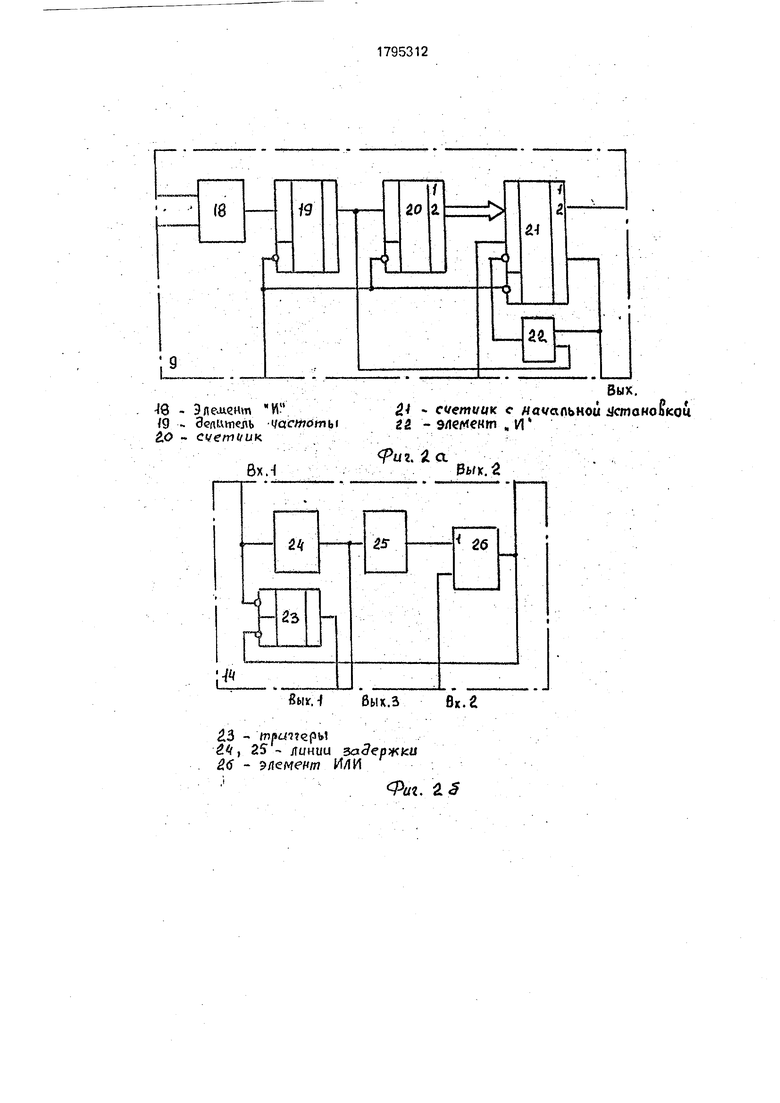

Однако, блок АВДИ от известных отличается тем, что часть функций этого блока выполняет пересчетный блок, причем блок АВДИ нельзя использовать без пересчетного блока. При этом пересчетный блок совместно с блоком АВДИ проявляет новое свойство - участвует в процессе автоматического выбора диапазона измерения. Кроме того, блок АВДИ известен как таковой только по своему назначению, а по структурной схеме заявляемый блок не имеет анало- гов. Совокупность технических решений блоков АВДИ, ВОС и реверсивного счетчика в устройстве для измерения угла закручивания вращающегося вала позволяет получить параметры устройства значительно превосходящие параметры известных. При выполнении устройства на микросхемах ЭСЛ-логики с опорной частотой 500 МГц можно получить параметры, приведенные в таблице в сравнении с параметрами отечественного фазометра мгновенных значений НФ-3, который можно использовать для исследования мгновенных значений угла закручивания.

Необходимо отметить, что фазометр НФ-3 можно использовать для исследования мгновенных значений угла закручивания при частоте вращения вала не более 6000 в то время, как заявляемое устройство можно использовать при скорости вращения до 34000 , следовательно,

заявляемое устройство можно использовать для исследования всех существующих двигателей. Из приведенных данных видно, что совокупность признаков: блоки АВДИ и

ВОС, реверсивный счетчик и их связи между элементами и блоками устройства позволяют получить сверхсуммарный положительный эффект. Кроме того, эта совокупность признаков обеспечивает новое свойство за0 являемому устройству - возможность использования его для исследования знакопеременных крутильных колебаний. Фазометр НФ-3 можно использовать для исследования колебаний, однако на часто5 тах вращения не более 84 , т.е. оно пригодно для малооборотных двигателей. Заявляемое устройство можно использовать для этой цели на частотах вращения до 12000 мин 1.

0 Совокупность признаков: ЦАП, датчики ВМТ и НМТ, делитель на два. временной селектор, формирователи угловой и амплитудной меток, телевизионный индикатор совместно с устройством для измерения

5 мгновенного значения угла закручивания вращающегося вала позволяет визуально в реальном масштабе времени исследовать динамику измеряемого процесса, причем совокупность признаков: ЦАП, датчики ВМТ

0 и НМТ, делитель на два, временной селектор совместно с устройством для измерения угла закручивания вала и регистратором, например, двухканальным самописцем или шлейфовым осциллографом, обеспечивает

5 фиксирование динамики процесса. В обоих случаях можно наблюдать и фиксировать не только весь процесс, но и его части, что обеспечивает совокупность следующих признаков: временной селектор, формировате0 ли амплитудной и угловой меток, их связи и внутренняя структура. Устройства для отображения динамики процесса известны, однако они не применимы в данном случае без их существенной доработки. Кроме того эти

5 устройства обладают рядом недостатков, например, невозможность наблюдения замкнутых линий процесса на экране, возможность отображения ограниченного числа кривых, что затрудняет статистический ана0 лиз исследуемого процесса. Предлагаемое же устройство вследствие специфической структуры.позволяет исследовать динамику крутильных колебаний в реальном масштабе времени и одновременно производить

5 анализ статистического закона распределения независимо от скорости вращения вала. Совокупность признаков и положительных эффектов от каждого признака позволяет реализовать такой положительный эффект, какой невозможно получить с помощью совокупности других известных уст- оойств, блоков и приборов, причем каждый признак привносит дополнительный эффект, суммарного, например, рассмотрен- ныЈ выше пересчетный блок и блок АВДИ. Блбк ВОС, например, выполняет дополнительно функции инвертора, имеющегося в прбтотипе, синхронизатора импульсов входной частоты с опорной, формирователя коротких импульсов из. входного сигнала, что|повышает надежность работы устройства достоверность измеренного значения.

Более подробное изучение признаков и их свойств дает возможность обнаружить множество взаимосвязанных проявлений, создающих, кроме суммарного, дополнительный положительный эффект. Совокупность функциональных возможностей поззоляетиспользовать заявляемое устройство для исследования не только мгновенных значений угла закручивания, крутящего момента, но и для исследования знакопере- мен|ных крутильных колебаний, т.е. само ус- тро йство появляет новое свойство и обладает сверхсуммарным положительным эффектом. При этом расширяется область применения заявляемого устройства.

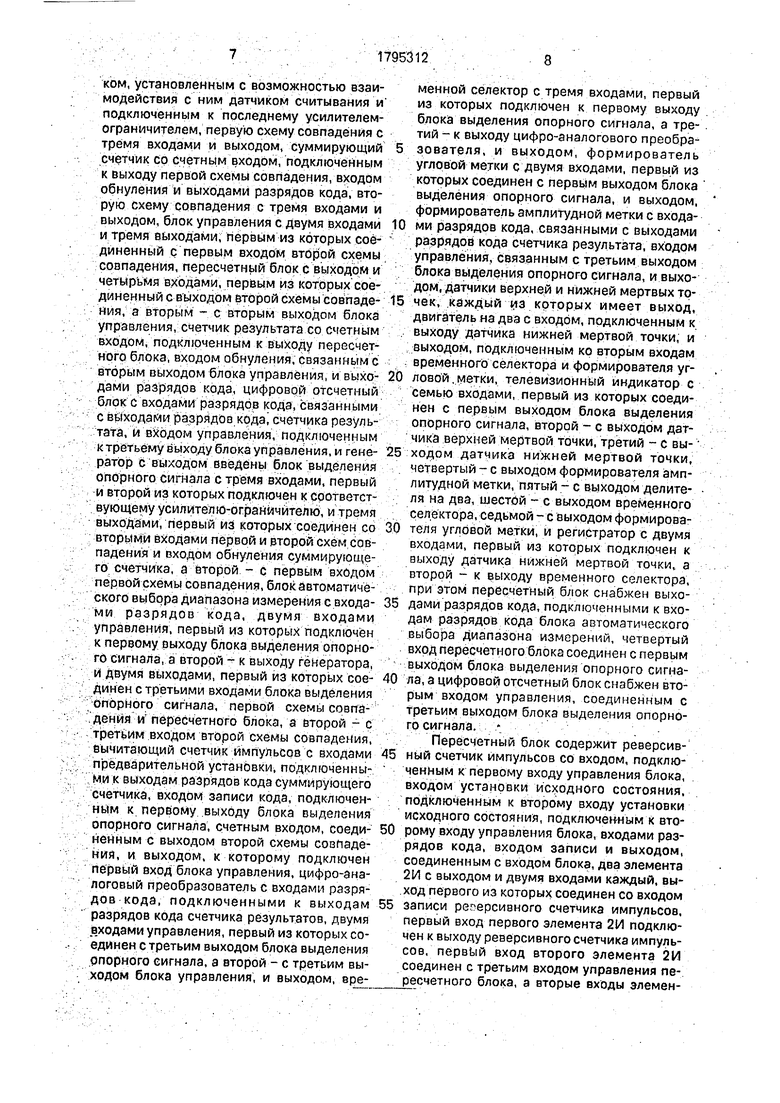

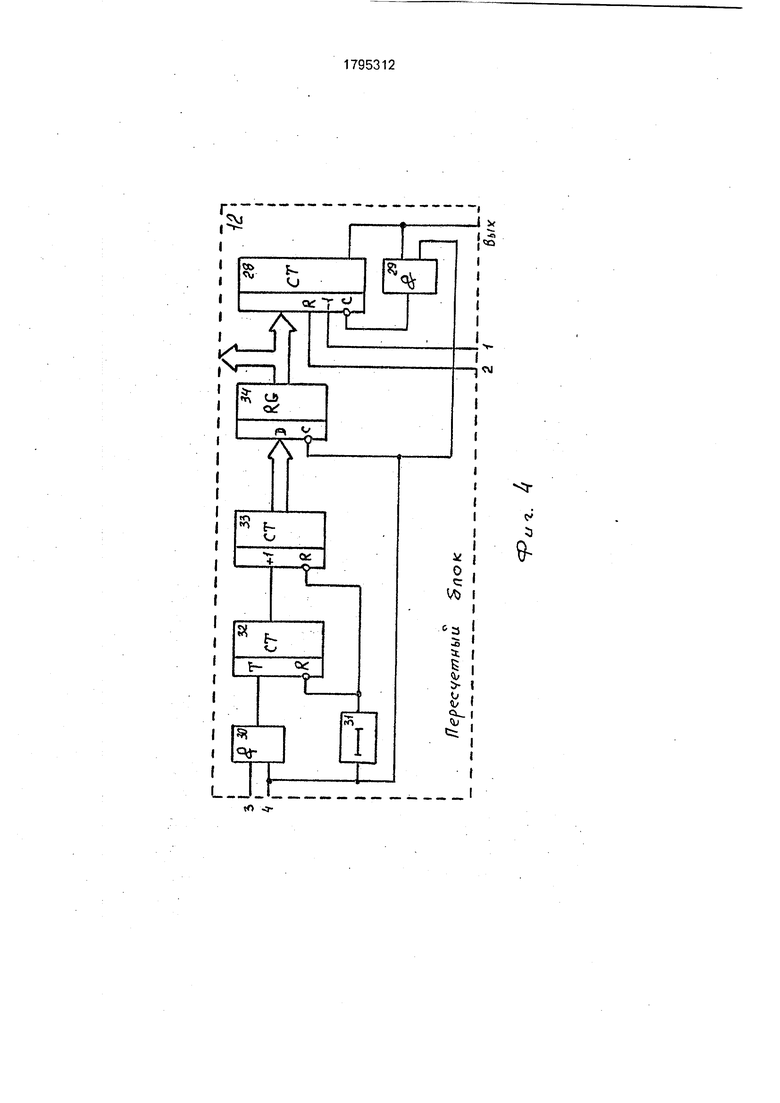

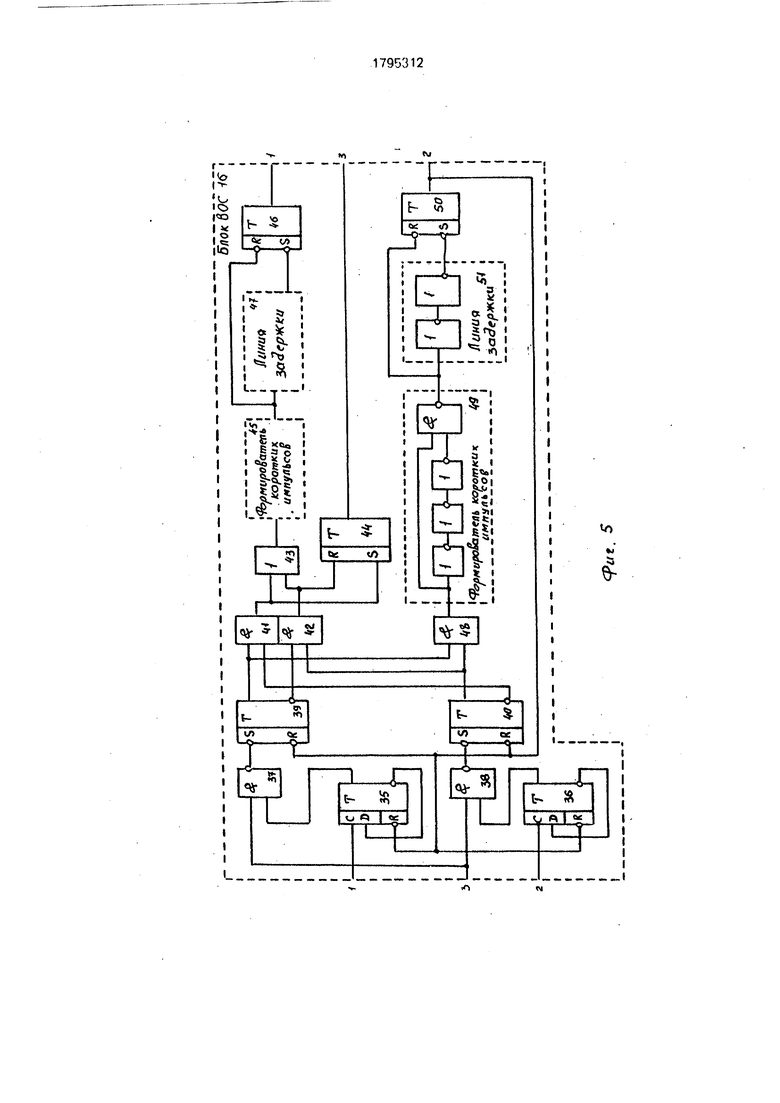

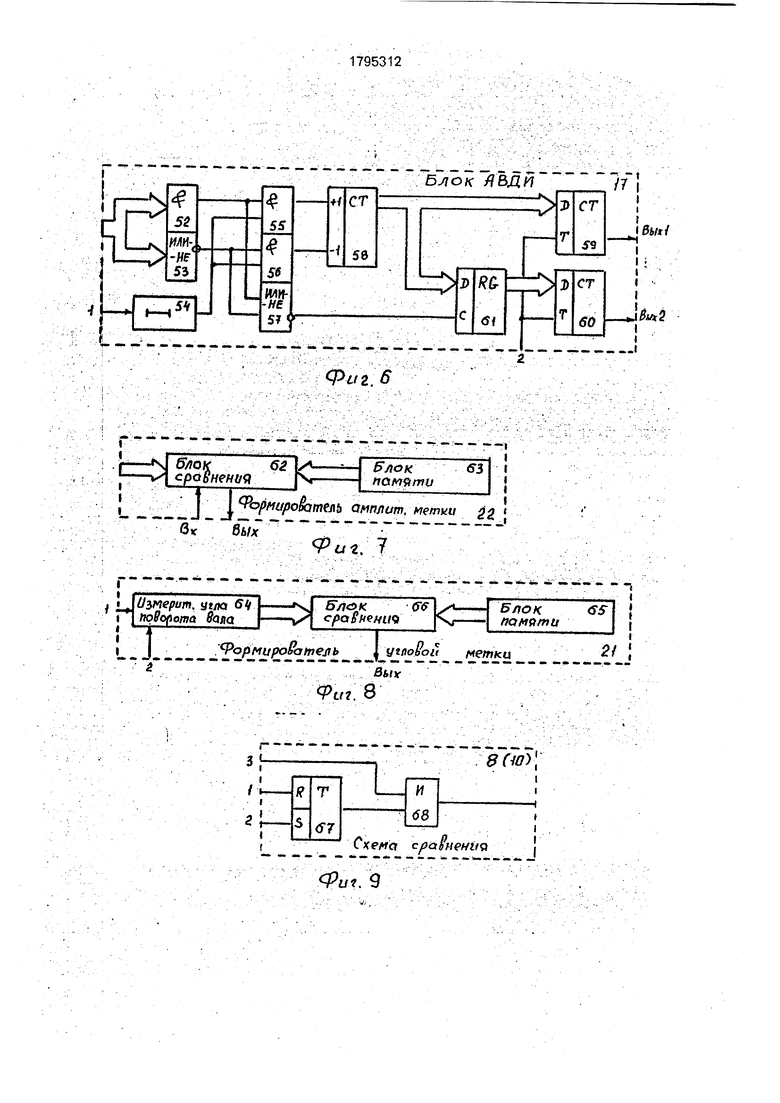

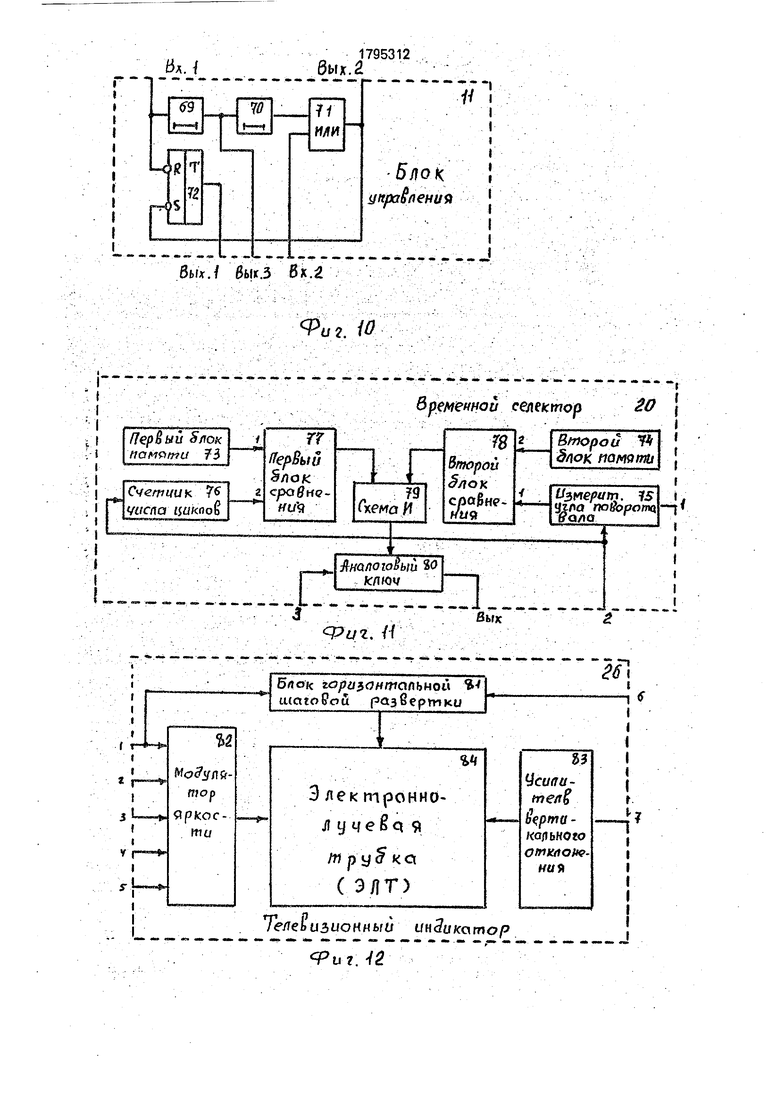

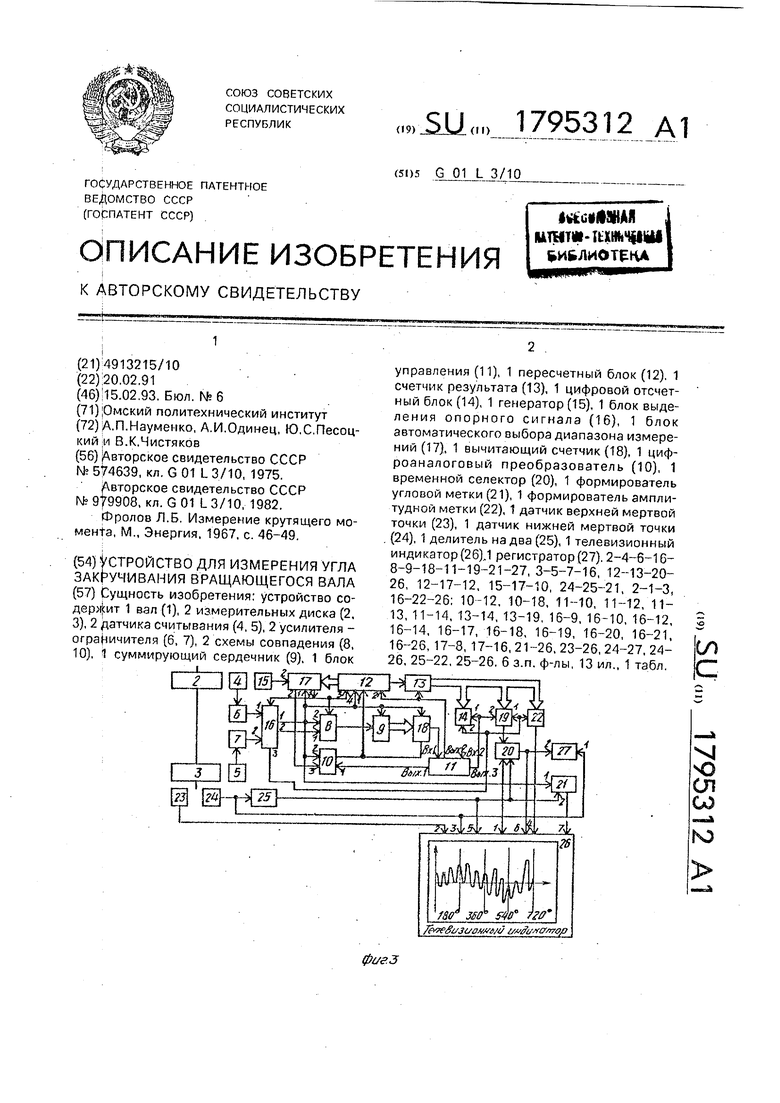

На фиг.З представлена структурная схема устройства для измерения угла закручи- вращающегося вала; на фиг.4 - пересчетного блока; на фиг.5 - блока выде- опорного сигнала; на фиг.б - блока автоматического выбора диапазона измере- ния;|на фиг.7 - формирователя амплитудной метни; на фиг.8 - формирователя угловой метни; на фиг.9 - схемы совпадения; на фиг. 10 - блока управления; на фиг.11 - временного селектора; на фиг. 12 -телевизионного индикатора; на фиг. 13 - временные диафаммы.

Устройство для измерения угла закручи- вани вращающегося вала (фиг.З) содержит две ветви, каждая из которых образована закрепленными на валу 1 измерительными диск эми 2 и 3, установленными с возможностью взаимодействия с ними датчиками 4 и 5 считывания и подключенными к последним усилителями-ограничителями 6 и 7, первую Јхему 8 совпадения с тремя входами и еыхоЬом, суммирующий счетчик 9 со счетным входом, подключенным к выходу первой схемы совпадения, входом обнуления и выходами разрядов кода, вторую схему 10 совпадения с тремя входами и выходом, блок 11 управления с двумя входами и тремя выходами, первым из которых соединенный с первым входом второй схемы 10 совпадения, ересчеткый блок 12 с выходом и четырьмя входами, первым из которых соединенный с выходом второй схемы 10

совпадения, а вторым - с вторым выходом блока 11 управления, счетчик 13 результата, со счетным входом, подключенным к выходу пересчетного блока 12, входом обнуления, 5 связанным с вторым выходом блока 11 управления, и выходами разрядов кода, цифровой отсчетный блок 14 с входами разрядов кода, связанными с выходами разрядов кода счетчика 13 результата, и входом

0 управления, подключенным к третьему выходу блока 11 управления, генератор 15 с выходом, блок 16 выделения опорного сигнала с тремя входами, первый и второй из которых подключен к соответствующим уси5 лителям-ограничителям б и 7, и тремя выходами, первый из которых соединен с вторыми входами первой и второй схем совпадения 8 и 10 и входом обнуления суммирующего счетчика 9, а второй - с первым

0 входом первой схемы 8 совпадения, блок 17 автоматического выбора диапазона измерения с входами разрядов кода, двумя входами управления, первый из которых подключен к первому выходу блока 1 б выде5 ления опорного сигнала, а второй - к выходу генератора 15, и двумя выходами, первый из которых соединен с третьими выходами блока 16 выделения опорного сигнала, первой схемы 8 совпадения и пересчетного бло0 ка 12, а второй - с третьим входом второй схемы 10 совпадения, вычитающий счетчик 18. импульсов с входами предварительной установки, подключенными к выходам разрядов кода суммирующего счетчика 9, вхо5 дом записи кода, подключенным к первому выходу блока 16 выделения опорного сигнала, счетным входом, соединенным с выходом второй схемы 10 совпадения, и выходом, к которому подключен первый

0 вход блока 11 управления., цифро-аналоговый преобразователь 19 с входами разрядов кода, подключенными к выходам разрядов кода счетчика 13 результатов, двумя входами управления, первый из которых

5 соединен с третьим выходом блока 16 выделения опорного Сигнала, а второй - с третьим выходом блока 11 управления, и выходом, временной селектор 20 с тремя входами, первый из которых подключен к

0 первому выходу блока 16 выделения опорного сигнала, а третий - к выходу цифро-аналогового преобразователя 19, и выходом формирователь 21 угловой метки с двумя входами, первый из которых соединен с

5 первым выходом блока 16 выделения опорного сигнала, и выходом, формирователь 22 амплитудной метки с входами разрядов кода, связанными с выходами разрядов кода счетчика 13 результата, входом управления, связанным с третьим выходом блока 16 выделения опорного сигнала, и выходом, датчики верхней 23 и нижней 24 мертвых точек, каждый из которых имеет выход, делитель

25 на два с входом, подключенным к выходу датчика 24 нижней мертвой точки, и выходом, подключенным ко вторым входам временного селектора 20 и формирователя 21 угловой метки, телевизионный индикатор

26 с семью входами, первый из которых соединен с первым выходом блока 16 выделения опорного сигнала, второй - с выходом датчика верхней 23 мертвой точки, третий - с выходом датчика 24 нижней мертвой точки, четвертый - с выходом формирователя 22 амплитудной метки, пятый - с выходом делителя 25 на два, шестой - с выходом временного селектора 20, седьмой - с выходом формирователя 21 угловой метки, и регистратор 27 с двумя входами, первый из которых подключен к выходу датчика 24 нижней мертвой точки, а второй - к выходу временного селектора 20, при этом пере- счетный блок 12 снабжен выходами разрядов кода, подключенными к входам разрядов кода блока 17 автоматического выбора диапазона измерений, четвертый блок пересчетного блока 12 соединен с первым выходом блока 16 выделения опорного сигнала, а цифровой отсчетный блок 14 снабжен вторым входом управления, соединенным с третьим выходом блока 16 выделения опорного сигнала,

Пересчетный блок 12 содержит реверсивный счетчик 28 импульсов со входом, подключенным к первому входу управления блока, входом установки исходного состояния, подключенным к второму входу управления блока, входами разрядов кода, входом записи и выходом, соединенным с выходом блока, два элемента 2И с выходом и двумя входами каждый, выход первого из которых соединен с входом записи реверсивного счетчика .28 импульсов, первый вход первого элемента 2И подключен к выходу реверсивного счетчика 28 импульсов, первый вход второго элемента 2И 30 соединен с третьим входом управления пересчетного блока 12, а вторые входы элементов 2И 29 и 30 соединены между собой и подключены к четвертому входу управления пересчетного блока 12, линию задержки 31 с входом, подключенным к четвертому входу управления пересчетного блока 12, и выходом, делитель 32 частоты импульсов со счетным входом, соединенным с выходом второго элемента 2И 30, входом установки исходного состояния, подключенным к выходу ли- нии задержки 31, и выходом, счетчик 33 импульсов со счетным входом, соединенным с выходом делителя 32 частоты импульсов, входом установки исходного состояния, соединенным с выходом линии задержки 31, и выходами разрядов кода, и регистр 34 памяти с входом записи кода, соединенным

с четвертым входом управления пересчетного блока 12, входами разрядов, подключенными к выходам разрядов кода счетчика 33 импульсов, и выходами разрядов кода, соединенными с входами разрядов кода ре0 версивногр счетчика 28 импульсов и выходами разрядов кода пересчетного блока 12,

Блок 16 выделения опорного сигнала содержит первый и второй D-триггеры 35 и 36, инверсные выходы которых соединены с

5 D-входами, а их С-входы соединены, соответственно, с первым и вторым входом блока 16 Выделения опорного сигнала, выходы подключены, соответственно, к первым входам первого и второго элементов 2И-НЕ 37

0 и 38, вторые входы которых соединены между собой и с третьим входом блока 16 выде- . ления опорного сигнала, выходы первого и второго элементов 2И-НЕ 37 и 38 подключены к S-входам, соответственно, первого и

5 второго RS-триггеров 39 и 40 с инверсными входами, выход первого 39 и инверсный выход второго 40 RS-триггеров соединены, соответственно, с первым и вторым входами первого элемента 2И 41, инверсный выход

0 первого 39 и выход второго 40 RS-тригге-; ров - соответственно, с первым и вторым входа- ми второго элемента 2И 42, выходы первого и второго элементов 2И 41 и 42 подсоединены, соответственно, к первому и второму

5 входам элемента ИЛИ 43 и к R и S входам третьего RS-триггера 44, выход элемента ИЛИ 43 подключен через формирователь 45 коротких импульсов к R-входу четвертого инверсного RS-триггерз 46 и к входу линии

0 47 задержки, выход которой соединен с S- входом четвертого RS-триггера 46, выход которого соединен с первым выходом блока 16 выделения опорного сигнала, выходы первого и второго RS-триггеров 39 и 40 подключе5 ны, соответственно, к первому и второму входам третьего элемента 2И 48, выход которого через формирователь 49 коротких импульсов соединен с R-входом пятого RS-триггера 50 с инверсными входами и к

0 входу линии 51 задержки/выход которой подключен к входу пятого RS-триггера 50, выход пятого RS-триггера 50 соединен с вторым выходом блока 16 выделения опорного сигнала, к третьему выходу которого подключен выход

5 третьего RS-триггера 44, при этом входу установки исходного состояния первых и вторых D- и RS-триггеров 35, 36, 39 и 40 соединены с выходом пятого RS-триггера 50.

Блок 17 автоматического выбора диапазона измерения содержит схемы И 52 и

ИЛИ-НЕ 53, входы которых поразрядно соединены между собой и с входами разрядов кода блока 17, линию задержки 54, вход которой подключен к первому входу блока 17 автоматического выбора диапазона из- мерейия, первый и второй элементы 2И 55 и 56J первые входы которых подключены, соответственно, к выходам схем И 52 и ИЛИ4-НЕ 53, вторые входы объединены и соединены с выходом линии задержки 54, элемент2ИЛИ-НЕ 57, первый и второй входы которого подсоединены, соответственно, к выходам схем И 52 и ИЛИ-НЕ 53, реверсивный счетчик 58 импульсов, вход прямого счета которого соединен с выходом первсго элемента 2И 55, и вход обратного счета;- с выходом второго элемента 2И 56, первь й и второй делители 59 и 60 частоты импульсов и регистр 61 памяти, причем входы разрядов кода первого делителя 59 .частоты подключены к выходам разрядов кода реверЫвного счетчика 58 импульсов, а входы разрядов кода второго делителя 60 частоты - к выходам разрядов кода реверсивного счетчика 58 импульсов через регистр 61 памяти, счетные входы первого и второго делителей 59 и 60 частоты импульсов соединены между собой и с вторым входом 17 автоматического выбора диапазона измерения, вход записи кода регистра памяти соединен с выходом элемента |2 ИЛИ-НЕ 57, а выходы первого и второгЬ делителей 59 и 60 частоты импульсов соединены, соответственно, с первым и вторым выходами блока 17 автоматического выбора1 диапазона измерения.

Формирователь 22 амплитудной метки содержит блок 62 сравнения с первыми и вторым и входами разрядов кода, входом управления и- выходом и блок 63 памяти с выхода ии разрядов кода, подключенными ко вторым входам разрядов кода блока 62 сравнения, причем первые входы разрядов кода, вз|:од управления и выход блока сравнения, (соответственно, соединены со входами разрядов кода, входом управления и выходов формирователя 22 амплитудной метки..

Формирователь 21 угловой метки содержит измеритель 64 угла поворота вала с выходами разрядов кода и с первым и вторым входами, соединенными, соответственно, с первым и вторым входами формирователя 21; угловой метки, блок 65 памяти с выходами разрядов кода и блок 66 сравнения с выходом, подключенным к выходу формирователя 21 угловой метки, и первыми и вторыми входами разрядов кода, соответственно, подключенными к выходам

разрядов измерителя 64 угла поворота вала и блока 65 памяти.

Каждая из схем совпадения 8 и 10 содержит RS-триггер 67 с инверсными входа- 5 ми и элемент 2И 68. причем входы R и S RS-триггера 67 каждой схемы совпадения, соответственно, соединены с ее первым и вторым входами, к третьему входу каждой схемы совпадения подключен первый вход

0 элемента 2И 68, выход которого связан с выходом схемы. 68 совпадения, а его второй вход - с выходом RS-триггера 67.

Блок 11 управления (фиг.10) содержит две линии задержки 69 и 70, элемент 2ИЛИ

5 71, RS-триггер 72 с инверсными входами, причем R-вход RS-триггера 72 и вход первой линии 69 задержки объединены и являются первым входом блока 11, выход RS-триггера 72 - первым-выходом блока 11, выход пер0 вой линии 69 задержки подключен к выходу второй линии задержки 70 и является третьим выходом блока 11, выход второй линии задержки 70 соединен с первым входом элемента 2ИЛИ 71, выход элемента 2ИЛИ 71

5 соединен с S-входом RS-триггера 72 и является вторым выходом блока 11 управления, : второй вход элемента 71 2ИЛИ является вторым входом блока 11 управления.

Временной селектор 20 (фиг.11) содер0 жит первый и второй блоки 73 и 74 памяти, в которые оператор заносит необходимую информацию, измеритель 75 угла поворота вала, первый вход которого является первым входом временного селектора 20, счет5 чик 76 числа циклов, вход которого объединен с зторым входом измерителя 75 угла поворота к является вторым входом временного селектора 20, первый и второй блоки 77 и 78 сравнения, причем первый

0 вход первого блока 77 сравнения соединен с выходом первого блока 73 памяти, второй вход - с выходом счетчика 76 числа циклов, первый вход второго блока 78 сравнения - с выходом измерителя 75 угла поворота,

5 второй вход - с выходом второго блока 74 памяти, схему И 79, первый и второй входы которой соединены, соответственно, с выходами первого и второго блоков 77 и 78 сравнения, анзлогозый ключ 80, первый вход

0 которого подключен к выходу схемы И 79, второй вход является третьим входом временного селектора 20, выход-выходом временного селектора.

Телевизионный индикатор 26 (фиг.12)

5 содержит блок 81 горизонтальной шаговой развертки, модулятор 82 яркости, усилитель 83 вертикального отклонения, подключенные к соответствующим входам электроннолучевой трубки (ЭЛТ) 84, причем первый вход телевизионного индикатора 26 является входом модулятора 82 яркости и первым входом блока 81 горизонтальной шаговой развертки, второй, третий, четвертый и пятый входы - соответствующими входами модулятора 82 яркости, шестой вход - вторым входом блока 81 горизонтальной шаговой развертки, а седьмой вход - входом уилите- ля 83 вертикального отклонения.

Измерительные диски 2 и 3, датчики считывания 4 и 5, усилители-ограничители 6 и 7 выполнены аналогично известным. Схемы совпадения 8 и 10 могут быть выполнены, например, на микросхемах (МС) типа К155ТМ2, К155ЛИ1, Суммирующий счетчик 9 может быть выполнен на МС К155ИЕ7, причем вход R должен быть подключен через линию задержки на двух-четырех инверторах типа К155ЛН1. (В начале информация переписывается из счетчика 9 в счетчик 18, а затем через время, определяемое линией задержки, обнуляется счетчик 9).

Блок управления 11 - МС К155ТМ2 (RS- триггер), К155ЛН1 (линии задержки), К155ЛЛ1 (элемент 2ИЛИ). Пересчетный блок 12 - МС К155ЛИ1 (элемент 2И), К155ИЕ8 (делитель 32 частоты), К155ИЕ7 (счетчики 28, 33), К155ИР13 (регистр 34 памяти).

Счетчик 13 результата - МС К155ИЕ6, К155ИЕ7. Известны схема цифрового отсчет- ного блока 14, схема генератора 15. Блок 16 ВОС - МС типа К155ТМ2 (35, 36, 39, 40, 44, 46,50), К155ЛАЗ (37,38), К155ЛИ1 (41,42,48), К155ЛЛ1 (43), К155ЛН1, К155ЛАЗ (49, 51).

Известна схема формирователей коротких импульсов 45, 49.

Блок 17 АВДИ МС типа К155ЛА2, К155ЛЕ1 (52), К155ЛА8 (53), К155ЛИ1 (54), К155ЛИ1 (55, 56). К155ЛЕ1 (57), К155ИЕ7 (58), К155ИР13 (61), К155ИЕ6, К155ИЕ7(59, 60).

Вычитающий счетчик 18 - МС типа К1551/1Е7. Цифро-аналоговый преобразователь 19 - МС типа К594ПА1, Аналоговый ключ 80 - МС КР590КН2. Блоки 62, 66,77,78 сравнения выполнены путем каскадного соединения компараторов 564ИП2. Делитель 25 на два выполнен на основе триггера К155ТВ1.

Блоки 63, 65, 73, 74 памяти представляют собой цепи из последовательно соединенных счетчиков по модулю 10 с дешифратором для вывода информации на семисегментный индикатор К176ИЕ4. Счетный вход счетчика подключен к выходу генератора импульсов на МС К155АГЗ по известной схеме, которым управляет опера- „тор. Частота импульсов на выходе генератора выбрана равной 1-2 Гц. На разрешающий вход Р через переключатель подается логический О или логическая 1.

При Р 0 колебания срываются. Оператор с помощью переключателя устанавливает необходимый код на выходе счетчика (т.е. на выходе соответствующего блока памяти),

контролируя его значение с помощью индикатора.

Измерители 64 и 75 угла поворота вала представляют собой счетчики импульсов. Каждый счетчик выполнен путем последова0 тельного соединения МС К176ИЕ1. На счетный вход каждого из счетчиков поступают импульсы с выхода 1 блока 16 ВОС, а на входы обнуления R подаются через делитель 25 на два импульсы от датчика 24 НМТ,

5 Блок 81 горизонтальной шаговой развертки функционирует как цифровой генератор ступенчатого линейно-изменяющегося напряжения, работающий в ждущем режиме. В состав блока входят последова0 тельно.соединенные двоичный счетчик/две МС К176ИЕ1 и ЦАП К594ПА1. Ступенчатое напряжение формируется при помощи ЦАП, на вход которого поступает линейно-изменяющееся во времени число. Для получения

5 такого числа на счетный вход счетчика подаются сигналы с выхода 1 блока 16 ВОС, а на вход сброса счетчика через делитель 25 на два импульс с датчика 24 НМТ.

Модулятор 82 яркости управляет вели0 чином тока луча ЭЛТ телевизионного индикатора 26 и состоит из сумматора и усилителя, выполненных по типовым схемам. Усилитель 83 вертикального отклонения смещает электронный луч ЭЛТ 84 по

5 вертикали и также вы полнен по типовой схеме.

Измерители 64 и 75 угла попорота вала в блоках 20 и 21 формируют код, который соответствует углу поворота вала в преде0 лах от 0° до 720°, что необходимо для формирования меток на экране ЭЛТ.

Блоки 63, 65, 73, 74 памяти в составе блоков 20, 21 и 22 предназначены для хранения информации, которую оператор зано5 сите помощью управляющих органов.

Цифровой отсчетный блок 14 представляет собой цифровой индикатор, показывающий угол закручивания.

Устройство (фиг.З) для измерения угла

0 закручивания вращающегося вала работает следующим образом.

При вращении вала 1 измерительные диски 2 и 3 перемещаются относительно датчиков 4 и 5 и наводят гармоническую ЭДС

5 в них, которая превращается в последовательность прямоугольных импульсов усилителями-ограничителями 6 и 7 и поступает на первый и второй входы блока 16 ВОС. В блоке 16 ВОС фронты входных импульсов синхронизируются с тактовой частотой, поступающей на третий вход блока 16 ВОС из блока 17 АВДИ, и один из входных импульсовЕ ыделяется в качестве опорного. На первом выходе блока 1 б ВОС появляется сигнал раньше, чем на втором выходе этого же бло- ка и шляется опорным во время дальнейшего процесса измерения, не зависимо от врек ени прихода входных импульсов относите1ьно друг друга на первый и второй входы блока 16 ВОС. На третьем выходе блока 16 ВОС присутствует бит информации, свидетельствующий о запаздывании или опережении импульса на первом входе блок|а 16 ВОС относительно импульса на вторам входе. Опорный сигнал с первого выхсда поступает на вторые входы схем совпадения 8 и 10, на суммирующий счетчик 9, на Е ычитающий счетчик 18, пересчетный блок 12 и блок 17 АВДИ,- на первый вход временного селектора 20, формирователя 21 у ловой метки, телевизионного индикатора 26. В момент прихода этого импульса на эти блоки происходит следующее: инфор- мац1/я о результате предыдущего измерения (числа импульсов за время фазового сдвига) из счетчика 9 переписывается в счетчик 1J8, счетчик 9 обнуляется, схема 8 совпадений начинает пропускать импульсы тактевой частоты с первого выхода блока 17 АВДИ на счетный вход счетчика 9, начинает свою работу пересчетный блок 12 по опре- числа импульсов М тактовой чги в единице младшего разряда измеряемой величины, схема 10 совпаде ачинает пропускать импульсы такто- цастоты со второго выхода блока 17 Л через третий вход этой схемы, при

НИИ

вой

АВД

этом на первом входе схемы 10 совпадений

присутствует разрешающий работу схемы

сигнал, и импульсы начинают поступать на

счетвый вход вычитающего счетчика 18 и на

первУй вход пересчетного блока 12.

$ момент прихода импульса со второго выхоЬа блока 16 ВОС на второй вход первой схем(ы совпадений 8 счетчик 9 прекратит свою работу и в нем до момента перезаписи опорным импульсом будет храниться новое число N, соответствующее числу импульсов актовой частоты за время фазового сдвига.

Wa вычитающий счетчик 18 и пересчетный Блок 12 импульсы со второй схемы 10 совпадений будут поступать до тех пор, пока на выходе обратного счета счетчика 18 не появится импульс, свидетельствующий об окончании вычитания числа N из счетчика 18, который поступает на первый вход блока

11 уг

дейс

равления. Этот импульс приведет его вме и на первом выходе блока 11 управления появится импульс, который запре510 15 20 5 0

5

0

5

0

5

тит работу второй схемы 10 совпадения. Во время работы счетчика 18 на первый вход пересчетного блока 12 поступают импульсы, общее количество которых равно числу N импульсов тактовой частоты за время фазового сдвига, и эти импульсы пересчетный блок 12 разделит на число М импульсов в япиниие младшего разряда измеряемой величины, например, в 0,1°. Таким образом, с выхода пересчетного блока 12 на счетчик 13 результата поступит число импульсов К, являющееся результатом деления N на М, которое и будет показывать угол закручивания с точностью до одной единицы младшего разряда измеряемой величины, например, с точностью до 0,1°, причем направление закручивания фиксируется с помощью бита информации с третьего выхода блока 16 ВОС. После прихода импульса с выхода счетчика 18 на первый вход блока 11 управления и появления импульса на первом выходе этого блока сигнал с третьего выхода блока 11 управления поступит на первый вход цифрового отсчетного блока 14, второй вход ЦАП 19, второй вход формирователя 22 амплитудной метки. В момент прихода этого импульса двоичный код, содержащий информацию о результате измерения угла закручивания, запишется в ЦАП 19, формирователь 22 амплитудной метки, временной селектор 20, причем на эти же блоки в виде бита информации приходит сигнал с третьего выхода блока 16 ВОС о знаке измеряемой величины. С приходом следующего опорного импульса с первого выхода блока 16 ВОС код нового числа N1 перепишется из счетчика 9 в счетчик 18 и процесс измерения повторится. Из описания видно, что измерение производится за два периода входного сигнала: во время первого периода происходит подсчет импульсов за период пересчетным блоком 12 и за время фазового сдвига счетчиком 9, во втором - нормирование, т.е. деление N на М, числа импульсов за время фазового сдвига и вывод результата. Причем, во время второго периода одновременно идет подсчет числа импульсов за период и за время фазового сдвига этого, второго, периода.

Блок 16 ВОС работает следующим образом.

Сигналы с выходов усилителей-ограничителей 6 и 7 поступают, соответственно, на первый и второй входы блока 16 ВОС, а на третий вход поступают импульсы тактовой частоты. Предположим, что импульс на первом входе появится раньше, чем на втором входе. В этом случае D-триггер 35 переключится в единичное состояние, сигнал поступит на первый вход элемента 2И-НЕ 37 и разрешит прохождение импульсов тактовой частоты на вход S RS-триггера 39. По первому импульсу на этом входе RS-триггер 39 переключится в единичное состояние. Этот сигнал поступит на первый вход элемента 2И 41 и при наличии уровня логической 1 на втором входе (RS-триггер 40 не переключен) уровень логической 1 поступит на первый вход элемента 2ИЛИ 43 и на вход RS-триггера 44 и установит его в единичное состояние. Таким образом, логическая Г на выходе RS-триггера ,44 и третьем выхбде блока 16 ВОС будет представлен бит информации о том, что сигнал на первом входе блока 16 ВОС опережает по фазе сигнал на втором входе. С выхода элемента 2ИЛИ 43 сигнал проходит через формирователь 45 коротких импульсов, поступает на вход R RS-триггера 46 и устанавливает его в нулевое состояние. Через время, которое определяется линией задержки 47, RS-триггер46 установится обратно в единичное состояние. Таким образом, на первом выходе блока 16 ВОС появится опорный импульс (фиг.13е). Затем при появлении импульса на втором входе блока 16. ВОС D-триггер 36 переключится в единичное состояние и через элемент 2И-НЕ 38 импульсы тактовой частоты поступят на S-вход RS-триггера 40. По первому импульсу RS-триггер 40 Переключится в единичное состояние. Так как на первом входе элемента 2И 42 присутствует логический О, а на первом входе элемента 2И 48 - логическая 1, то сигнал с RS-триггера 40 поступит через второй вход элемента 2И 48 на формирователь 49 коротких импульсов, а с его выхода - на вход линии задержки 51 и на R-вход RS-трйггера 50, который переключится в нулевое состояние. Через время, определяемое линией задержки 51, импульс с ее выхода поступит на S- вход RS-триггера 50 и он установится в единичное состояние, В результате этого на втором выходе блока 26 ВОС появится импульс (фиг.13,д). Этот же импульс поступит на входы установки в нулевое состояние триггеров 35, 36, 39 и 40. После этого блок 16 ВОС готов к обработке следующих импульсов. Если импульс на втором входе блока 16 ВОС появится раньше, чем на первом входе, то D-триггер 36 переключится в единичное состояние, импульс тактовой частоты через элемент 2И-НЕ 38 переключит RS-триггер 40 и логическая 1 с его выхода поступит на второй вход элемента 2И 42, на .втором входе элемента 2И 41 установится сигнал логического О, который запретит прохождение сигнала с выхода RS-триггера 39 на выход элемента 2И 41, логическая Г

установится и на втором входе элемента 2И 48. С выхода элемента 2И 42 сигнал поступит через элемент 2ИЛ И 43, формирователь 45 коротких импульсов на R-вход RS-триггера 46. на выходе которого появится логический О, а через время, определяемое линией задержки 47, на выходе RS-триггера 46установится логическая 1 (фиг.13,г). Таким образом, формируется опорный сигнал

на первом выходе блока 16 ВОС от импульса со второго входа блока 16 ВОС. При появлении импульса на первом входе блока 16 ВОС D-триггер 35 переключится в единичное состояние, импульс тактовой частоты с третьего входа блока 16 ВОС установит на выходе RS-триггера 39 логическую 1, которая поступит на вход элемента 2И 48. Сигнал с выхода элемента 2И 48 передается через формирователь 49 коротких импульсов на

R-вход RS-триггера 50 и установит его в нулевое состояние. Через время, определяемое линией задержки 51, RS-триггер 50 установится в единичное состояние (фиг.13,д), При появлении логического О на

выходе RS-триггера 50 триггеры 35, 36, 39 и 40 установятся в нулевое состояние и блок 16 ВОС будет готов к обработке новых входных импульсов.

Пересчетный блок 12 работает следующим образом (фиг.4).

На второй вход элемента 2И 30 поступает импульс опорного сигнала, который пере- писывает результат предыдущего цикла измерения в регистр 34 памяти, а пройдя

через элемент 2И 29 записывается код с выхода регистра 34 памяти в реверсивный счетчик 28 импульсов. Импульс опорного сигнала, пройдя через линию задержки 31, обнуляет делитель 32 частоты импульсов и

счетчик 33 импульсов, Во время присутствия импульса на втором входе элемента 21/1 30 тактовая частота не проходит на вход делителя 32 частоты импульсов. После окончания опорного импульса на втором входе

элемента 2И 30 установится логическая 1 и импульсы тактовой частоты поступают на счетный вход делителя 32 частоты импульсов. Коэффициент деления делителя 32 частоты импульсов определяется следующим

образом

L. t

360

где k - число импульсов за один оборот вала;

п - точность измерения (или единица младшего разряда измеряемой величины).

Так, если за один оборот вала формируется два импульса, а точность измерения 0,1°, то коэффициент деления делителя 32

чафтоты импульсов составит 1800. Таким обратом, при делении импульсов тактовой ча- стфты за время между двумя опорными импульсами на это число в счетчик 33 им- nyiibcoB поступит число импульсов тактовой частоты, приходящихся на единицу младшего разряда измеряемой величины М. Дво- ичфый код этого числа следующим опорным имЬульсом перепишется в регистр 34 памяти.; Этот код поступит в блок 17АВДИиэтим же| импульсом через элемент 2И 29 перепишется в реверсивный счетчик 28 импульсов в качестве его коэффициента деления. После этого на первый вход реверсивного счетчика 28 импульсов начнут поступать импульсы с выхода схемы 10 совпадений, число которых равно числу N импульсов тактовой частоты за время фазового сдвига. образом, осуществляется деление числа N импульсов тактовой частоты за вр€ мя фазового сдвига на число М импуль- СОЕ тактовой частоты в единице младшего разряда измеряемой величины, что дает число К, соответствующее углу закручивание в градусах с точностью до единицы млг дшего разряда измеряемой величины. С выхода реверсивного счетчика 28 импульсов К импульсов поступает в счетчик 13 результата.

: Блок 17 АВДИ (фиг.6) предназначен для автоматического изменения частоты тактовых; импульсов с целью расширения диапазона входных частот при оптимально-минимальной разрядности счетчиков 9, 18, 28 и других блоков устройства и работает следу- ющИм образом. На входы схем И 52 и ИЛИ- НЕ |53 поступает код с выхода регистра 34 памяти пересчетного блока 12, В случае присутствия в разрядах кода на входе блока 17 АВДИ всех логических 1 - это может произойти только в момент прихода опор- ногр импульса на вход пересчетного блока 12, - что свидетельствует о возможности, при; дальнейшем уменьшении частоты сигнал, заполнения максимальной емкости счетчика 33 импульсов, т.е. частота тактовых имНульсов при данной входной частоте на- сто/ibKO велика, что счетчику 33 импульсов (и другим) грозит переполнение, на выходе фемы И 52 появится логическая 1. По- еле Јтого в регистр 61 памяти через элемент ИЛЙ-НЕ 57 запишется код реверсивного счет|чика 58 импульсов, соответствующий коэффициенту деления частоты импульсов в только что прошедшем периоде входного сигйала. В момент прихода опорного им- пуль)са через время, определяемое линией задержки 54 на входе прямого счета ревер- сив4ого счетчика 58 импульсов появятся сигфл, который увеличит код на выходе реверсивного счетчика 58 на единицу. Если разряды реверсивного счетчика 58 импульсов будут подключены к разрядам делителя частоты 59 импульсов и регистра 61 памяти не с первого, а например, младший разряд реверсивного счетчика 58 импульсов будет подключен к четвертому разряду делителя 59 частоты импульсов и регистра 61 памяти, второй разряд - к пятому разряду, третий - к шестому и т.д., то при появлении логической 1 в младшем разряде реверсивного счетчика 58 импульсов коэффициент деления делителя 59 частоты импульсов, а в следующем периоде и делителя 60 частоты импульсов, увеличится в восемь раз, что и обеспечит уменьшение частоты тактовых импульсов на выходе блока 17 АВДИ и счетчику 33 импульсов уже не будет грозить переполнение, так что число импульсов в единице младшего разряда измеряемой величины в данном случае уменьшится в восемь раз. Запись кода в регистр 61 памяти необходим по следующим соображениям. Предположим, что до момента изменения кода в реверсивный счетчик 58 импульсов частота тактовых импульсов на первом и втором выходах блока 17 АВДИ соответствовала F1 и коэффициент деления делителей 59 и 60 импульсов - Кд1. При изменении кода на выходе реверсивного счетчика 58 импульсов тактовая частота импульсов на первом выходе блока 17 АВДИ станет равной F2, а коэффициент деления делителя 59 частоты - Кд2. Теперь рассмотрим процесс изменения частоты тактовых импульсов на первом и втором выходах блока 17 АВДИ. Пусть в первом периоде на первом и втором выходах блока 17 АВДИ будет частота F1. При изменении частоты входного сигнала с измерительных дисков 4 и 5 таким образом, что на выходе реверсивного счетчика 58 импульсов код примет значение Кд2 и, следовательно, частота заполнения счетчика 9 импульсов будет F2. Однако, в регистре 58 памяти хранится число М1 импульсов тактовой частоты Ft в единице младшего разряда, а в вычитающем счетчике 18 хранится число М импульсов тактовой частоты F1 за время фазового сдвига. Если на счетчики 18 и 28 импульсов подавать частоту F2 с первого выхода блока 17 АВДИ, то получится неправильный результат измерения. Для предотвращения этого со второго выхода блока 17 АВДИ на счетчики 18 и 28 импульсов подается частота тактовых импульсов F1. а а это время в. течение текущего периода в счетчиках 33 и 9 импульсов накапливается, соответственно, число М2 импульсов тактовой частоты F2 и число N2 импульсов

тактовой частоты F2..B момент прихода следующего опорного импульса и начала третьего периода входной частоты код на выходе регистра 34 памяти изменится таким образом, что на выходе схемы И 52 появится логический О и с выхода элемента ИЛИ- НЕ 57 поступит сигнал, который запишет код Кд2 в регистр 61 памяти и в течение третьего периода входной частоты с первого и второго выходов блока 17 АВДИ будут поступать импульсы с частотой .F2. При этом необходимо заметить, что изменение тактовой частоты импульсов на первом и втором выходах блока 17 АВДИ должно быть таким, чтобы в момент присутствия на втором выходе частоты F2, а на первом выходе - F1, при частоте F2 счетчику 33 . импульсов не грозило переполнений, что зависит от скорости изменения входной частоты сигнала и устраняется подбором подключения младшего разряда реверсивного счетчика 58 импульсов к.тому или иному разряду регистра 61 памяти и делителя 59 частоты импульсов. В случае наличия во всех разрядах кода на входах блока 17 АВДИ логического О на выходе схемы ЙЛИ- НЕ 5.3 появится логическая 1 и запишет код в регистр 61 памяти. Опорный импульс, пройдя через линию задержки 54 и элемент 2И 56, поступит на вход обратного счета реверсивного счетчика 58 импульсов и уменьшит код на его выходе на единицу, Дальнейшая работа блока 17 АВДИ описана выше с той разницей, что частота на первом и втором выходах блока 17 АВДИ увеличи- езется..

Блок 11 управления (фиг. 10) работает следующим образом.

На первый вход блока 11 управления поступает с выхода реверсивного счетчика 18 импульс и устанавливает RS-триггер 72 в состояние логического О, который поступает на первый выход блока 11, Затем им- пульс проходит через линию задержки 69, поступает на второй выход блока 11 управления, проходит линию задержки 70, -элемент 2ИЛИ 71 и устанавливает RS-триггер 72 в единичное состояние.

Схемы 8 и 10 совпадения (фип9) работают Следующим образом.

На вторые входы схем 8 и 10 совпадения приходит сигнал и устанавливается логическая 1 на выходе RS-триггера 67, который разрешает прохождение импульсов тактовой частоты через элемент 2Й 68. Сигнал, поступивший на первые входы схем 8 и 10 .совпадения, устанавливает RS-триггер 67 в нулевое состояние и прохождение импульсов тактовой частоты через элемент 2И 68 прекращается.

Одновременно с регистрацией угла за- кручив ания вращающегося вала цифровым отсчетным блоком 14 на телевизионном индикаторе 26 отображается кривая зависимости угла закручивания от угла поворота вала. С этой целью на входы телевизионного индикатора 26 поступает сигнал с первого выхода блока 16 ВОС, несущий информацию об угловом перемещении вала прршне0 вой машины, сигналы с датчиков ВМТ 23 и НМТ24. В результате этого осуществляется горизонтальное перемещение электронного луча электронно-лучевой трубки (ЭЛТ) 84 телевизионного индикатора 26 с шагом,

5 пропорциональным угловому перемещению вала. Начало развертки совпадает с моментом прохождения поршнем НМТ в начале цикла, а ее конец - НМТ в конце цикла. На вход усилителя 83 вертикального откло0 нения поступает сигнал с временного селектора 20, который пропорционален углу закручивания, а на вход модулятора 82 яркости - импульсы о моментах совпадения угла закручивания с сигналом амплитудной

5 метки и о моментах совпадения угла поворота вала с сигналом угловой метки. Таким образом, на экране ЭЛТ 84 формируется последовательно цикл за циклом изображение кривой зависимости угла закручивания

0 от угла поворота и амплитудная и угловая метки. ;

Временной селектор 20 (фиг. 11) работает следующим образом.

В первый блок 73 памяти информация о

5 выбранном цикле заносится оператором, а счетчик 76 числа циклов, связанный с датчиком 24 НМТ, осуществляет счет числа циклов с момента включения поршневой машины. В момент совпадения кодов, по0 ступающих на входы первого блока 77 сравнения, формируется импульс, длительность которого равна длительности выбранного цикла. Второй блок 78 сравнения связан с измерителем 75 угла поворота вала и вто5 рым блоком 74 памяти. Во второй блок 74 памяти информация об угловом положении выбранной части цикла заносится оператором. Измеритель 75 угла поворота вала, свя- эанный с датчиком 24 НМТ и первым

0 выходом блока 16 ВОС, осуществляет измерение углового положения вала. Измеритель 75 угла поворота вала периодически производит счет числа импульсоа, поступающих с первого выхода блока 16 ВОС, а

5 начало счета совпадает с передним фронтом каждого второго импульса, поступающего с выхода датчика 24 НМТ, т.е. подсчет ведется в течение цикла поршневой машины, В момент совпадения кодов, поступающих на входы второго блока 78 сравнения,

формируется импульс, длительность которого совпадает с длительностью выбранной части цикла. Следовательно, на первый и второй входы схемы И 79 временного селектора 20 поступают следующие сигналы: пря- мо гольный импульс с выхода первого бло|ка 77 сравнения, совпадающий по времени с выбранным оператором циклом, прямоугольный импульс с выхода второго блока 78 равнения, совпадающий по времени с выбранной оператором частью цикла, например с процессом сжатия.

С выхода схемы И 79 сигнал открывает аналоговый ключ 80, который пропускает си™ ал с выхода ЦАП 19 на шестой вход теле визионного индикатора 26, а в нем - на усилитель 83 вертикального отклонения. Таким збразом, временной селектор 20 осуще- ствл|яет временное стробирование сигнала, несущего информацию о мгновенном значении угла закручивания вращающегося вала.

формирователь 22 амплитудной метки (фиг.7) работает следующим образом.

На первые входы разрядов кода блока 62 сравнения поступает цифровой код с выхода счетчика 13 результата, несущий ин- об угле закручивания вала. На вторые входы разрядов кода блока 62 сравненное блока 63 памяти подается цифровой код, оторый устанавливается оператором до во время процесса измерения. Этот код, 1зпример, может соответствовать определенному углу закручивания, который хочет увидеть оператор. Этот угол отобразится на экране более яркими точками, чем вся остальная кривая зависимости угла за- кручийания от угла поворота, так как в момент ровпадения кодов с выходов счетчика 13 результата и блока 63 памяти на выходе формирователя 22 амплитудной метки поя- вится имлульс, который поступит на модулятор 82 яркости телевизионного индикатора

26- ,

Формирователь 21 угловой метки (фиг.8 работает следующим образом.

На первый вход измерителя 64 угла поворот; i вала поступают импульсы с первого выхода блока 16 ВОС, несущие информацию об угловом перемещении вала, а на второй вход измерителя 64 угла поворота вала подаются импульсы с датчика 24 НМТ через целитель 25 на два. Измеритель 64 угла пс ворота вала периодически осуществляет с1 ет числа импульсов, приходящих на его первый вход. Начало счета совпадает с передг им фронтом каждого второго им- пульса поступающего с датчика 14 НМТ на вход делителя 25 на два. Таким образом, измеритель 64 угла поворота вала осуществляет подсчет числа импульсов с первого

выхода блока 16 ВОС за цикл поршневой машины, который обычно составляет четыре такта или два оборота вала. Цифровой код с выхода измерителя 64 угла поворота вала 5 поступает на первые входы разрядов кода блока 66 сравнения, а на вторые входы разрядов кода поступает код с выхода блока 65 памяти. Этот код устанавливает оператор. В момент совпадения кодов, поступающих на

10 входы блока 66 сравнения, формируется импульс, который поступает на вход модулятора 82 яркости и подсвечивает нужный оператору угол поворота.

Блок 81 горизонтальной шаговой раз5 вертки функционирует как генератор ступенчатого линейно-изменяющегося напряжения (ГЛИН), работающего в ждущем режиме. На его входы поступают сигналы с датчика 24 НМТ и с первого выхода

0 блока 16 ВОС. Напряжение с блока 81 горизонтальной шаговой развертки поступает на отклоняющую систему телевизионного индикатора 26 и осуществляет горизонтальное перемещение электронного луча. Дли5 тельность развертки равна времени цикла поршневой машины, которое в данном слу- чзз равно длительности двух оборотов вала (четырехтактный двигатель) и может быть изменено путем изменения коэффициента

0 деления делителя 25 на два. Начало развертки электронного луча совпадает с моментом прохождения поршнем НМТ в начале цикла, а ее конец - НМТ в конце цикла. Затем следует обратный ход электронного

5 луча. Количество элементов разложения по горизонтали определяется числом опорных импульсов, поступивших с первого выхода блока 16 ВОС за один цикл работы поршневой машины. Если опорные импульсы посту0 пают, например, через два градуса по углу поворота, что вполне достаточно для исследования мгновенных значений угла закручивания вала и совершаемых крутильных колебаний, то элементов разложения по го5 ризонтали равно 360 (720 : 2 360). Количество элементов разложения определяется размером ЭЛТ 84 телевизионного индикатора 26, диаметра электронного луча и разрядностью ЦАП 19. Если разрядность ЦАП

0 19 равна восьми, то число элементов разложения по вертикали равно 512 (). Это меньше, чем принятое число строк разложения по стандарту для телевизионных приемников, равное 625. На модулятор 82 яркости

5 поступают импульсы от датчиков ВМТ 23 и НМТ 24 и с первого выхода блока 16 ВОС. В результате этого линии развертки имеют соответствующие метки, информирующие об угловом положении коленчатого вала поршневой машины. Таким образом, на экране

ЭЛТ 84 формируется изображение кривой, которая определяет угол закручивания вращающегося вала от угла его поворота. Изображение при этом остается устойчивым независимо от числа оборотов вала.

Предлагаемое устройство для измерения угла закручивания вращающегося вала имеет следующие режимы работы:

непрерывное измерение угла закручивания в процессе работы поршневой машины и индикация результатов цифровым отсчетным блоком;

регистрация и визуальное наблюдение кривой зависимости угла закручивания от угла поворота вала на самописце и на экране ЭЛТ телевизионного индикатора любого цикла или его части, а также последовательности циклов;

регистрация и визуальное наблюдение в заданный момент времени угла поворота или угла закручивания вала.

Преимущества устройства для измерения угла закручивания вращающегося вала по сравнению с прототипом заключаются в том, что оно позволяет получать не одно дискретное значение угла закрутки за цикл, а по дискретным значениям развертку изменения угла закручивания за один или несколько циклов поршневой машины, а также повысить надежность работы устройства за счет применения блока АВДИ. Кроме того, устройство позволяет измерять не отклонениеугла закручивания от заранее заданного значения, а знакопеременные значения относительно абсолютного нуля угла закручивания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения угла закручивания вращающегося вала | 1985 |

|

SU1348670A1 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| Электронный музыкальный звонок | 1988 |

|

SU1748176A1 |

| Измеритель длительности импульсов сложной формы | 1984 |

|

SU1174898A1 |

| Устройство электронного синтеза мелодии для часов | 1987 |

|

SU1499309A1 |

| Счетно-импульсный преобразователь разности последовательных кодов в параллельный | 1975 |

|

SU612241A1 |

| Устройство для динамической балансировки лучом лазера роторов | 1983 |

|

SU1130753A2 |

| Устройство для управления разгоном и торможением исполнительного двигателя станка | 1981 |

|

SU1062646A1 |

| Устройство для программного управления инвертором напряжения в электроприводе переменного тока | 1990 |

|

SU1737678A1 |

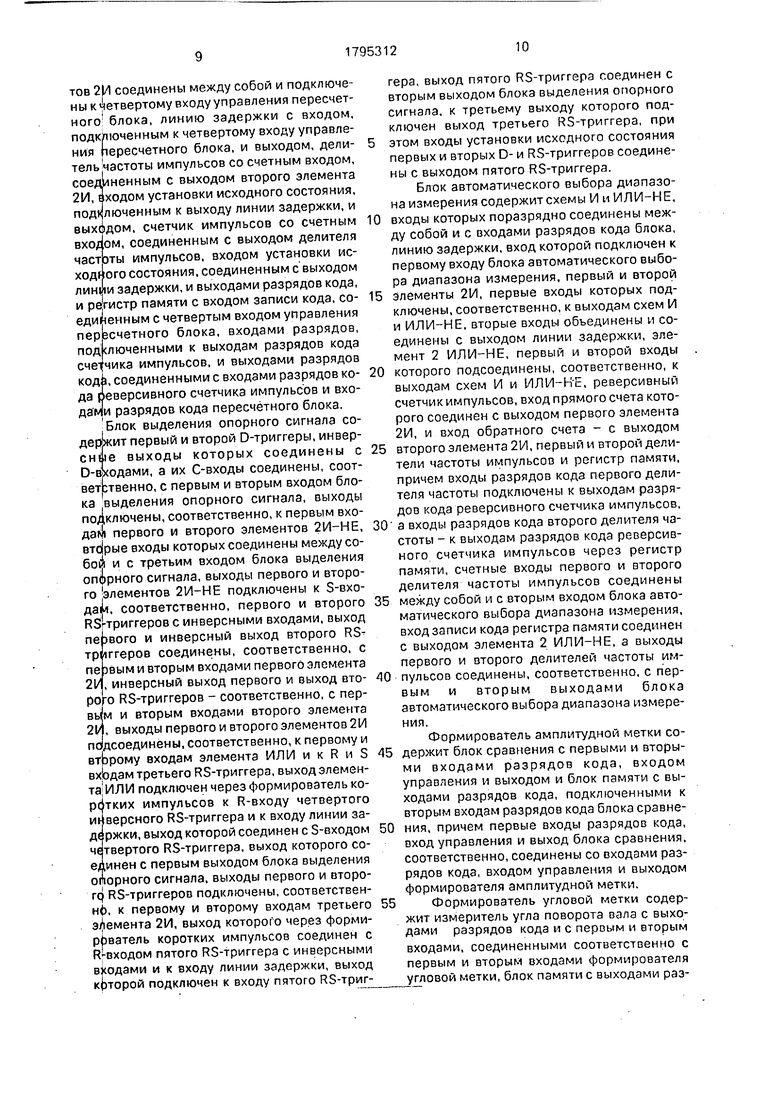

Сущность изобретения: устройство со- дер4ит 1 вал (1), 2 измерительных диска (2. 3), 2 датчика считывания (4, 5), 2 усилителя - ограничителя (6, 7), 2 схемы совпадения (8, 10), 1 суммирующий сердечник (9), 1 блок 2 . управления (11), 1 пересчетный блок (12). 1 счетчик результата (13), 1 цифровой отсчет- ный блок (14), 1 генератор (15), 1 блок выделения опорного сигнала (16), 1 блок автоматического выбора диапазона измерений (17), 1 вычитающий счетчик (18), 1 циф- роаналоговый преобразователь (10), 1 временной селектор (20), 1 формирователь угловой метки (21), 1 формирователь амплитудной метки (22), 1 датчик верхней мертвой точки (23), 1 датчик нижней мертвой точки . (24), 1 делитель на два (25), 1 телевизионный индикатор (26)J регистратор (27). 2-4-6-16- 8-9-18-11-19-21-27, 3-5-7-16, 12-13-20- 26, 12-17-12, 15-17-10, 24-25-21, 2-1-3, 16-22-26; 10-12, 10-18, 11-10, 11-12, 11- 13,11-14, 13-14, 13-19, 16-9, 16-10, 16-12, 16-14, 16-17, 16-18, 16-19, 16-20, 16-21, 16-26, 17-8, 17-16,21-26,23-26,24-27,24- 26, 25-22, 25-26. 6 з.п. ф-лы, 13 ил., 1 табл. ел

Формул а-изобретения 1. Устройство для измерения угла закручивания вращающегося вала, содержащее две ветви, каждая из которых образована закрепленным на валу измерительным диском, установленным с возможностью взаимодействия с ним датчиком считывания и подключенным к последнему усилителем- ограничителем, первую схему совпадения с тремя входами и выходом, суммирующий счетчик со счетным входом, подключенным к выходу первой схемы совпадения, входом обнуления и выходами разрядов кода, вторую схему совпадения с тремя входами и выходом, блок управления с двумя входами и тремя выходами, первым из которых соединенный с первым входом второй схемы совпадения, пересчетный блок с выходом и четырьмя входами, первым из которых соединенный с выходом второй схемы совпадения, а вторым - с вторым выходом блока управления, счетчик результата со счетным входом, подключенным к выходу пересчетного блока, входом обнуления, связанным с вторым выходом блока управления, и выходами разрядов кода, цифровой отсчетный блок с входами разрядов кода, связанными с выходами разрядов кода счетчика результата, и входом управления, подключенным к третьему выходу блока управления, и генератор с выходом, отличающееся тем, что, с целью увеличения эффективности за счет обеспечения возможности получения развертки угла закручивания за период вращения вала и повышения надежности, в него введены блок выделения опорного

сигнала с тремя входами, первый и второй из которых подключен к соответствующему усилителю-ограничителю, и тремя выходами, первый из которых соединен с вторыми входами первой и второй схем совпадения и входом обнуления суммирующего счетчика, а второй - с первым входом первой схемы совпадения, блок автоматического выбора диапазона измерения с входами разрядов кода, двумя входами управления, первый из которых подключен к первому выходу блока выделения опорного сигнала, а второй - к выходу генератора, и двумя выходами, первый из которых соединен с третьими входами блока выделения опорного сигнала, первой схемы совпадения и пересчетного блока, а второй - с третьим входом второй схемы совпадения, вычитающий счетчик импульсов с входами предвари- тельной установки, подключенными к выходам разрядов кода суммирующего счетчика, входом записи кода, подключенным к первому выходу блока выделения опорного сигнала, счетным входом, соединенным с выходом второй схемы совпадения, и выходом, к которому подключен первый вход блока управления, цифроана- логовый преобразователь с входами разрядов кода, подключенными к выходам разрядов кода счетчика результатов, двумя входами управления, первый из которых соединен с третьим выходом блока выделения опорного сигнала, а второй - с третьим выходом блока управления, и выходом, временной селектор с тремя входами, первый из которых подключен к первому выходу

выделения опорного сигнала, а третий1- к выходу цифроаналогового преобразователя, и выходом, формирователь угловой метки с двумя входами, первый из которых соединен с первым выходом блока :ления опорного сигнала, и выходом,

выл фор

иировзтель амплитудной метки с входами разрядов кода, связанными с выходами разрядов кода счетчика результата, входом управления, связанным с третьим выходом блок|а выделения опорного сигнала, и выхо- дом,|датчики верхней и нижней мертвых точек, каждый из которых имеет выход, делитель на два с входом, подключенным к датчика нижней мертвой точки, и выходом, подключенным к вторым входам временного селектора и формирователя уг- ловоН метки, телевизионный индикатор с семью входами, первый из которых соединен о первым выходом блока выделения опорного сигнала, второй - с выходом датчика эерхней мертвой точки, третий - с выходов датчика нижней мертвой точки, четвертый - с выходом формирователя амплитудной метки, пятый - с выходом делителя на1два, шестой - с выходом временного селектора, седьмой - с выходом формирователя угловой метки, и регистратор с двумя

входа

ии, первый из которых подключен к

выходу датчика нижней мертвой точки, а в.торой - к выходу временного селектора, при пересчетный блок снабжен выходами Разрядов кода, подключенными к входам разрядов кода блока автоматического выборе диапазона измерений, четвертый вход пёресчетного блока соединен с первым выходам блока выделения опорного сигнала, а цифровой отсчетный блок снабжен вторым вводом управления, соединенным с третьи выходом блока выделения опорного сигфла.

вторым выходом блока выделения опорного сигнала, к третьему выходу которого подключен выход третьего RS-триггера, при этом входы установки исходного состояния первых и вторых D- и RS-триггеров соединены с выходом пятого RS-триггера.

Диапазон измер.фаз.сдвига, град

Точность измерения, град Погрешность движения во всем диапазоне входных частот, не более Fox 0,01 -.50 Гц РВх 50-100Гц

венно с первым и вторым выходами блока автоматического выбора диапазона измерения.

НФ - 3

0,001 -100 0... ±360

±0,5 ±1,0

KbtVbfVb Ov

л

g 3 n i-g

5 S

ъ § -

§Ј

3gs%

та 77 ft

о

г

4Г-

С

5

9Фиг. 6

бк вЫх

Фиг.1

Bwy Фаг/8

, 9

Блок Я&ДП

П

г

ОитяЛЈНП Ш 7ННОПЈП р1/« Ј

#/ г/7сЬ

ГХ9 С «..

Х1Ч0 21CS62.1

P«i. /3

| Устройство для измерения улга закручивания вала | 1976 |

|

SU574639A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР № ,кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Фролов Л.Б | |||

| Измерение крутящего мо- менТа, М., Энергия, 1967, с | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

Авторы

Даты

1993-02-15—Публикация

1991-02-20—Подача