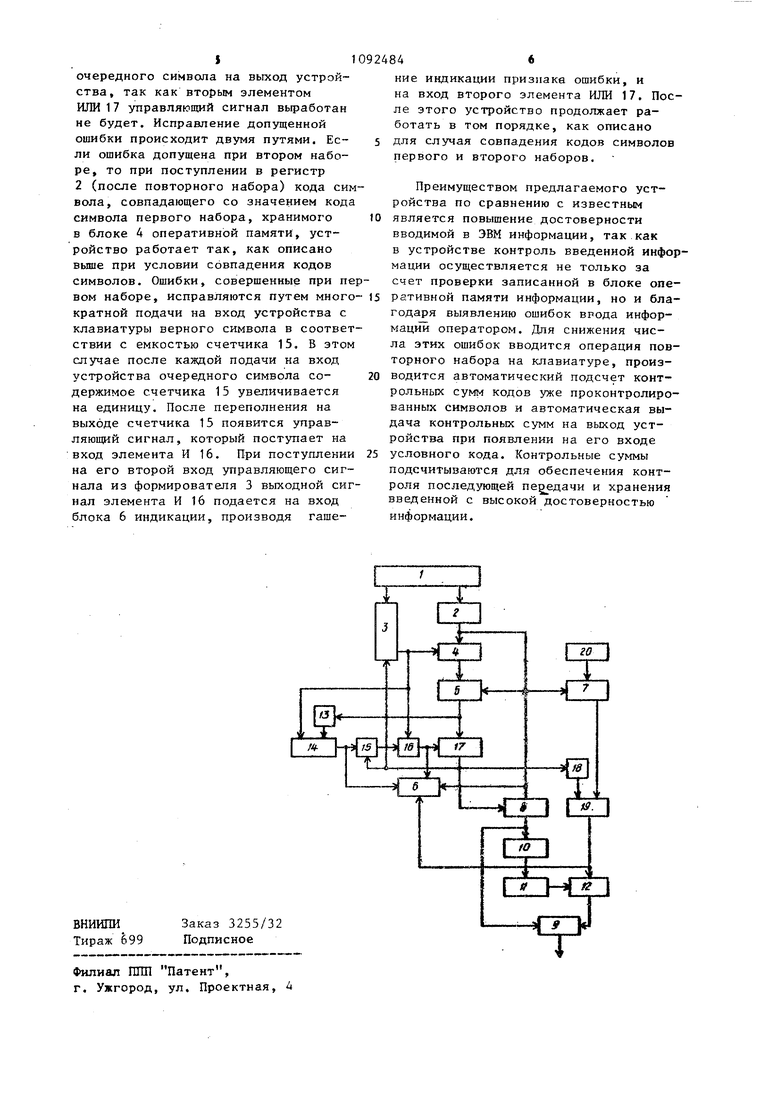

Изобретение относится к вычислительной технике и предназначено для использования в устройствах ввода информации преимущественно с клавиатуры при создании машинных носителей или ввода в ЭВМ. Известно устройство для ввода ин формации, содержащее запоминающее устройство с клавиатурой ввода ин формации, блок индикации для отобра жения хранимой информации и результатов вычислений, регистр блока индикации, блок подавления нулей при .индикации, схему ньделения старшего разряда числа, находящегося-в регис ре блока индикации, блок переключения из режима Подавление нулей в режим Контроль информации, схем сравнения выходной информации регис ра блока индикации с информацией, введенной с клавиатуры запоминающег устройства. Последний в зависимости от результатов сравнения, осуществл емого схемой, посылает в качестве управляющего сигнала подавления инд кации в блок подавления нулей выходной сигнал схемы вьщеления старшего разряда C1 о Недостатком данного устрор5ства является пониженная наделсность изза отсутствия контроля работы оператора. Наиболее близким к предлагаемому по технической сущности является устройство для ввода информации, содержащее клавиатуру, формирователь, первый и второй регистры, бло оперативной памяти, первый блок сра нения, блок индикaц п- и сумматор, кл виатура соединена с первым входом формирователя и с выходом .первого регистра, выход которого подключен к информацион ому входу блока оперативной памяти, управляющий вход -к выходу формирователя, а выход к первому входу первого блока сравнения, выход второго регистра соединен с входом сумматора 2. Недостатком известного устройства также является пониженная надежность из-за отсутствия контроопя работы оператора. Цель изобретения - повышение надежности устройства за счет обеспечения контроля ввоТи-мой информации. Указанная цель достигается тем, что в устройство для ввода информации, содержащее клавиатуру, формиро ватель, первый и второй регистры, 842 блок оперативной памяти, первый блок сравнения, блок индикации и сумматор, клавиатура соединена с первым входом формирователя и с входом первого регистра, выход которого подключен к информационному входу блока оперативной памяти, управляющий входк выходу фJЭpмиpoвaтeля5 а выход- к первому входу первого блока сравнения, выход второго регистра соединен с входом су 1матора, введены элемент задержки, инвертор, счетчик, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй коммутаторь, второй блок сравнения и третий регистр, выход формирователя подключен к первым входам первого и второго элементов И, выход первого регистра соединен с вторым входом первого блока сравнения, с первыми входами второго блока сравнения и блока индикации, с информационным входом первого комг-утатора, выход первого блока сравнения подключен к первому входу первого элемента ИЛИ и через инвертор к второму входу первого элемента И, выход которого подключен к второму входу блока индикации, и к счетпому входу счетчика, выход которого соединен с вторым входом второго элемента И, выход, которого подключен к третьему входу блока индикации и к второму входу первого элемента ИЛИ, выход которого соединен с вторым входом формирователя, с управлярощим вход.ом счетчика, с - отравляющим входом первого коммутатора и через элемент задержки - с первьм входом третьего элемента И, второй вход которого подключен к выходу второго блока сравнения 3 второй вход которого соединен с вьжодом третьего регистра, выход третьего элемента И подключен к четвертому входу блока индикации м к управляюш,ему входу второго коим}/татора, информационный вход которого соединен с выходом сумматора, а выход - с -первым входом второго элемента ИоЧИ,, выход первого коммутатора соединен с входом второго регистра и с вторьм входом второго элемента И1И, выход которого является выходом устройства, На чертеже изображена схема предлагаемого устройства. Устройство содержит клавиатуру 1 ., первый регистр 2, формирователь 3, блок 4 оперативной памяти, первый 3 блок 5 сравнения, блок 6 индикации, второй блок 7 сравнения, первый ком мутатор 8, второй элемент ИЛИ 9, второй регистр 10, сумматор 11, вто рой коммутатор 12, инвертор 13, пер вый элемент И 14, счетчик 15, второ элемент И 16, первый элемент ИЛИ 17 элемент 18 задержки, третий элемент И 19, третий регистр 20. Блок 4 оперативной памяти для упрощения техпроцесса подготовки машинных носителей имеет емкость, позволяющую хранить всю строку, и служит для запоминания информации строки символов. Буферный регистр предназначен для оперативного запоминания кода символа вводимой инфор мации. Формирователь 3 задает режим записи или чтения блоку 4 оперативной памяти. Блок 6 индикации служит для отобра жения поступающей на его вход информации и сигнализации об обнаруженно ошибке. Устройство работает следующим образом. Каждую строку информации набирают на клавиатуре дважды. При первом наборе код очередного символа, поступивший с клавиатуры 1 по кодовым шинам, записывается в регистр 2. С поступлением очередного синхроимпул са с второго выхода клавиатуры 1 фо мирователем 3 разрешается запись информации в блок 4 оперативной памяти и изменяется адрес его очередного свободного поля памяти. Аналогичньм образом последовательно набираются символы одной строки. При втором наборе той же строки код очередного символа, поступивший с клавиатуры 1 по кодовым шинам, записывается в регистр 2. При поступлении синхроимпульса с клавиатуры 1 формирователем 3 изменяется адрес очередного поля блока 4 оперативной памяти и производится перевод его в режим чтения, разрешая сравнение в блоке 5 кода символа первого набора (записанного в блоке 4 оперативной памяти) и соответству щего ему кода символа второго набора (записанного в регистре 2) . При совпадении кодов, поступивших на об входа блока 5 сравнения, на его выходе вырабатывается сигнал, повторяемый элементом ИЛИ 17, который вы полняет следуюшие функции:разрешает 44 прохождение сигнала по кодовым шинам через первый коммутатор 8; устанавливает счетчик 15 в исходное, например нулевое, положение; разрешает формирователю 3 увеличение адреса поля памяти блока 4 оперативной памяти. При поступлении на управляющий вход первого коммутатора 8 с выхода элемента ИЛИ 17 сигнала, разрешающего передачу информации, код, записанный в регистр 2, через коммутатор 8 и элемент ИЛИ 9 подают на выход устройства, а через последовательно соединенные регистр .10 и су 5матор 11 - на вход второго коммутатора 12. С регистра 2 информацию подают и на второй блок 7 сравнения, который вырабатывает управляющий сигнал при поступлении на вход устройства кода, означающего конец записи. Этот код постоянно хранится в регистре 20 памяти, подключенном к другому входу блока 7 сравнения. Вьфаботанный в этом случае сигнал схемы 7 сравнения подают на вход третьего элемента И 19, на второй вход которого подают сигнал элемента ИЛИ 17 через элемент 18 задержки. При поступлении на третий элемент И 19 двух сигналов одновременно на его выходе вырабатывается управляющий сигнал, разрешающий второму коммутатору 12 вьщачу через первый элемент ИЛИ 9 на выход устройства содержимого сзмматора 11. При поступлении последующих строк информации цикл работы устройства повторяется. Если на входы блока 5 сравнения с блока 4 оперативной памяти и регистра 2 различные коды, то на вход первого элемента И 14 через инвертор подают сигнал. С приходом на второй вход элемента И 14 управляЕощего сигнала, переводящего блок 4 оперативной памяти в режим чтения, вырабатывается сигнал, увеличивающий содержимое счетчика 15 на единице и поступающий в блок 6 индикации. Этот сигнал разрешает индикацию признака ошибки.,Таким образом, несовпадение значений первого и второго набора при посимвольном их сравнепии служит признаком ошибки, блокирующим изменение адреса блока 4 оперативной памяти формирователем 3 и поступление кода

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1984 |

|

SU1149238A1 |

| Устройство для ввода информации | 1984 |

|

SU1259240A1 |

| Устройство для ввода информации | 1989 |

|

SU1682996A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1981 |

|

SU1043731A1 |

| Устройство для отображения графической информации на телевизионном индикаторе | 1983 |

|

SU1161985A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1987 |

|

SU1495845A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1980 |

|

SU959143A1 |

| Устройство для отображения информации на телевизионном индикаторе | 1983 |

|

SU1091216A1 |

| Устройство для контроля знаний обучаемых | 1987 |

|

SU1524082A1 |

| Устройство для контроля знаний обучаемых | 1983 |

|

SU1176362A1 |

УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ, содержащее клавиатуру, формирователь, первый и второй регистры, блок оперативной памяти, первый блок сравнения, блок индикации и сумматор, клавиатура соединена с первым входом формирователя и с входом первого регистра, выход которого подключен к информационному входу бпока оперативной памяти, управляющий вход - к выходу формирователя, а выход - к первому входу первого блока сравнения, выход второго регистра соединен с входом сумматора, отличающеесятем, что, с целью псьышения надежности устройства за счет обеспечения контроля ВВОДИМОЙ информации, в него введены элемент задержки, инвертор, счетчик, первый, второй и третий элементы И, первый и второй элементы ИЛИ, первый и второй коммутаторы, второй блок сравнения и третий регистр, выход формирователя подключен к первым входа;м первого и второго элементов И, выход первого регистра соединен с вторым входом первого блока сравнения, с первыми входами второго блока сравнения и блока индикации, с информационным входом первого коммутатора, выход первого блока сравнения подключен к первому входу первого элемента ИЛИ и через инвертор - к второму входу первого элемента И, выход которого подключен к второму входу блока индикации, и к счетному входу счетчика, выход которого соединен с вторым входом второго элемента И, выход которого i подключен к третьему входу блока индикации и к второму входу первого СЛ элемента ИЛИ, выход которого соединен с вторым входом формирователя, с управляющим входом счетчика, с управляющим входом первого коммутатора и через элемент задержки с первым входом третьего элемента И, второй вход которого подключен к со выходу второго блока сравнения, второй вход которого соединен с выходом lN3 третьего регистра, выход третьего 4 00 4 элемента И подключен к четвертому входу блока индикации и к управляющему входу второго коммутатора, информационный вход которого соединен с выходом сумматора, а выход - с первым входом второго элемента ИЛИ, выход первого коммутатора соединен с входом второго регистра и с вторым входом второго элемента ИЛИ, выход которого является выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Бесколесный шариковый ход для железнодорожных вагонов | 1917 |

|

SU97A1 |

Авторы

Даты

1984-05-15—Публикация

1983-01-06—Подача