1095

теля строб-импульсов этого же канала и D -входом триггера последующего канала, инверсный выход триггера Р-го канала соединен с входом Пуск блока фиксированной задержки, а вход синхронизации - с первым входом Сброс блока фиксированной задержки, второй вход Сброс которого соединен с шиной Сброс и вторыми R -входами триггеров всех каналов, первыми Р-входами соединенных с вторым выходом блока фиксированной задержки, причем D -вход триггера первого канала соединен с выходом блока элементов ИСКЛЮЧАЮЩЕЕ РШИ-НЕ, вторыми и третьими информационными входами соединенного с первой g второй информационными шинами задания номеров точек, а первыми информационными входами - с выходами счетчика точек первого канала, инверсный выход формирователя строб-импульсов каждого канала соединен со счетным входом счетчика точек

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель однократных коротких интервалов времени | 1980 |

|

SU917174A1 |

| Устройство для анализа и регистрации формы однократных электрических импульсов | 1981 |

|

SU954899A1 |

| Измеритель коротких интервалов времени | 1980 |

|

SU920629A1 |

| Измеритель однократных коротких интервалов времени | 1980 |

|

SU918930A1 |

| Измеритель коротких интервалов времени | 1980 |

|

SU930222A2 |

| Устройство для анализа формы однократных электрических импульсов | 1982 |

|

SU1051463A1 |

| Устройство для допускового контроля частоты | 1990 |

|

SU1781633A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| Самонастраивающийся генератор опережающих импульсов | 1989 |

|

SU1700533A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

УСТРОЙСТВО ДЛЯ АНАЛИЗА ФОРМЫ ОДНОКРАТНЫХ ЭЛЕКТРИЧЕСКИХ ИМПУЛЬСОВ, содержащее триггер Старт, 5-вход которого соединен с шиной Старт, R-вход - с шиной Сброс, единичный выход - с первым входом элемента И-НЕ, а нулевой выход с первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом второго .элемента И-НЕ, а второй вход - с выходом счетчика интервалов времени и третьим входом первого элемента И-НЕ, второй вход которого соединенс вторым входом второго элемента И-НЕ и выходом кварцевого генератора, а выход-со счетным входом счетчика интервалов времени, информационный вход которого соединен с информационной шиной задания интервала времени, а вход ,обнуления-с шиной Сброс.,и Р каналов , в каждом из которых сигнальный вход блока амплитудных дискриминаторов соединен с шиной анализируемого сигнала, вход стробирования - с прямым выходом формирователя строб-импульсов, а выходы - с входами шифратора, выходы которого соединены с информационными входами блока Г s:-... ...элементов памяти, разрешающими входами соединенного с выходами дешифратора, входы которого с.оединены с выходами счетчика точек, запрещающий выход - с входом остановки счетчика точек, счетный вход которого соединен с входом управления блока элементов памяти,причем вход формирователя строб-импульсов соединен с Р-ым выходом формирователя последовательностей импульсов, первый вход обнуления которого соединен с входами обнуления счетчиков точек по шине Сброс, отличающееся тем, что, с целью § расширения функциональных возмож(Л ностей, оно снабжено управляемым делителем частоты следования импульсов и блоком фиксированной задержки, первый канал снабжен блоком, элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, а каждый канал - триггером, причем вход Пуск управляемого делителя частоты соединен с выходом второго со ел элемента И-НЕ и первым входом блока фиксированной задержки, информационные входы - с информационными шинами задания частоты, управляющий со вход - с третьим выходом блока фиксированной задержки, первый вход обнуления - с первым выходом блока фиксированной задержки и вторым входом обнуления формирователя последовательностей импульсов, второй вход - с шиной Сброс, а выход - с входом Пуск формирователя последовательностей импульсов, выходы которого соединены с входами синхронизации триггеров каналов,, прямой выход триггера каждого канала соединен с управляющим входом формирова

Изобретение относится к электроизмерительной технике и может быть использовано при разработке анализаторов однократных импульсов сложной формы. Известно устройство для анализа фор1«и однократных электрических импульсов, содержащее триггер Старт, п амплитудных стробируемьт дискриминаторов, кварцевый генерато два элемента И-НЕ, элемент И, счетчик задержки времени, счетчик точек анализа, дешифратор, регистры и шиф ратор Cl 3. Однако устройство отличается недостаточно высокой точностью регист рации сложных импульсов, ограниченн временем задержки элементов устройства, недостаточно широкими функцио нальными возможностями, невозможностью изменения частоты опроса дискриминаторов, что приводит к необходимости увеличения числа регистраторов., Наиболее близким к изобретению по технической сущности является устройство для анализа однократных электрических импульсов,содержащее триггер Старт, 5-вход которого соединен с шиной Старт, R-вход - с шиной Сброс, единичный выход - с первым входом эл мента И-НЕ, а нулевой выход - с .первым входом элемента ИЛИ-НЕ, выход которого соединен с первым входом второго элемента И-НЕ, а второй вход - с выходом счетчика интервалов времени и третьим входом первого элемента И-НЕ, второй вход которого соединен с вторым входом второго элемента И-НЕ и выходом кварцевого генератора, а выход - со счетным входом счетчика интервалов времени, информационный вход которого соединен с информационной шиной задания интервала времени, а вход обнуления - с шиной Сброс и Р каналов, в каждом из которых сигнальный вход блока амплитудных дискриминаторов соединен с шиной анализируемого сигнала, вход стробирования - с прямым выходом формирователя строб-импульсов, а выходы - с входами шифратора, выходы которого соединены с информационными входами блока элементов памяти, разрешающими входами соединенного с выходами дешифратора, входы которого соединены с выходами счетчика точек, а запрещающий выход - с входом остановки счетчика точек, счетный вход которого соединен с входом управления блока элементов памяти и выходом формирователя импульсов записи, первый вход которого соединен l выходом второго элемента И-НЕ, входом Пуск формирователя последовательностей импульсов и с первым входом формирователя стробирующих импульсов, а второй вход - с Р-ым выходом формирователя последовательностей импульсов и вторым входом формирователя строб-импульсов, причем первый вход обнуления формирователя последовательностей импульсов соединен с входами обнуления счетчиков точек и шиной Сброс 1.2. Недостатком этого устройства явл ется ограниченность функциональных возможностей: не обеспечивает возможность изменения частоты опроса амплитудных дискриминаторов непосредственно в процессе анализа,чт приводит к необходимости увеличения числа элементов памяти или ограничению максимальной длительности исследуемого сигнала. Цель изобретения - расширение функциональных возможностей. . Цель достигается тем, что устрой ство для анализа формы однократных электрических импульсов, содержащее триггер Старт, S -вход которого соединен с шиной Старт, R-входпс шиной Сброс, единичный выход - с первым входом элемента И-НЕ, а нулевой выход - с первы входом элемента ИЛИ-НЕ, выход которого соединен с первым входом второ го элемента И-НЕ, а второй вход с выходом счетчика интервалов време ни и третьим входом первого элемента И-НЕ, второй вход которого соеди нен с вторым входом второго элемента И-НЕ и выходом кварцевого генератора, а выход - со счетным входом счетчика интервалов времени, информационный вход которого соединен с информационной шиной задания интервала времени, а вхЪд обнуления с шиной Сброс, и Р каналов, в каждом из которых сигнальный вход блока амплитудных дискримитаторов соединен с шиной анализируемого сиг нала, вход стробирования - с прямым выходом формирователя строб-импульсов, а выходы - с входами шифратора выходы которого соединены с информационными входами блока элементов памяти, разрешающими входами соединенного с выходами дешифратора,входы которого соединены с выходами счетчика точек, а запрещающий выход - с входом остановки счетчика точек, счетный вход которого соеди нен с входом управления блока элементов памяти, причем вход формиро вателя cтpoб-и myльcoв соединен с Р-ым выходом формирователя после довательностей импульсов, первый вход обнуления которого соединен с входами обнуления счетчиков то34чек и шине Сброс, снабжено управляемым делителем частоты следования импульсов и блоком фиксированной задержки, первый канал снабжен блоком элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, а каждьй канал - триггером, причем вход Пуск управляемого делителя частоты соединен с выходом второго элемента И-НЕ и первым входом блока фиксированной задержки, информационные входы - с информационными шинами Зс1Дания частоты, управляющий вход - с третьим выходом блока фиксированной задержки, первый вход обнуления - с первым выходом блока фиксированной задержки и вторым входом обнуления формирователя последовательностей импульсов, второй вход обнуления - с шиной Сброс, а выход с входом Пуск формиррвателя последовательностей импульсов, выходы которого соединены с входами синхронизации триггеров каналов, прямойвыход триггера каждого канала соединен с управляющим входом формирователя строб-импульсов этого же канала и D -входомтриггера последующего канала, инверсный выход триггера Р-го канала соединен с входом Пуск блока фиксированной задержки, а вход синхронизации - с первым входом Сброс блока фиксированной задержки, второй вход Сброс которого соединен с шиной Сброс и вторыми R -входами триггера всех каналов, первыми R-BXOдами соединенных с вторым выходом блока фиксированной задержки,причем D -вход триггера первого канала соединен с выходом блока «элементов ИСКПЮЧАЮЩЕЕ Ш1И-НЕ, вторыми и третьими информационными входами соединенного с первой и второй информационными шинами задания номеров точек, а первыми информационными входами - с выходами счетчика точек первого канала, инверсный выход формирователя строб-импульсов каждого канала соединен со счетным входом счетчика точек. На фиг.1 представлена структурная электрическая схема устройстваJ на фиг.2 - временная диаграмма импульсов на входе и выходах формирователя последовательностей импульсов} на фиг.З - временная диаграмма импульсов на прямом и инверсном выходах формирователя строб-импульсов; на фиг. 4 - временная диаг рамма импульсов на прямом и инверсном выходах формирователя стробимпульсов в момент переключения час тоты управляемого делителя частоты. Устройство состоит из триггера 1 Старт, кварцевого генератора 2 первого и второго элементов 3,4 И-H счетчика 5 интервалов времени, элемента 6 ИЛИ-НЕ, формирователя 7 последовательностей импульсов и Р каналЪв, каждый из которых включает блок 8 амплитудных дискриминаторов, шифратор 9, блок 10 элементов памяти, дешифратор 11, счет чик 12 точек, формирователь 13 строб-импульсов, триггер 14. Первый канал включает также блок 15 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ. В устройство входят также управляемый делитель 16 частоты следования импульсов, блок 17 фиксированной за держки, шина 18 Сброс, шина 19 Старт, информационная шина 20 задания интервала времени, информационные шины 21, 22 задания часто информационные шины 23, 24 задания номеров точек и входная шина 25. 5-вход триггера Старт 1 соединен с шиной 19 Старт, R -вход - с шиной Сброс, единичный выход - с первым входом элемента 3 И-НЕ, а ну левой выход - с первым входом элемента 6 ИЛИ-НЕ, выход которого соединен с первым входом второго элемента 4 И-НЕ, а второй вход - с выходом счетчика 5 интервалов времени и третьим входом первого элемента 3 И-НЕ, второй вход которого соединен с вторым.входом второго эл мента 4 И-НЕ и выходом кварцевого генератора 2, а выход - со счетным входом счетчика 5 интервалов времени, информационный вход которого соединен с информационной щиной 20 задания интервала време 1и, а вход обнуления-с шиной 18 Сброс. В каждом из Р каналов сигнальный вход блока 8 амплитудных дискримина торов соединен с шиной анализируемо го сигнала, вход стробирования с прямым выходом формирователя 13 строб-импульсов, а вькоды - с входа ми пшфратора 9, выходы которого соединены с информационными входами блока 10 элементов памяти, разрешаю щими входами соединенного с выходами дешифратора 11, а входы которого соединены с выходами счетчика 12 точек, запрещающий выход - с входом остановки счетчика 12 точек, счетный вход которого соединен с входом управления блока 10 элементов памяти, причем вход формирователя 13 стробимпульсов соединен с Р-ным выходом формирователя 7 последовательностей импульсов, первый вход обнуления которого соединен с входами обнуления счетчиков 12 точек и шиной 18 Сброс. Вход Пуск управляемого делителя 16 частоты соединен с выходом второго элемента 4 И-НЕ и первым входом блока 17 фиксированной задержки, информационные входы - с информационными шинами 21, 22 задания частоты, управляющий вход - с третьим выходом блока 17 фиксированной задержки, первый вход обнуления - с первым выходом блока 17 фиксированной задержки и вторым входом обнуления формирователя 7 последовательностей импульсов, второй вход обнуления - с шиной 18 Сброс, а выход - с входом Пуск формирователя 7 последовательностей импульсов, выходы которого соединены с входами синхронизации триггеров 14 каналов, прямой выход триггера 14 каждого канала соединен с управляющим входом формирователя 13 строб-импульсов этого же канала и Г-входом триггера 14 последующего канала, инверсный выход триггера 14 Р-го канала соединен с входом Пуск блока 17 фиксированной задержки, а вход синхронизации - с первым входом Сброс блока 17 фиксированной задержки, второй вход Сброс которого соединен с шиной 18 Сброс и вторыми -входами триггеров 14 всех каналов, первыми R-входами соединенных с вторым выходом блока 17 фиксированной задержки, причем D -вход триггера 14 первого канала соединен с выходом блока 15 элементов ИСКЛЮЧАЮЩЕЕ ШШ-НЕ, вторыми и третьими информационными входами соединенного с первой и второй информационными шинами 23, 24 задания номеров точек, а первыми информационными входами - с выходами счетчика 12 точек первого канала, инверсный выход формирователя 13 строб-импульсов каждого канала соединен со счетным входом счетчика 12 точек. Каждый из дискриминаторов 8j1,.. 8jn блока 8 амплитудных дискриминаторов при наличии на стробирующем входе единичного логического сигнала (режим иьшульсов сравнения) срабатывает при достижении исследуемым -импульсом пороговой величины Цд при этом на выходе сработавшего дис крими1 тора 8JK (где ...п) сигнал принимает едини 1ное логическое значение. При уменьшении исследуемо го импульса ниже пороговой величины и и наличии на стробирующем -входе дискриминатора 8jK единичного логического сигнала дискриминатор 8JK отпускает, при этом на его выходе сигнал принимает нулевое логического значение. При наличии на стробирующем входе дискриминатора BjK нулевого логического сигнала дискриминатор 8jK запоминает предьщущее состояние вне зависимости от величины исследуемого сигнала (режим хранения). Каждый из блоков 8 амплитудных дискриминаторов всех Р каналов строится таким образом, что входящие в него дискриминаторы 8j1...8jn образуют амплитудную сетку с дискретностью ли г,,, т.е. если первый дискриминатор 8j 1 имеет порог срабаты вания (и порог отпускания) Vnt то второй дискриминатор 8j2 имеет порог срабатьтания а третий дискриминатор 8j3 - порог срабатывания Uj 4 и т.д. Таким образом, п-й дискримийатор 8jn имеет порог срабатывания ((n--i)uUn В блоках 10.1,... ЮР элементов памяти запись информации по информационным входам (с выходов шифраторов 9.1,...9.Р) происходит только /ipH наличии на разрешающем входе единичного логического сигнала в момент изменения на управляющем выходе логического сигнала с единичного на нулевой. Таким образом, если на информационном входе первого элемента 10j блока 10j (j-ro канала) присутствуе единичный логический сигнал и одновременно на разрешающем входе также единичный, то в момент изменения си нала на управляющем входе с единичного на нулевой в элемент lOjl (при ) записана 1. Если на информационном входе элемента lOjl присутствует нулевой логический сигнал, а на разрешающем - единичный, то в момент изменения сигнала на управляющем входе с единичного на нулевой элемент lOjl записан О. Если на разрешающем входе элемента lOjl нулевой логический сигнал, то при изменении логического сигнала на управляющем входе с единичного на нулевой информация, записанная в элементе 10J1, не меняется. Если сигнал на управляющем входе управляемого делителя 16 частоты имеет нулевое логическое значение, то частота на его выходе определяётся информацией, задаваемой по шине 21. Если сигнал на управляющем входе управляемого делителя 16 частоты имеет единичное логическое значение, то частота на его выходе определяется информацией, задаваемой по шине 22. По единичному сигналу подаваемому на вход обнуления управляющего делителя 16 частоты, последний устанавливается в нулевое состояние. После установки нулевого логического сигнала на входе обнуления управляемого делителя 16 частоты он начинает работу с нулевого состояния. При. подаче на второй вход Сброс блока 17 фиксированной задержки единичного логического сигнала он устанавливается в нулевое состояние, при котором на его йыходах нулевые логические сигналы. При подаче на вход Пуск блока 17 фиксированной задержки нулевого логического сигнала на первом и третьем его выходах устанавливаются единичные логические сигналы. Через интервал времени t сигнал на втором выходе блока 17 фиксированной задержки также принимает единичное логическое значение.При подаче на вход Пуск блока 17 фиксированной задержки единичного логического сигнала на его первом выходе сигнал принимает нулевое логическое значение. При подаче на первый вход Сброс блока 17 фиксированной задержки первого импульса состояние на его выходах не меняется, а при подаче второго импульса блок 17 фиксированной задержки переходит в состояние, при котором на его втором выходе устанавливается нулевой логический сигнал. При подаче второго импульса по входу Пуск блока 17 фиксированной

задержки на его третьем выходе устанавливается нулевой логический сигнал, в остальном работа блока 17 фиксированной задержки не отличается от указанной.

Устройство работает следующим образом.

Непосредственно перед измерением по шиле 18 Сброс подаетсяединичный логический импульс, который устанавливает триггер 1 Старт, счетчик 5 интервалов времени, формирователь 7 последовательностей импульсов, счетчики 12 точек, триггер 14, делитель 16 частоты и блок 17 фиксированной задержки в нулевое состояние. При этом на выходе счетчика 5 интервалов времени устанавливается единичный логический сигнал, на выходах формирователя 7 последовательностей импульсов также единичные логические сигналы, а счетчики 12 точек находятся в состоянии, при котором только на первых выходах дешифраторов 11 присутствуют разрешающие сигналы, т.е. разрешающий сигнал присутствует только при разрешающем входе элемента памяти 10j1 (j-ro канала). Затем или одновременно по информационной шине 20 вводится информация об интервале времени, по истечении которого устройство начнет анализ исследуемого сигнала. Эта информация вводится как в прямом коде (счетчик 5 работает в режиме вычитания), так и в обратном (счетчик 5 работает в режиме суммирования) . Одновременно по информационной шине 21 вводится информация о частоте f на первом и третьем этапах работы анализатора, а

по шине 22 о частоте f..,

f). По шине 24 вводится импульсов

информация о номере точки 1, на которой заканчивается второй этап работы анализатора, т.е. переключение частоты опроса с f на .Единичные логические сигналы с прямых выходов формирователей строб-импульсов 13.1, поступая на стробирующие входы амплитудных дискриминаторов 8.1, устаплвливают последние в режим

сравнения. Нулевые логические сигналы с инверсных выходов формирователей 13.1 импульсов,- поступая на управляющие входы блоков запоминающих устройств 10.1, запрещают запись информации. Состояние блоков 10 элементов памяти неопределенно, т.е. в них может быть записана любая информация.

По сигналу Старт, поступающему на шину 19, устройство начинает работу. Импульс по шине 19 Старт, имеющей .единичное логическое значение, опрокидывает триггер 1 в единичное состояние. Единичный логический сигнал с единичного выхода триггера 1 открывает элемент 3 И-НЕ, импульсы с кварцевого генератора 2 через элемент 3 И-НЕ поступают на счетный вход счетчика 5 интервалов времени. Начинается отсчет интервалов времени t/j. Одновременно нулевой логический сигнал с нулевого выхода триггера 1, поступая на первый вход элемента 6 ИЛИ-НЕ, подготавливает этот элемент к срабатыванию.

Через интервал времени t сигнал На выходе счетчика 5 интервалов времени меняет свое логическое значение с единичного на нулевое и закрывает элемент 5 И-НЕ, прекращая тем самым поступление импульсов с кварцевого генератора 2 на счетный вход счетчика 5 интервалов времени.

Одновременно нулевой логический сигнал с выхода счетчика 5 интервалов времени поступает, на второй вход элемента 6 ИЛИ-НЕ. В результате на выходе элемента 6 ИЛИ-НЕ устанавливается сигнал,который разрешает прохождение импульсов с выхода кварцевого генератора 2 через элемент 4 ИЛИ-НЕ на вход управляемого делителя 16 частоты, на выходе которого появляются импульсы с частотой f в соответствии с введенной по информационной шине 21 информации.

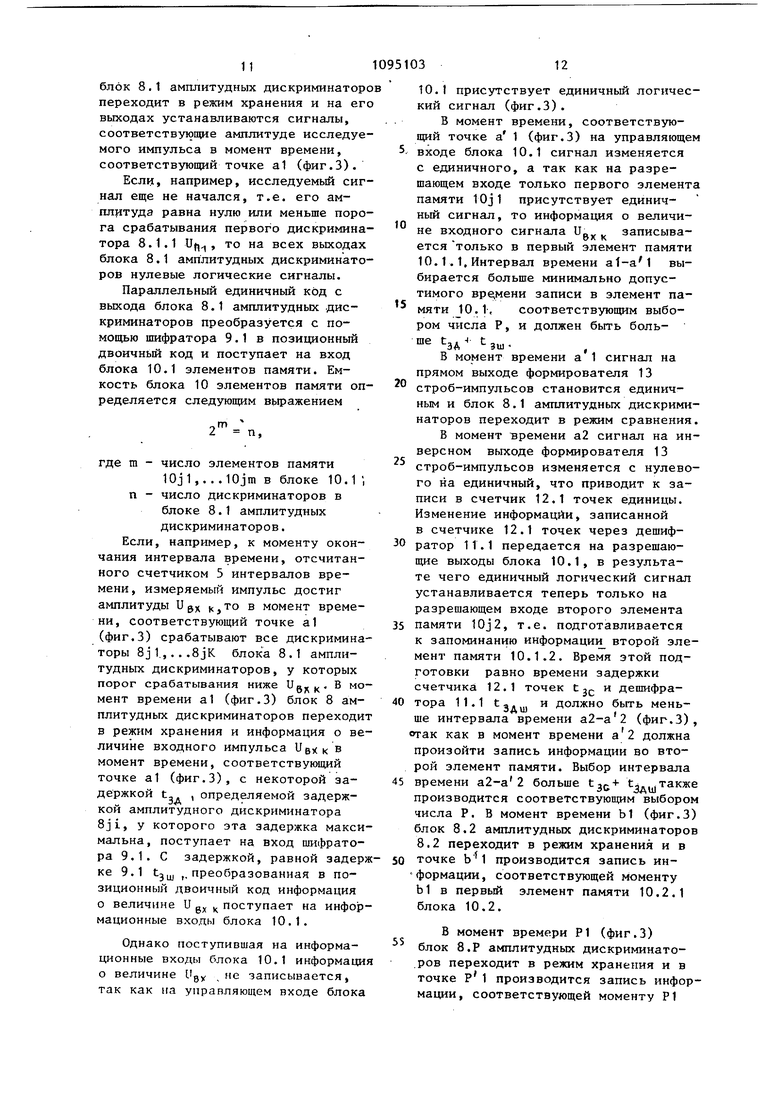

Формирователь 7 последовательностей импульсов включается в работу и вьдает на своих выходах последовательность импульсов f сдвинутых по фазе друг относительно друга на 1/Р эл.град. (фиг.2).

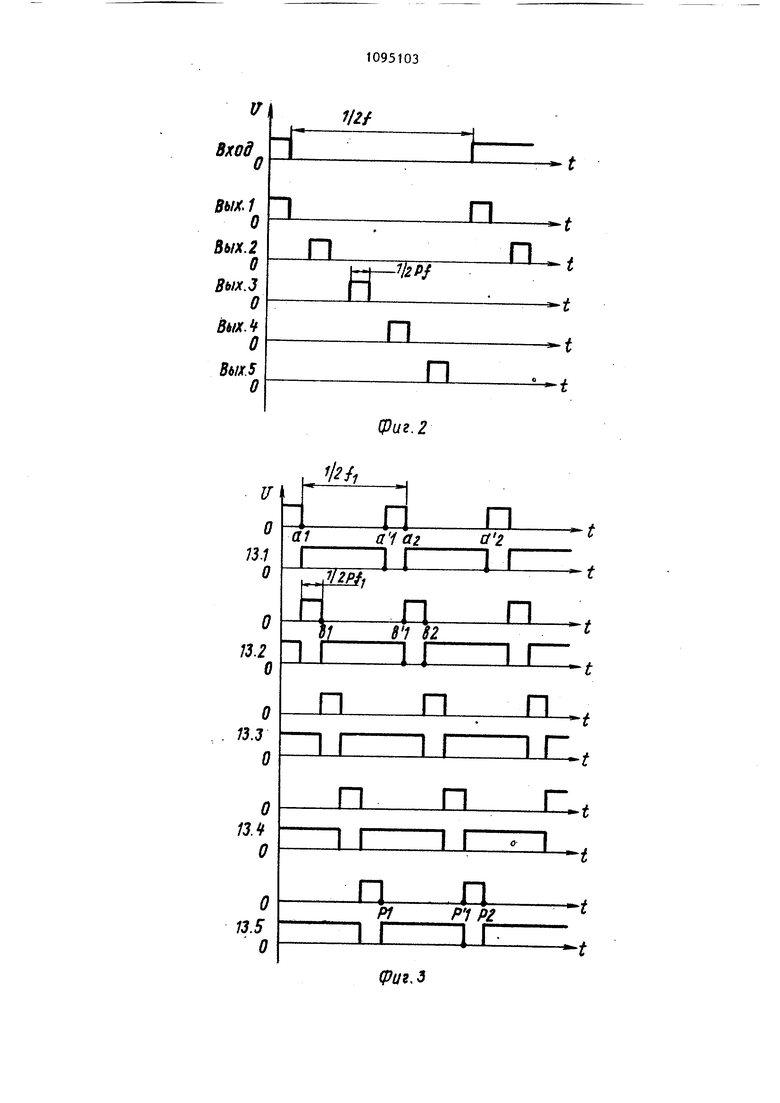

В точке a1 (фиг. 3) сигнал на прямом выходе формирователя 13.1 строб-импульсов меняется с единичного на нулевой. Следовательно,

блок 8.1 амплитудных дискриминаторо переходит в режим хранения и на его выходах устанавливаются сигналы, соответствующие амплитуде исследуемого импульса в момент времени, соответствующий точке a1 (фиг.З).

Если, например, исследуемый сигнал еще не начался, т.е. его амплитуда равна нулю или меньше порога срабатывания первого дискриминатора 8.1.1 Uf, , то на всех выходах блока 8.1 амплитудных дискриминаторов нулевые логические сигналы.

Параллельный единичный код с выхода блока 8.1 амплитудных дискриминаторов преобразуется с помощью шифратора 9.1 в позиционный двоичный код и поступает на вход блока 10.1 элементов памяти. Емкость блока 10 элементов памяти определяется следующим выражением

2

где m - число элементов памяти

10J1,...10jm в блоке 10.1 ; п - число дискриминаторов в блоке 8.1 амплитудных дискриминаторов. Если, например, к моменту окончания интервала времени, отсчитанного счетчиком 5 интервалов времени , измеряемый импульс достиг амплитуды и gx к,1о в момент времени, соответствующий точке a1 (фиг.З) срабатывают все дискриминаторы 8j1.,...8jK блока 8.1 амплитудных дискриминаторов, у которых

порог срабатывания ниже U

В МО-

бл к

мент времени a1 (фиг.З) блок 8 амплитудных дискриминаторов переходит в режим хранения и информация о величине входного импульса в момент времени, соответствующий точке a1 (фиг.З), с некоторой задержкой ta, , определяемой задержкой амплитудного дискриминатора 8ji, у которого эта задержка максимальна, поступает на вход шифратора 9.1. С задержкой, равной задержке 9.1 tj ,, преобразованная в позиционный двоичный код информация о величине U g поступает на информационные входы блока 10.1.

Однако поступившая на информационные входы блока 10.1 информация о величине Ugy , не записывается, так как на управляющем входе блока

В момент времени, соответствующий точке а 1 (фиг.З) на управляющем . входе блока 10.1 сигнал изменяется с единичного, а так как на разрещающем входе только первого элемента памяти 1OJ1 присутствует единичный сигнал, то информация о величине входного сигнала U записывается только в первый элемент памяти 10.1.1, Интервал времени at-al выбирается больше минимально допустимого вре,мени записи в элемент памяти 10.1, соответствующим выбором числа Р, и должен быть боль е ЧА Чшв момент времени а 1 сигнал на прямом выходе формирователя 13 строб-импульсов становится единичным и блок 8.1 амплитудных дискриминаторов переходит в режим сравнения. В момент времени а2 сигнал на инверсном выходе формирователя 13 строб-импульсов изменяется с нулевого на единичный, что приводит к записи в счетчик 12.1 точек единицы. Изменение информации, записанной в счетчике 12.1 точек через дешифратор 11.1 передается на разрешающие выходы блока 10.1, в результате чего единичный логический сигнал устанавливается теперь только на разрешающем входе второго элемента памяти 10J2, т.е. подготавливается к запоминанию информации BTOPOII элемент памяти 10.1.2. Время этой подготовки равно времени задержки счетчика 12.1 точек t и депшфратора 11.1 Ьддщ и должно быть меньше интервала времени а2-а2 (фиг.З), отак как в момент времени а2 должна произойти запись информации во второй элемент памяти. Выбор интервала

времени а2-а2 больше

t3C

t, также

производится соответствующим выбором числа Р. В момент времени Ы (фиг.З) блок 8.2 амплитудных дискриминаторов 8.2 переходит в режим хранения и в точке ЬЧ производится запись информации, соответствующей моменту Ы в первый элемент памяти 10.2.1 блока 10.2.

В момент времери Р1 (фиг.З) блок 8.Р амплитудных дискриминаторов переходит в режим хранения и в точке 1 производится запись информации, соответствующей моменту Р1

в первый элемент памяти 10.1 блока 10.Р. В точке РЗ в счетчик 12.Р добавляется единица.

Далее процесс работы устройства повторяется до тех пор,пока информация в счетчике 12,1 не станет равной N1, заданной по шине 23.

На первом этапе работы устройства порядок вьшода точек информации следующий;а 1, Ы,...Р1,а2,Ь2...Р2,

N1 М

В момент времени, когда информация в счетчике 12.1 станет равной N1, (а N) (фиг.З), информация на выходе счетчика точке 12.1 с задержкой t зс становится равной информации N1 и через время t , равное задержке блока 15 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ, на выходе пос- . леднего устанавливается сигнал 1. Это время должно быть меньше интервала времени a1-a1 (фиг.З) нли, что то же самое, меньше интервала времени (фиг.4), что устанавливается соответствующим выбором числа Р. При переходе следующего на вход формирователя 13.1 строб-импульсов триггер 14.1 первог канала перебрасывается в единичное состояние. При этом единичный логический сигнал с единичного выхода триггера 14.1 удерживается формирователем 13.1 строб-импульсов в состоянии, при котором на его прямом выходе удерживается сигнал 1.

Так как импульс на вход формирователя 13.1 строб-импульсов с выхода формирователя 7 последовательностей импульсов поступает раньше, чем сигнал с единичного выхода триггера

Срабатывание триггера 14.1 подготавливает к срабатыванию триггер

В момент времени bf срабатывает триггер 14.2 и т.д.

В момент времени срабатывает триггер 14.Р. Начиная с этого момента все формирователи 13.1,...13.Р удерживаются в состоянии, при котором на их прямых выходах - единичный логический сигнал.

Нулевой логический сигнал с инверсного выхода триггера 14.Р запускает блок 17 фиксированной задержки по выходу Пуск. На первом и третьем выходах блока 17 фиксированной

задержки устанавливаются единичные логические сигналы, при этом формирователь 7 последовательностей импульсов и управляемый делитель 16 частоты устанавливаются в нулевое состояние и одновременно управляемый делитель 16 частоты изменяет свой коэффициент деления в соответствии с заданной по шине 22 информацией, т.е. подготавливается для цаботы с частотой выходных импульсов fJ. Через фиксированный интервал времени t 3.., , определяемый частотой кварцевого генератора 2 и коэффициентом

деления блока 17 фиксированной задержки, сигйал на втором выходе блока 17 фиксированной задержки принимает единичное логическое значение . В результате все триггеры 14 устанавливаются и нулевое состояние и на прямых: выходах всех формирователей 13 строб-импульсов, кроме первого, сигнал принимает нулевое логическое значение Ь или Р

5 (фиг.4)..

Задержка t,.должна быть дольше времени обнуления управляемого делителя 16 частоты и формирователя 7 последовательностей импульсов.

0 Установка триггера 14.Р в нулевое состояние приводит к измерению сигнала на первом выходе блока 17 фиксированной задержки с единичного на нулевой. С этого момента управляемьй делитель 16 частоты и формирователь 17 последовательностей импульсов опять включаются в работу. В точке Ь или Р (фиг.4) во все счетчики 12 точек, кроме первого,

добавляется единица и все блоки 8 амплитудных дискриминаторов, кроме первого, переводятся в режим хранения.

С выхода управляемого делителя

5 16 частоты поступают импульсы с частотой f „ .

112 () блок 8.1 амВ точке

плитудных дискриминаторов переходит JQ в режим хранения и одновременно во все блоки 10, кроме первого, записьшается информация, соответствующая точке Ь(Р),а в счетчик 12.1 точек прибавляется единица.

55 Далее работа устройства повторяется аналогично, только,частота на выходе управляемого делителя 16 час тоты равна f,. На втором этапе-работы .устройства порядок вьшода точек информации следующий: а| ,Ь . .. ,Р (.,,,Ь И Т.Д 142 °N2 NZ А. --Так как триггеры 14 принудительно удерживаются в нулевом состоянии сигналом со второго выхода блока 17 фиксированной задержки в течение времени, равного двум импульсам с первого выхода формирователя 7 последовательностей импульсов, то в момент прихода первого импульса с первого выхода формирователя 7 последовательностей импульсов триггер 14.1 не перебрасывается, благод ря чему в момент переключения время задержки счетчика 12.1 и блока 15 элементов ИСКПЮЧАВДЕЕ ИЛИ-НЕ не оказывают влияния на работу устройства. С приходом второго импульса формирователя 7 последовательностей импульсов сигнал на втором выходе блока 17 задержки принимает нулевое логическое значение и сигнал принудительного обнуления триггеров 14 снимается. Далее работа устройства аналогич на указанному до тех пор,пока инфор мя vKaaaHHOMV до 1ел j.iui-, мация В счетчиках 12 точек не станет ра 1 3 а информации N2,введенной по шине 24.В этот момент начинается переключение на третий этап работы с частотой на выходе управляемого делителя 16 частоты f (т.е. частоте на первом этапе работы). Это переключение происходит аналогично и затем начинается третий этап работы (полностью аналогичный первому). На третьем этапе работы устройства порядок вывода точек информации аналогичен второму этапу. При переполнении счетчиков 12 точек сигнал с выхода соответствующих дешифраторов 11 останавливает счетчики 12. На этом процесс анализа заканчивается. В блоках 10 элементов памяти хранится информация о величине мгновенного значения входного импульса в точках, сдвинутых одна относительно другой на определенные промежутки времени, часть из которых соответствует частоте выборки f-f, вторая часть - fj и третья - f. Устройство обеспечивает возможность изменения частоты опроса амплитудных дискриминаторов, что позволяет уменьшить число элементов памяти или увеличить максимальную длительность исследуемого сигнала

Вход

iJlA

i-mt- С

1aia

ai

I

,J/2Pf.

n

/3.J

фиг. 2

n

n

n

u:.

игЛ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке К 3253248/18-21, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке К« 3311418/18-21, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| , | |||

Авторы

Даты

1984-05-30—Публикация

1983-03-05—Подача