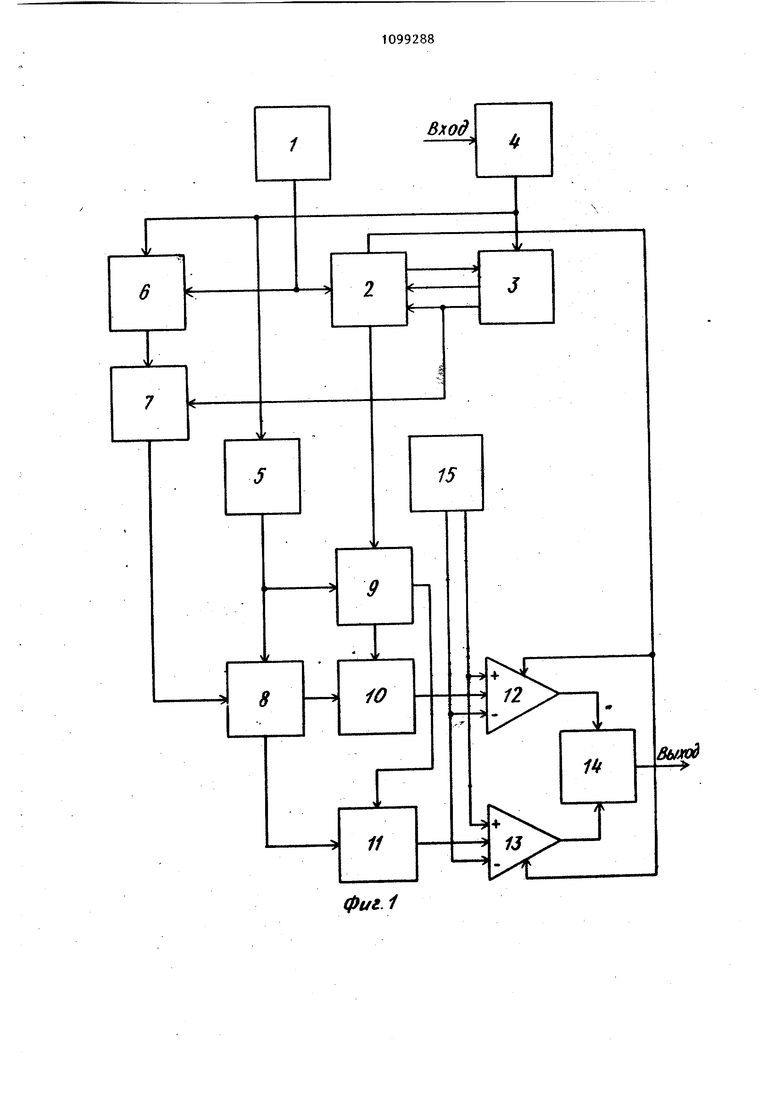

Изобретение относится к электрои радиоизмерительной технике. Известно устройство для контроля частоты, содержащее последовательно соединенные опорный генератор, делитель, элемент равнозначности, управляемый генератор, первый счетчик, триггер, второй счетчик и блок памяти, а тдкже регистр и входной формирователь импульсов, подключенный к регистру, триггеру, первому и вто рому счетчикам и делителю, выходы первого счетчика соединены с блоком памяти и делителем, а второго - с регистром, выход блока памяти подклю чен к входу элемента равнозначноети 1. Однако это устройство не позволяет контролировать мгновенное значение частоты f) при узкой зоне допуска ifff так как точность измерения в нем ограничивается ошибкой квантования из-за некоррелированности измеряемого и опорного колебаний. Наиболее близким по технической сущности к изобретению является устройство, осуществляющее контроль пе-риода колебания и содержащее входной формирователь импульсов, счетчик, блок запуска и сброса, опорный генератор и схему И, выход формирователя импульсов соединен с первыми входами блока запуска и сброса и схемы И, выходы сброса и разрешения счета блока запуска и сброса подклю чены к соответствуклцим входамсчетч ка, выход переполнёнйя которого подключен к вторым входам блока запуска и сброса и схемы И, выход опор ного генератора соединен с сигнальным входом счетчика 2 . Однако известное устройство также не позволяет контролировать период входного колебания при узкой зоне допуска из-за присущей ему ошибки квантования. Целью изобретения является повьпие ние точности контроля периода колеба ния путем устранения ошибки квантования . Поставленная цель достигается тем, что в устройство для контроля периода колебания, содержащее блок запуска и сброса, счетчик, первый формирователь импульсов, подключенный к первому входу блока запуска и сброса, выходы сброса и разрещения счета КОТОРОГО соединены с роответствующими входами счетчика, а второй вход - с выходом переполнения счетчика, а также опорный генератор, подключенный .к сигнальному входу счетчика, введены второй формирователь импульсов, два элемента ИЛИ, два коммутатора, два интегратора, два компаратора, счетный триггер и источник опорных напряжений, входы второго формирователя импульсов соединены с выходами первого формирователя импульсов и опорного- генератора, а его выход соединен с первым, входом первого элемента ИЛИ, к вто- . рому входу которого подключен выход сброса блока запуска и сброса, а к выходу первого элемента ИЛИ подключен сигнальный вход первого коммутатора, вход счетного триггера соединен с выходом первого формирователя импульсов, а его выход - с управляющими входами первого и второго коммутаторов, первьй выход первого коммутатора через включенные последовательно перяьй интегратор и компаратор подключен к первому входу второго элемента ИЛИ, а второй выход первого коммутатора через последовательно соединенные вторые интегратор и компаратор - к второму входу второго элемента ИЛИ, второй выход счетчика соединен с входами стробирования itep-: вого и второго компараторов, а третий выход - с управляющим входом второго коммутатора, выходы которого подключены к входам сброса первого и второго интеграторов, выходы источника опорных напряжений соединены с соответствующими входами компараторов. Указанные отличия позволяют повысить точность контроля путем интегрирования импульсов в начале и в конце контролируемого периода и двустороннего контроля получаемого напряжения с помощью компараторов. На фиг. .1 представлена электрическая структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства. Устройство состоит из опорного генератора 1, счетчика 2, блока 3 запуска и сброса, первого формирователя 4 импульсов, счетного триггера 5, второго формирователя 6 импульсов, первого элемента ИЛИ 7, первого 8 и второго 9 коммутаторов, первого 10 и второго 11 интеграторов.

первого 12 и второго 13 компараторов, второго элемента ИЛИ 14, а также источника 15 опорных напряжений. Выход первого формирователя 4 импульсов соединен с первыми входами блока 3 запуска и сброса и второго формирователя 6 импульсов, а через счетный триггер 5 - с .управляющими рходами коммутаторов 8 и- 9. Выход опорного генератора 1 подключен к сигнальному входу счетчика 2 и второму входу второго формирователя 6 импульсов, а выход последнего - к первому входу первого элемента ИЛИ 7. Выходы разрешения счета и сброса блока 3 запуска и сброса соединены с соответствующими входами счетчика 2, а выход сброса - также и с вторым входом первого элемента ИЛИ 7, выход которого подключен к сигнальному входу первого коммутатора 8, первый выход которого через первые интегратор 10 и компаратор 12 подключег: к первому входу второго элемента ИЛИ 14, а второй выход через вторые интегратор 11 и компаратор 13 - к второму входу второго элемента ИЛИ 14. Второй выхЬд счетчика 2 соединен с входами стробирования компараторов 12 и 13, а.третий выход - с сигнальным входом второго коммутатора 9, выходы которого подключены к входам сброса интеграторов Ю и 11. Выходы источника 15 опорных напряжений соедикены с соответствующими входами компараторов 12 и 13. Вход первого формирователя 4 импульсов является входом устройства, а выход второго элемента ИЛИ 14 - его выходом.

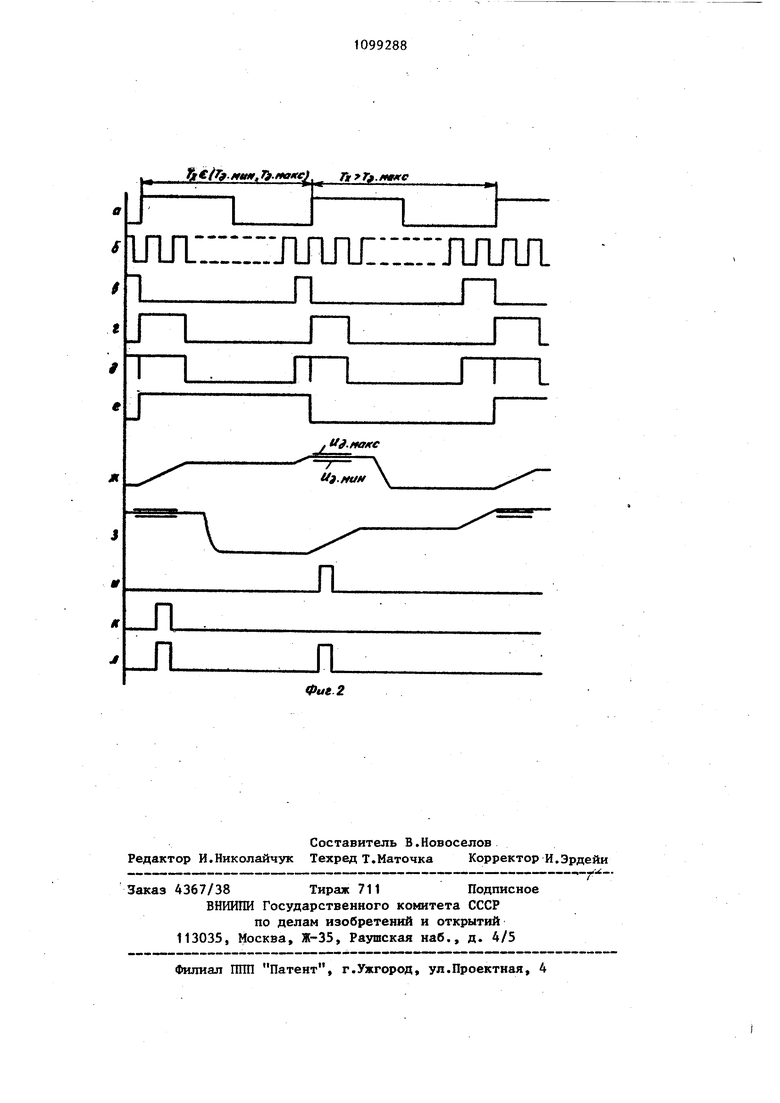

На фиг. 2 обояначены напряжения на выходе первого формирователя 4 импульсов (Q), опорного генератора 1 (S), на выходе сброса блока 3 запуска и сброса ( Ь), выходе второго формирователя 6 импульсов (2 ) выходе первого элемента ИЛИ 7 (А ) выходе счетного триггера 5 ( 6), выходах интеграторов 10 (ж) и 11 С, выходах компараторов 12 (и) и13 (к ) и выходе второго элемента ИЛИ 14(л).

Устройство работает следующим образом.

Контролируемый сигнал в первом формирователе 4 импульсов преобразуется в последовательность прямоуголь ных импульсов с тем же периодом Т (фиг. 2а). Фронт каждого из этих импульсов через блок 3 запуска и

сброса разрешает счет счетчику 2, который начинает считать импульсы от опорного генератора 1, имеющие период следования Т (фиг. 28i) . Импульс переполнения с первого выхода счетчика 2, получаемый после счета N опорных импульсов, поступает на блок 3 запуска и сброса, сигналы с которого производят блокирование счетчика 2 и его обнуление.

Если Т- находится в зоне допуска, то счетчик 2 заканчивает счет за ut Tg до прихода следующе1го фронта контролигу чого сигнала. Импульс длительностью и tjформируется на выходе сброса блока 3 запуска и сброса (фиг. 2Ь) по сигналам с первого формирователя 4 импульсов и счетчика 2. Второй формирователь 6 импульсов по сигналам с первого формирователя 4 импульсов и опорного генератора 1 формирует импульс t.) (фиг.22 начинающийся по фронту контролируемого сигнала и заканчивающийся по фронту второго импульса опорного генератора 1 , пришедшего после фронта контролируемого сигнала.

Хотя длительность Аt) и ut зависи от фазовьгх соотношений контролируемого и опорного сигналов, от них не зависит. Суммирование длительностей указанных импульсов производится первым элементом ИЛИ 7 (фиг.2о

Так как за импульсом t предыдущего периода Т непосредственно(Следует импульс it следующего периода, то дальнейшая их обработка производится двумя одинаковыми цепочками, состоящими из последовательно включеных интегратора 10 и компаратора 12 (в другой цепочке соответ.ственно 11 и 13), одна из которых работает в четные периоды TX, а другая - в нечетные. Разделение периодов TX на четные и нечетные производится по фронту сигнала с первого формирователя импульсов 4 счетным триггером 5 (фиг. 2е). По сигналу со счетного триггера 5 первый коммутатор 8 подсодиняет выход первого элемента ИЛИ 7 к интегратору 10 (или 11), который преобразует длительность импульсов it, + ut2 в напряжение U (фиг. 2,J.) Это напряжение поступает на двусторонний стробируемый компаратор 12 (или 13), в котором производится его допусковый контроль путем сравнения с постоянными опорными напряжениями иодд„„. и поступающими от источника 15 опорных напряжений. Во время следующего за измеряемым периода Т, импульс с второго выхода счетчика 2 поступает -на стробирующие входы компараторов 12 и 13, во время его действия определяется выполнено ли условие U в {U- .. , омакс т.е. находился ли измеренный период в пределах допуска. Если условие выполнено, то на выходе компаратора 12 (или 13) появляется импульс (фиг. 2.U, к ), проходящий через второй элемент ИЛИ 14 на выход устройства (фиг. 2).

Сброс интегратора 10 (или 11) производится импу;1ьсом с третьего-выхода счетчика 2, прошедшим через второй коммутатор 9 на вход сброса интегратора.

Наличие импульса на выходе второго элемента ИЛИ 14 свидетельствует о том, что предьщущий период Т находился в пределах допуска.

В предлагаемом устройстве счетчик 2 представляет собой обычный счетчик емкостью N, два из промежуточных состояний которого опознаются схемами опознавания (например,элементами И, подключенными.к прямым или инверсным выходам старших разрядов счетчика), сигналы с которых поступают соответственно на второй и третий выходы счетчика. Блок 3 запуска и сброса может быть реализован на D-триггерё, прямой и инверсный вьпсодЫ которого являются соответственно выходами разрешения счета и сброса блока, С-вход триггера соединен с первым формирователем 4 импульса, R-вход - с выходом переполнения счетчика 2, на D-вход подается логическая единица. Второй формирователь 6 импульсов может быть выполнен на двухразрядном регистре сдвига и элементе И, причем D-вход регистра и первый вход элемента И соединены с первым формирователем импульсов 4, С-вход регистра - с опорным генератором 1, а инверсный выход регистра - с вторым входом элемента И.

В устройстве за счет устранения погрешности квантования удалось повысить точность контроля периода.

фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для оценки характеристик узкополосного случайного процесса | 1983 |

|

SU1117650A1 |

| Устройство для измерения времени установления выходного сигнала цифроаналогового преобразователя | 1990 |

|

SU1716601A2 |

| Устройство для измерения времени установления цифроаналогового преобразователя | 1986 |

|

SU1432776A1 |

| УСТРОЙСТВО ДЛЯ ВОЗБУЖДЕНИЯ УДАРНЫХ ИМПУЛЬСОВ | 1993 |

|

RU2019795C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1337784A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| РАДИОЛУЧЕВОЙ ДАТЧИК ОХРАНЫ | 1992 |

|

RU2079889C1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Тренажер руководителя группы операторов | 1990 |

|

SU1714653A1 |

| Устройство для регистрации динамических процессов | 1988 |

|

SU1624437A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЕРИОДА КОЛЕБАНИЙ, содержащее блок запуска и сброса, счетчик, первый формирователь импульсов, выход которого подключен к первому входу блока запуска и сброса, выходы сброса и разрешения счета которого соединены с соответствующими входами счетчика, а его второй вход - с выходом переполнения счетчика, а также опорный генератор, выход которого подключен к сигнальному входу счетчика, отличающееся тем, что, с целью повышения точности контроля периода колебания путем устранения ошибки квантования, в него введены второй формирователь импульсов, два элемента ЮШ, д в а коммутатор а, два интегратора, два компаратора, счетный триггер и источник опорных напряжений, причем первый и второй входы второго формирователя импульсов соединены соответственно с выходами первого формирователя импульсов и опорного генератора, а выход соединен с первым входом первого элемента ИЛИ, к второму входу которого подключен выкод сброса блока запуска и сброса, а к выходу первого элемента ИЛИ подключен сигнальный вход перво- , го коммутатор., при этом вход счетного триггера соединен с выходом первого формирователя импульсов, его выход - с управлякмцими входами первого и второго коммутаторов, первый выход первого коммутатора через включенные последовательно первый инте(Л гратор и первый компаратор подключен к первому входу второго элемента ИЛИ, причем второй выход первого коммутатора через последовательно соединенные второй интегратор и второй компаратор подключен к второму входу второго элемента ИЛИ, при этом второй выход счетчика соединен с входами стробирования первого и второго компараторов, третий В1ЛХОД счетчика - с управляющим входом второго коммутатора, выходы которого подключены к входам сброса первого и второго интеграторов , а выходы источника опорных напряжений соединены с соответствующими входами компараторов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Широкопредельный фазометр | 1979 |

|

SU918879A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Дискретный полосовой фильтр | 1966 |

|

SU481121A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-06-23—Публикация

1982-12-20—Подача