vj 00 00 СЛ

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2008728C1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ РЕЧЕВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2018180C1 |

| Устройство для магнитной записи и воспроизведения речевых сигналов | 1986 |

|

SU1365115A1 |

| СЕЙСМИЧЕСКАЯ СТАНЦИЯ С БЛОКОМ РЕЧЕВОГО СОПРОВОЖДЕНИЯ, ИСПОЛЬЗУЮЩИМ ПРИНЦИП ДЕЛЬТА-МОДУЛЯЦИИ | 2007 |

|

RU2339055C1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Устройство для записи-считывания звуковых сигналов | 1989 |

|

SU1712964A1 |

| Устройство для цифровой записи и считывания речевых сигналов | 1985 |

|

SU1302291A1 |

| Устройство для магнитной записи-воспроизведения речевых сигналов | 1990 |

|

SU1739384A1 |

| Устройство для цифровой записи-считывания речевых сигналов | 1984 |

|

SU1210132A1 |

Изобретение относится к накоплению информации, а именно к устройствам для цифровой записи-воспроизведения речевой информации, и предназначено для расширения рабочего динамического диапазона записываемых речевых сигналов за счет поддержания средней мощности воспроизводимых речевых сигналов, независимо от их средней мощности при записи. При записи речевых фрагментов на выходе сигнала уровня речи появляются пачки однородных символов, плотность которых пропорциональна уровню входного речевого сигнала. Сигнал пачек преобразуется в аналоговый сигнал, несущий информацию об уровне входного речевого сигнала. Этот сигнал сравнивается с уровнем порога и на основе сравнения формируется сигнал речевых фрагментов (логическая 1) и пауз (логический О), поступающий на вход сигнала пауз блока управления. Блок управления управляет записью речевой дельта-последовательности в блок основной памяти и записью информации о длительности пауз в блок дополнительной памяти. В режиме чтения сигнал среднего значения уровня записи управляет величиной шага квантования при дельта-демодуляции и соответственно величиной средней мощности воспроизведения. 2 з.п. ф-лы. 3 ил. ь/ - В

Изобретение относится к накоплению информации, а именно к устройствам для цифровой записи-воспроизведения речевой информации.

Известное устройство для цифровой записи-воспроизведения речевой информации содержит блок основной динамической памяти, элемент И аналого-цифровой пре: образователь, формирователь управляющих импульсов, адресный счетчик, дешифратор, цифроанэлоговый преобразователь, счетчик временных интервалов, адресный мультиплексор, первый, второй и третий элементы ИЛИ, коммутатор и триггер записи.

Недостатком данного устройства является ограниченный рабочий динамический диапазон записываемых речевых сигналов для заданной разборчивости речи при воспроизведении.

Наиболее близким к предлагаемому является устройство для цифровой записи- воспроизведения речевых сообщений, содержащее блок основной памяти, выходом подключенный к первому входу первого коммутатора, блок аналого-цифрового и цифроэналогопого преобразователей (АЦП/ЦАП). первый вход которого подключен к входной шине речевого сигнала, гене- ратор кода паузы, блок дополнительной памяти, соединенный первым входом с первым входом блока основной памяти и первым входом блока управления, первый, второй, третий, четвертый, пятый и шестой входы которого подключены соответственно к управляющему входу первого коммутатора, первому, второму и третьему входам блока дополнительной памяти, первому и второму управляющим входам блока основ- ной памяти, второй коммутатор, элемент И, интегратор, входную шину управления режимами, входную шину тактового сигнала, подключенную к второму входу блока управления, входную шину запуска, подклю- ченную к третьему входу блока управления, и выходную шину для звукового воспроизведения.

Данное устройство обладает ограниченным рабочим динамическим диапазо- ном записываемых сигналов при заданной разборчивости речи при воспроизведении, что обусловлено тем, что при записи слабых сигналов они .воспроизводятся с тем же уровнем.

Целью изобретения является расширение рабочего динамического диапазона записываемых речевых сигналов за счет поддержания средней мощности воспроизводимых речевых сигналов независимо от их средней мощности при записи.

Для этого в устройство для цифровой записи-воспроизведения речевых сигналов, содержащее блок основной памяти, выхо- дом подключенный к первому входу первого коммутатора, блок аналого-цифрового и цифроаналогового преобразователей, первый вход которого подключен к входной шине речевого сигнала, генератор кода паузы, блок дополнительной памяти, соединенный первым входом с первым входом блока основной памяти и первым входом блока управления, первый, второй, третий, четвертый, пятый и шестой выходы которого подключены соответственно к управляюще- му входу первого коммутатора, первому, второму и третьему входам блока дополнительной памяти, первому и второму управляющим входам блока основной памяти, второй коммутатор, элемент И, интегратор, входную шину управления режимами, входную шину тактового сигнала, подключенную к второму входу блока управления, входную шину запуска, подключенную к третьему входу блока управления, и выходную шину

для звукового .воспроизведения, дополни тельно введены элемент НЕ, пороговый блок, аналоговый ключ, интегратор со сбросом и формирователь импульсов, при этом второй, третий, четвертый и пятый входы блока АЦП/ЦАП соединены соответственно с входной шиной управления режимами, входной шиной тактового сигнала, выходами первого и второго коммутаторов, а первый, второй и третий выходы подключены соответственно к выходной шине для звукового воспроизведения, второму входу блока основной памяти и входу интегратора, выход которого соединен через пороговый блок и элемент И с четвертым входом блока управления и подключен через аналоговый ключ, и интегратор со сбросом к первому входу второго коммутатора, второй вход которого соединен с общей шиной, управляющий вход - с другим входом элемента И, подключенным через формирователь импульсов к управляющему входу интегратора со сбросом и соединенным через элемент НЕ с входной шиной управления режимами и первыми входами блоков основной и дополнительной памяти, а входная шина тактового сигнала подключена через генератор кода паузы к второму входу первого коммутатора.

Кроме того, блок АЦП/ЦАП содержит последовательно соединенные блок сравнения, формирователь цифровой последовательности, первый коммутатор, цифровой детектор уровня, интегратор, регулируемый усилитель, амплитудно-импульсный модулятор (АИМ) и двойной интегратор, выход которого подключен к одному входу блока сравнения, второй коммутатор и фильтр нижних частот, вход которого подключен к выходу второго коммутатора, первый и второй входы которого соединены соответственно с выходом двойного интегратора и общей шиной, выход первого коммутатора подключен к второму входу АИМ модулятора, при этом первым, вторым, третьим, четвертым, пятым входами, первым, вторым и третьим выходами АЦП/ЦАП являются соответственно другой вход блока сравнения, управляющий вход первого коммутатора, соединенный с управляющим входом второго коммутатора, другой вход формирователя цифровой последовательности соединенный с другим входом цифрового детектора уровня, второй вход первого коммутатора, управляющий вход регулируемого усилителя, выход фильтра нижних частот, выход формирователя цифровой последовательности и выход цифрового детектора уровня.

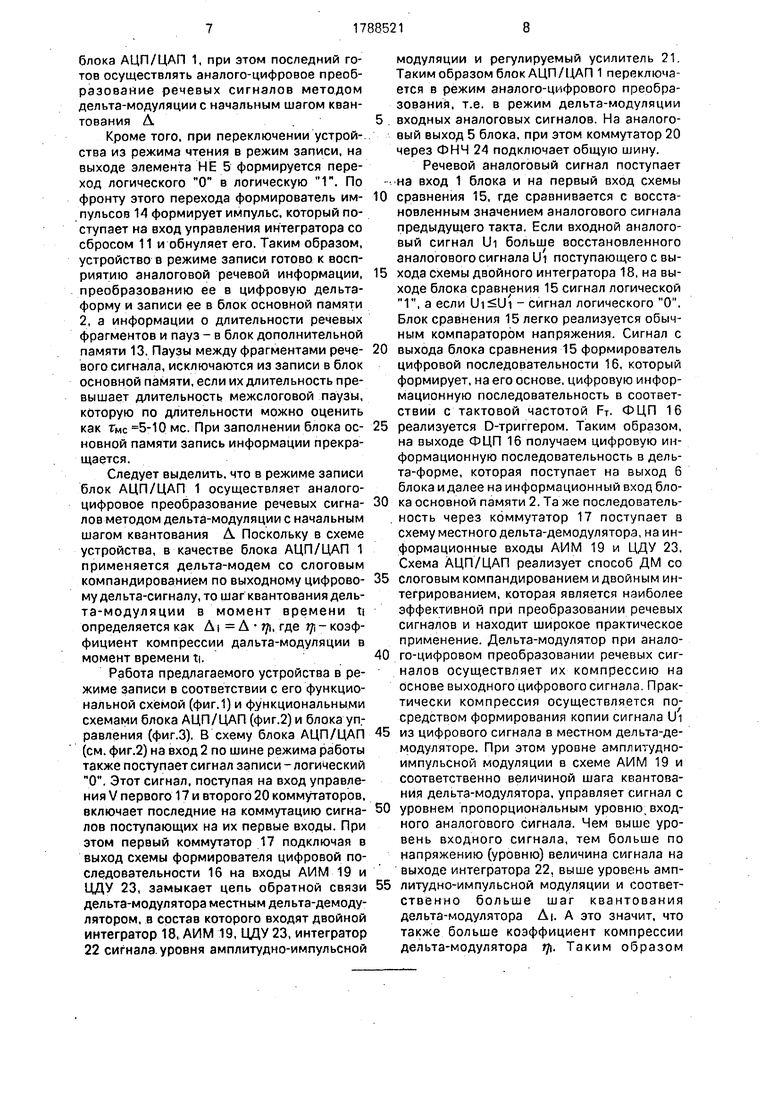

Блок управления содержит шесть элементов И, элемент ИЛИ, дпа адресных счетчика, счетчик-делитель частоты, два дешифратора, таймер, два триггера и буферный блок, при этом выход п ервлго адресного счетчика соединен через первый дешифратор с инверсным входом первого элемента И, оыход которого подключен к одному входу второго элемента И, инверсный выход которого соединен со счетным входом первого адресного счетчика, выход счетчика-делителя частоты подключен к счетным входам второго адресного счетчика и таймера, а через третий элемент И по его инверсному выходу - к синхровходу первого триггера, D-вход которого соединен с первым выходом буферного блока, прямой выход первого триггера подключен через четвертый элемент И и элемент ИЛИ к другому входу первого элемента И, выход второго триггера соединен через элемент И с другим входом элемента ИЛИ и через шестой элемент И по его инверсному выходу - с управляющими входами счетчика-делителя частоты и второго адресного счетчика, выход которого подключен через второй дешифратор к инверсному входу третьего элемента И, второй вход шестого элемента И соединен с выходом таймера, первым, вторым, третьим и четвертым входами блока управления являются соответственно другой вход четвертого элемента И, соединенный с третьими инверсными входами пятого и шестого элементов И и с вторым входом буферного блока, другой вход второго элемента И, соединенный с синхровходом счетчика-делителя частоты, вход сброса первого адресного счетчика, соединенный с входом сброса второго адресного счетчика, входами сброса счетчика-делителя частоты и второго триггера, и вход установки второго триггера, соединенный с входом сброса таймера, с вторым входом пятого элемента И и с первым входом буферного блока, а первым, вторым, третьим, четвертым, пятым и шестым выходами блока управления являются соответственно инверсный выход первого триггера, выход буферного блока, инверсный выход третьего элемента И, выход второго адресного счетчика, инверсный выход второго элемента И и выход первого адресного счетчика.

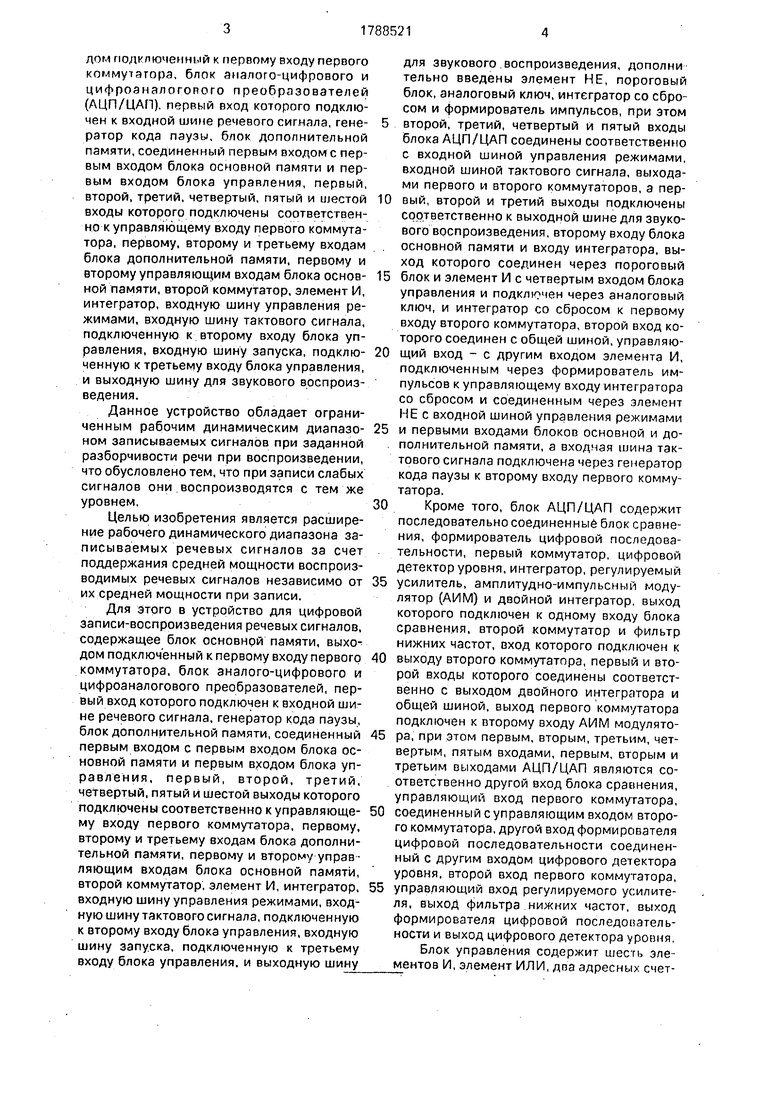

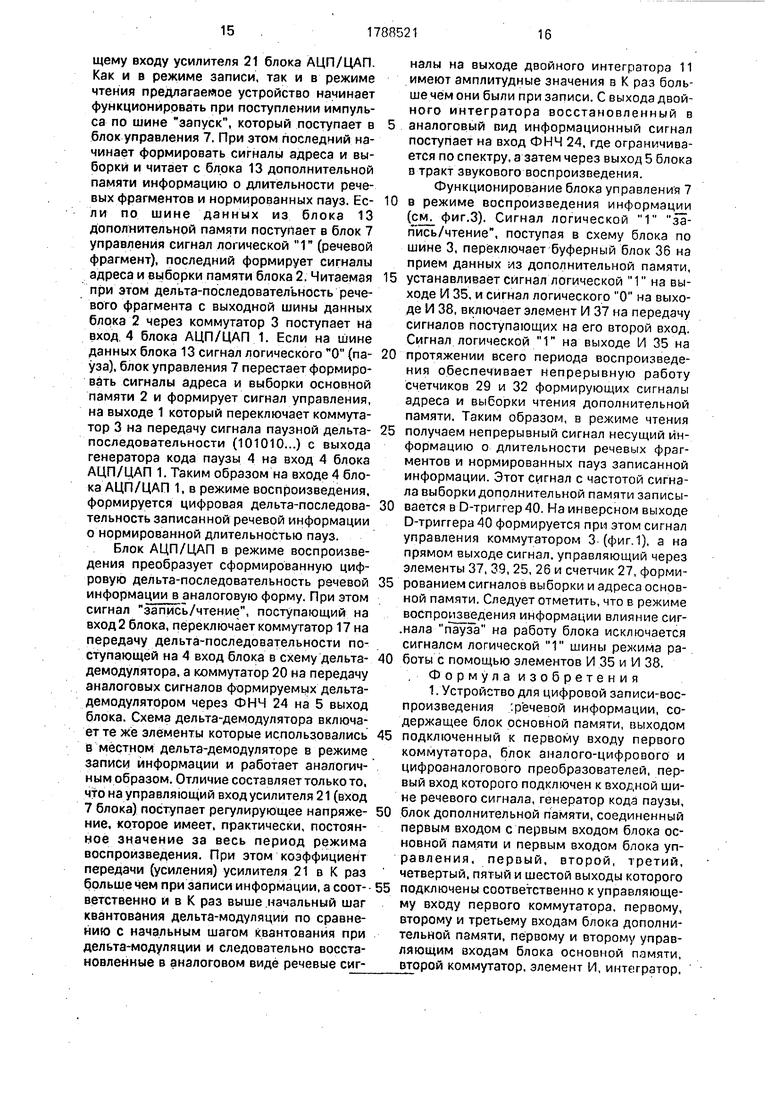

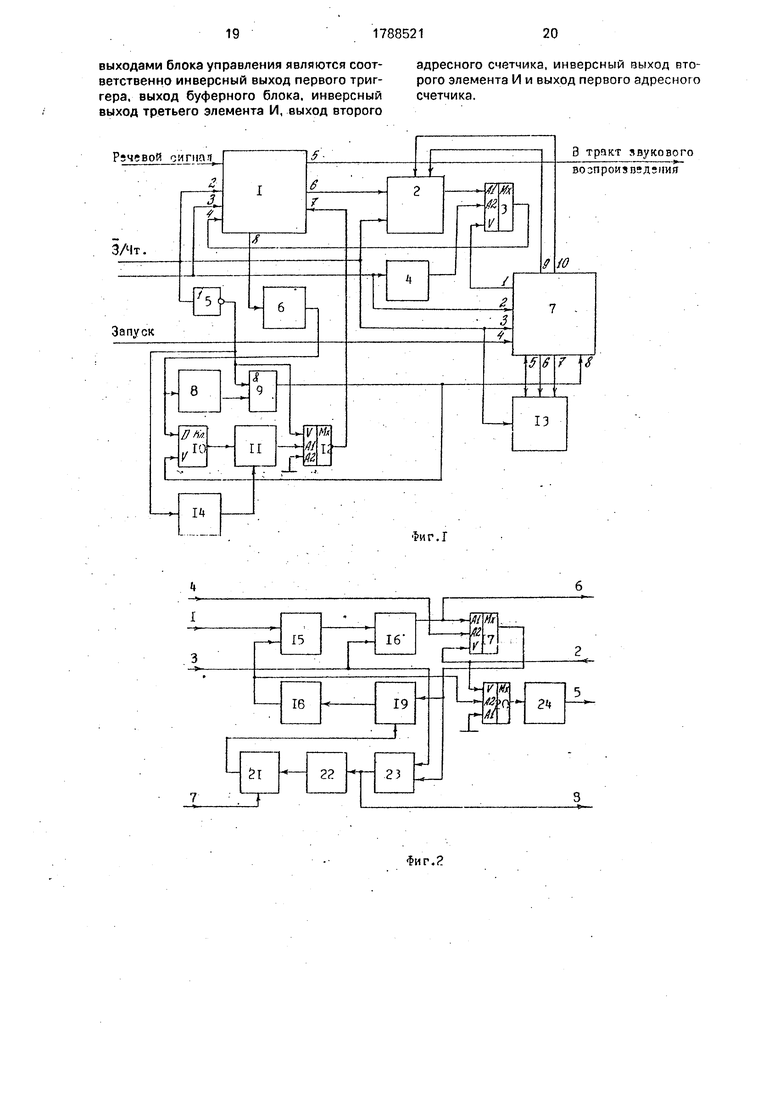

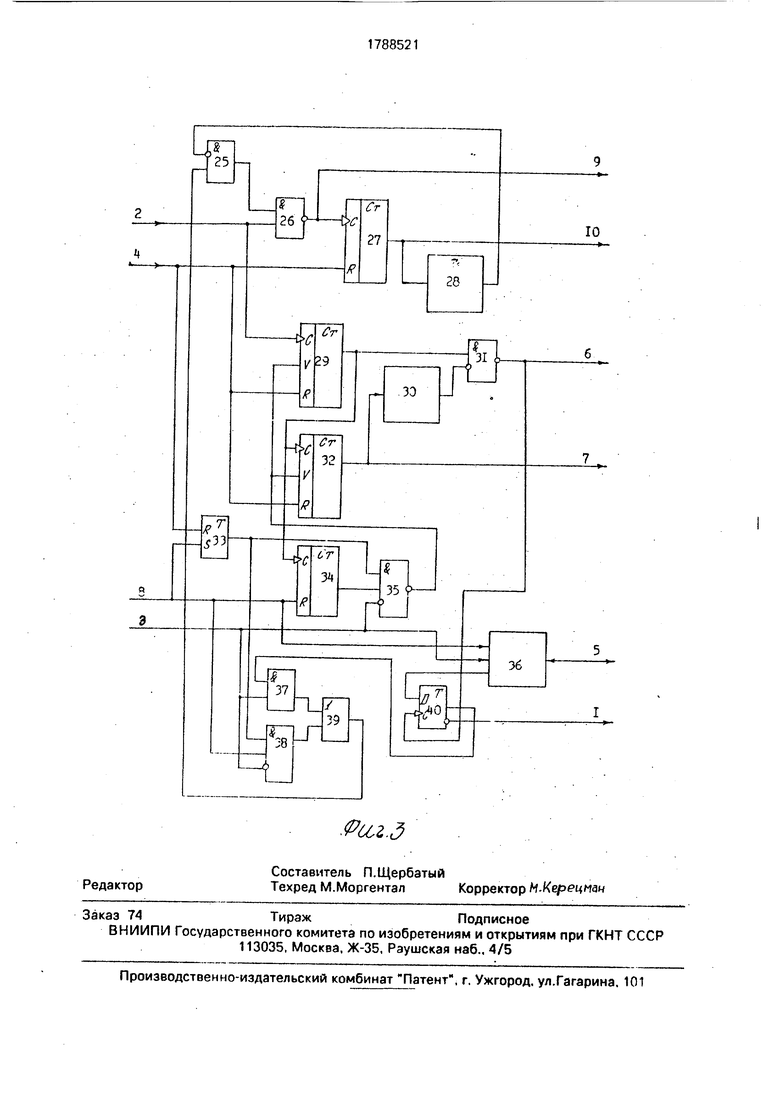

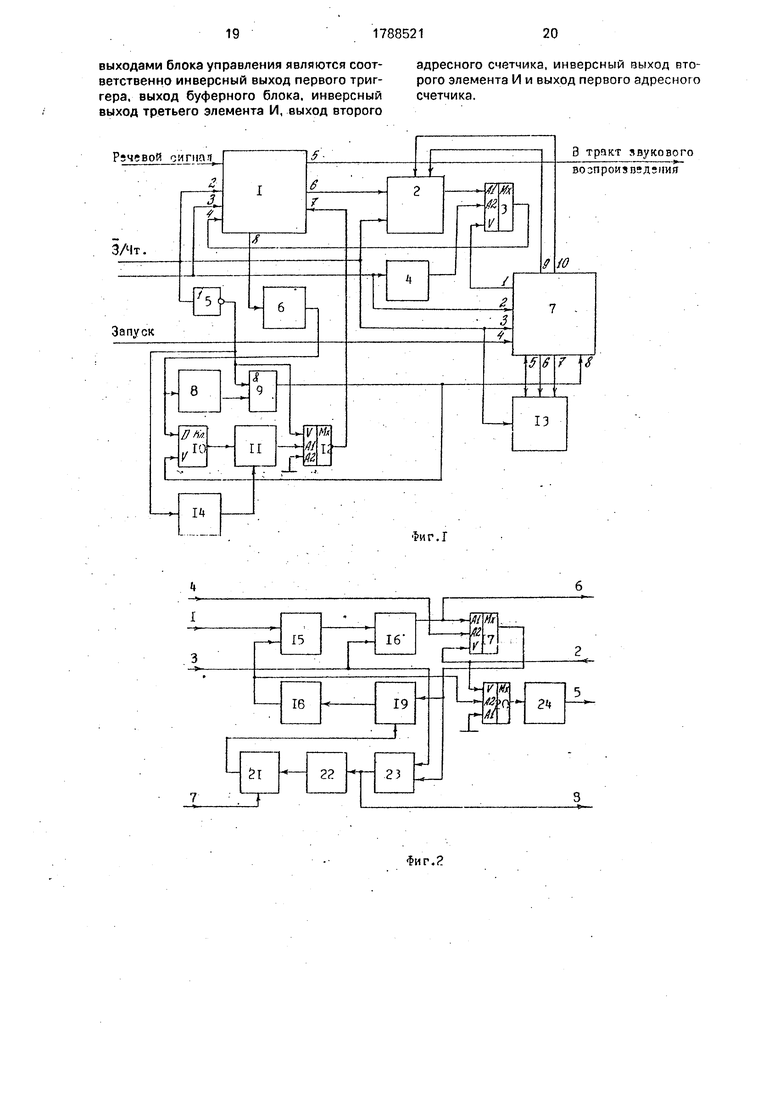

На фиг, 1 представлена функциональная схема устройства для цифровой записи-воспроизведения речевой информации; на фиг.2 - функциональная схема блока анало- го-цифрового и цифроаналогового преобразований; па фиг.З - функциональная схема блока управления.

Устройство для цифровой записи-воспроизведения речевой информации (фиг.1) состоит из блока аналого-цифрового и цифроаналогового преобразований 1, блока основной памяти 2, генератора кода паузы 4, первого 3 и второго 12 коммутаторов, элемента НЕ 5, интегратора б, блока упрэвле- 5 ния 7, порогового устройства 8, элемента И 9, аналогового ключа 10. интегратора со сбросом 11, блока дополнительной памяти 13 и формирователя импульсов 14. .

Блок аналого-цифрового и цифроанало0 гового преобразований (фиг.2) включает блок сравнения 15, формирователь цифровой последовательности 16, первый 17 и второй 20 коммутаторы, двойной интегратор 18, амплитудно-импульсный модулятор

5 19, фильтр нижних частот 24, регулируемый усилитель 21, интегратор 22 и цифровой детектор уровня 23.

Блок управления (фиг.З) состоит из первого 25, второго 26, третьего 31, четвертого

0 37, пятого 38 и шестого 35 элементов И, первого27 и второго 32 адресных счетчиков, счетчика-делителя частоты 29, первого 28 и второго 30 дешифраторов, таймера 34, первого 40 и второго 33 триггеров, элемента

5 ИЛИ 39 и буферного блока 36.

Принцип работы устройства для цифровой записи-воспроизведения речевой информации в соответствии с его функциональным назначением, заключает0 ся в следующем. Для записи речевой или другой информации в устройство, его схема подключается к источнику напряжения питания и по тактовой шине подается сигнал тактовой частоты FT (см. фиг.1). К шине уп5 равления режимом работы устройства за- пись/чтение подключается сигнал логического О, а по шине запуск подает- . ся импульс логической 1, который устанав- ливает блок управления 7 в начальное

0 состояние. Сигнал логического О шины . запись/чтение, поступая в блок АЦП/ЦАП 1 включает его в режим аналого-цифрового преобразования, поступая в блок управления 7, переключает его на работу управле5 ния записью информации в. устройство и поступая в блоки основной 2 и дополнительной 13 памяти включает их на режим записи цифровой информации. Кроме того, сигнал логического О режима записи поступает.

0 на вход элемента НЕ 5, преобразуется в сигнал логической 1 и поступает на первый вход элемента И 9 и управляющий вход коммутатора 12. При этом, элемент И 9 транслирует выходной сигнал порогового

5 блока 8 на вход управления аналогового ключа 10 и на вход 8 сигнала паузы блока управления 7. Коммутатор 12, при сигнале логической на.управляющем входе, подключает общую шину устройства к входу 7 управления масштабом шага квантования

блока АЦП/ЦАП 1, при этом последний готов осуществлять аналого-цифровое преобразование речевых сигналов методом дельта-модуляции с начальным шагом квантования А

Кроме того, при переключении устрой-, ства из режима чтения в режим записи, на выходе элемента НЕ 5 формируется переход логического О в логическую Г. По фронту этого перехода формирователь импульсов 14 формирует импульс, который поступает на вход управления интегратора со сбросом 11 и обнуляет его. Таким образом, устройство в режиме записи готово к восприятию аналоговой речевой информации, преобразованию ее в цифровую дельта- Форму и записи ее в блок основной памяти 2, а информации о длительности речевых фрагментов и пауз - в блок дополнительной памяти 13. Паузы между фрагментами речевого сигнала, исключаются из записи в блок основной памяти, если их длительность превышает длительность межслоговой паузы, которую по длительности можно оценить как Тмс 5-10 мс. При заполнении блока основной памяти запись информации прекращается.

Следует выделить, что в режиме записи блок АЦП/ЦАП 1 осуществляет аналого- цифровое преобразование речевых сигналов методом дельта-модуляции с начальным шагом квантования Л Поскольку в схеме устройства, в качестве блока АЦП/ЦАП 1 применяется дельта-модем со слоговым компандированием по выходному цифровому дельта-сигналу, то шаг квантования дель- та-модуляции в момент времени ti определяется как A t А rj. где - коэффициент компрессии дальта-модуляции в момент времени ti.

Работа предлагаемого устройства в режиме записи в соответствии с его функциональной схемой (фиг.1) и функциональными схемами блока АЦП/ЦАП (фиг.2) и блока управления (фиг.З). В схему блока АЦП/ЦАП (см. фиг.2) на вход 2 по шине режима работы также noctynaeT сигнал записи-логический О. Этот сигнал, поступая на вход управления V первого 17 и второго 20 коммутаторов, включает последние на коммутацию сигналов поступающих на их первые входы. При этом первый коммутатор 17 подключая в выход схемы формирователя цифровой последовательности 16 на входы АИМ 19 и ЦДУ 23, замыкает цепь обратной связи дельта-модулятора местным дельта-демодулятором, в состав которого входят двойной интегратор 18, АИМ 19, ЦДУ 23, интегратор 22 сигнала, уровня амплитудно-импульсной

модуляции и регулируемый усилитель 21. Таким образом блок АЦП/ЦАП 1 переключается в режим аналого-цифрового преобразования, т.е. в режим дельта-модуляции

входных аналоговых сигналов. На аналоговый выход 5 блока, при этом коммутатор 20 через ФНЧ 24 подключает общую шину.

Речевой аналоговый сигнал поступает на вход 1 блока и на первый вход схемы

сравнения 15, где сравнивается с восстановленным значением аналогового сигнала предыдущего такта. Если входной аналоговый сигнал Ui больше восстановленного аналогового сигнала Ui поступающего с выхода схемы двойного интегратора 18, на выходе блока сравнения 15 сигнал логической 1, а если - сигнал логического О. Блок сравнения 15 легко реализуется обычным компаратором напряжения. Сигнал с

выхода блока сравнения 15 формирователь цифровой последовательности 16, который формирует, на его основе, цифровую информационную последовательность в соответствии с тактовой частотой FT. ФЦП 16

реализуется D-триггером. Таким образом, на выходе ФЦП 16 получаем цифровую информационную последовательность в дельта-форме, которая поступает на выход 6 блока и далее на информационный вход блока основной памяти 2. Та же последовательность через коммутатор 17 поступает в схему местного дельта-демодулятора, на информационные входы АИМ 19 и ЦДУ 23, Схема АЦП/ЦАП реализует способ ДМ со

слоговым компандированием и двойным интегрированием, которая является наиболее эффективной при преобразовании речевых сигналов и находит широкое практическое применение. Дельта-модулятор при аналого-цифровом преобразовании речевых сигналов осуществляет их компрессию на основе выходного цифрового сигнала. Практически компрессия осуществляется посредством формирования копии сигнала 1/1

из цифрового сигнала в местном дельта-демодуляторе. При этом уровне амплитудно- импульсной модуляции в схеме АИМ 19 и соответственно величиной шага квантования дельта-модулятора, управляет сигнал с

уровнем пропорциональным уровню, входного аналогового сигнала. Чем выше уровень входного сигнала, тем больше по напряжению (уровню) величина сигнала на выходе интегратора 22, выше уровень амплитудно-импульсной модуляции и соответственно больше шаг квантования дельта-модулятора Д|. А это значит, что также больше коэффициент компрессии дельта-модулятора т. Таким образом

ществляется компрессия в схеме дельта-ко- дека при анзлого-цифровом преобразовании,

Формирование сигнала, управляющего уровнем амплитудно-импульсной модуля- ции. В выходном цифровом дельта-сигнале плотность пачек однородных посылок пропорциональна величине уровня (средне- квадратического значения напряжения) входного аналогового сигнала. ЦДУ 23 ана- лизирует выходную информационную дель- та-последовательность и если в ней появляются пачки из N и более однородных посылок (нулей или единиц) вырабатывает импульс длительность которого равна (про- порциональна) длительности однородных посылок в пачке. Для преобразования речевых сигналов с FT 32-64 кГц как правило, используются дельта-кодеки с . Импульсы интегрируются интегратором 22, на вы- ходе которого получаем сигнал пропорциональный уровню входного аналогового сигнала. Этот сигнал через регулируемый усилитель 21 поступает на вход управления уровнем АИМ 19. Коэффициент передачи по напряжению регулируемого усилителя 21 в режиме записи равен , Это достигается подачей на управляющий вход регулируемого усилителя 21 (вход 7 блока АЦП/ЦАП) сигнала нулевого уровня.

Таким образом, в режиме записи информации формируется сигнал управляющий уровнем амплитудно-импульсной модуляции, а следовательно и величиной шага квантования дельта-модуляции, который в момент времени trc учетом коэффициента передачи усилителя (коэффициента усиления) можно определить как:

AI Д $ К

С учетом, что .

Цифровая информационная дельта-последовательность с выхода ФЦП 16 посту- паетна выход 6 блока АЦП/ЦАП и далее (см. фиг.1) на информационный вход блока основной памяти.

В устройстве, на основе сигнала пачек выделенного ЦДУ 23 и несущего информа- цию об уровне входного аналогового сигнала, ведется выделение, с помощью порогового контроля, речевых фрагментов и пауз речи, а также определение (оценка) среднего уровня записываемых речевых фрагментов. При этом сигнал пачек с выхода ЦДУ 23 поступает также на выход 8 сигнала уровня речи блока АЦП/ЦАП и далее (см. фиг.1) на вход интегратора 6. Интегратор 6 на основе сигнала пачек формирует сигнал, отображающий уровень входного сигнала. Постоянные времени заряда Гзар.б и разряда граэр.б интегратора б выбираются из следующих соображений. Постоянная времени заряда Г3арб выбирается такой, чтобы не было потери информации при определении начала речевого фрагмента. А это, как было установлено экспериментально, выполняется если теряется не более 1/4 длительности слогового интервала. Длительность слогового интервала пример- неравна 10-20 мс. Постоянная времени разряда интегратора б выбирается такой, чтобы устройство не воспринимало межслоговые паузы, как паузы в речевом сигнале и соответственно чтобы дельта-сигнал межслоговых пауз записывался в блок основной памяти. Это условие выполняется если постоянная времени разряда интегратора б примерно в два-три раза больше постоянной времени межслоговой паузы. Реализуется интегратор 6 на основе RC-злементов, а для получения различных постоянных времени разряда и заряда используется диод. Пороговый блок 8 сравнивает сигнал уровня, формируемый интегратором 6, с сигналом порога и на основе сравнения формирует сигнал логической 1, если на аналоговом входе АЦП речевой фрагмент и логического О, если на аналоговом входе АЦП пауза. Реализуется такой пороговый блок с помощью обычного компаратора на второй вход (-) которого подается сигнал порога формируемый обычным резистив- ным делителем напряжения питания устройства ип. В режиме записи информации сигнал сформированный пороговым блоком 8 через элемент И поступает на вход 8 блока управления 7 и на вход управления V ключа 10. На информационный вход D ключа 10 поступает сигнал уровня с выхода интегратора 6. В промежутки времени, соответству- .ющие речевым фрагментам во входном аналоговом сигнале, пороговое устройство 8 формирует сигнал логической 1й, который через элемент И 9 поступает на вход управления V ключа 9, при этом последний подключает сигнал поступающий на его вход D к информационному входу интегратора со сбросом 11. Таким образом, сигнал уровня формируемый интегратором 6 поступает на информационный вход интегратора со сбросом 11 только в промежутки времени соответствующие речевым фрагментам во входном аналоговом сигнале. В результате интегратор со сбросом формирует средний уровень записываемых речевых фрагментов. С учетом того, что каждый раз перед

началом записи интегратор со сбросом 11 обнуляется сигналом формирователя импульсов 14, то за весь пербиод записи этот интегратор формирует средний уровень речевых фрагментов поступающих на аналоге- вый вход устройства за время записи.

Работа в режиме записи блока управления 7 и его взаимодействие с блоками основной 2 и дополнительной 13 памяти, Функциональной задачей этого блока в ре- жиме записи является управление записью речевых фрагментов в блок основной памяти, а информации о их длительности и длительности речевых пауз в блок дополнительной памяти и в соответствии с этим формирование сигналов адреса и выборки основной и дополнительной памяти. Частота сигнала выборки основной памяти определяется и равна тактовой частоте ана- лого-цифрового преобразования (FT). Часто- та сигнала выборки дополнительной памяти существенно ниже FTи определяется максимальным временным интервалом, потеря которого не приводит к потери информации в слоге речевого фрагмента, и его величина примерно составляет 4-5 мс.

В блок управления (фиг.З), в режиме записи, по шине 3 поступает сигнал логического О. Этот сигнал поступает на второй вход элемента И 37, на инверсные третьи входы элементов И 38 и И 35 и на вход управления буферного блока 36 дополнительной памяти. При этом буферный блок 36 переключается на трансляцию данных поступающих на его прямой вход (сигнала па- уза поступающего на вход 8 блока). Для элемента И 37 этот сигнал исключает передачу на его выход сигналов поступающих на другой вход, а для элементов И 38 и И 35 он является разрешающим, поскольку посту- пает на их инверсные входы. Импульс логической 1, поступающий на 4 вход блока управления по шине запуск и определяющий готовность устройства к записи речевой информации, устанавливает в исходное состояние адресный счетчик 27 основной памяти, счетчик-делитель частоты 29, адресный счетчик 32 дополнительной памяти и RS-триггер 33. По шине 2 в схему блока поступает сигнал тактовой частоты FT. На основе этого сигнала формируются в блоке сигналы управления записью в основную и дополнительную памяти. В дальнейшем работу блока управления в режиме записи информации рассмотрим в зависимости от логического сигнала на входе 8 пауза (О

- на аналоговом входе устройства пауза, 1

- на аналоговом входе устройства речевой фрагмент). Сигнал пауза, поступающий на вход 8 блока посредством элементов И 38,

ИЛИ 39, И 28 и И 26 на основе сигнала FT, формирует сигнал выборки основной памяти и управляет работой счетчика 27 формирующего сигнал адреса основной памяти. При этом сигналы выборки и адреса основной памяти формируются схемой блока если на входе 8 пауза сигнал логической 1 (речевой фрагмент на аналоговом входе блока). Указанные сигналы управляют записью речевого фрагмента, преобразованного блоком 1 АЦП/ЦАП в цифровую форму, в блок 2 основной памяти. Счетчик-делитель частоты 29 на основе сигнала FT формирует сигнал выборки дополнительной памяти, частота которого, как уже отмечалось выше, определяется максимальным временным интервалом, потеря каждого не приводит к потере информации в слоге речевого фрагмента. Сигнал с выхода счетчика-делителя частоты 29 поступает на выход 6 блока и на счетные (С) входы адресного счетчика 32 и таймера 34. На основе этого сигнала адресный счетчик 32 формирует сигнал адреса дополнительной памяти. Таймер 34, функциональное назначение которого нормирование допустимой длительности пауз между фрагментами речи при записи, включается по входу R сигналом перепада с высокого уровня на низкий, а выключается обратным перепадом. Поэтому при сигнале логической 1 на входе 8 блока (речевой фрагмент) таймер выключен и соответственно на его выходе сигнал логического О, а на выходе элемента И 35 сигнал логической 1. При этом счетчик-делитель частоты 29 и адресный частоты 29 и адресный счетчик 32 непрерывно формируют соответственно сигнал выборки дополнительной памяти, тем самым обеспечивая запись в блок дополнительной памяти 13 сигнала логической 1 пауза поступающего в этот блок через буферный блок 36 и шину данных дополнительной памяти 5.

При переходе от речевого фрагмента к паузе в сигнале пауза происходит перепад с высокого уровня на низкий, который включает таймер 34. Кроме того низкий уровень (логический О) сигнала пауза через элементы 38, 39, 25 и с помощью элемента И 26 прерывает поступление сигнала FT на выход этого элемента, тем самым останавливается формирование сигналов выборки и адреса основной памяти. Таким образом, в устройстве исключается запись паузной дельта-последовательности в блок основной памяти 2. Формирование сигналов выборки и адреса дополнительной памяти продолжается и в дополнительную память записывается логический О сигнала пауза поступающий в блок 13 через буферный блок 36 и шину

данных дополнительной памяти.. Если пауза между речевыми фрагментами превышает заданную таймером 34 длительность, последний срабатывает и через элемент И 35 останавливает работу счетчиков 29 и 32, тем самым прекращается запись сигнала логического О пауза в блок 13. Нормирование пауз позволяет применять в блоке 13 память с малым объемом. Схема блока управления предусматривает выбрасывание паузы перед речевым фрагментом записываемым в устройство и выбрасывание речевого фрагмента который начался до поступления импульса по шине 4 запуск. Это осуществляется с помощью RS-тригге- ра 33, который формирует сигнал логической 1 на выходе только после поступления первого речевого фрагмента начавшегося после поступления импульса запуск. Выходной сигнал триггера 33 через элементы 38, 39, 25, 26, 35 управляет работой счетчиков 27, 29 и 32.

При заполнении основной или дополнительной памяти, по соответствующей кодовой комбинации сигнала адреса срабатывает дешифратор окончания счета (28 или 30) и запись информации прекращается. Таким образом, функционирует в режиме записи информации блок управления 7 предлагаемого устройства.

Как уже отмечалось, целью предлагаемого изобретения является расширение рабочего динамического диапазона записываемых речевых сигналов за счет поддержания средней мощности при их воспроизведении независимо от средней мощности при записи. За весь период записи интегратор 11 сформирует средний уровень речевых фрагментов записанных в блоке основной памяти 2. В режиме воспроизведения напряжение сформированное интегратором 11 подключается через мутатор 12 к регулирующему входу усилителя 21 в блоке 1 АЦП/ЦАП и устанавливает величину его коэффициента К передачи (усиления). Следовательно и в К раз увеличивается начальный шаг квантования дельта-демодуляции, которая осуществляется в блок АЦП/ЦАП в режиме чтения, по сравнению с начальным шагом квантования при дельта-модуляции. С учетом того, что при чтении дельта-демодулятором является схема включающая элементы блока 1 ЦАП/АЦП которые использовались как местный дельта-демодулятор при дельта-модуляции в режиме записи и при этом начальный шаг квантования в К раз больше начального шага при дельта-модуляции, получим амплитудные значения восстановительных в блоке 1 речевых фрагментов в

К раз большими чем они были при записи. Это значит что сигнал при воспроизведении в К раз линейно усиливается по сравнению с записываемым. Следует отметить, что при 5 этом достигается высокая линейность усиления, т.к. нелинейные искажения будут определяться механизмом квантования (шумами квантования) и нелинейностью характеристики зависимости К усилителя 21

0 от величины регулирующего напряжения. Линейность такую достаточно просто обеспечивать, т.к. необходимые пределы изменения начального тага квантования незначительны и абсолютные значения ма5 лы. Такая регулировка усиления при воспроизведении по сравнению с непосредственной регулировкой речевого восстановленного сигнала, динамический и частотный диапазоны которого значительно

0 шире, является значительно эффективней по энергетическим параметрам и проще при реализации. Для поддержания средней мощности воспроизведения независимо от средней мощности при записи

5 необходимо, чтобы зависимость от средней мощности при записи необходимо, чтобы зависимость К усилителя 21 от величины регулирующего напряжения была обратно пропорциональной, т.е. малым значениям

0 напряжения сформированным интегратором 11 при записи слабых сигналов соответствовали большие значения коэффициента передачи (усиления) К усилителя 21,

. Таким образом, предлагаемое устройст5 во позволяет поддерживать среднюю мощность воспроизведения речевых фрагментов независимо от их средней мощности при записи в блок памяти, что позволяет расширить рабочий динамический

0 диапазон записываемых речевых фрагментов.

Работа устройства в режиме чтения (воспроизведения) информации. В режиме чтения по шине загшсь/чтение поступает

5 сигнал логической 1, который, поступая в блок 1 АЦП/ЦАП, 2 основной памяти, 13 дополнительной памяти и управления, переводит их в режим чтения информации. Элементом НЕ 5 этот сигнал преобразуется

0 в сигнал логического О, который поступает на вход элемента И 9 и управляющий вход коммутатора 12. Поступая на один из входов элемента И 9 сигнал логического О исключает передачу сигнала пауза, фор5 мируемого пороговым устройством, на 8 вход блока 7 управления. Поступая на вход управления коммутатора 12, сигнал логического О переключает его на коммутацию сигнала среднего уровня фрагментов, сформированного интегратором 11,к управляющему входу усилителя 21 блока АЦП/ЦАП. Как и в режиме записи, так и в режиме чтения предлагаемое устройство начинает функционировать при поступлении импульса по шине запуск, который поступает в блок управления 7. При этом последний начинает формировать сигналы адреса и выборки и читает с блока 13 дополнительной памяти информацию о длительности речевых фрагментов и нормированных пауз. Ее- ли по шине данных из блока 13 дополнительной памяти поступает в блок 7 управления сигнал логической I (речевой фрагмент), последний формирует сигналы адреса и выборки памяти блока 2. Читаемая при этом дельта-последовательность речевого фрагмента с выходной шины данных блока 2 через коммутатор 3 поступает на вход. 4 блока АЦП/ЦАП 1. Если на шине данных блока 13 сигнал логического О (па- уза), блок управления 7 перестает формировать сигналы адреса и выборки основной памяти 2 и формирует сигнал управления, на выходе 1 который переключает коммутатор 3 на передачу сигнала паузной дельта- последовательности (101010...) с выхода генератора кода паузы 4 на вход 4 блока АЦП/ЦАП 1. Таким образом на входе 4 блока АЦП/ЦАП 1, в режиме воспроизведения, формируется цифровая дельта-последова- тельность записанной речевой информации о нормированной длительностью пауз.

Блок АЦП/ЦАП в режиме воспроизведения преобразует сформированную цифровую дельта-последовательность речевой информации в аналоговую форму. При этом сигнал запись/чтение, поступающий на вход 2 блока, переключает коммутатор 17 на передачу дельта-последовательности поступающей на 4 вход блока в схему дельта- демодулятора, а коммутатор 20 на передачу аналоговых сигналов формируемых дельта- демодулятором через ФНЧ 24 на 5 выход блока. Схема дельта-демодулятора включает те же элементы которые использовались в местном дельта-демодуляторе в режиме записи информации и работает аналогичным образом. Отличие составляет только то, что на управляющий вход усилителя 21 (вход 7 блока) поступает регулирующее напряже- ние, которое имеет, практически, постоянное значение за весь период режима воспроизведения. При этом коэффициент передачи (усиления) усилителя 21 в К раз больше чем при записи информации, а соответственно и в К раз выше начальный шаг квантования дельта-модуляции по сравнению с начальным шагом квантования при дельта-модуляции и следовательно восстановленные в аналоговом виде речевые сигналы на выходе двойного интегратора 11 имеют амплитудные значения в К раз больше чём они были при записи. С выхода двойного интегратора восстановленный в аналоговый вид информационный сигнал поступает на вход ФНЧ 24, где ограничивается по спектру, а затем через выход 5 блока в тракт звукового воспроизведения.

Функционирование блока управления 7 в режиме воспроизведения информации (см. фиг.З). Сигнал логической 1 запись/чтение, поступая в схему блока по шине 3, переключает буферный блок 36 на прием данных из дополнительной памяти, устанавливает сигнал логической 1 на выходе И 35, и сигнал логического О на выходе И 38, включает элемент И 37 на передачу сигналов поступающих на его второй вход. Сигнал логической 1 на выходе И 35 на протяжении всего периода воспроизведения обеспечивает непрерывную работу счетчиков 29 и 32 формирующих сигналы адреса и выборки чтения дополнительной памяти. Таким образом, в режиме чтения получаем непрерывный сигнал несущий информацию о длительности речевых фрагментов и нормированных пауз записанной информации. Этот сигнал с частотой сигнала выборки дополнительной памяти записывается вО-триггер40. На инверсном выходе D-триггера 40 формируется при этом сигнал управления коммутатором 3 (фиг. 1), а на прямом выходе сигнал, управляющий через элементы 37, 39, 25, 26 и счетчик 27, формированием сигналов выборки и адреса основной памяти. Следует отметить, что в режиме воспроизведения информации влияние сиг- .нала пауза на работу блока исключается сигналом логической 1 шины режима работы с помощью элементов И 35 и I/I 38. . Формула изобретения

входную шину управления режимами, входную шину тактового сигнала, подключенную к второму входу блока управления, входную шину запуска, подключенную к третьему входу блока управления, и выходную шину для звукового воспроизведения, отличающееся тем, что, с целью расширения динамического диапазона записи-воспроизведения за счет поддержания средней мощности воспроизводимых речевых сигналов независимо от их средней мощности при записи, введены элемент НЕ, пороговый блок, аналоговый ключ, интегратор со сбросом и формирователь импульсов, при этом второй, третий, четвертый и пятый входы блока аналого-цифрового и цифроанало- гового преобразователей соединены соответственно с входной шиной управления режимами, входной шиной тактового сигнала, выходами первого и второго коммутаторов, а первый, второй и третий выходы подключены соответственно к выходной шине звукового воспроизведения, второму входу блока основной памяти и входу интегратора, выход которого соединен через пороговый блок и элемент И с четвертым входом блока управления и подключен через аналоговый ключ, и интегратор со сбросом к первому входу второго коммутатора, второй вход которого соединен с общей шиной, управляющий вход - с другим входом элемента И, подключенным через формирователь импульсов к управляющему входу интегратора со сбросом и соединенным через элемент НЕ с входной шиной управления режимами и первыми входами блоков основной и дополнительной памяти, а входная шина тактового сигнала подключена через генератор кода паузы к второму входу первого коммутатора.

управляющим входом второго коммутатора, другой вход формирователя цифровой последовательности, соединенный с другим входом цифрового детектора уровня, второй вход первого коммутатора, управляющий

0 вход регулируемого усилителя, выход фильтра нижних частот, выход формирователя цифровой последовательности и выход цифрового детектора уровня.

5 входом первого адресного счетчика, выход счетчика-делителя частоты подключен к счетным входам второго адресного счетчика и таймера, а через третий элемент И по его инверсному выходу - к синхровходу первого

0 триггера, D-вход которого соединен с первым выходом буферного блока, прямой выход первого триггера подключен через четвертый элемент И и элемент ИЛИ к другому входу первого элемента И, выход вто5 рсго триггера соединен через пятый элемент И с другим входом элемента ИЛИ и через шестой элемент И по его инверсному выходу - с управляющими входами счетчика-делителя частоты и второго адресного

0 счетчика, выход которого подключен через второй дешифратор к инверсному входу третьего элемента И, второй вход шестого элемента И соединен с выходом таймера, первым, вторым, третьим и четвертым вхо5 дами блока управления являются соответственно другой вход четвертого элемента И, соединенный с третьими инверсными входами пятого и шестого элементов И, и с вторым входом буферного блока, другой

0 вход второго элемента И, соединенный с синхровходом счетчика делителя частоты, вход сброса первого адресного счетчика, соединенный с входом сброса второго адресного счетчика, входами сброса

5 счетчика-делителя частоты и второго триггера, и вход установки второго триггера, соединенный с входом сброса таймера, с вторым входом пятого элемента И и с первым входом буферного блока, а первым, вторым, третьим, четвертым, пятым и шестым

выходами блока управления являются соот- адресного счетчика, инверсный выход вто- ветственно инверсный выход первого триг- рого элемента И и выход первого адресного гера, выход буферного блока, инверсный счетчика. выход третьего элемента И, выход второго

| Устройство для цифровой записи-воспроизведения речевой информации | 1985 |

|

SU1272355A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для цифровой записи-воспроизведения речевых сообщений | 1985 |

|

SU1312641A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1993-01-15—Публикация

1990-11-05—Подача