допол1штельных перемножителей соедийены с выходом первого блока задержки, а объединенные вторые входы третьего и четвертого дополнительных перемножителей соединены с выходом .второго блока задержки, выходы первого и четвёртого дополнительных перемножителей соединены с соответствующими входами первого дополнительного сумматора, а выходы второго и третьего дополнительных перемножителей соединены с соответствующими входами второго дополнительного сумматора, кроме того, в каждом блоке регулирования синфазного и квадратурного подканалов последовательно соединены первый перемножитель, сумматор, интегратор, выход которого соединен с управляющим входом аттенюатора, второй вход сумматора соединен с выходом второго перемножителя, при этом первый вход второго перемножителя каждого блока регулирования синфазного подканала объединен попарно с первым входом второго перемножителя соответствукщего блока регулирования квадратурного

подканала и соединен с соответствующим входом, выходом или отводом второй: многоотводной линии задержки, а объединенные попарно первые входы первых перемножителей соответствуннцих блоков регулирования Синфазного и квадратурного подканалов соединены с соответствующим входом, выходом или отводом первой многоотводной линии задержки, кроме того, объединенные попарно вторые входы первого перемножителя каждого блока регулирования сифазного и второго перемножителя соответствующего блока регулирования квадратурного подканалов соединены с выходом первого дополнительного сумматора, а попарно объединенные вторые входы второго перемножителя каждого блока регулирования синфазного и первого перемножителя соответствукицего блока регулирования квадратурного подканалов соединены с выходом второго до полнительного сумматора (N - число отводов каждой многоотводной линии задержки, включая вход и выход).

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ АДАПТИВНЫЙ КОРРЕКТОР | 1983 |

|

RU2024199C1 |

| Цифровой адаптивный корректор сигналов многократной фазовой модуляции | 1981 |

|

SU1012445A1 |

| Адаптивный корректор сигналов с фазовой модуляцией | 1976 |

|

SU605321A1 |

| Адаптивный корректор | 1979 |

|

SU866756A2 |

| Адаптивный корректор | 1979 |

|

SU790353A1 |

| Способ когерентного приема сигналов амплитудно-фазовой модуляции и устройство для его осуществления | 1983 |

|

SU1185640A1 |

| Адаптивный корректор | 1978 |

|

SU769748A1 |

| Адаптивный корректор | 1977 |

|

SU657626A1 |

| Устройство для моделирования многолучевого радиоканала | 1984 |

|

SU1224810A1 |

| Устройство синхронизации несущей частоты | 1985 |

|

SU1356249A1 |

УСТРОЙСТВО ДЛЯ ПОЛОСОВОЙ АДАПТИВНОЙ КОРРЕКЩШ СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИИ, содержащее N блоков регулирования синфазного подканала и N блоков регулирования квадратурного подканала, каждый из которых состоит из аттенюато.ра, первую и вторую многоотводные линии задержки, при этом вход второй многоотводной линии задержки через первый фазовращатель соединен с входом первой многоотводной линии задержки, вход, выход и каждый из отводов которой подключен к аттенюаторам соответствующего блока регулирования синфазного подканала, выходам которых подключены к одному из вхо- , дов первого сумматора, а вход, выход и каждый из отводов первой многоотводной линии задержки подключены к аттенюаторам соответствунадего блока регулирования квадратурного подканала , выходы которых подключены к соответствующему входу второго сумматора, выход которого через второй фазовращатель подключен к входу третьего сумматора, другой вход которого соединен с выходом первого сумматрра, а выход третьего сумматора соединен с объединенными входами третьего фазовращателя, первого блока задержки, первого и второго перемножителей, выходы первого и второго перемножителей соединены соответственно с синфазным и квадратурным входами решакщего блока, а другие входы первого и второго перемножителей соединены соответственно с выходами первого и второго блоков задержки, при этом вход второго блока задержки соединен с выходом третьего фазовращателя, о т л и i Чающееся тем, что, с повышения помехоустойчивости приема сигналов, введены первый и второй генераторы ошибки, четыре дополнительных перемножителя, два дополнительных сумматора, а в каждый из блоков регулирования синфазного подканала и в каждый из блоков регулирования квадратурного подканала введены интегратор, сумматор и два перемножителя, при зтом входы первого генератора ошибки подключены соответственно к синфа.зным входу и выходу решаняцего блока, а входы второго генератора ошибки подключены соот ветственно к квадратурным входу и выходу решающего блока, выход первого генератора ошибки соединен с объединенными первыми входами первого и третьего дополнительных перемножителей, выход второго генератора ошибки соединен- с объединенными первыми входами второго и четвертого дополнительных перемножителей, объединенные вторью входы первого и второго

Изобретение относится к электросвязи и может использоватьсй для кор рекции искажений, вызванных ограничением полосы частот пропускания каналов связи в системах передачи цифровых сигналов методом относител ной фазовой модуляции. Известно устройство для адаптивн коррекции сигналов, состоящее из ли ний задержки, группы аттенюаторов, накопителей и корреляторов, включен ных в каждый из отводов линии задержки, при этом выходы аттенюаторо соединены с соответствующими входам сумматора, выход которого через решающий блок подключен к другим вхо-дам упомянутых аттенюаторов lj . Однако извёстнре устройство имее низкую точность коррекции при автокорреляционном приеме сигналов, а также зависимость процесса настройки от изменений фазы несущего коле/ания и, вследствие этого, низкую помехоустойчивость приема. Наиболее близким по технической сущности.и достигаемому эффекту является устройство для полосовой адаптивной коррекции сигналов относительной фазовой модуляции, содержащее N блоков регулирования синфазного подканала и N блоков регулирования квадратурного подканала, каждый из которых состоит из аттенюатора, первую и вторую многоотводные линии заде1якки, при этом вход второй многоотводной линии задержки через первый фазовращатель соединен с входом пер-вой многоотводной линии задержки, вход, выход и каждый из отводов которой подключеи к аттенюаторам соответствующего блока регулирования синфазного подканала, выходы которых подключены к одному из входов первого сумматора, а вход, вьйсод и каждый из отводов первой многоотводной линии

задержки подключены.к аттенюаторам соответствуюцего блрка регулирования квадратурного подканала, выходы которых подключены к соответствующему входу второго сумматора, выход которого через второй фазовращатель подключен к входу третьего сумматора, другой вход которого соединен с выходом первого сумматора, а выход третьего сумматора соединен.с объединен ными входами третьего фазовращателя,, первого блока задержки, первого и второго перемножителей, выходы первого и второго перемножителей соединены соответственно с синфазным и .квадратурным входами ре:шающего блока а другие входы первого и второго перемножителей соединены соответственно с выходами первого и второго блоков задержки, при этом вход второго блока задержки соединен с выходом третьего фазовращателя 2.

Однако данное устройство имеет также низкую помехоустойчивость автокорреляционного приема сигналов относительной фазовой модуляции.

Цель изобретения - повьппение помехоустойчивости приема сигналов.

Лдя этого в устройство для полосоBtj/J адаптивной коррекции .сигналов относительной фазовой модуляции, содержащаее N блоков регулирования синфазного и N блоков регулирования квадратурного подканалов, каждьй из которых состоит из аттенюаторов, первую и вторую многоотводные линии задержки, при этом вход второй многоотводной линии задержки через первый фазовращатель соединен с входом первой многоотводной линии задержки, вход, выкод и каждый из отводов которой подключен к аттенюаторам соответствующего блока регулирования синфазного подканала, выходы которых подключены к одному из входов первого сумматора, а вход, выход и каждый из отводов первой многоотводной линии задержки подключены к аттенюаторам соответствующего блока регулирования квадратурного подканала, выходы которых подключены к соответствующему входу второго сумматора, выход которого через, второй фазовращатель подключен к входу третьего сумматора, другой вход которого соединен с выводом первого сумматора, а выход

третьего сумматора соединен с объединенными входами третьего фазовращателя, первого блока задержки, первого и второго перемножителей, выходы первого я второго перемножителей соединены соответственно с синфазным и квадратурным входами решающего блрка а другие входы первого и второго перемножителёй соединены соответственн с выходами первого и второго блоков задержки, при этом вход второго блока задержки соединен с выходом

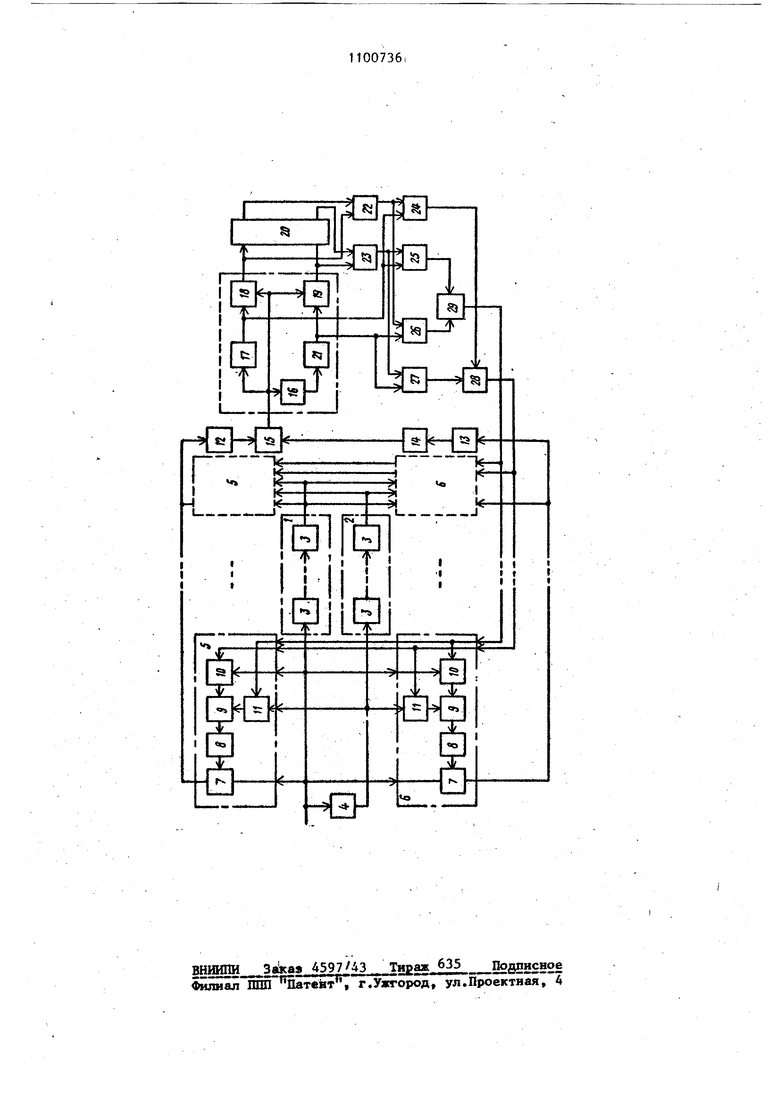

третьего фазовращателя, введены первый и второй генераторы ошибки, четыре дополнительных перемножителя, два дополнительных сумматора, а в каждый из блоков регулирования синф|азного подканала и в каждый из блоков регулирования квадратурного подканала введены интегратор, сумматор и два перемножителя, при этом входы первого генератора ошибки подключены соответственно к синфазным входу и выходу решающего блока, а входы второго генератора ошибки, подключены соответственно к квадратурным входу и выходу решающего блока,выход первого генератора ошибки соединен с объединенными первыми входами первого и третьего дополнительных перемножителей, выход второго генератора ошибки соединен с объединенными первыми входами второго и четвертого дополнительных перемножителей, объединенные вторые входы первого и второго дополнительных перемножителей соединены с выходом первого блока задержки, а объединенные вторые входы третьего и четвертого дополнительных перемножителей соединены с выходом второго блока задержки, выходы первого и четвертого дополнительных перемножителей соединены с соответствующими входами первого дополнительного сумматора, а выходы второго и третьего дополнительных перемножителей соединены с соответствующими входами второго дополнительного сумматора, кроме того, в каждом блоке регулирования синфазного и квадратурного подканалов последовательно соединены первый перемножитель, сумматор, интегратор, выход которого соединен с управляющим входом аттенюатора, второй вход сумматора соединен с выходом второго перемножителя, при этом первый / вход второго перемножителя каждого блока регулирования синфазного подканала объединен попарно с первым входом второго перемножителя соответ ствующего блока регулирования квадра турного подканала и соединен с соответствующим входом, выходом или отво дом второй многоотводной линии задер ки, а объединенные попарно первые входы первых перемножителей соответс вующих блоков регулирования синфазно го и квадратурного подканалов соединены с соответствующим входом, выходом или отводом первой многоотводной линий задержки, кроме того, объе диненные пойарно вторые входы первого перемножителя каждого блока регулирования синфазного и второго перемножителя cooтвetcтвyющeгo блока регулирования квадратурного подканалов соединены с выходом первого дополнительного сумматора, а попарно объе диненные вторые входы второго перемножителя каждого блока регулирования синфазного и первого перемножителя соответствующего блока регулирования квадратурного подканалов соединены с выходом второго дополнительного сумматора (N - число отводов каждой многоотводной линии задержки , включая вход и выход). I На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство для полосовой адаптивной коррекции сигналов относительной фазовой модуляции содержит первую и вторую многоотводные линии задержки 1 и 2, содержащие элементы задерж ки 3, первый фазовращатель 4, блоки регулирования синфазного и квадратурного подканалов 5 и 6, каждый из которых содержит аттенюатор 7, интегратор 8, сз мматор 9, первый и второй перемножители 10, 11 синфазного и квадратурного подканалов. Кроме того, устройство содержит первый и второй сумматоры 12 и 13, второй фазовращатель 14, третий сумматор 15, третий фазовращатель 16, пер вый элемент задержки 17, первый и второй перемножители 18 и 19, решающий блок 20, второй элемент задержки 21, первый и второй генераторы ошибки 22, 23, первьй,-второй, третий и четвертый дополнительные пере множители 24, 25, 26 и 27, первый и второй дополнительные сумматоры 28 и 29. Устройство работает следующим образом. Принимаемый сигнал поступает на вход первой многоотводной линии задержки 1 устройства. Сигналы с выходов линий задержки 1 и 2 через соответствующие аттенюаторы 7, изменяясь пропорционально весовым коэффициентам, суммируются в каждом подканале устройства первым и вторым сумматорами 12 и 13. Суммарный сигнал квадратурного подканала с выхода второго сумматора 13 через второй фазовращатель 14 поступает на вход третьего сумматора 15, на второй вход которого поступает сигнал с выхода первого сумматора 12. Сигнал с выхода третьего сумматора 15 поступает на вход первого перемножителя 18, на выходе КОТОРОГО сигнал пропорционален косинусу разности фаз несущего колебания в соседних тйктовых интервалах. На выходе второго перемножителя 19 сигнал пропорционален синусу разности фаз несущего колебания. На выходе решающего блока 20 вьфабатьюаются оценки передаваемых информационных символов по обоим подканалам. Первый и второй генераторы и ошибки 22 и 23 формируют сигналы ошибки S С п как разность между выходными сигналами синфазного или квадратурного подканалов соответственно и его оценкой в момент времени tn Сигнал ошибки ,„с вьпсода первого генератора ошибки 22 поступает на первый и третий дополнительные перемножители 24 и 26, где перемножается с выходными сигналами элементов задержки 17 и 21 соответственно, а сигнал ошибкой 6 J с выхода второго генератора ошибки 23 поступает на второй и четвертый дополнительные перемножители 25 и 27, где перемно- . жается с выходными сигналами первого и второго элементов задержки 17 и 21 соответственно. Сигналы с выходов первого и четвертого дополнительных перемножителей 24 и 27 суммируются в первом дополнительном сумматоре 28 и образуют первый вспомогательный сигнал управления U,, а сумма сигналов с выходов второго и третьего дополнительных перемножителей 25 W 26 - на выходе второго дополнительного сумматора 29, соответствует второму вспомогательному сигналу управления U.. Первый и второй вспомогательные сигналы управления поступают на входы первых и вторых перемножителей 10 и 11 блоков регулирования синфазного и квадратурного подканалов 5 и 6. На другие входы перемножителей 10 поступает сигнал с вькода соответст вующего отвода первой линии задержки 1, а на другие входы перемножителей 11 поступает сигнал с выхода соответствунмцего отвода второй лини задержки 2. Сигналы с выходов перемножителей 10 и 11 суммируются в су маторах 9 и через интеграторы 8 поступают на управлякядий вход аттенюа торов 7, чем обеспечивается процесс адаптивной настройки весовых коэффициентов устройства в соответствии со следующим алгоритмом: ,...«-%,Л 6n4i,w®n..Wn.,nn,w 1) где J. , А 1,n V 111 - коэффициент пропорциональности, причем 04( , Хц(п}{- сигнал в m отводе устройства в момент времени t, и сигнал - на входе устройства в момент д времени t,.. соответственно; to- символ преобразователя Гильберта, -весовой коэффициент m отвода линии задержки синфазного 5 и квадратурного 6 подканалов соответст- , венно в момент времени Ц; Технико-экономическая эффективность применения предлагаемого устройства заключается в обеспечении устойчивой коррекции сигналов относительной фазовой модуляции при меньших требованиях к искажением частотных характеристик проводных каналов связи, достигаемой за счет малой зависимости сигналов управления весовыми коэффициентами корректора от изменений фазы несущего колебания, что эквивалентно повышению помехоустойчивости автокорреляционного приема сигналов.

ми

,L5rn

J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США К 3727134, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 3755738, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| . | |||

Авторы

Даты

1984-06-30—Публикация

1982-12-20—Подача