мирования сигналов управления, тре- тий выход блока управления является вторым выходом блока формирования сигналов управления, четвертый блока управления является третьи выходом блока формирования сигналов управления, четвертый выход которого соединен с входом триггера, выход .которого соединен с вторым входом интегратора с хранением и сбросом.

пятый выход блока формирования сиг налов управления соединен с третьим входом интегратора с хранением и сбросом, пятый выход блока управления является шестым выходом блока формирования сигналов управления, шестой выход блока управления является седьмым выходом блока формирования сигналов управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель добротности резонансной системы | 1983 |

|

SU1109671A1 |

| Устройство для контроля манипулятора | 1988 |

|

SU1657375A1 |

| Цифровой измеритель добротности | 1977 |

|

SU659994A1 |

| Цифровой измеритель добротности | 1980 |

|

SU940087A2 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Устройство для определения частоты и добротности резонансных характеристик | 1981 |

|

SU960725A1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ОБЪЕМНОГО РАСХОДА ВЕЩЕСТВ С ПОМОЩЬЮ УЛЬТРАЗВУКОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2169906C2 |

| Датчик скорости, направления вращения и углового положения вала | 1988 |

|

SU1654972A1 |

| Устройство для измерения собственной частоты резонансной системы | 1987 |

|

SU1583875A1 |

1. ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ДОБРОТНОСТИ РЕЗОНАНСНЫХ СИСТЕМ, содержащий смеситель, гетеродин, вычислитель, частот7омер, два зажима для подключения резонансной системы и блок управления, причем первый из зажимов Для подключения резонансной системы соединен с одним из входов смесителя, выход вычислителя соединен с входом блока управления, выход гетеродина соединен с первым входом частотомера, отличающийся тем, что, с целью расширения пределов измерения добротности, в него дополнительно введены генератор шума, ограничитель, микропроцессор, индикатор и фильтр, причем выход генератора шума соединен с входом ограничителя , выход которого соединен с вторым зажимом для подключения резонансной системы, первый зажим для подключения резонансной системы соединен с первым входом вычислителя, ВЕ1ХОД смесителя соединен с входом фильтра, выход которого соединен с вторым входом вычислителя, выход гетеродина соединен с вторым входом смесителя, выход частотомера соединен с первым входом микропроцессора, выход которого соединен с первым входом гетеродина, второй выход блока управления соединен с первым входом индикатора, первый выход блока управления соединен с вторым входом гетеродина, третий выход блока управления соединен с вторым входом микропроцессора, четвертый выход блока управления соединен с третьим входом вычислителя, пятый выход блока управления соединен с вторым входом частотомера, шестой выход блока управления соединен с вторым входом индикатора, 2.Измеритель по п. 1, отличающийся тем, что вычислитель содержит первый пиковый детектор, амплитудный детектор, второй пиковый детектор, делитель, напряжения, коммутатор и компаратор, при- Щ чем первый вход вычислителя являет- мл ся входом первого пикового детек- Уд тора, выход которого соединен с первым входом коммутатора, второй вход вычислителя является входом амплитуд- ного детектора, выход которого сое- 5 динен с первым входом компаратора и с входом второго пикового етек-, тора, выход которого соединен с входом делителя напряжения, выход которого соединен с вторым входом коммутатора, выход которого соединен с вторым входом компаратора,, выход Ч ел которого является выходом вычислителя, третий вход вычислителя является третьим входом коммутатора. 3.Измеритель по п. 1, отличающийся тем, что блок управления содержит блок формирования сигнала управления, триггер и интегратор с хранением и сбросом, причем вход блока управления является первым входом интегратора с хранением и сбросом и входом блока формироваг ния сигналов управления, первый выход блока управления является выходом интегратора с хранением и сбросом, второй выход блока управления является первым В14ходом блока фор

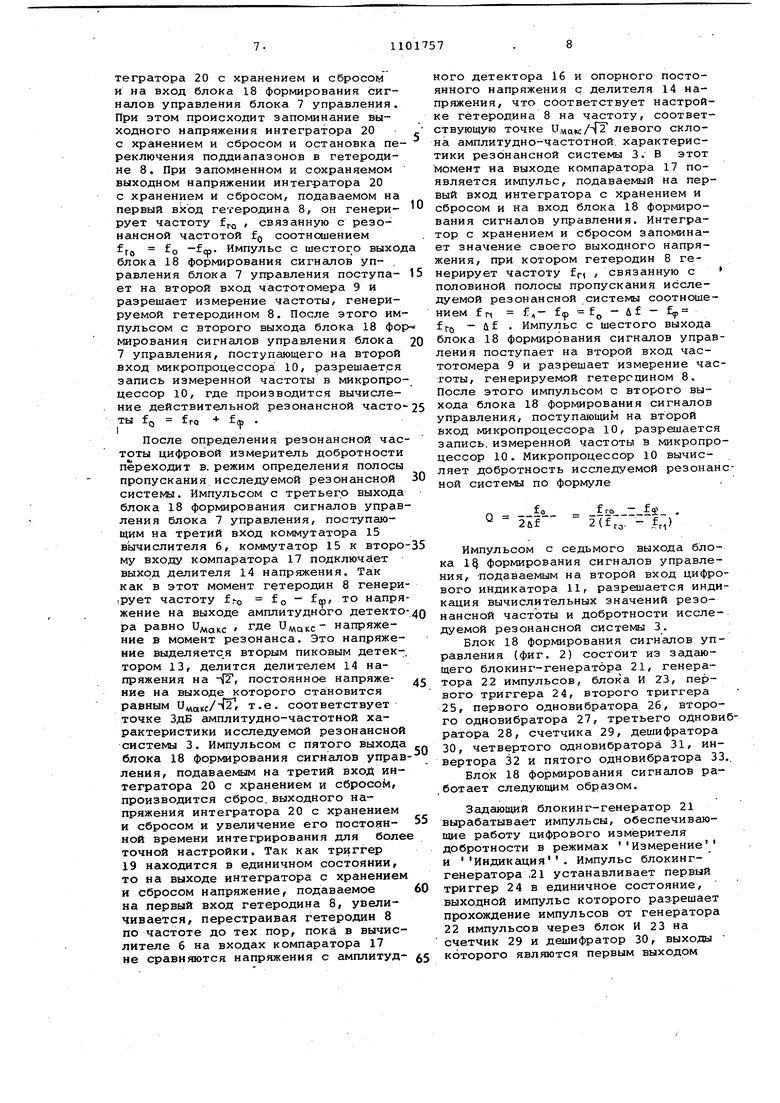

Изобретение относитсяк измерениям электрических и магнитных вели чин, в частности к измерению доброт ности резонансных электрических цепей. Известен цифровой измеритель доб ротности, содержащий генератор высо кой частоты, измерительный блок с широкополосным усилителем на выходе фазочувствительный блсж,первый вход которого соединен с выходом широкополосногр усилителя, широкополосный фазовращатель, цифровой измеритель, последовательно соединенные генератор низкой частоты, фазоинвертор, первый ключ и балансный модулятор, второй ключ, делитель частоты и блок управления, причем второй вход балан ного модулятора соединен с выходом генератора высокой частоты и входом делителя частоты, выход которого сое динен с одним из входов цифрового измерителя, другой вход которого сое динен с выходом генератора низкой частоты, а выход балансного модулято ра соединен с одним из входов широкополосного фазовращателя, выход О которого соединен с входом измерительного блока и с одним из входов второго ключа, .другой вход которого соединен с выходом 145 широкополосного фазовращателя, выход второго ключа соединен с вторым входом фаэочувствительного-блока, при этом управляющие входы фазоинвертора и вшрокополосного фазовра1аателя соединены с выходом блока управления {l . Недостатком такого цифрового измерителя добротности является отсутствие автоматической настройки на резонансную частоту и на частоту, соответствующую половине Полосы пропускания исследуемой резонансной сястена, что не позволяет проводить измерения в автоматическом режиме. Известен также цифровой измерител добротности, содержащий генератор перестраиваемой частоты, зажимы для подключения резонансной систе1 а, Вычислительный блок, гетеродин, смеситель, блок управления, частотомер, генератор гармоник и блок формирования управляющего напряжения, причем выход генератора переменной частоты . соединен с одним из зажимов для подключения резонансной системы и с одним из входов смесителя, другой вход которого соединен с выходом генератора -гармоник, выход смесителя соединен с первым входом блока управЛения и с одним из входов частотомера, другой вход которого соединен с первым выходом вычислительного блока, второй выход которого соединен с другим входом блока управления, выход которого соединен с вторым входом блока формирования управляющего напряжения, первый вход которого соединен с управляющим выходом генератора переменной частоты, выход блока формирования управляющего напряжения соединён с входом гетероди- , на, выход которого соединен с входом генератора гармоник и с третьим входом частотомера, вход вычислительного блока соединен с другим зажимом дляподключения резонансной системы, Вычислительный блок содержит пиковый детектор, делитель напряжения, блок сравнения и дифференцирующую цепь, причем вход вычислительного блока является первым входом блока сравнения и входом пикового детектора, выход которого соединен с в.хрдом делителя напряжения, выход которого соединен с вторым входом блока сравнения, выход которого соединен с входом дифференцирующей цепи, выходы которой являются выходами вычислительного блока. Блок управления содержит формирователь импульсов, элемент совпадения и генератор линейно изменяющегося напряжения, причем первый вход блока управления является входом формирователя импульсов, выход которого соединен с первым входом элемента совпадения, второй вход которого является вторым входом блока управления, выход элемента со падение соединен с входом генератор линейно изменяющегося напряжения, выход которого является выходом бло ка управления. Блок формирования уп равляющего напряжения содержит ийтегрирующую цепь, функциональный пр образователь и суммирующий блок, причем первый вход блока формирован управляющего напряжения является вх дом интегрирующей цепи, выход котор соединен с входом функционального п образователя, выход которого соединен с первым входом суммирующего блока,, выход которого являетсяг выходом блока формирования управляющего напряжения, второй вход которого является вторым входом суммиру щего блока 2 . Недостатком известного цифрового измерителя добротности является его невысокая точность при измерении низкодоб ротных систем. Цель изобретения - расширение пределов измерения добротности. Поставленная цель достигается те что в цифровой измеритель добротности, содержайщй смеситель, гетеродин, вычислитель, частотомер, два зажима для подключения резонансной системы и блок управления/ причем один из зажимов для подключения резонансной системы соединен с одним из входов смесителя, выход вычислителя, соединен с входом блока управления, выход гетеродина соединен с первым входом частотомера, дополнительно введены генератор шума, огра ничитель, микропроцессор, индикатор и фйль,тр, причем выход генератора шума соединен с входом ограничителя выход которого соединен с вторым за жимом для подключения резонансной системы, первый зажим для подключения резонансной системы соединен с первым входом вычислителя, выход .смесителя соединен с входом Фильтра выход которого соединен с вгорьам входом вычислителя, вых,:д гетеродина соединен с вторым входом смесите ля, выход частотомера соединен с пе вым входом микропроцессора, выход которого соединен с первым входом гетеродина,второй, выход блока управ ления соединен с первым входом инди катора, первый выход блока управления соединен с вторым входом гетеродина, третий выход блока управления соединен с вторым входом микропроцессора, четвертый выход блока у равления соединен с третьим входом вычислителя, пятый выход блока ления соединэн с-вторым входом частотомера, шестой,выход блока управления соединен с вторым входом инди катора. При этом вычислитель содержит первый пиковый детектор, амплитудный детектор, второй пиковый детектор, деЛитель напряжения, коммутатор и компаратор, причем первг1й вход вычислителя является входом первого пикового детектора, выход которого соединен с первым входом коммутатора, второй вход вычислителя является входом амплитудного детектора, выход которого соединен с первым входом компаратора и с входом второго пикового детектора, выход которого соединен с входом делителя напряжения, выход которого соединен с втор;ам входом коммутатора, в{лход которого соединен с вторым входом компаратора, выход .которого является выходом вычислителя, третий вход вычислителя является третьим входом коммутатора.Блок управления содержит блок формирЪвания сигнала управления, триггер и интегратор с хранением и сбросом, причем вход блока управления является первым входом интегратора с хранением и сбросом и входом блока формирования сигналов управления, первый выход блока управления является выходом интегратора с хранением и сбросом, второй выход блока управления является первым выходом блока формирования сигналов управления, третий выход блока управления является вторым выходом блока формирования сигналов управления, четвертый выход блока управления является третьим выходом блока формирования сигналов управления, чет- вертый выход которого соединен с входом триггера, выход которого согдинен с вторым входом интегратора с хранением и сбросом, пятый выход блока формирования сигнгшов управления соединен с третьим входом интегратора с хранением и сбросом, пятый выход блока управления является шестым выходом блока формирования сигИсшов управления, шестой выход блока управления является седьмым выходом блока формирования сигналов управления. На фиг. 1 изображена электрическая функционсшьная схема цифрового измерителя добротности; на фиг. 2 электрическая функциональная схема блока формирования сигналов управления; на фиг. 3 - электрическая функциональная схема интегратора с хранением и сбросом. Цифровой измеритель добротности состоит из генератора 1 шума, амплитудного ограничителя 2, измеряемой резонансной систе1«ы 3, смесителя 4, фильтра 5, вычислителя 6, блока 7 управления, гетеродина 8, частотомера 9, микропроцессора 10, цифрового индикатора 11. Вычислитель 6 состокт из первого пикового детектора 12, второго пикового детектора 13, дели теля 14 напряжения, коммутатора 15, амплитудного детектора 16, компаратора 17. Блок 7 управления состоит из блока 18 формирования сигналов у равления, триггера 19, интегратора 20 с хранением и сбросом. При этом выход генератора шума соединен с входом ограничителя, выход которого соединен с входом измеряемой резо- нансной систекы, выход резонансной системы соединен с первым входом вы числителя, выход смесителя соединен с входом фильтра, выход которого со динен с вторым входом вычислителя, выход гетеродина соединен с вторым входом смесителя, выход частотомера соединен с первым входом вычислителя, выход которого,соединен с Ьервы входом индикатора, первый выход бло ка управления соединен с первым вхо дом гетеродина, второй выход блока управления соединен с вторым входом гетеродина, третий выход блока упра ления соединен с вторьцу}. входом вычи лителя, четвертой выход блока управ ления соединен с третьим входом вычислителя, пятый выход блока управления соединен с вторым входом частотомера, шестой выход блока управления соединен с вторым входом индикатора. Первый вход вычислителя является входом первого пикового детектора, выход которого соединен с первым входом коммутатора, второй вход вы. числителя является входом амплитудного детектора, выход которого соединен с первым входом компаратора и с входом второго пикового детектора, выход которого соединен с входом делителя напряжения, выход которого соединен с вторым входом коммутатора выход которого соединен с вторым йходом компаратора, выход которого является выходом вычислителя. Вход блока управления является пе вым входом интегратора и входом блока формирования сигналов управления, первый выход блока управления . является выходом интегратора, второй третий, четвертый, пятый, шестой выходы блока управления являются выход ми блока формирования сигналов управ ления. Четвертый выход соединен с вторым входом интегратора. Цифровой измеритель добротности работает следующим образом. Генератор 1 шума генерирует ши- , рокий равномерный спектр, который ограничивается по амплитуде ограничи телем 2 и поступает на исследуемую резонансную систему 3. Резонансная система 3 вырезает из спектра генератора 1 шума учасаок, ограниченный ее амплитудно-частотной характеристи кой, который подается на первый вход вычислителя б и на первый вход смесителя 4, где он смешивается с подаваемой на второй вход смесителя 4 частотой гетеродина 8, т.е. участок спектра генератора 1 шума, ограниченный амплитудно-частотной характеристикой исследуемой резонансйой системы 3, переносится в более низкочастотную область. Фильтр 5 фильтрует этот участок спектра, и на его выходе в ыделяется одна частота fjp, которая подается на второй вход вычисли±еля б. Цифровой измеритель добротности резонансной системы работает в двух режимах: режиме поиска и определения резонансной частоты и в режиме определения ее полосы пропускания, причем переключение из одного режима в другой происходит по сигналам блок-а 7 управления. Поиск и определение резонансной частоты происходит следующим образом. Импульс с третьего выхода блока 18 Формирования сигналов управления блока 7 управления поступает на третий вход коммутатора 15 вычислителя б, и коммутатор 15 -подключает выход первого пикового детектора 12 к второму входу компаратора 17. На выходе первого пикового детектора .выделяется постоянное напряжение UMOUC/ равное напряжению на исследуемой резонансной системе на частоте резонанса. Импульсы с первого выхода блока 18 формирования сигналов управления блока 7 управления поступают на второй вход гетеродина В и последовательно переключают его поддиапазоны. Одновременно импульсом с четвертого выхода блока 18 формирования сигналов управления триггер 19 переключается в единичное состояние, единичный импульс которого интегрируется интегратором 20 с хранением и сбросом напряжение с которого подаеЗгся на первый вход гетеродина 8 и изменяет его частоту в пределах каждого поддиапазона. В конце каждого поддиапазона происходит сброс напряжения на интеграторе 20 с хранением и сбросом импульсом, поступающим на его третий вход с пятого выхода блока 18 формирования сигналов управления. Процесс перестройки по поддиапазонам гетеродина 8 происходит до тех пор, пока в вычислителе 6 на входах компаратора 17 не сравняются по амплитуде постоянное напряжение Омакс с первого пикового детектора 12 и. напряжение Ьгибающей резонансной кривой исследуемой резонансной системы 3 с амплитудного детектора 16. В момент равенства этих напряжений на выходе компаратора 17 появляется импульс, который поступает на первый вход интегратора 20 с хранением и сбросом и на вход блока 18 формирования сигналов управления блока 7 управления. При этом происходит запоминание выходного напряжения интегратора 20 с хранением и сбросом и остановка переключения поддиапазонов в гетеродине 8. При запомненном и сохраняемом выходном напряжении интегратора 20 с хранением и сбросом, подаваемом на первый вход гетеродина 8, он генерирует частоту f , связанную с резонансной частотой fg соотношением ffe fo fcp Импульс с шестого выход блока 18 формирования сигналов управления блока 7 управления поступает на второй вход частотомера 9 и разрешает измерение частоты, генерируемой гетеродином 8. После этого импульсом с второго выхода блока 18 фор мирования сигналов управления блока 7 управления, поступающего на второй вход микропроцессора 10, разрешаетря запись измеренной частоты в микропроцессор 10, где производится вычисление действительной резонансной часто

ты fg fro + ф .

После определения резонансной частоты цифровой измеритель добротности переходит в. режим определения полосы пропускания исследуемой резонансной системы. Импульсом с третьего выхода блока 18 формирования сигналов управления блока 7 управления, поступающим на третий вход коммутатора 15 вычислителя 6, коммутатор 15 к второ му входу компаратора 17 подключает выход делителя 14 напряжения. Так как в этот момент гетеродин 8 генери.рует частоту fo - fm/ то напряжение на выходе амплитудного детекто ра равно , где U gitc- напряжение в момент резонанса. Это напряжение выделяетс,я вторым пиковым детектором 13, делится делителем 14 напряжения на -fT, постоянное напряжевне на выходе которого становится равным т.е. соответствует точке ЗдБ амплитудно-частотной характеристики исследуемой резонансной системы 3. Импульсом с пятого выхода блока 18 формирования сигналов управ ления, подаваемым на третий вход интегратора 20 с хранением и сбросом, производится сброс,выходного напряжения интегратора 20 с хранением и сбросом и увеличение его постоднной времени интегрирования для боле точной настройки. Так как триггер 19 находится в единичном состоянии, то на выходе интегратора с хранением и сбросом напряжение, подаваемое на первый вход гетеродина 8, увеличивается, перестраивая гетеродин 8 по частоте до тех пор, пока в вычислителе 6 на входах компаратора 17 не сравняются напряжения с амплитудкого детектора 16 и опорного постоянного напряжения с делителя 14 напряжения/ что соответствует настройке гетеродина 8 на частоту, соответствующую точке и.исщс/Тз левого склона амплитудно-частотной, характеристики резонансной системы 3. В этот момент на выходе компаратора 17 появляется импульс, подаваемый на первый вход интегратора с хранением и сбросом и на вход блока 18 формирования сигналов управления. Интегратор с хранением и сбросом запоминает значение своего выходного напряжения, при котором гетеродин 8 генерирует частоту f(-, , связанную с половиной полосы пропускания исследуемой резонансной системы соотношением f п f ЕО - Л f - f fro uf . Импульс с шестого выхода блока 18 формирования сигналов управления поступает на второй вход частотомера 9 и разрешает измерение часготы, генерируемой гетеродином 8, После этого импульсом с второго выхода блока 18 формирования сигналов управления, поступающим на второй вход микропроцессора 10, разрешается запись, измеренной частоты в микропроцессор 10. Микропроцессор 10 вычисляет добротность исследуемой резонанной cHCTeNSJ по формуле

.$ .

frc. r

,.

- fn)

2uf

Импульсом с седьмого выхода блока 1 формирования сигналов управления, -подаваемым на второй вход цифрового индикатора 11, разрешается индикация вычислительных значений резонансной частоты и добротности исследуемой резонансной системы 3.

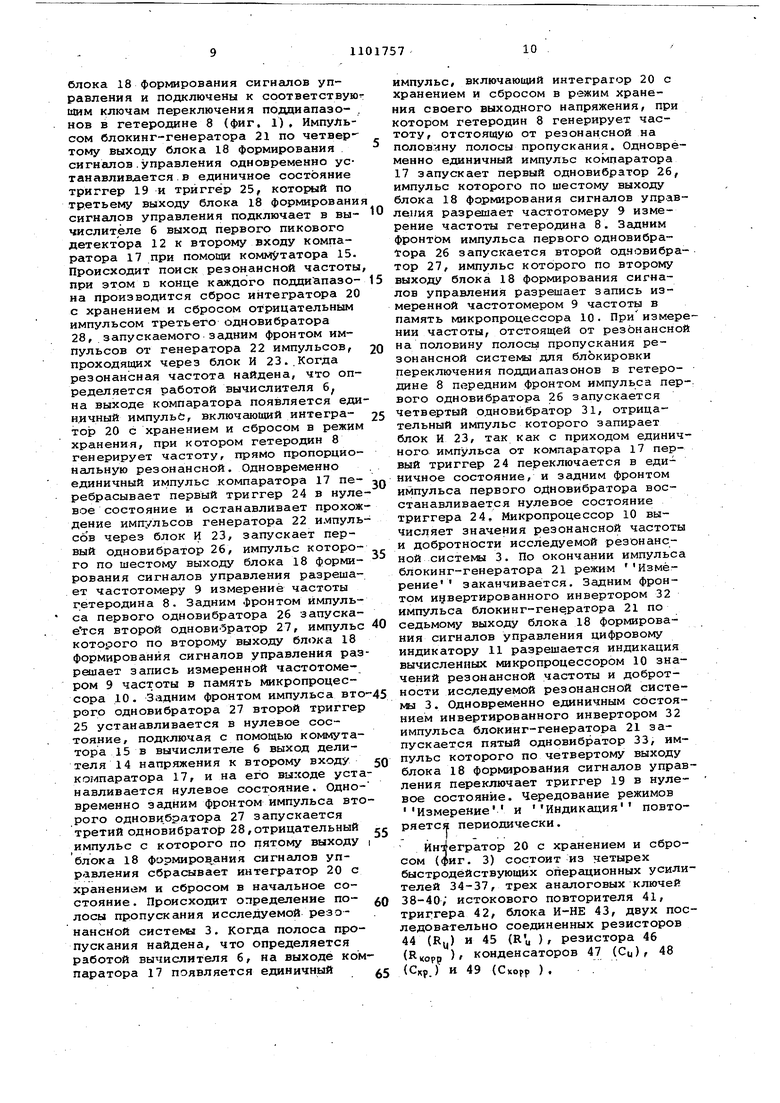

Блок 18 формирования сигналов управления (фиг. 2) состоит из задающего блокинг-генератора 21, генератора 22 импульсов, блока И 23, первого триггера 24, второго триггера 25, первого одновибратора 26, второго одновибратора 27, третьего одновиратора 28, счетчика 29, дешифратора 30, четвертого одновибратора 31, инвертора 32 и пятого одновибратора 33

Блок 18 формирования сигналов ра,ботает следующим образом.

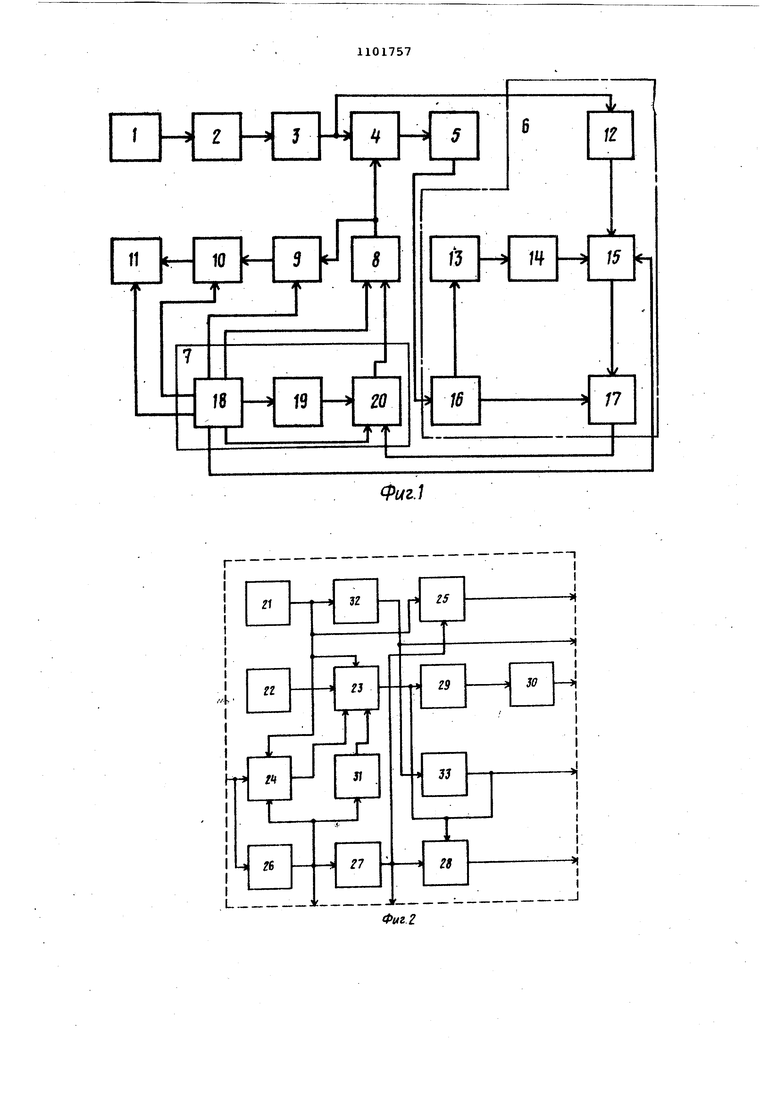

Задающий блокинг-генератор 21 вырабатывает импульсы, обеспечивающие работу цифрового измерителя добротности в режимах Измерение и Индикация. Импульс блокинггенератора ,21 устанавливает первый триггер 24 в единичное состояние, выходной импульс которого разрешает прохождение импульсов от генератора 22 импульсов через блок И 23 на счетчик 29 и дешифратор 30, выходы которого являются первым выходом блока 18 формирования сигналов управления и подключены к соответствую щим ключам переключения поддиапазонов в гетеродине 8 (фиг. 1), ИмпуЛьсом блокинг-генератора 21 по четвертому выходу блока 18 формирования сигналов.управления одновременно устанавливлется в единичное состояние триггер 19 и триггер 25, который по третьему выходу блока 18 формировани сигналов управления подключает в вычислителе б выход первого пикового детектора 12 к второму входу компаратора 17 при помощи коммутатора 15. Происходит поиск резонансной частоты при этом D конце каждого поддиапазона производится сброс интегратора 20 с хранением и сбросом отрицательным импульсом третьего одновибратора 28, запускаемого задним фронтом импульсов от генератора 22 импульсов, проходящих через блок И 23.,Когда резонансная частота найдена, что определяется работой вычислителя 6, на выходе компаратора появляется еди н.ичный импульй, включающий интегратор 20 с хранением и сбросом в режим хранения, при котором гетеродин 8 генерирует частоту, прямо пропорциональную резонансной. Одновременно единичный импульс компаратора 17 перебрасывает первый триггер 24 в нуле вое состояние и останавливает прохож дение имп:/льсов генератора 22 импуль сов через блок И 23, запускает первый одновибратор 26, импульс которого по шестому выходу блока 18 формирования сигналов управления разрешает частотомеру 9 измерение частоты гетеродина 8. Задним Фронтом импульса первого одновибратора 26 запускается второй одновибратор 27, импульс которого по второму выходу блока 18 формирования сигналов управления раз решает запись измеренной частотомером 9 частоты в память микропроцессора 10. Задним фронтом импульса вто рогр одновибратора 27 второй триггер 25 устанавливается в нулевое состояние, подключая с помощью коммутатора 15 в вычислителе 6 выход делителя 14 напряжения к второму входу компаратора 17, и на его выходе уста навливается нулевое состояние. Одновременно задним фронтом импульса вто рого однови.братора 27 запускается третий одновибратор 28,отрицательный импульс с которого по пятому выходу блока 18 формиров ания сигналов управления сбрасывает интегратор 20 с хранением и сбросом в начальное состояние . Происходит определение полосы пропускания исследуемой резонансной системы 3. Когда полоса пропускания найдена, что определяется работой вычислителя 6, на выходе компаратора 17 появляется единичный импульс, включающий интегратор 20 с хранением и сбросом в хранения своего выходного напряжения, при котором гетеродин 8 генерирует частоту, отстоящую от резонансной на половг ну полосы пропускания. Одновременно единичный импульс компаратора 17 запускает первый одновибратор 26, импульс которого по шестому выходу блока 18 формирования сигналов управления разрешает частотомеру 9 измерение частоты гетеродина В. Задним фронтом импульса первого одновибратора 26 запускается второй одновибратор 27, импульс которого по второму выходу блока 18 формирования сигналов управления разрешает запись измеренной частотомером 9 частоты в память микропроцессора 10. При измерении частоты, отстоящей от резонансной на половину полосы пропускания резонансной системы для блокировки переключения поддиапазонов в гетеродине 8 передним фронтом импульса пер-: вого одновибратора 26 запускается четвертый одновибратор 31, отрицательный импульс которого запирает блок И 23, так как с приходом единичного импульса от компаратора 17 первый триггер 24 переключается в единичное состояние, и задним фронтом импульса первого одновибратора восстанавливается нулевое состояние триггера 24, Микропроцессор 10 вычисляет значения резонансной частоты и добротности исследуемой резонансной системы 3. По окончании импульса блокинг-генератора 21 режим Измерение заканчивается. Задним фронтом инвертированного инвертором 32 импульса блокинг-генератора 21 по седьмому выходу блока 18 формирования сигналов управления цифровому индикатору 11 разрешается индикация вычисленных микропроцессором 10 значений резонансной частоты и добротности исследуемой резонансной системы 3 . Одновременно единичным состоянием инвертированного инвертором 32 импульса блокинг-генератора 21 запускается пятый одновибратор 33, импульс которого по четвертому выходу блока 18 формирования сигналов управления переключает триггер 19 в нулевое состояние. Чередование режимов Измерение и Индикация повторяется периодически. Интегратор 20 с хранением и сбросом {фиг. 3) состоит-из четырех быстродействующих операционных усилителей 34-37, трех аналоговых ключей 38-40; истокового повторителя 41, триггера 42, блока И-НЕ 43, двух поседовательно соединенных резисторов 44 (R) и 45 (Ru ), резистора 46 (RWPP )/ конденсаторов 47 (Сц), 48 (Схр.) и 49 (Схорр ) . . Интегратор 20 с хранением и сбросом работает следующим образом. .При замкнутом ключе 38, что соответствует нулевому состоянию.на его управляющем входе, подаваемом по первому входу интегратора 20 с хранением и сбросом от компаратора 17 вычислителя 6 (фиг. 1) и разомкнутом ключе 40, что соответствует единичному состоянию на его управляю щем входе, подаваемом по третьему входу интегратора 20 с хранением и сбросом от третьего одновибратора 28 блока 18 (фиг. 2), происходит интегрирование постоянного входного напряжения, поступающего от триггера 19 на второй вход интегратора 20 с хранением и сбросом по следующему закону; с постоянной времени Т R..-CU, так как ключ 3,9 замкнут, что соответству ет нулевому состоянию на выходе триг гера 42. На конденсаторе 48 напряжение следит за напряжением на конденсаторе 47 и в каждый момент времени точно ему равно. При поступлении е4}иничного состояния от компаратора 17 по первому входу интегратора 20 с хранениеми сбросом ключ 38 размыкается, и напряжение на выходе интегратора 20 с хранением и сбросом остается постоянным и равным напряже нию на конденсаторе, 48, так кгис нагрузкой конденсатора 48 является ис токовый повторитель 41. Блок хранит значение напряжения на конденсаторе 48, При замыкании обоих ключей 38 и 40, что определяется одновременной подачей нулевых состояний от компара тора 17 вычислительного блока 6 и третьего одновибратора 28 блока 18 происходит быстрый разряй конденсаторов 47 и 48 на малые выходные сопротивления операционных усилителей либо до нуля, либо до начального уровня, задаваемого на вход операци ного у си.лителя 37 через резистор 46 Интегратор готов к следующему интегр рованию входного напряжения. Резистор 46 и конденсатор 49 препятствуют самовозбуждению интегратора 20 с хранением и сбросом во время сброса вьйсодного напряжения. , Для повышения точности определения частоты, отстоящей от резонансн на половину полосы пропускания, интегратор 20 с хранением и сбросом можно дополнить переключателем постоянной интегрирования. В исходном состоянии триггер .42 находится в ну.левом состоянии и ключ 39 замкнут. При поиске резонансной частоты импульсы сброса, поступающие на первый вход блока И-НЕ 43, не переключают триггер 42, так как блок И-НЕ 43 заперт по второму входу единичным импульсом от второго триггера 25 блока 18.После измерения и записи в микропроцессор 10 резонансной частоты, второй триггер 25 блока 18 переключается в нулевое состояние, отрицательным импульсом от третьего одновибратора 28 блока 18 во время сброса интегратора 20 с хранением и сбросом для подготовки к поиску полосы пропускания через блок ИНЕ 43 по входу с триггера 42 переключается в единичное состояние, ключ 39 размыкается, и последовательно с резистором 44 подключается резистор 45, что увеличивает постоянную времени интегратора 20 с хранением и сбросом. По окончании режима Измерение импульсом от инвертора 32 блока 18, поступающим на R-вход триггера 42, происходит его переключение в нулевое состояние, ключ 39 замыкается и интегратор с хранением и сбросом готов к следующему циклу измерения. Использование предлагаемого цифрового измерителя добротности резонансной системы обеспечивает по сравнению с базовым образцом Е 9-5 повышение точности измерения, резонансной частоты и добротности с 10 до 0,2% за счет автоматизации процесса измерения и уменьшения, мeтo ичecкoй и инструментальной погрешности измерения, кроме того, су1цественно улучшает условия труда за счет уменьшения трудоемкости, повышает качество и надежность выпускаемой продукции за счет повышения точности и автоматизации процесса измерения. Экономический эффект от внедрения предлагаемого цифрового измерителя добротности образуется за счет сокращения трудоемкости, т.е. за счет уменьшения времени измерения добротности.

чч

r

uT

55

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель добротности | 1979 |

|

SU824077A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для автоматического измерения экстремальных частот пьезопреобразователей | 1980 |

|

SU940078A2 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-07-07—Публикация

1983-02-28—Подача