ный модулятор, первый переключатель ПАЛ/СЕКАМ и блок задержки, первый выход которого соединен с входом первого инвертора, а второй выход с первым входом первого сумматора и первым входом второго переключателя ПАЛ/СЕКАМ, а также третий переключатель ПАЛ/СЕКАМ, генератор опорного сигнала, первый выход которого соединен с первым входом первого синхронного детектора и с первым входом первого коммутатора, выход которого соединен с вторым входом амплитудного модулятора, а второй вход первого коммутатора с вторым выходом генератора опорного сигнала и с первым входом второго синхронного детектора, вход управления первого коммзпгатора является входом меандра полустрочной частоты, при этом второй вход первого переключателя ПАЛ/СЕКАМ объединен с входом корректора высокочастотных предыскажений и является входом декодера ПАЛ/СЕКАМ, а вход управления соединен с входами управления второго и третьего переключателе

ПАЛ/СЕКАМ, отличающийся тем, что, с целью уменьшения перекрестffi K искажений при приеме сигнал ла CEKAMj в него введены второй сумматор, второй инвертор и второй коммутатор, вход управления которого соединен с входом управления первого коммутатора, первый вход второго коммутатора соединен с первым выходом блока задержки, второй вход соединен с выходом первого инвертора, а выход - с первым входом второго сумматора, с первым входом третьего переключателя ПАЛ/СЕКАМ и через второй инвертор с вторым входом первого сумматора, выход которого соединен с вторым входом второго переключателя ПАЛ/СЕКАМ соединенного выходом с вторым входом первого синхронного детектора, причем второй вход второго сумматора соединен с вторым выходом блока задержки, а выход - с вторым входом третьегЪ переключателя ПАЛ/СЕКАМ выход которого соединен с вторь входом второго синхронного детектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Канал сигнала цветности декодера СЕКАМ | 1989 |

|

SU1653180A1 |

| Канал сигнала цветности декодера СЕКАМ (его варианты) | 1984 |

|

SU1248078A1 |

| Устройство разделения сигналов цветности и яркости | 1983 |

|

SU1172082A1 |

| Канал цветности многостандартного цветного телевизора | 1988 |

|

SU1619422A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА СТЕРЕОЦВЕТНОГО ТЕЛЕВИЗИОННОГО СИГНАЛА | 1990 |

|

RU2037977C1 |

| ЦИФРОВОЕ УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ЯРКОСТИ И ЦВЕТНОСТИ В ДЕКОДЕРЕ СИСТЕМЫ СЕКАМ | 1991 |

|

RU2013888C1 |

| СПОСОБ КОРРЕКЦИИ НЕЛИНЕЙНЫХ ПРЕДЫСКАЖЕНИЙ ЦВЕТОРАЗНОСТНЫХ СИГНАЛОВ СЕКАМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2206184C2 |

| УСТРОЙСТВО РАЗДЕЛЕНИЯ СИГНАЛОВ ЯРКОСТИ И ЦВЕТНОСТИ В ДЕКОДЕРЕ СИСТЕМЫ СЕКАМ | 1991 |

|

RU2014753C1 |

| Устройство для разделения сигналов яркости и цветности в декодере (его варианты) | 1984 |

|

SU1239895A1 |

| РАДИОЛИНИЯ СВЯЗИ С ПОВТОРНЫМ ИСПОЛЬЗОВАНИЕМ ЧАСТОТЫ | 2002 |

|

RU2233030C2 |

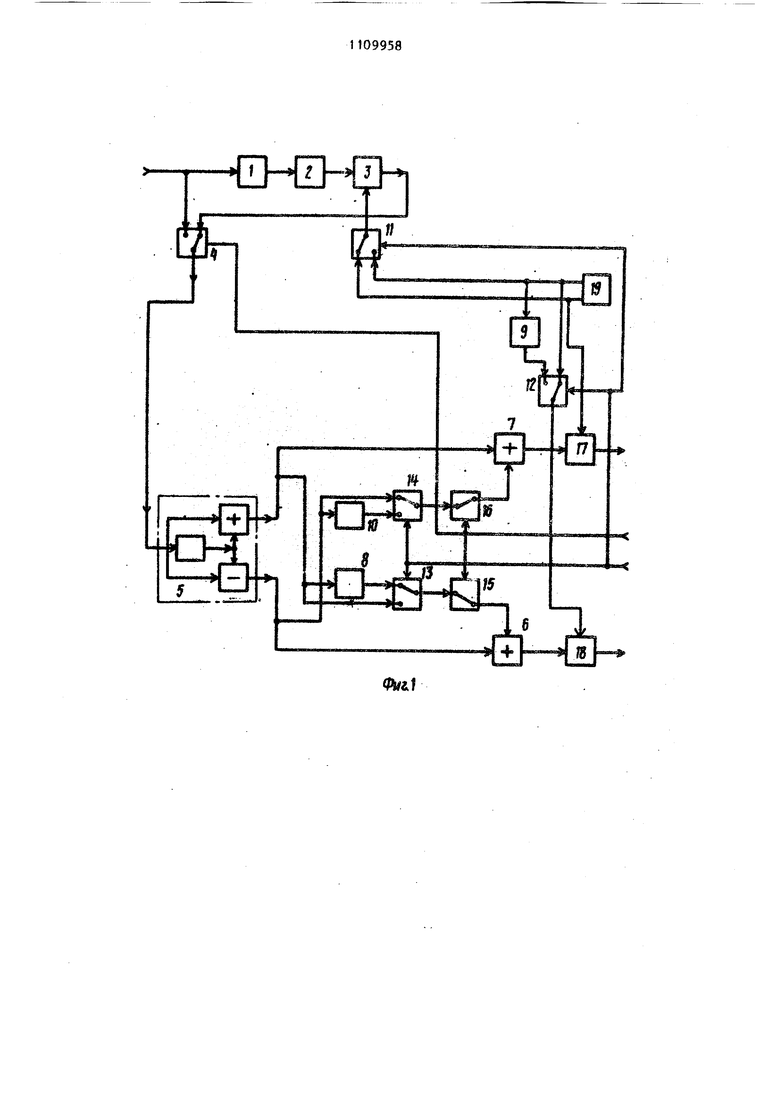

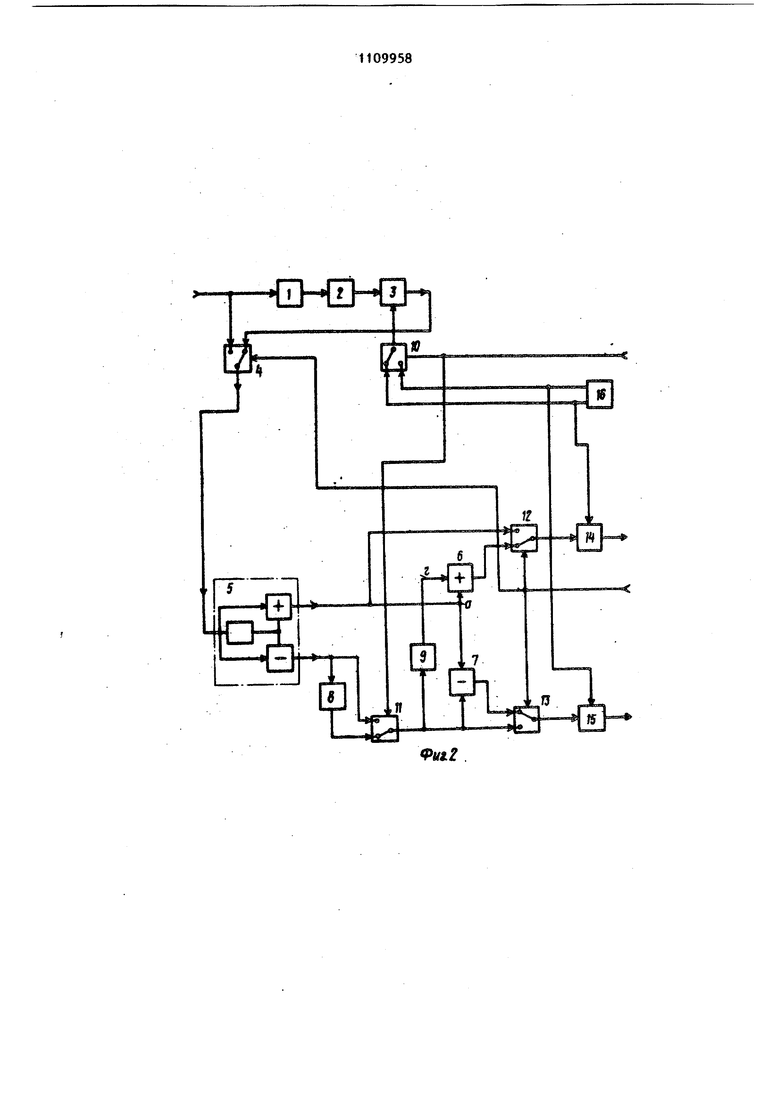

1. Декодер ПАЛ/СЕКАМ, содержащий последовательно соединенный корректор высокочастотных предыскажений, частотный детектор, амплитудный модулятор, первый переключатель ПАЛ/СЕКАМ и блок задержки, первый выход которого соединен с входом первого инвертора, а второй выход - с первым входом первого сумматора, а также второй и третий переключатели ПАЛ/СЕКАМ, генератор опорного сигнала, первый выход которого соединен с первым входом первого синхронного детектора и с первым входом первого коммутатора $ выход которого соединен с вторым входом амплитудного модулятора, второй выход генератора опорного сигнала соединен с вторым входом первого коммутатора, с первым входом второго коммутатора и с вторым входом второго коммутатора через второй инвертор, выход второго коммутатора соединен с первым входом второго синхронного детектора, при этом входы управления первого и второго коммутаторов являются входами меандра полустрочной частоты, второй вход первого переключателя ПАЛ/СЕКАМ объединен. с входом корректора высокочастотных предыскажений И является входом декодера ПАЛ/СЕКАМ, а вход згаравления соединен с входами управления второго и третьего перекл очателей ПАЛ/СЕКАМ, отличающийся тем, что, с целью уменьшения перекрестных искажений при приеме сигнала СЕКАМ, в него введены третий инвертор, второй cyi-iматорз третий и четвертый торы, причем первый выход блока задержки соединен с первым входом второго сумматора и с первым входом третьего коммутатора, второй вход которого соединен с выходом первого инвертора, а выход - с входом второ го переключателя ПАЛ/СЕКАМ, первый выход которого соединен с вторым входом первого сумматора, выход которого соединен с вторьм входом второго синхронного детектора, второй выход блока задержки соединен с первым входом четвертого коммутатора непосредственно и с вторым О входом четвертого коммутатора через х третий инвертор, а выход четвертого коммутатора соединен с входом ел 00 третьего переключателя ПАЛ/СЕКАМ, первый выход которого соединен с вторым входом второго сумматора, выход которого соединен с вторым входом первого синхронного детектора,, при этом входы управления третьего и четвертого коммутаторов соединены с входом управления первого коммутатора. 2. Декодер ПАЛ/СЕКАМ, содержа1ДИЙ последовательно соединенные корректор высокочастотных предыскажениЙ5 частотный детектор, амплитуд

Изобретение относится к технике цветного телевидения, в частности к двухстандартным цветным телевизорам и видеоконтрольньм устройстваМо ,

Известен декодер ПАЛ/СЕКАМ, который содержит последовательно соединенные корректор высокочастотных предыскажений, частотный детектор, балансный амплитудный модулятор, блок задержки, генератор опорного сигнала и два синхронных детектоРа 1.

В данном декодере велики фазовые,перекрестные искажения в режиме СЕКАМ, которые обусловлены наличием на входах синхронных детекторов двух неразделенных компонент сигнала цветности.

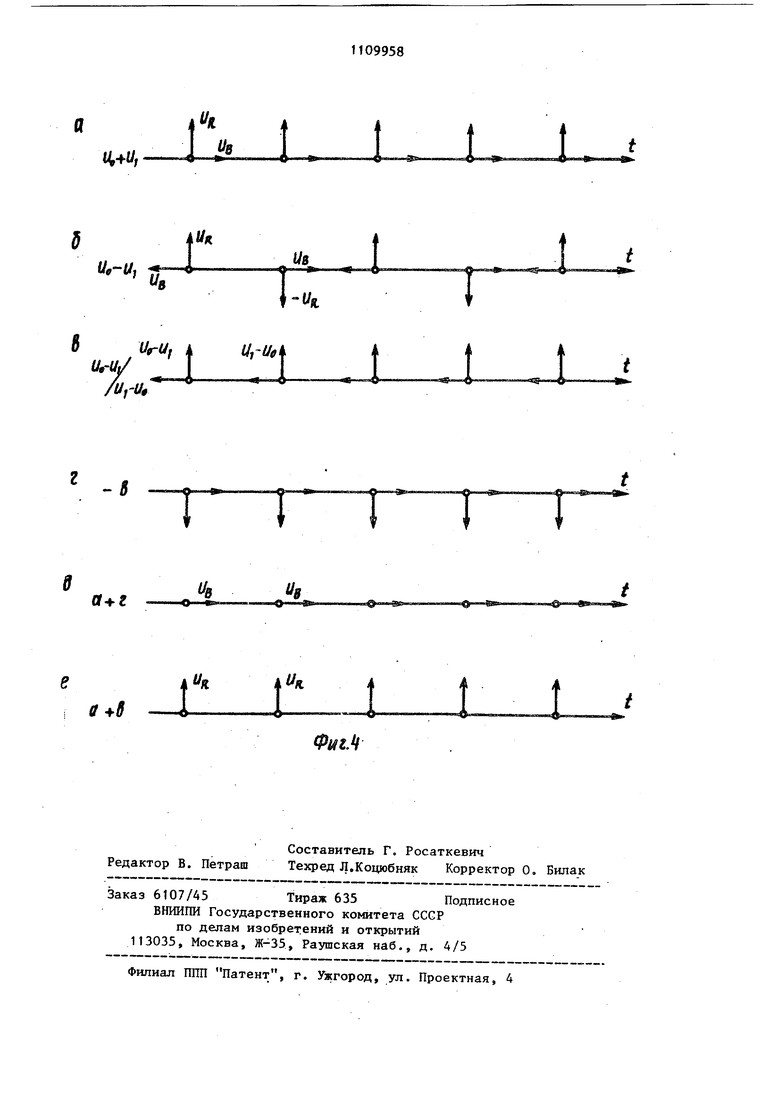

Наиболее близким по технической сущности к предлагаемому является декодер ПАЛ/СЕКАМ, содержащий после довательно соединенные корректор высокочастотных предыскажений, частотный детектор, амплитудный детектор, первый переключатель ПАЛ/СЕКАМ блок задержки, два выхода которого соединены через второй и третий переключатель ПАЛ/СЕКАМ соответственно с первыми входами первого и/ второго синхронных детекторов, вторые входы которых через первый и второй коммутаторы соединены с выгодами генератора опорного сигнала, лричем первый выход блока задержки соединен с первым входом первого сумматора, а второй выход соединен с вторьм входом первого сумматора через инвертор, при этом выход первого сумматора соединен через третий коммутатор с вторыми входами второго и третьего переключателей ПАЛ/СЕКАМ, входы управления кото1илх соединеш с входами управления первого переключателя ПАЛ/СЕКАМ, кроме того, первый илход генератора опорного сигнала соединен с вторым входом амплитудного модулятора непосредiственно и с вторым входом первого коммутатора через второй инвертор С 2 }. Однако паразитные связи в коммутаторе -и других узлах устройства вы зьюаЬт взаимное наложение двух компонент сигналов цветности. Поскольку обе компоненты синфазны, такое наложение вызывает амплитудные перекрестные искажения, нарушающие цветопередачу. Цель изобретения - уменьшение фазовых и амплитудных перекрестных искажений при приеме сигнала СЕКАМ Для достижения поставленной цели в декодер ПАЛ/СЕКАМ, содержащий пос ледовательно соединенные корректор высокочастотных предыскажений, частотный детектор, амплитудный модулятор, первый переключатель ПАЛ/СЕКАМ и блок задержки, первый выход которого соединен с входом первого инвертора, а второй выход с первьм входом первого сумматора, а также второй и третий переключатели ПАЛ/СЕКАМ, генератор опорного сигнала, первый выход которого cdeдинен с первым входом первого синхронного детектора и с первым входом первого KOMNryTaTopa, выход которого соединен с вторым входом амплитудного модулятора, второй выход генератора опорного сигнала соединен с вторым входом первого коммутатора, с первым входом второго коммутатора и с вторым входом второго коммутатора через второй инвертор, выход второго коммутатора соединен с первым входом второго синхронного детектора, при этом входы управления первого и второго коммутаторов являются входами меанд ра полустрочной частоты, второй вход первого переключателя ПАЛ/СЕКА объединен с входом корректора высокочастотных предыскажений и является входом декодера ПАЛ/СЕКАМ, а вход управления соединен с входами управления второго и третьего переключателей ПАЛ/СЕКАМ, введены третий инвертор, второй сумматор, третий и четвертый коммутаторы, причем первый выход блока задержки соединен с первым входом второго сумматора и с первым входом третьего коммутатора, второй вход которого соединен с выходом первого инвер тора , а выход - с входом второго переключателя ПАЛ/СЕКАМ, первый 584 выход которого соединен с вторым входом первого сумматора, вькод которого соединен с вторым входом второго синхронного детектора, второй выход блока задержки соединен с первым входом четвертого коммутатора непосредственно и с вторым входом четвертого коммутатора через третий инвертор, а выход четврртого коммутатора соединен с входом третьего переключателя ПАЛ/СЕКАМ, первый выход которого соединен с вторым входом второго сумматора, выход которого соединен с вторым входом первого синхронного детектора, при этом входы управления третьего и четвертого коммутаторов соединены с входом управления первого коммутатора. Согласно второму варианту в декодер ПАЛ/СЕКАМ, содержащий последовательно соединенные корректор высокочастотных предыскажений, частотный детектор, амплитудный модулятор, первый переключатель / ПАЛ/СЕКАМ и блок задержки, первый выход которого соединен с входом первого инвертора, а второй выход с первым входом первого сумматора и первым входом второго переключателя ПАЛ/СЕКАМ, а также третий переключатель ПАЛ/СЕКАМ, генератор опорного сигнала, первый выход которого соединен с первым входом первого синхронного детектора и с первым входом первого коммутатора, выход которого соединен с вторым входом амплитудного модулятора, а второй вход первого коммутатора с вторым выходом генератора опорной частоты и с первым входом второго синхронного детектора, вход управления первого коммутатора является входом меандра полустрочной частоты, при этом второй вход первого переключателя ПАЛ/СЕКАМ объединен с входом корректора высокочастотных предыскажений и является входом декодера ПАЛ/СЕКАМ, а вход управления соединен с входами управления второго и третьего переключателей ПАЛ/CEKAMj введены второй сумматор, второй инвертор и второй коммутатор, вход управления которого соединен с входом управления первого коммутатора, первый вход второго коммутатора соединен с первым выходом блока задержки, второй вход соединен с выходом первого инвертора, a выход - с первым входом второго сумматора, с первым входом третьего переключателя ПАЛ/СЕКАМ и через второй инвертор с вторым входом первого сумматора, выход которого соединен с вторым входом второго переключателя ПАЛ/СЕКАМ, соединенного выходом с вторым входом первого синхронного детектораJ причем второй вход второго сумматора соединен с вторым выходом блока задержки, а выход с вторым входом третьего переключателя ПАЛ/СЕКАМ, выход которого соединен с вторым входом второго синхронного детектора, На фиг. 1 и 2 представлены струк турные электрические схемы двух вариантов декодера ПАЛ/СЕКАМ, на фиг. 3 и 4 - эпюры сигналов, по ясняющие работу декодеров ПАП/СЕКЛ Декодер ПАЛ/СЕКАМ согласно первому варианту (фиг. 1) содержит корректор 1 высокочастотных предыс кажений, частотный детектор 2, амплитудный модулятор 3, первый .ti ер включат ель ПАЛ/СЕКАМ 4, блок 5 задержки, первый сумматор 6, вто рой сумматор 7, первый, вто|5ой и т тий инверторы 8-tO, первый, второй третий и четвертый коммутаторы 11второй и третий переключатели IbLH/CEKAM 15 и 16, первый и второй синхронные детекторы 17 и 18, гене ратор 19 опорного сигнала. Устройство работает следующим образом. При приеме сигнала ПАЛ переключ 4, 15.и тели 4, 15-И 16 находятся в положении П. При этом принятый сигна проходит блок 5 задержки, который разделяет компоненты U,g и Uo и через сумматоры 6 и 7 поступает на синхронные детекторы 17 и 18, где сравнивается с опорным сигналом от генератора 19 и демодулируется известным способом. При приеме сигнала СЕКАМ расгюз 41аватель систем (не показан) переводит переключатели 4, 15 и 16 в положение С. Принятый сигнал про ходит корректор 1 высокочастотных предыскажений и поступает на вход частотного детектора 2, где обеспечиваются амплитудное ограничение поднесущей, частотная демодуляция, вьфавнивание уровней черного в пос ледовательно чередующихся составляющих Е. и Е и коррекция йизкочастотных предыскажений. Демодулированный сигнал СЕКАН поступает на первый вход амплитудного модулятора 3 балансного типа. На его второй вход через первый коммутатор 11, yпpaвляe вJ й меандром полустрочной частоты от блока цветовой синхронизации (не показан)j поступают, опорные поднесущие с двух выходов генератора 19. На первом выходе фаза по опорной поднесущей равна нулю, угол 90. а на втором сдвинута Поэтому составляющие U на выходе амплитудного модулятора 3 имеют угол 90, а составляющие Ug 0° (фиг. За). Этот сигнал (Ug) через первый переключатель 4 поступает на блок 5 задержки. На выходе линии задержки блока 5 вьщеляется сдвинутая на строку последовательность сигналов и (фиг. 35). , На выходах блока 5 задержки выделяются сумма и разность прямого и задержанного сигналов (фиг, Зв и г). Эти сигналы поступают на первые входы сумматоров 6 и 7, На выходах первого и третьего инверторов 8 и 10 последовательности (фиг. Зб иг) получают фазовый сдвиг 180® (фиг. ЗЭ и е). Благодаря действию четвертого коммутатора 14 на второй вход втсоого сумматора 7 поочередно, через строку подаются компоненты е и г (фиг. 3 ж). В резулЬ тате на его выходе выделяется сигнал 8+ ж (фиг. Зи), который сьдержит только компоненту Ug с фазовым углом О. Аналогично на второй вход первого сумматора 6 поступают поочередно сигналы ей Э (фиг. Зз), а на выходе этого сумматора вьщеляется сигнал t э , представляющий собою компоненты Ug с чередующейся фазой 90 и 270° (фиг. ). Сигналы фиг, 3,м ил, поступающие на входы первого и второго синхронных детекторов 17 и 18, по виду ничем не отличаются от сигналов, поступакнцих на эти входы в режиме ПАЛ. Компоненты U-H Ug полностью разделены и ортогональны. От генератора 19.на первый синхронный детектор 17 подается опорный сигнал с постоянной фазой О. Фаза опорного сигнала, подаваемого на второй синхронный детектор 18, имеет благодаря действию второго коммутатора 12 и второго инвертора 9 чередующиеся значения 90 и 270 Поэтому демодулируемые и опорные сигналы оказьшаются синфазными. В резульфате на выходах первого и второго синхронных детекторов 17 и 18 вьщеляются сигналы Eg-y и постоянной фазой. Ортогонал ность демодулируемых сигналов на входах синхронньпс детекторов обеспечивает нечувствительность устрой ства к паразитным связям в его узлах (проекция одного сигнала на другой обращается в точку), Вместе с тем устройство мало чувствительн и к фазовым погрешностям опорных сигналов. В самом деле, поскольку компоненты U(j и Ug на входах синхр ных детекторов полностью разделены поворот фазы опорного сигнала на угол не вызьшает перекрестных и кажений, а лишь приводит к незначительному уменьшению амплитуды выходного сигнала в cos йЧ, раз, Второй вариант предлагаемого ус ройства рассчитан на использование декодера ПАЛ, в котором опорный сигнал на синхронный детектор R подается с постоянной фазой 90, но меняется фаза сигнала, поступаю щего на синхронный детектор R - У от блока задержки (такой принцип используется, в частности в микросхемах ТСА 640 и тел 650), Декодео ПАЛ/СЕКАМ согласно второму варианту (фиг. 2) содержит корректор t высокочастотных предыскажений, частотный детектор 2 с цепями амплитудного ограничения, демодуляции сигнала, выравнивания уровня черно го и коррекции низкочастотных пред ыскажений, амплитудный модулятор 3, первый переключатель ПАЛ/СЕКАМ блок 5 задержки, первый и второй сумматоры 6 и 7, первый и второй и верторы 8 и 9, первый и второй ком мутаторы to и 11, второй и третий переключатели ПАЛ/СЕКАМ 12 и 13, первый и второй синхронные детекторы 14 и 15 и генератор . 16 опорно го сигнала. Устройство работает следующим образом. В режиме ПАЛ переключатели 4, 12 и 13 находятся в положении П. Сигнал ПАЛ проходит блок 5 задерж8ки, обеспечивающий разделение компонент Ug и и 5 и поступает на первый синхронный детектор 14 непосредственно, а на второй синхронный ; детектор 15 через второй коммутатор 11, который с помощью первого инвертора 8 на каждой второй троке меняет фазу сигнала на 180. Поэтому компонента U на входе синхронного детектора 15 имеет одинаковую фазу 90 на всех строках, что обеспечивает ее демодуляцию опорным сигналом от генератора 16, также имекяцим фазовый сдвиг 90. Компонента Ug, имеющая фазовый сдвиг О, демодупируется синхронным детектором 14, на который поступает опорная поднесущая с фазовым углом О. В режиме СЕКАМ переключатели 4, 12 и 13 переводятся в положение С На выходах блока 5 задержки, как и в первом варианте устройства, выделяются сигналы Ug + и., и Up- и (фиг. 4о и Б). После второго коммутатора 11 получается чередующаяся последовательность Up- Ц j U,; Up- U и.т.д. (фиг. 4 в). На выходе второго инвертора 9 эта последовательность меняет знак (фиг. 4г), и на выходе первого сумматора 6 полз ается сигнал а+г (фиг. 43 ), а на выходе второго сзгмматора 7 а + в (фиг. 4 и ). В этом варианте устройства на входы синхронных детекторов также поступают разделенные ортогональные компоненты и„ и U,j. Отличие состоит в том, что компонента Up не меняет знак, так как на второй синхронный детектор поступает опорный -сигнал от генератора 16 с постоянной фазой 90°, а на всех строках демодулированный сигнал Е получается положительным. Оба варианта устройства обеспеивают полное разделение и ортогональность компонент и,, и U, ваемых на входы синхронных детекторов. Поэтому наличие паразитных вязей в цепях между блоком задержи и синхронными детекторами, в отичие от прототипа, не вызывает J мплитудных перекрест 1ьгх; искажений (взаимные проекции ортогональных екторов равны нулю). При этом редлагаемое устройство малочувстительно к фазовым искажениям. HZH Ib

tk

У. 0-1

8

n

t-tf«

r

t-tt.

.J Г It (4.ц -J Ц-.

i(/,

(/n

Wir(/, Ai/,-,AA %- 2 « - 09 --0 a Q 3

6tUg

Д.го ... Г г ,.l .

. tt i , i,..s. 8. AA -i--i J Q eg-- -««- -9 1 11 I II/

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент Великобритании № 1358551, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Funkschau, 1981, № 16, с | |||

| Приспособление для соединения пучка кисти с трубкою или втулкою, служащей для прикрепления ручки | 1915 |

|

SU66A1 |

Авторы

Даты

1984-08-23—Публикация

1982-06-21—Подача