Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах для формирования символов, например, на экране электронно-лучевой трубки (ЭЛТ). Известно устройство для отображения информации, содержащее генератор импульсов, формирователь импульсов, блок памяти, .счетчик адреса, логичес кий блок, преобразователь код время, регистр микрокоманд, генератор функциональных напряжений, блок подсвета луча Си . В данном устройстве время формирования символа определяется по формулеTC- -t-i где m - количество единичных отрезков (векторов), входящих в контур отображаемого символапериод тактовых импульсов, равный минимальному времени выборки числа из блока памяти. Величина гп выбирается конкретно для каждого символа, исходя из требований к его конфигурации и различимости на экране ЭЛТ, поэтому не может изменяться в больших пределах без ухудшения качества, Единиственным путем увеличения быстродействия устройства является повышение тактовой частоту, т.е. уменьшение величины t , .что требует применение быстро действующих блоков памяти. Однако такие блоки потребляют большую мощность, требуют применения дорогостоящих блоков питания, что в конечном итоге приводит к увеличению стоимости, усложнению конструкции из-за необходимости отвода тепла от электрорадиоэлементов и снижению надежности устройства. Следовательно, основным недостатком данного устройства является зависимость быстродействия всего устройства от быстродействия примененных блоков памяти. Известно также устройство для отображения информации, содержащее Генератор импульсов, логический блок счетчик адреса, блок памяти, преобра зователь код - время, регистр микрокоманд, генератор функциональных напряжений, блок подсвета, управляемый делитель частоты, триггер 2, Однако такое устройство позволяет увеличить быстродействие в два раза только в том случае, когда в .фигуре формируемых символов отсутст-. вуют векторы единично. длины. Недостатком известного устройства является невозможность повышения его быстродействия при формировании символов, содержащих векторы единичной длины. Наиболее близким по технической сущности к предлагаемому является устройство для отображения информации, содержащее две группы элементов И, одни информационные входы которых являются соответственно информационными входами устройства, а другие- - подключены к выходу первого блока памяти, управляющие.входы - к. первому выходу синхронизатора, а.выходы - к входим элементов ИЛИ группы, В1ДХОДЫ которых соединены с первым входом первого счетчика, второй вход которого подключен к второму выходу синхронизатора, другие выходы которого соединены с первым входом генератора развертки, входами сброса генератора импульсов и преобразователя код - время, синхровходами первого и второго блоков Пс1мяти и преобразователя код - время, а входы - с выходами генератора импульсов и преобразователя код - время, выход которого соединен с первым входом регистра, выход первого счетчика соединен с адресным входом первого блока памяти, выходы регистра подключены к генератору развертки и блоку подсвета, второй блок памяти соединен с преобразователем код - время и регистром, второй счетчик, который соединен с синхронизатором, преобразователем код - время, первым и вторым блоками памяти, элемент И, соединенный с преобразователем код - время, вторым блоком памяти, синхронизатором и первым и вторым счетчиками 3. Недостатком данного устройства является также ограниченное быстродействие, обусловленное конечным быстродействием переменных блоков памяти. Так, например, время формирования символа будет пропорционально числу единичных отрезков, входящих в контур символа. Время формирования символа может быть сокращено только за счет уменьшения величины m , т,е, за счет уменьшения числа отрезков (векторов), которыми аппроксимируется контур формируемого символа. Однако такой путь повышения быстродействия приводит к снижению качества отображаемых символов, ухудшению их различимости, а в случае отображения специальньох символов упрощение их конфигурации вообще недопустимо,« Цель изобретения - повышение быстродействия устройства, Поставленная цель достигается тем, что в устройство, содержащее блок элементов 2И-ИЛИ, первый вход которого является первым входом устройства, второй вход подключен к первому выходу синхронизатора, третий вход - к выходу первого блока

памяти, вход которого соединен с выходом счетчика, первый вход которог подключен к выходу блока элементов 2И-Ш1И, делитель частоты, первый вход которого и первые входы синхронизатора, элемента И и регистра подключены к выходу, преобразователя код - время, первый вход которого соединен с вторым вьгходом синхронизатора, третий выход которого являеся первым выходом устройства и подключен к вторым входам делителя частоты и преобразователя код - время и к первому.входу.генератора импульсов, второй вход которого.является вторым входом устройства, а выход соединен с вторым входом синхронизатора, четвертый выход которого связан с первым входом генератора развертки, выходы которого являются вторым и третьим выходами устройства, второй вход генератора развертк подключен к первому выходу регистра второй выход которого соединен с блоком подсвета, выход которого являе.тся четвертым выходом устройства второй блок памяти, введен коммутатор, выход которого подключен к второму входу регистра и третьим входам синхронизатора и преобразователя код - время, первый вход коммутатора соединен с выходом первого блока памяти, второй вход - с вторым выходом делителя частоты, выход которого подключен к второму входу элемента .И, выход которого соединен с вторым входом счетчика, выход которого связан с входом второго блока памяти, выход которого со.единен с третьим входом коммутатора.

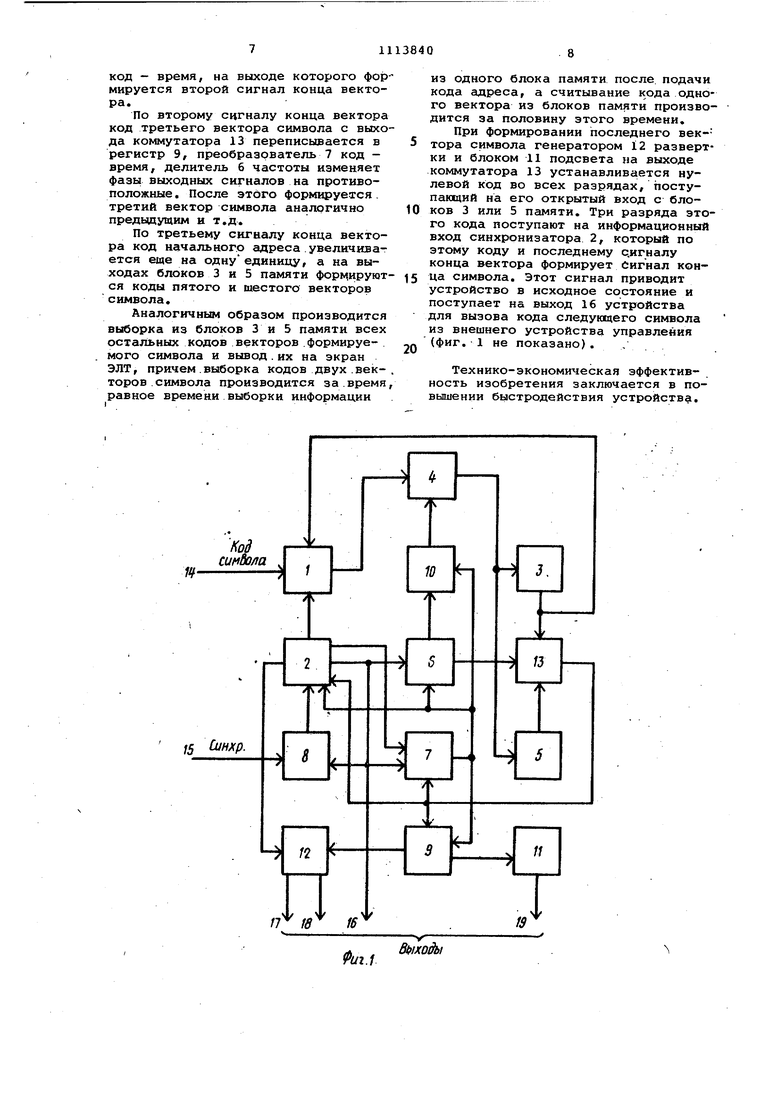

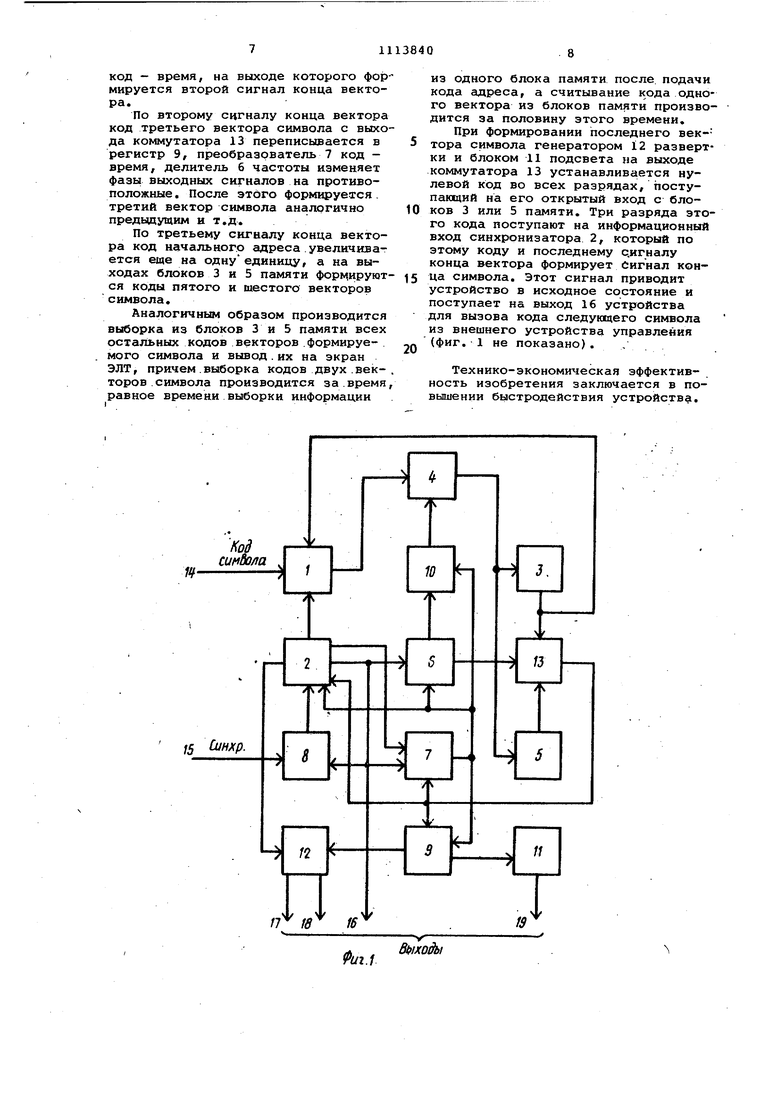

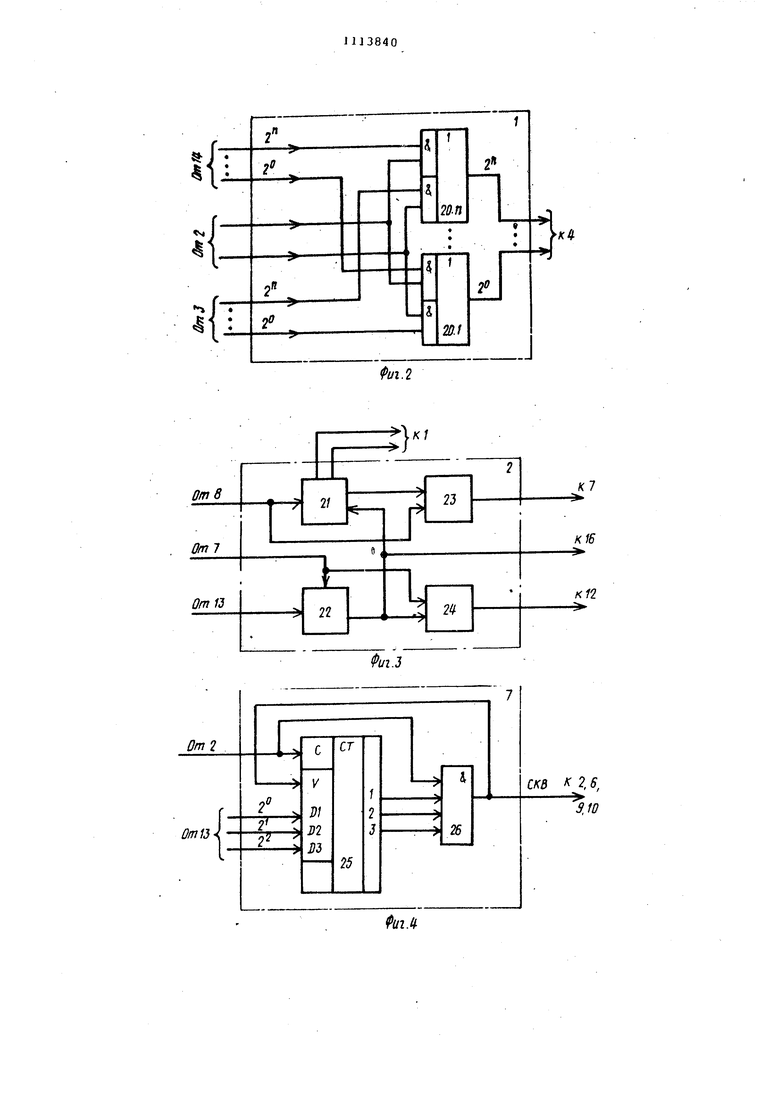

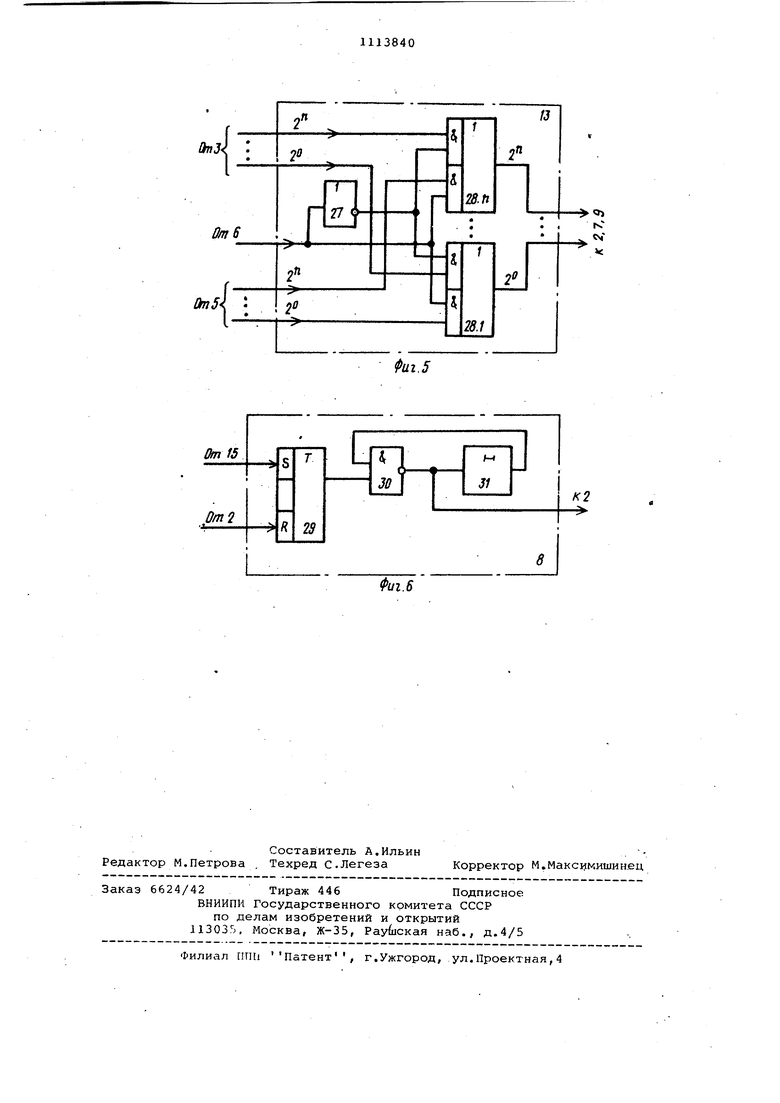

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока элементов 2И-ИЛИ на фиг. 3 - структурная схема синхронизатора; на фиг. 4 - структурная схема преобразователя код - время; на фиг. 5 - структурная схема коммутатора; на фиг. 6 - структурная схема генератора импульсов.

Устройство содержит блок 1 элементов 2И-ИЛИ, синхронизатор 2, первый блок 3 памяти, счетчик 4, второй блок .5 памяти, делитель 6 частоты, преобразователь 7 код - время, генератор 8 импульсов, регистр 9, элемент 10 И, блок 11 подсвета, генератор 12 развертки, коммутатор 13 .Позициями 14-19 обозначены входы и выходы устройства.

Блок 1 содержит элементы 2И-ИЛИ, Синхронизатор 2 содержит формирователь 21 импульсов, формирователь 22 сброса, блок 23 выделения тактовых импульсов, триггер 24. Преобразователь 7 код - время содержит вычитающий счетчик 25 и элемент 26 И, коммутатор Ij - элемент 27 НЕ и элементы ;..-ИЛИ, а

генератор 8 импульсов - триггер 29, элемент 30 И-НЕ и элемент 31 задержки.

Устройство работает следуккцим образом.

Код симв.ола с входа 14 устройства поступает на первый информационный вход блока 1 элементов 2И-ИЛИ. На вход 15 устройства поступает импульс синхронизации, которым запускается стартстопный генератор 8 импульсов. С выхода генератора В последовательность тактовых импульсов поступает на первый вход синхронизатора 2, который на первом выходе формирует сигнал разрешения на прохождение: кода символа через .блок 1 элементов 2И-ИЛИ в счетчик 4 адреса

Код символа записывается в счетчик 4 и с его выхода поступает на . адресные входы блоков 3 и 5.памяти. По коду адреса, соответствующему входному коду символа, на выходе блока 3 памяти формируется код начального (промежуточного) адреса-миропрограммы символа, который хранится в выходном .регистре блока 3 памяти (на фиг. 1 не показан).

Микропрограмма символа состоит из кода начального адреса, кодов векторов символа и кода конца символа. Каждому входному коду символа соответствует свой код начального адреса, который является адресом дл выборки кодов векторов формируемого символаиз блоков 3 и 5 памяти.

Микропрограмма символа записывается в блоки 3 -и 5 памяти следующим образом.

Коды начальных адресов всех формируемых символов записываются в информационные ячейки блока 3 памяти с первого по N -и адрес, где N число формируемых символов, образуя первый информационный массив. Начиная с N -fl-й ячейки в блоках 3 и 5 памяти размещаются коды векторов символов, образуя второй информационный массив. Коды нечетных векторо символа размещаются в блоке 3 памяти, а четных - в блоке 5 памяти по одним и тем же адресам.

Код конца символа записывается в виде нулей во всех разрядах после последнего вектора формируемого символа в блоке 3 или 5 памяти в зависимости от длины слова, занимающего микропрограммой символа. Так, например, если последний вектор формируемого символа является нечетным то код конца этого символа записывается в блоке 5 памяти и наоборот.

Каждый .вектор символа занимает одну И -разрядную информационную ячейку во BTORpM массиве. Необходимое число ячеек для записи микропрограммы одного символа зависит от числа векторов, образующих его фигуру, т.е. от конфигурации символа. Каждая пара векторов одного символа расположенная в двух блоках памяти, смещена по адресу на единиду относительно друг друга. . .

Код начального адреса в первом информационном массиве блока 3 памяти является адресом для выборки кхздов первых двух векторов символа из .второго массива блоков 3 и 5 памяти. Выборка всех последующих пар векторов формируемого символа производится увеличением кода начального адреса на единицу.

По коду начального адреса с вы-. хода счетчика 4 адреса на выходе блоков 3 и 5 памяти формируются код первого и второго векторов формируемого символа, которые имеют следуютую информационную структуру: 6 разрядов предназначены для управления разверткой вектора по координатам X и V ; 3 разряда - для задания длины вектора и один разряд - для формирования сигнала подсвета вектора на экране ЭЛТ.

С выходов блоков 3 и 5 памяти коды первого и второго векторов символа поступают на первый и второй входы коммутатора 13 соответственно, В исходном состоянии на управляющий вход коммутатора 13 поступает нулево уровень с выхода делителя 6 частоты. Этим уровнем коммутатор 13 открыт по первому входу и закрыт по второму.

Через о гкрытый первый вход код первого символа с выхода блока 3 памяти поступает на выход коммутатора 13. Код второго вектора символа хранится в выходном регистре блока 5 па мяти (на фиг. 1 не показан) и заблокирован на втором информационном входе коммутатора 13.

После выборки кодов двух векторов из блоков 3 и 5 памяти на синхровход прес1бразователя 7 код - время начинают поступать тактовые импульсы с третьего выхода синхронизатора 2, а на его информационный вход поступает 3-разрядный код длины первого вектора символа с выхода коммутатора 13.

При поступлении тактовых импульсов преобразователь 7 код - время формирует сигнал ввода, совпадающий по времени с первым импульсом поступившей пачки.

По сигналу ввода код длины вектора вводится в преобразователь 7 кодвремя, а код развертки и подсвета вектора - в регистр 9.

По этому же сигналу синхронизатор 2 формирует на четвертом выходе сигнал разрешения рабЬты генератора 12 развертки символа, а на первом выходе делителя б устанавливается

ёд иничный уровень. Этим уровнем коммутатор 13 закрьюается по первому входу и открывается по второму, и код второго вектора символа с блока

5памяти поступает на выход коммутатора 13.

После згшиси кода первого вектора в регистр 9 генератор 12 развертки символа формирует функциональные напряжения развертки первого вектора по координатам К и У , блок 11 . подсвета определяет необходимость подсвета или эвтемнения вектора на экране ЭЛТ, а преобразователь 7 кодвремя задает длину формируемого

вектора пропорционально поступившему коду.

Выходным сигналом преобразователя 7 код.- время.является.сигнал конца вектора. Каждый вектор формируемого символа состоит из т. единичных векторов. Время формирования едничного вектора равно периоду тактовых импульсов.

После окончания формирования первого вектора символа на входе преобразователя 7 код - время формируется сигнал с временным интервалом, пропорциональным периоду тактовых импульсов на синхровходе и весу 3-раэрядного кода на информационном входе. Этим сигналом код второг вектора символа с выхода коммутатора 13 вводится в преобразователь 7 код - время и регистр 9, а делитель

6снова переключается в нулевое состояние.

На двух выходах делителей 6 формируются строб-импульсы противоположной фазы. Длительность этих импульсов равна временному положению сигналов конца вектора. Сигналы конца вектора и положительные стробимпульсы с второго выхода делителя 6 поступают на первый и второй входы элемента 10 И соответственно. На выходе элемента 10 И выделяется первый и каждый нечетный сигналы конца вектора, которые поступают на счетный вход счетчика 4 и увеличивают на единицу записанный в нем код начального адреса.

По измененному коду начального адреса на выходах блоков 3 и 5 памяти формируются коды третьего и четвертого векторов символа соответственно.

f.

-Отрицательный строб-импульс с первого выхода делителя 6 частоты открывает коммутатор 13 по первому I входу и блокирует его по второму входу. Код третьего вектора символа поступает на выход коммутатора 13

Код второго символа аналогично коду первого вектора управляет работой генератора 12 развертки, блока 11 подсвета и преобразователя 7

код - время, на выходе которого формируется второй сигнал конца вектора.

По второму сигналу конца вектора код третьего вектора символа с выхода коммутатора 13 переписывается в регистр 9, преобразователь 7 код время, делитель б частоты изменяет фазы выходных сигналов на противоположные. После этого формируется, третий вектор символа аналогично предьщущим и т.д.

По третьему сигналу конца вектора код начального адреса увеличивается еще на однуединицу, а на выходах блоков 3 и 5 памяти формируются коды пятого и шестого векторов символа.

Аналогичным образом производится выборка из блоков 3 и 5 памяти всех остальных кодов векторов.формируемого символа и вывод. их на экран ЭЛТ, причем.выборка кодов двух .векторов символа производится за.время равное времени выборки информации

из одного блока памяти после, подачи кода адреса, а считывание кода одного вектора из блоков памяти производится за половину этого времени.

При формировании последнего век- 5 тора символа генератором 12 развертки и блоком 11 подсвета на выходе коммутатора 13 устанавливается нулевой код во всех разрядах, поступакщий на его открытый вход с бло0 ков 3 или 5 памяти. Три разряда этого кода поступают на информационный вход синхронизатора 2, который по этому коду и последнему с.игналу конца вектора формирует Сигнал кон5 Ца символа. Этот сигнал приводит устройство в исходное состояние и поступает на выход 16 устройства для вызова кода следующего символа из внешнего устройства управления (фиг. 1 не показано).

0

Технико-экономическая эффективность изобретения заключается в повышении быстродействия устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1005170A1 |

| Устройство для формирования символов на экране электронно-лучевой трубки | 1981 |

|

SU1001160A1 |

| Устройство для отображения информации | 1981 |

|

SU963080A1 |

| Устройство для отображения информации | 1980 |

|

SU943700A1 |

| Устройство для отображения информации | 1978 |

|

SU746629A1 |

| Устройство для формирования символов | 1983 |

|

SU1088060A1 |

| Устройство для отображения информации | 1985 |

|

SU1316028A2 |

| Устройство для формирования символов | 1980 |

|

SU934540A1 |

| Устройство для отображения информации | 1979 |

|

SU868822A2 |

| Устройство для отображения информации | 1976 |

|

SU634322A1 |

УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИМВОЛОВ, содержащее блок элементов 2И-ИЛИ, первый вход которого является первым входом устройства, второй вход подключен к первому вьлходу синхронизатора, третий вход - к выходу первого блока памяти, вход которого соединен с выходом счетчика, первый вход которого подключен к выходу блока элементов 2И-ИЛИ, делитель частоты, первый вход которого и первые входы синхронизатора, элемента И и регистра подключены к выходу преобразователя код-время, первый вход которого соединен с вторым выходом синхронизатора, третий выход которого является первым выходом устройства и подключен к вторым входам делителя частоты и преобразователя код - время и к первому входу генератора импульсов, второй вход которого является вторым входом устройства, а выход соединен с вторым входом синхронизатора, четвертый выход которого связан с первым входом генератора развертки, выходы которого являются вторым и третьим выходами устройства, второй вход генератора развертки подключен к первому выходу регистра, второй выход которого соединен с блоком подсвета, выход которого является четвертым выходом устройства, второй блок памяти, о тличающеес.я тем, что, с целью увеличения быстродействия устройства, оно содержит комсл мутатор, выход которого подключен к второму входу регистра и третьим входам синхронизатора и преобразователя код - время, первый вход коммутатора соединен с выходом первого блока памяти, второй вход - с вторым выходом делителя частоты, выход которого подключен к второму входу элемента И, выход которого соединен с вторым входом счетчика, выход которого связан с входом второго блока памяти, выход которого соединен со с третьим входом коммутатора. СХ) 4

иг.1

& 1ходы

fui.l

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Устройство для отображения информации | 1980 |

|

SU943700A1 |

Авторы

Даты

1984-09-15—Публикация

1983-05-25—Подача