(54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1977 |

|

SU711602A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1981 |

|

SU1005170A1 |

| Устройство для формирования символов | 1980 |

|

SU934540A1 |

| Устройство для отображения информации | 1978 |

|

SU746629A1 |

| Устройство для отображения информации | 1985 |

|

SU1316028A2 |

| Устройство для отображения информации | 1979 |

|

SU868822A2 |

| Устройство для формирования символов | 1983 |

|

SU1113840A1 |

| Устройство для формирования символов | 1983 |

|

SU1088060A1 |

| Устройство для отображения информации | 1980 |

|

SU943700A1 |

| Устройство для формирования символов на экране электронно-лучевой трубки | 1981 |

|

SU1001160A1 |

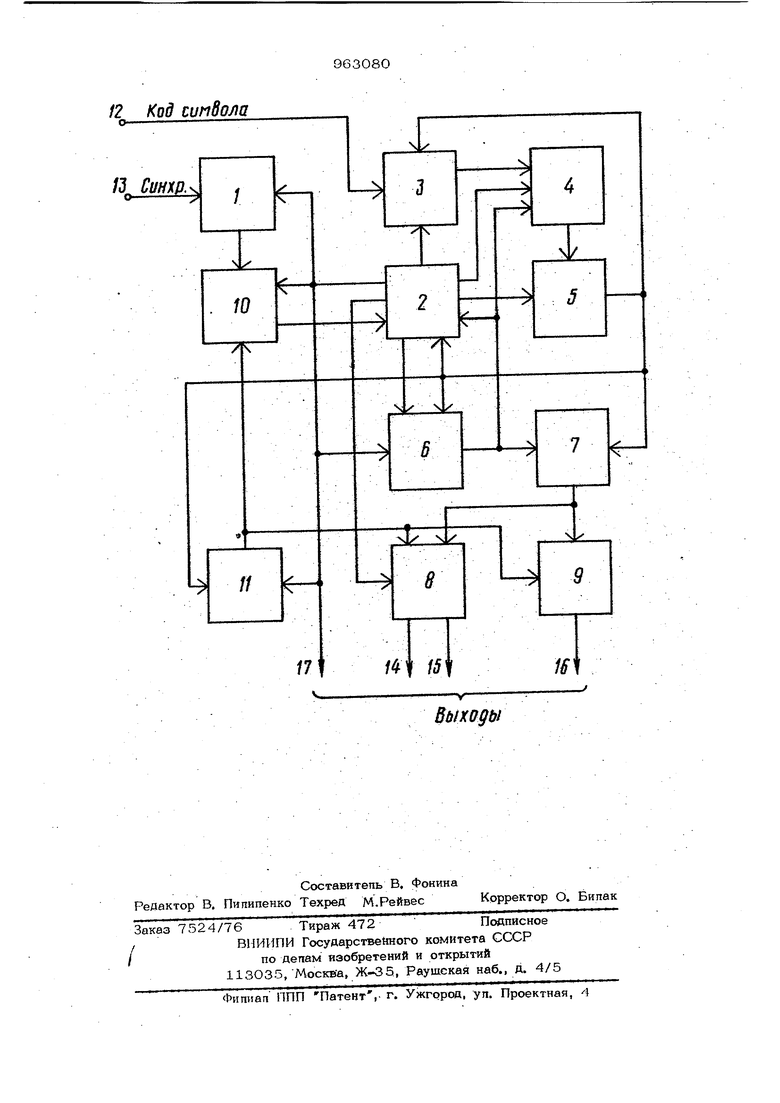

. 1 Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах дпя формирования символов на экране электронно71у-г чевой трубки (ЭЛТ). Известно устройство дпя индикации символов на экрану электроннолучевой трубки, содержащее схему выбора, выходы которой подключены к входам бпока памяти символов, другие входь которого связаны с выходами распределителя, соединенного с генератором, а выходы подключены к входам блоков координатной развертки луча и к триггеру, иыход триггера подсвета подключён к входам блоков координатной развертки луча и ко вхо ду генератора fl. Недостатком данного устройства явля.ется то, что в нем все символы формируются из фигурного микрорастра, который ограничивает номенклатуру отображаемых символов, а следовательно, и область при менения устройства. Наиболее близким по технической сущности к предлагаемому является устройство для отображения информации, содержащее блок памяти, соединенный с регистром, генератор функциональных напряжений, подключенный к регистру, преобразователь код - время, соединенный с генераторе импульсов регистром, подкточенным к блоку подсвета луча, счетчик адреса, логический блок и формирователь импульсов соединенный с генератором импульсов, преобразователем кой - время, генератором функциональных напряжений, б лсж ом памяти, счетчнк мч1 адреса и логическим блоком, подключенным к блоку памяти и счетчирсу адреса, соединенному с преобразователем код-время и блоком памяти Х2. Недостатком известного устройства 5Юпяется низкое быстродействие, обусловленное постоянной скоростью формирования векторов символа независимо от их длины. Эта скорость определяется временем формирования единичного вектора. которое, в свою очередь, ограничивается минимальным временем выборки кода из блока памяти. Цель изобретения -.повышение быстродействия устройства. Поставленная цепь достигается тем, что в и;звестнре устройство, содержащее формирователь импульсов, выходы которого подключены к первым входам логического блока, счетчика адреса, блока памяти, генератора функциональных напряжени генератора импульсов, первому и второму входам преобразователя код - время, вы ход которого соединен с первыми входами регистра микрокоманд, формирователя импульсов и вторым входом счетчика адреса, выход которого подключен к второму входу блока памяти, выход которого соединен с третьим входом преобразователя код-время и с вторыми входами формирователя импульсов, логического блока и регистра микрокоманд, выход которого подключен к первому входу блока подсвета и второму входу генератора функциональных напряжений, выхоДы которых являются выходами устройства, третий вход логического блока является первым входом устройства, а второй вход генератора импульсов яэляется вторым входом устройства, дополнительно введены управляемый делитель частоты и триггер, первый вход которого соединен с первыми входами управляемого Делителя частоты и генератора импульсов, второй вход триггера подключен к выходу блока памяти, а выход соединен с вторыми входами бло ка подсвета, управляемого делитепя частоты и третьим входом генератора функциональных напряжений, выход генератора импульсов подключен к третьему входу управляемого Делителя частоты, соединенного выходом с третьим входом фор мирователя импульсов. На чертеже приведена блок-схема уст ройства. Устройство содержит генератор 1 импульсов формирователь 2 импульсов, логический блок 3, счетчик 4 адреса, блок 5 памяти, преобразователь 6 код - время, регистр 7 микрокоманд, генератор 8 функциональных напряжений, блок 9 подсвета луча, управляемый делитешь 1О частоты, tpиггep 11. Позициями 12-17 обозначены вкоды и выходы устройства. Генератор 1 импульсов управляющим входом подключен ко входу 13 синхронизации, входом установки в ггупь соединен с входал и установки в нуль управляемого делителя 10 частоты, преобразоватеного адреса микропрограммы символа, по которым выбирается информация с блока 5 памяти. Блок S памяти предназначен ля 6 код - время, триггера 11, выходом 17 устрой;ства и первым выходом формирователя 2 импульсов, который вторым выходом связан с входом записи информации логического блока 3, третьим выходом соединен с входом установки в нуль счетчика 4 адреса, четвертым выходом связан с входом опроса блока 5 памяти, -ПЯТЫМ выходом соединен со счет - ным входом преобразователя 6 код - время, шестым выходом связан с входом разрешения работы генератора 8 функци-ональных напряжений, первый информационный вход логического блока 3 является входом 12 устройства, а второй инфор1мационный вход соединен с выходом блока 5 памяти, выход погического блока 3соединен с адресным входом счетчика 4адреса, который своим выходом соединен с адресньгм входом блока 5 памяти, выход которого соединен с информационным входом формирователя 2 импул)сов, преобразователя 6 код время, регистра 7 микрокоманд и входом триггера 11, выход преобразователя 6 код время соединен с входом формирователя 2 импульсов, счетным входом счетчика 4 адреса и входом записи информации регистра 7 микрокоманд, выход которого подключен к информационным входам ге нератора 8 функциональных напряжений и блока 9 подсвета луча, выходы которых являются выходами 14-16 устройства, выход генератора 1 импульсов соединен с первым входом управляемого делителя 10 частоты, связанного выходом с входом поступления тактовых импульсов формирователя 2, выход триггера 11 соединен с управляющими входами генератора 8 функциональных -напряжений, блока 9 подсвета луча, управляемого делителя 1О частоты. Генератор 1 импульсов предназначен для формирования пачки тактовых импульсов. Формирователь 2 импульсов предназначен для формирования основных сигналов управления между блоками устройства. Логический блок 3 Представляет собой схему коммутатора ин формации с двух направлений и предназначен для коммутации кода Символа со входа 12 устройства или кода начального ацреса с выхода блока 5 памяти. Техническая реализация его. может бытпь выполнена на элементах 2И-ИЛИ. Счетчик 4 адреса предназначен записи кода символа или кода начапьдля заттиси и хранения колов начапышх адресов и кодов векторов симвопов. Пре обраэоватепь 6 код - время предназначен дпя формирования сигнапов с временными интервалами, пропорциональными коДУ Длины вектора. Регистр 7 микрокоманд предназначен дпя записи и хранения кодов векторов на время их- написания. Генератор 8 функциональных напряжений предназначен дпя формирования напряжений развертки символа по координатам V и . Блок 9 подсвета пуча предназначен Для формирования сигналов подсвета векторов символа. Управляемый делитепь 1О частоты предназначен для изменения так- товой частоты на входе формироватепя 2 импульсов. Техническая .реализация его может быть осуществлена, например, на базе микросхемь 133 ИЕ8. Триггер 11 предназначен для записи и хранения признака скорости формирования симвопа. Устройство работает следующим образом. Код симвопа с входа 12 устройства поступает на первый вход погического блока 3, а с входа 13 устройства импупь сом синхронизации запускается старт-сто ный генератор 1 импупьсов. С выхода ге нератора 1 последовательность импульсов через управпяеьа 1й делитель Ю частоты поступает на первый вход формирователя 2 импульсов, который на первом выходе формирует сигнап записи кода символа через погический бпок 3 в счетчик 4 адреса, а на втором выходе сигнап обращения к блоку 5 памяти. По коду симвопа с выхода счетчика 4 адреса к первому сигналу обращения на выходе блока 5 памяти формируется код начального (промежуточного) адреса мик ропрограммы символа, который хранится в выходном регистре блока 5 памяти (не показан). Микропрограмма символа записывав тся в блок 5 памяти в два массива. В пер вый массив записываются коды начапьны адресов символов, а во второй - коды их векторов. Каждому входному коду символа соо ветствует свой код начапьного адреса, который является адресом кода первого вектора сикшопа. После выборки кода начапьного адреса из бпока 5 памяти счетчик 4 адреса сбрасывается в нуль сигналом сброса с -третьего выхода формирователя 2, который на первом выходе формирует сигнап записи кода начального адреса через логический бпок : в счетчик 4, а на втором - сигнал обращения к 6nojcy 5 памяти. По коду начального адреса с выхода счетчика 4 и второму обращению на выходе блока 5 памяти формируется код первого вектора символа. Коды векторов символа содержат информацию о развертке векторов по координатам X и Y (б разрядов), о подсвете вектора (1 разряд), о длине вектора (3 разряда), о скорости формирования символа (1 разряд в первом векторе символа ), о конце формирования симвопа (1 разряд в последнем векторе). После выборки кода первого вектора символа с блока 5 памяти с четвертого выхода формироватепя 2 начинают поступать тактовые импульсы на первый вход преобразоватепячЭ код-время, который в начальный момент времени на своем выходе формирует сигнап конца векторй (СКВ), соответствующий вектору , нулевой дпины. По этому сигналу в преобразователь 6 код-время вводится 3-х разрядный код длины первого вектора символа, а в регистр 7 микрокоманд 7-ми разрядный код развертки и подсвета вектора. Одновременно по этому сигналу увеличивается на единицу младшего разряда код начального адреса на выходе счетчика 4, формируется очередной сигнал обращения к блоку 5 памяти и сигнал разрешения работы генератора 8 функциональных напряжений на пятом выходе формирователя 2. С момента записи кода первого векто ра симвопа в регистр 7 микрокоманд генератор 8 функциональных напряжений формирует напряжения развертки символа по координатам у и , блок 9 подсвета опредепяет подсвет пуча ЭЛТ, а преобразователь 6 кс«-время задает дпину вектора. После окончания формирования первого вектора символа на выходе преобразователя 6 код-время форкглруется сигнап СКВ с временным интервалом, пропорциональнь1м частоте тактовых импульсов на первом входе и 3-х разряднокту коду длины вектора на втором входе. Аналогичным образом производится формирование всех последующих векторов символа. При формировании последнего вектора символа в его коде содержится признак конца символа, который поступает на второй вход формирователя 2 импульсов. По этому признаку на шестом выходе формирователя 2 формируется сигнал конца символа, которым все улпь уст 79630ройства ус тана впиваются в нулевое состояние. Одновременно этот сигнал поступав ет на выход 17 устройства для вь13ова кода следующего символа. Время формирования символов в пред- 5 латаемом устройстве зависит от чиспа векторов в его контуре и частоты работы преобразователя 6 код-время. Число векторов в контуре определяется необходимой конфигуранией символа, а частота так- товых импульсов на входе преобразошателя 6 код-время задается управляемым Делителем 10 частоты по признаку скорости формирования символа. Признак скорости формирования симво- ла в виде сигнала логическойединицы записыв(эется в блок 5 памяти в одном из разрядов кода первого векторш только для тех символов, которые содержат в своем Контуре векторы единичной длины. 20 По этому признаку триггер 11 устанавли- вается в единичное состояние, а на выко- де управляемого делителя 1О устанавливается частота тактовых импульсов, рав- ная максимальной частоге выборки кодов из блока 5 памяти. При отсутствии признака скорости формирования символа частота тактовых импульсов на выходе управляемого Делителя 10 удваивается, что обеспечивает уменьшение времени форми- 30 рования символа в 2 раза. Признак скорости формирования символа .с триггера 11 поступает также на управлякядие входы генератора 8 функциональных н-апряжеНИИ и блока 9 подсвета луча для измене- з$ ния амплитуды выходных напряжений с. делью сохранения размеров и яркости символа. По сравнению с известным в предлагаемам устройстве учитываются длины век- 40 торов символа, скорость формирования которых может быть увеличена в 2 раза, если в их составе отсутствуют единичные. векторы. Поэтому при построении фигуры символа необходимо по возможности (без 4S ухудшения качества) избегать применения единичных векторов, а за счет этого уменьшить время формирования символа в 2 раза. Эффективность применения устройства будет возрастать с уменьшением ко- JQ личества символов, содержащих векторы. единичной длинь. Таким образом, применение предпагаемого устройства может Дать попожитепьи ный эффект, заключающийся в выводе до08попнительной информации за счет сокрашедая времени формирования символов, йе сойержащих векторов единичной длины. Ф о р м ула изобретения Устройствр для отображения информаиии, содержащее формирователь импульсов, выходы которого подключены к первым входам логического блока, счетчика адреса, блока памяти, генератора функциональных напряжений, генератора импульсов, первому и второму входам преобразоватепя код-время, выход которого соединен с первыми входами регистра микрокоманд, формирователя импу-льсов И вторым BXOJEIOM счетчика адреса, выход которого подключен к йходу блока памяти, выход которого соединен с третъим входом преобразователя кой-время и с вторыми входами формирователя импульсов, логического блока и регистра микрокоманд, выход которого подключен к первому входу блока подсвета и второму входу генератора функциональных напряжений, выходы которых являются выходами устройства, третий вход логического блока является первым входом уст- ройства, а второй вход генератора импульсов является вторым входом устройства, о т л и ч а ю щ е ее я тем, что с цепью цовьшгенйя быстродействия, в устройство введены управляемый делитель частоты и триггер, первый вход которого соединен с первыми входами управляемогр Делителя :Частоть1 и генератора им- щгльсов, второй вход триггера подключен к-выходу блока пшляти, а выход соединен с вторыми входами блока подсвета, управляемого делителя частоты и третьим входом генератора функциональных напряжениЙ, выход генератора импульсов подключей к третьему входу управляемого Делителя частоты, выхеш которого соединен с третьим входом формирователя импульсов.. Источники информ§ции, принятые во внимание при экспертизе 1,Авторосое свидетельство СССР № 343263, кп. Q 06 F 3/14, 1970. 2.Авторское свидетельство СССР № 634322, кл. G 06 К 15/2О, 1976. (прототип).

/2 Код сипвола

Выходы

Авторы

Даты

1982-09-30—Публикация

1981-03-31—Подача