Изобретение относится к радиотехнике и может быть использовано для детектирования частотно-модулиро н- ных (ЧМ) сигналов при изменении несущей частоты входного сигнала в поло-5 се частот, бо много раз превышающей раствор дискриминационной характеристики.

Известен частотный детектор (ЧД), содержаний первый и второй сумматоры, первые входы которых подключены к входу частотного детектора через линию задержки, а вторые входы - через фазовращатели, при этом выходы сумматоров соединены через последова тельно соединенные регулируемые усилители и амплитудные детекторы с входами блока вычитания и с входами третьего сумматора, выход которого прдключен к управляющим входам регули- 20 руемых усилителей Л

Недостатком известного ЧД является возникновение искажений детектируемого сигнала при приближении несущей частоты входного ЧМ-сигнала . 25 к краю дискриминационной характеристики. .

Наиболее близким по технической сущности к предлагаемому является адаптивный ЧД, содержащий последо- 30 вательно соединенные линию задержки, первый сумматор, первый амплитудный детектор, первый блок вычитания, первый инвертор, первый коммутатор, другой вход которого подключен к 35 входу первого инвертора, и второй коммутатор, выход которого является выкодом ЧД, последовательно соединенные фазоинвертор, второй сумматор и второй амплитудный детектор, вы- 40 ход которого подключен к другому входу первого блока вычитания, последовательно соединенные первый фазовращатель, третий сумматор, третий амплитудный детектор, второй блок вы-45 читания, второй инвертор и третий коммутатор, второй вход которого подключен к входу второго инвертора, а выход - к второму входу второго коммутатора, последовательно соеди- 50 ненные второй фазовращатель, четвертый сумматор и четвертый амплитудный етектор, выход которого подключен к второму входу второго блока вычитания, последовательно соединенные и 55 включенные между выходами первого лока вычитания и управляющим вхоом третьего коммутатора и, соответтвенно, между выходом второго блока

вычитания и управляющим входом первого коммутатора, первый фильтр нижних частот (ФНЧ) и первый пороговый элемент и, соответственно, второй ФНЧ и второй пороговый элемент, а также компаратор, вькод которого подключен к управляющему входу второго коммутатора и два детектора абсолютной величины сигнала, включенные между точками соединения ФНЧ с пороговыми элементами и входами компаратора, при этом вторые входы второго, третьего и четвертого сумматоров соединены с выходом линии задержки, второй вход первого сумматора подключен к входу линии задержки, к входам фазоинвертора, второго и первого фазовращателей и является входом ЧД 2J .

Недостатком известного адаптивног частотного детектора является узкая рабочая часть дискриминационной характеристики ЧД. Это вызвано переключением характеристики между соседними каналами. В результате ширина полосы входного сигнала, ко- торая может быть обработана известным ЧД, составляет только часть раствора дискриминационной характеристики.

Цель изобретения - расширение рабочей области дискриминационной характеристики.

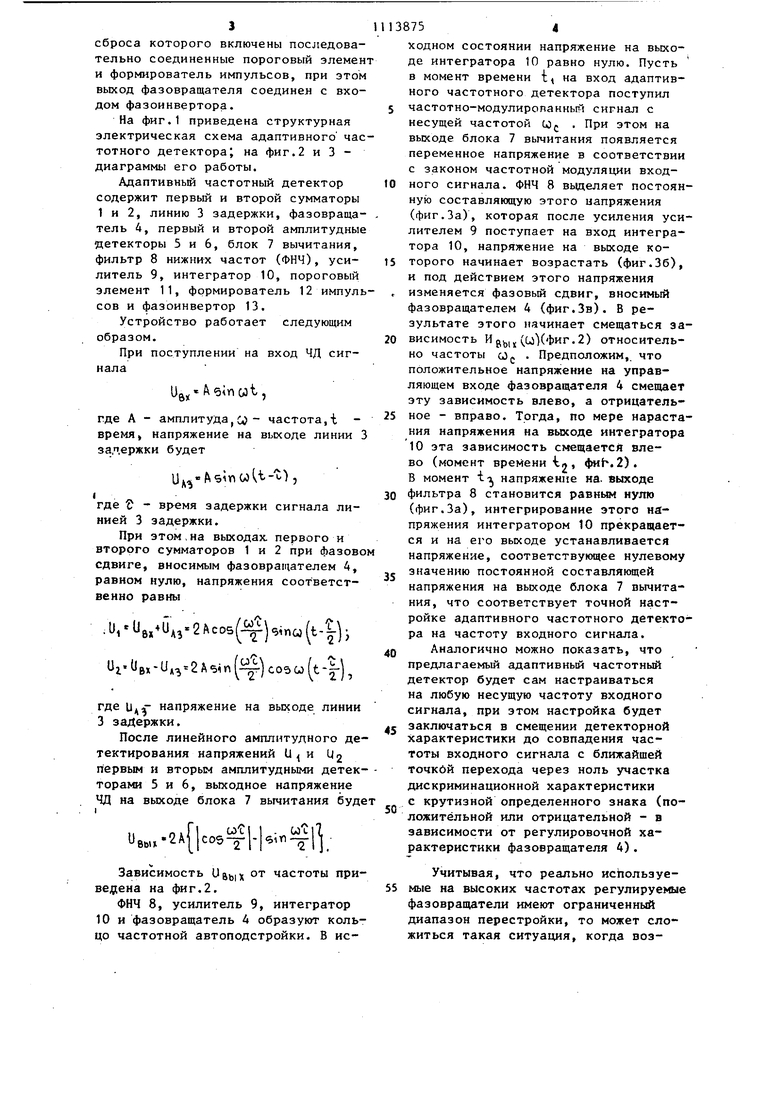

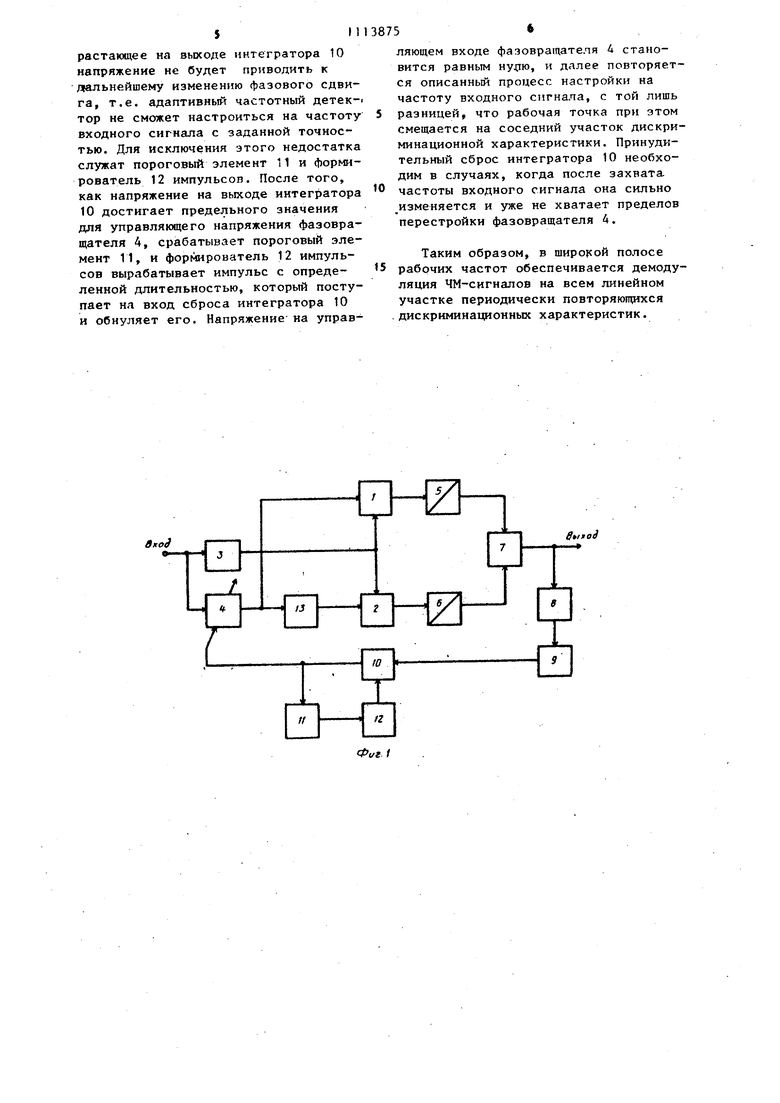

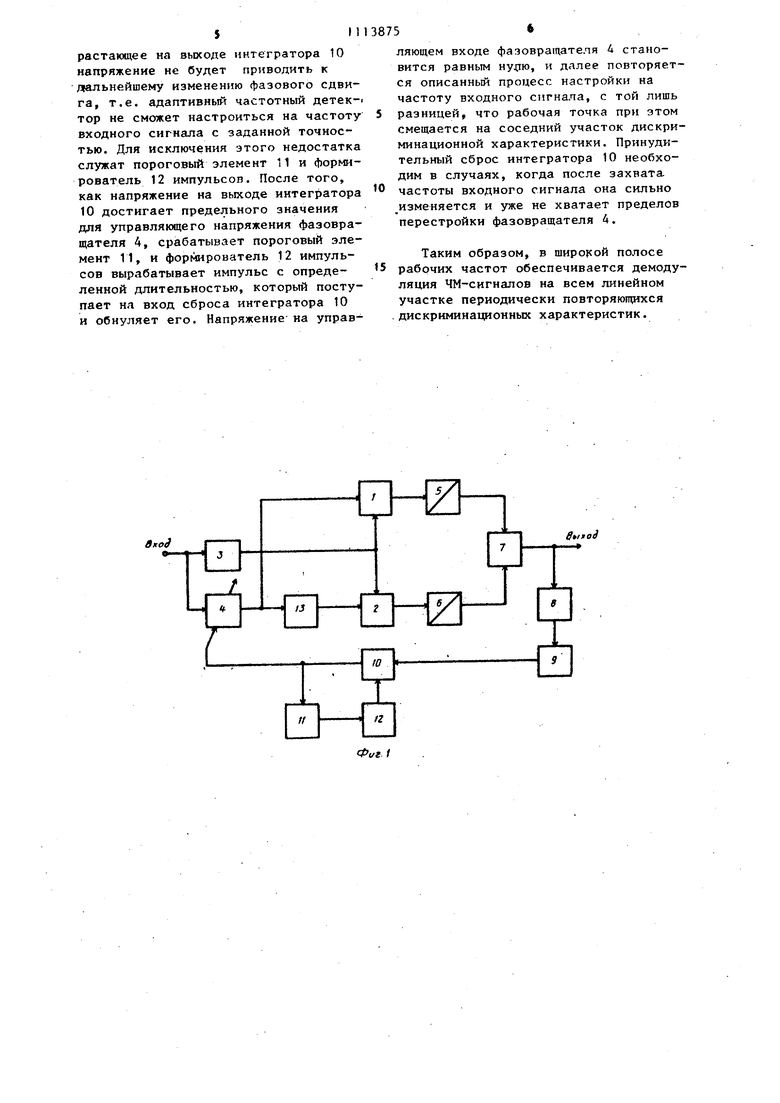

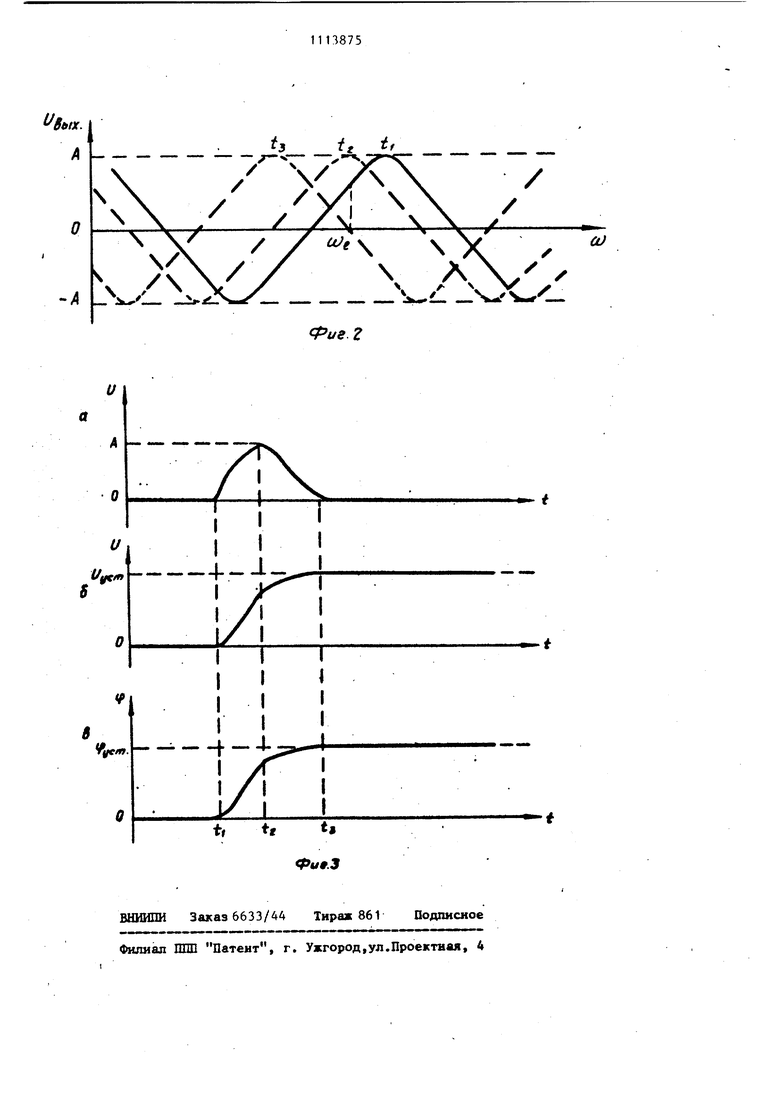

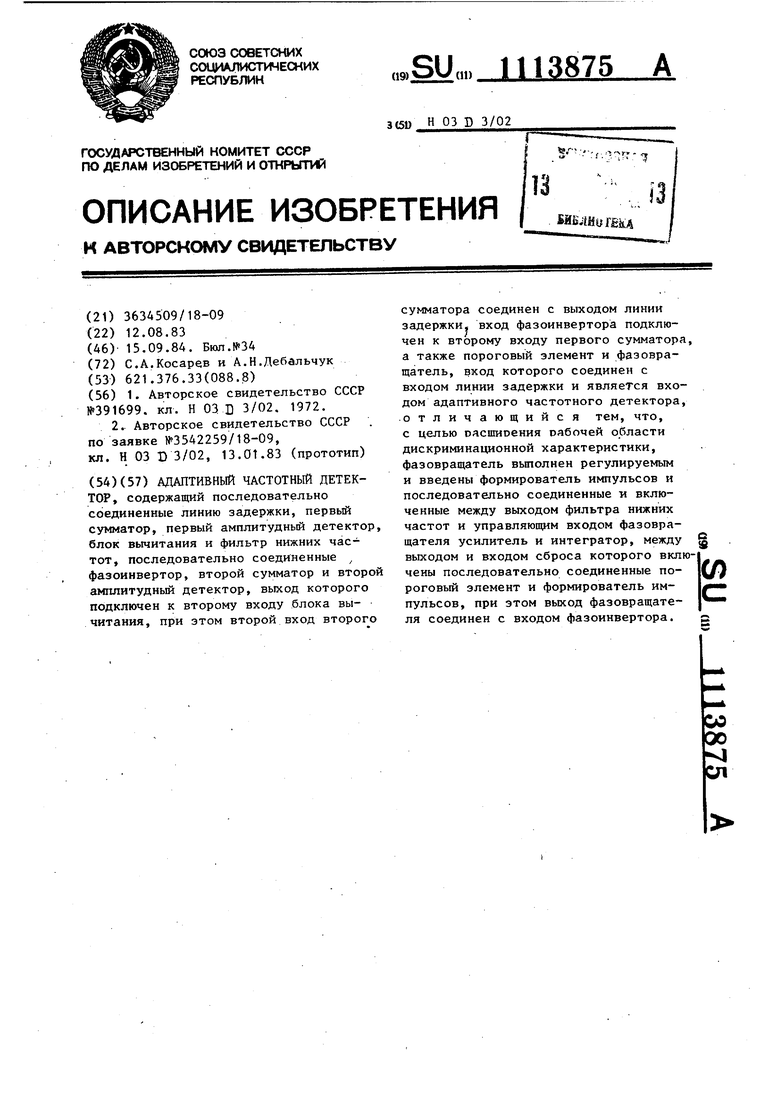

Указанная цель достигается тем, что в адаптивный частотный детектор, содержащий последовательно соединенные линию задержки, первый сумматор, первый амплитудньй детектор, блок вычитания и фильтр нижних частот, последовательно соединенные фазоинвертор, второй сумматор и второй амплитудный детектор, выход которого подключён к второму входу блока вычитания, при этом второй вход второго сумматора соединен с выходом линии задержки, вход фазоинвертора подключен к второму входу первого сумматора, а также пороговый элемент и фазовращатель, вход которого соединен с входом линии задержки и является входом адаптивного частотного детектора.фазовращатель вьтолнен регулируемым, введены формирователь импульсов и последовательно соединные и включенные между выходом фильтра нижних частот и управляющим входом фaзoвpaщateля усилитель и интегратор, между выходом и входом 3 сброса которого включены последовательно соединенные пороговый элемен и формирователь импульсов, при этом выход фазовращателя соединен с входом фазоинвертора. На фиг.1 приведена структурная электрическая схема адаптивного час тотного детектора; на фиг.2 и 3 диаграммы его работы. Адаптивный частотный детектор содержит первый и второй сумматоры 1 и 2, линию 3 задержки, фазовраща тель 4, первый и второй амплитудны детекторы 5 и 6, блок 7 вычитания, фильтр 8 нижних частот (ФНЧ), усилитель 9, интегратор 10, пороговый элемент 11, формирователь 12 импул сов и фазоинвертор 13. Устройство работает следующим образом. При поступлении на вход ЧД сигналаllft. , где А - амплитуда СО частота,t время, напряжение на выходе линии задержки будет ид -Л51псо1 -), где J - время задержки сигнала линией 3 задержки. При этом,на выходах первого и второго сумматоров 1 и 2 при фазов сдвиге, вносимым фазовращателем 4, равном нулю, напряжения соответственно равны .1liвx Uд,(4)51nQ(t-| Ui«llBx-U,()co5Co(t-|-), где напряжение на выходе линии 3 задержки. После линейного амплитудного де тектирования напряжений U2 первым и вторым амплитудными детек торами 5 и 6, выходное напряжение ЧД на выходе блока 7 вычитания буд I nifl i WtlZ 1 вьи-2А|1со5-2-1- . Зависимость частоты при ведена на фиг.2. ФНЧ 8, усилитель 9, интегратор 10 и фазовращатель 4 образуют коль цо частотной автоподстройки. В ис75ходном состоянии напряжение на выходе интегратора 10 равно нулю. Пусть в момент времени t на вход адаптивного частотного детектора поступил частотно-модулиропанньй сигнал с несущей частотой COj, . При этом на выходе блока 7 вычитания появляется переменное напряжение в соответствии с законом частотной модуля1у1и входного сигнала. ФНЧ В вьделяет постоянную составляющую этого напряжения (фиг.За), которая после усиления усилителем 9 поступает на вход интегратора 10, напряжение на выходе которого начинает возрастать (фиг.36), и под действием этого напряжения изменяется фазовый сдвиг, вносимый фазовращателем 4 (фиг.Зв). В результате этого начинает смещаться эависимость (иХФиг.2) относительПредположим,, что но частоты со. положительное напряжение на управляющем входе фазовращателя 4 смещает эту зависимость влево, а отрицательное - вправо. Тогда, по мере нарастания напряжения на выходе интегратора 10 эта зависимость смещается влево (момент времени trt Фи.2). В момент i- напряжение на- выходе фильтра 8 становится равным нулю (фиг.За), интегрирование этого напряжения интегратором 10 прекращается и на его выходе устанавливается напряжение, соответствующее нулевому значению постоянной составляющей напряжения на выходе блока 7 вычитания, что соответствует точной настройке адаптивного частотного детектора на частоту входного сигнала. Аналогично можно показать, что предлагаемый адаптивный частотный детектор будет сам настраиваться на любую несущую частоту входного сигнала, при этом настройка будет заключаться в смещении детекторной характеристики до совпадения частоты входного сигнала с ближайщей точкбй перехода через ноль участка дискриминационной характеристики с крутизной определенного знака (положительной или отрицательной - в зависимости от регулировочной характеристики фазовращателя 4). Учитывая, что реально исПользуемые на высоких частотах регулируемые фазовращатели имеют ограниченный диапазон перестройки, то может сложиться такая ситуация, когда воз$in

растающее на выходе интегратора 10 напряжение не будет приводить к дальнейшему изменению фазового сдвига, т.е. адаптивный частотный детек-тор не сможет настроиться на частоту входного сигнала с заданной точностью. Для исключения этого недостатка служат пороговый элемент 11 и формирователь 12 импульсов. После того, как напряжение на выходе интегратора 10 достигает предельного значения для управляющего напряжения фазовращателя А, срабатывает пороговый элемент 11, и формирователь 12 импульсов вырабатывает импульс с определенной длительностью, которьй поступает на вход сброса интегратора 10 и обнуляет его. Напряжение на управ56

ляющем входе фазовращателя Д становится равным , и далее повторяется описанньй процесс настройки на частоту входного сигнала, с той лишь разницей, что рабочая точка при этом смещается на соседний участок дискриминационной характеристики. Принудительный сброс интегратора 10 необходим в случаях, когда после захвата частоты входного сигнала она сильно изменяется и уже не хватает пределов перестройки фазовращателя 4.

Таким образом, в широкой полосе рабочих частот обеспечивается демодуляция ЧМ-сигналов на всем линейном участке периодически повторяющихся дискриминационных характеристик.

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный демодулятор частотно-модулированных сигналов | 1985 |

|

SU1261081A1 |

| Адаптивный частотный детектор | 1984 |

|

SU1202018A1 |

| Устройство для автоматического измерения девиации частоты | 1983 |

|

SU1325374A1 |

| Частотный детектор | 1983 |

|

SU1111249A1 |

| Частотный детектор | 1983 |

|

SU1131020A1 |

| Устройство автоматического контроля радиопередающих устройств | 1983 |

|

SU1218338A1 |

| Устройство для измерения девиации частоты | 1983 |

|

SU1323975A1 |

| Частотный детектор | 1983 |

|

SU1185565A1 |

| Демодулятор частотно-манипулированных сигналов | 1984 |

|

SU1228297A1 |

| Частотный детектор | 1983 |

|

SU1231574A1 |

АДАПТИВНЫЙ ЧАСТОТНЫЙ ДЕТЕКТОР, содержащий последовательно соединенные линию задержки, первый сумматор, первый амплитудный детектор, блок вычитания и фильтр нижних частот, последовательно соединенные фазоинвертор, второй сумматор и второй амплитудный детектор, выход которого подключен к второму входу блока вычитания, при этом второй вход второго сумматора соединен с выходом линии задержки, вход фазоинвертора подключен к второму входу первого сумматора, а также пороговый злемент и фазовращатель, вход которого соединен с входом линии задержки и является входом адаптивного частотного детектора, отличающийся тем, что, с целью оясщиоения рабочей области дискриминационной характеристики, фазовращатель выполнен регулируемым и введены формирователь импульсов и последовательно соединенные и включенные между выходом фильтра нижних частот и управляющим входом фазовращателя усилитель и интегратор, между выходом и входом сброса которого вклю(Л чены последовательно соединенные пороговый элемент и формирователь импульсов, при этом выход фазовращателя соединен с входом фазоинвертора. мм

вхоЗ

t/е.г v. )

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ЧАСТОТНЫЙ ДЕТЕКТОР | 0 |

|

SU391699A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке №3542259/18-09, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1984-09-15—Публикация

1983-08-12—Подача