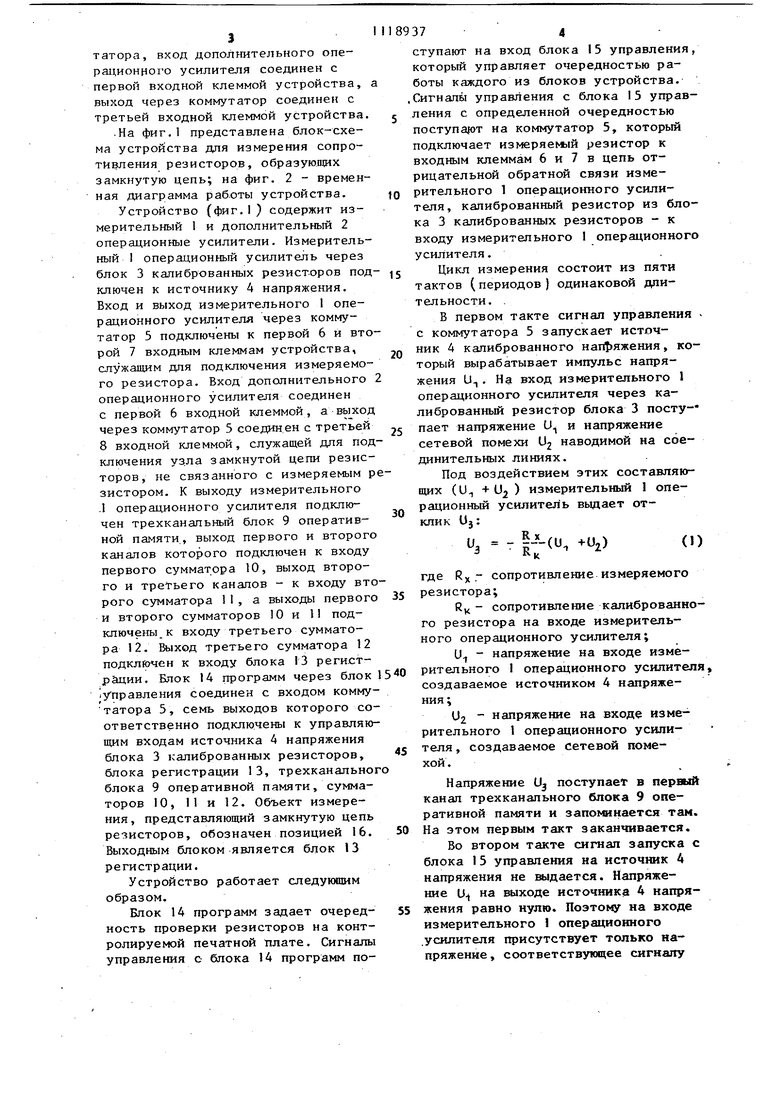

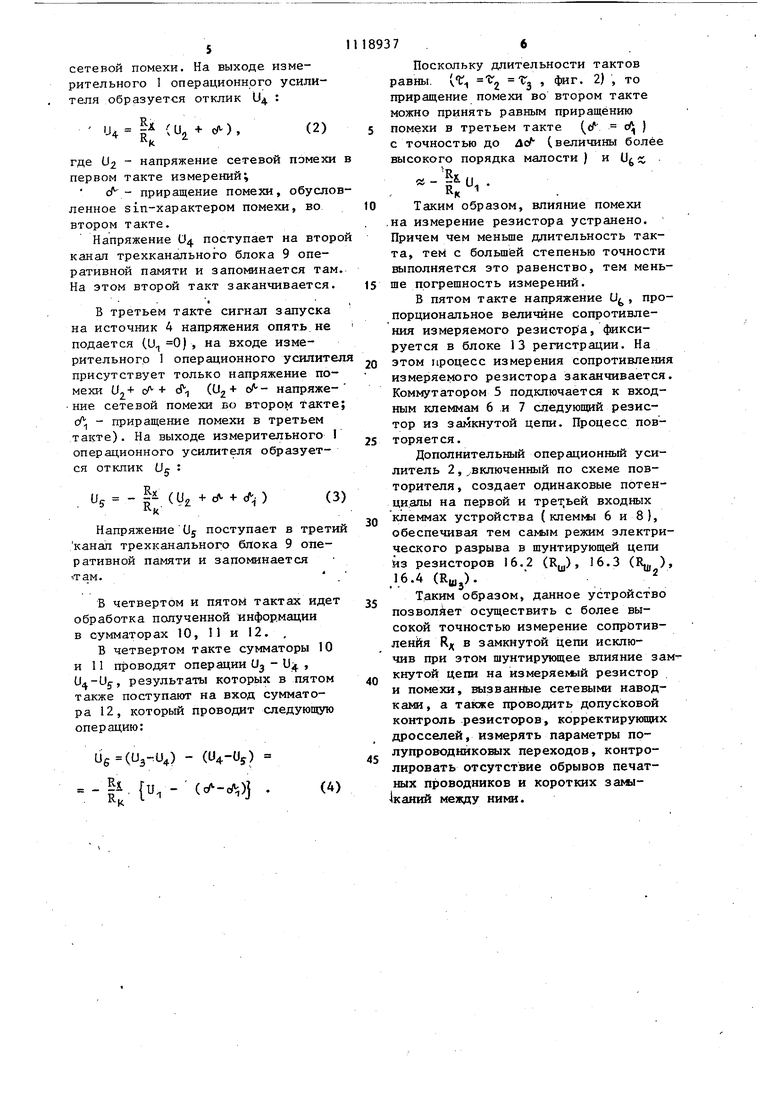

Изобретение относится к измерению электрических величин, в частности к измерению элементов цепей с сосредоточенными постоянными, и может быт использовано дЛя быстродействующего автоматического контроля радиокомпонентов радиоэлектронных схем, собран ных на печатных платах в условиях массового производства. Известно устройство для измерения сопротивления резисторов, образующих замкнутую цепь, содержащее источник напряжения, подключенный че рез калиброванный резистор к входным зажимам дпя подключения измеряемого резистора, измерительный прибор, подключенный к этим же зажимам, повторитель сигнала, неинвертирующий вход которого подключен к этим же зажимам, повторитель сигнала, неинвертирующий вход которого подключен к входному зажиму, а выход - к узлу замкнутой цепи резисторов, несвязанному с измеряемым резистором t 3Равенство потенциалов между входом и выходом повторителя позволяет устранить шунтирующее влияние резисторов замкнутой цепи на измеряемый резистор и таким образом повысить точность проводимых измерений. Однако погрешность измерений, связанн с наличием сетевых помех, ,в данном устройстве не учитывает1ся что приводит к невысокой точности измерений. Наиболее близким техническим решением к изобретению является устройство для измерений сопротивления резисторов, образующих замкнутую цеп:ь, содержащее три входные клеммы, основной измерительный one рационный усилитель, вход которого через блок калиброванных резисторов подключен к выходу источника напряжения, вход и выход измерительного операционного усилителя через коммуг татор соединены с первой и второй входными клеммами устройства, служащими дпя подключения измеряемого резистора, дополнительный операционный усилитель, блок регистрации, блок программ, соединенный через блок управления с входом коммутатора, три выхода которого подключены соответственно к управляющим входам источника напряжения, блока калиброванных резисторов и блока регистрации, блок резисторов, включенН между входом выходом дополнительного операцион372ного усилителя, вход которого соединен с блоком регистрации и через коммутатор с третьей входной клеммой устройства, служащей для подключения узла замкнутой цепи резисторов, непосредственно несвязанного с измеряемым резистором, управляющий вход блока резисторов подключен к четвертому выходу коммутатора t21. Однако известное устройство из-за наличия сетевых помех не обеспечивает необходимой точности измерений. Цель изобретения - повышение точности измерений. Поставленная цель достигается тем, что в устройство для измерения сопротивления резисторов, образующих замкнутую цепь, содержащее источник напряжения, выход которого через блок калиброванных резисторов подключен к входу измерительного операционного усилителя, вход и выход которого через коммутатор соединены с первой и второй входными клеммами устройства, служащими для подключения измеряемого резистора, дополнительный операционный усилитель, блок регистрации, блок программ, выход которого через блок управления соединен с входом коммутатора, три выхода которого соответственно подключены к управляюищм входам источника напряжения, блока калиброванных резисторов и блока регистрации, третью входную клемму устройства, служащую для подключения узла замкнутой цепи резисторов, не связанного с измеряемым резистором, введены трехканальный блок оперативной памяти и три сумматора, причем входы всех трех каналов блока оперативной памяти объединены и подключены к выходу измерительного операционного усилителя, выходы первого и второго каналов блока оперативной памяти подключены к входу первого сумматора, выходы второго и третьего каналов блока оперативной памяти - к входу второго сумматора, а выходы первого и второго сумматоров - к входам третьего сумматора, выход которого подключен к блоку регистрации, управлякяцие входы трехканального блока оперативной памяти и сумматоров подключены соответственно к четвертому, пятому, шестому и седьмому выходам коммутагора, вход дополнительного операционного усилителя соединен с первой входной клеммой устройства, выход через коммутатор соединен с третьей входной клеммой устройства .На фиг,1 представлена блок-схема устройства дпя измерения сопротивления резисторов, образующих замкнутую цепь; на фиг. 2 - временная диаграмма работы устройства. Устройство (фиг.1) содержит измерительный 1 и дополнительный 2 операционные усилители. Измерительный 1 операционный усилитель через блок 3 калиброванных резисторов под ключен к источнику 4 напряжения. Вход и выход измерительного 1 операционного усилителя через коммутатор 5 подключены к первой 6 и вто рой 7 входным клеммам устройства, служащим для подключения измеряемого резистора. Вход дополнительного операционного усилителя соединен с первой 6 входной клеммой, а выход через коммутатор 5 соединен с третьей 8 входной клеммой, служащей для под ключения узла замкнутой цепи резисторов, не связанного с измеряемым р зистором. К выходу измерительного .1 операционного усилителя подключен трехканапьный блок 9 оперативной памяти., выход первого и второго каналов которого подключен к входу первого сумматора 10, выход второго и третьего каналов - к входу вт рого сумматора 11, а выходы первого и второго сумматоров 10 и 11 подключены, к входу третьего сумматора 12. Выход третьего сумматора 12 подключен к входу блока 13 регистрации. Блок 14 программ через блок управления соединен с входом комму татора 5, семь выходов которого со ответственно подключены к управляю щим входам источника 4 напряжения блока 3 калиброванных резисторов, блока регистрации 13, трехканально блока 9 оперативной памяти, сумматоров 10, 11 и 12. Объект измерения, представляющий замкнутую цепь резисторов, обозначен позицией 16. Выходным блоком является блок 13 регистрации. Устройство работает следующим образом. Блок 14 программ задает очередность проверки резисторов на контролируемой печатной плате. Сигналы управления с блока 14 программ по374ступают на вход блока 15 управления, который управляет очередностью работы каждого из блоков устройства. Сигналы управления с блока 15 управления с определенной очередностью nocTynajOT на коммутатор 5, который подключает измеряеи11й резистор к входным клеммам 6 и 7 в цепь отрицательной обратной связи измерительного 1 операционного усилителя, калиброванный резистор из блока 3 калиброванных резисторов - к входу измерительного 1 операционного усилителя. Цикл измерения состоит из пяти тактов (периодов) одинаковой длительности. . В первом такте сигнал управления с коммутатора 5 запускает источник 4 калиброванного нап11)яжения, который вырабатывает импульс напряжения и. На вход измерительного 1 операционного усилителя через калиброванный резистор блока 3 поступает напряжение U и напряжение сетевой помехи U2 наводимой на соединительных линиях. Под воздействием этих составляюЕцих (и + и ) измерительный 1 операционный усилитель вьщает отклик и. и, - (и, -ю) где KX сопротивление измеряемого резистора; R - сопротивление калиброванного резистора на входе измерительного операционного усилителя; и - напряжение на входе измерительного 1 операционного усилителя, создаваемое источником 4 напряжения ; и - напряжение на входе измерительного 1 операционного усилителя , создаваемое сетевой помехой. Напряжение U поступает в первый канал трехканального блока 9 оперативной памяти и запоминается там. На этом первым такт заканчивается. Во втором такте сигнал запуска с блока 15 управления на источник 4 напряжения не выдается. Напряжение Ц на выходе источника 4 напряжения равно нулю. Поэтому на входе измерительного I операциониого .усилителя присутствует только напряжение , соответствующее сигналу S сетевой помехи. На выходе измерительного 1 операционного усилителя образуется отклик U4 U4 t (U,, сА), где U2 - напряжение сетевой помех первом такте измерений; c - приращение помехи, обусл ленное sin-характером помехи, во втором такте. Напряжение 04 поступает на вто канал трехканального блока 9 оперативной памяти и запоминается та На этом второй такт заканчивается В третьем такте сигнал запуска на источник 4 напряжения опять.не подается (U 0), на входе измерительного 1 операционного усилит присутствует только напряжение по мехи (/ + ci, (U2 + 1 напряже кие сетевой помехи во втором такт с/ - приращение помехи в третьем такте). На выходе измерительного операционного усилителя образуется отклик Ug 5 - |- (Уг +dv. -К) Напряжение U поступает в трет канал трехканального блока 9 оперативной памяти и запоминается 1там. В четвертом и пятом тактах иде обработка полученной информации в сумматорах 10, 1 и 12. , В четвертом такте сумматоры 10 и 11 проводят операции Uj -114 , , результаты которых в пятом также поступают на вход сумматора 12, который проводит следующую операцию: U6() - (4-0.) -М {и,-(.) . 76 Поскольку длительности тактов равны. ,f 2 Т а , фиг. 2) , то приращение помехи во втором такте можно принять равным приращению помехи в третьем такте (сГ с ) с точностью до ДсА (величины более высокого порядка малости ) и (J х « - -« и р и . RK . Таким образом, влияние помехи на измерение резистора устранено. Причем чем меньше длительность такта, тем с большей степенью точности выполняется это равенство, тем меньше погрешность измерений. В пятом такте напряжение U, пропорциональное величине сопротивления измеряемого резистора, фиксируется в блоке 13 регистрации. На этом процесс измерения сопротивления измеряемого резистора заканчивается. Коммутатором 5 подключается к входным клеммам 6 .и 7 следующий резистор из замкнутой цепи. Процесс повторяется. Дополнительный операционный усилитель 2,включенный по схеме повторителя , создает одинаковые потенци.апы на первой и трет.ьей входных клеммах устройства ( клемм 1 6 и 8), обеспечивая тем самым режим электрического разрыва в шунтирующей цепи из резисторов 16.2 (R...), 16.3 (R,. ), 16.4 (Кщ,). Таким образом, данное устройство позволяет осуществить с более высокой точностью измерение сопротивления Rj в замкнутой цепи исключив при этом шунтирующее влияние замкнутой цепи на измеряемый резистор и помехи, вызванные сетевыми наводками, а также проводить допусковой контроль резисторов, корректирующих дросселей, измерять параметры полупроводнйкоаях переходов, контролировать отсутствие обрывов печатных проводников и коротких замыканий между ними.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения сопротивления резисторов | 1987 |

|

SU1652940A1 |

| Аналого-цифровой преобразователь сопротивления | 1983 |

|

SU1108369A1 |

| Устройство для измерения сопротивления резисторов,образующих замкнутую цепь | 1978 |

|

SU771567A1 |

| ИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО | 2011 |

|

RU2469341C1 |

| ИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО | 2011 |

|

RU2469339C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЭЛЕКТРОКОЖНОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ, УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА И ЕГО ВАРИАНТЫ | 2001 |

|

RU2268643C2 |

| Источник калиброванных напряжений | 1986 |

|

SU1345179A1 |

| Прибор для измерения параметров вибрации | 2024 |

|

RU2831263C1 |

| УСТРОЙСТВО ДЛЯ ДИАГНОСТИКИ ПО МЕТОДУ Р. ФОЛЛЯ И ЕГО ВАРИАНТЫ | 2002 |

|

RU2262296C2 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТОРОВ, ОБРАЗУЮЩИХ ЗАМКНУТУЮ ЦЕПЬ, содержащее источник напряжения, выход которого через блок калиброванных резисторов подключен к входу измерительного операционного усилителя, вход и выход которого через коммутатор соединены с первой и второй входными клеммами устройства, служащими для подключения измеряемого резистора, дополнительный операционньй усилитель, блок регистрации, блок программ, выход которого через блок управления соединен с входом коммутатора, три выхода которого соответственно подключены к управляющим входам источника напряжения, блока калиброванных резисторов и блока регистрации, третью входную клемму устройства, служащую для подключения узла замкнутой цепи резисторов, не связанного с измеряемым резистором, отличающееся тем, что, с целью повышения точности измерений, введены трехканальный блОк оперативной памяти и три сумматора, причем входы всех трех каналов блока оперативной памяти объединены и подключены к выходу измерительного операционного усилителя, выходы первого и второго каналов блока оперативной памяти подключены к входу первого сумматора, выходы второго и третьего каналов блока оперативной памяти .- к входу второго сумматора, а выходы первого и второго сумматоров - к входам третьего сумматора, выход которого подключен к блоку регистрации, управляющие входы трехканального блока оперативной памяти и сумматоров подключены соответственно к четвертому, пятому, шестому и седьмому выходам коммутатора, СХ) вход дополнительного операционного со усилителя соединен с первой входной клеммой устройстваГ а выход череа 00 коммутатор соединен с третьей вход I ной кпбймой устройства.

PU8.S.

| I | |||

| Устройство для измерения сопротивления резисторов образующих замкнутую цепь | 1978 |

|

SU718804A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения сопротивления резисторов,образующих замкнутую цепь | 1978 |

|

SU771567A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-10-15—Публикация

1983-06-27—Подача