Изобретение относится к измерению электрических величин, в частности к измерению .элементов цепей с сосредоточенными постоянными, и может быть использовано для быстродействующего автоматического контроля радиокомпонентов радиоэлектронных схем, собранных на печатных платах в условиях массового производства.

Цель изобретения - повышение быстродействия за счет сокращения числа тактов измерения.

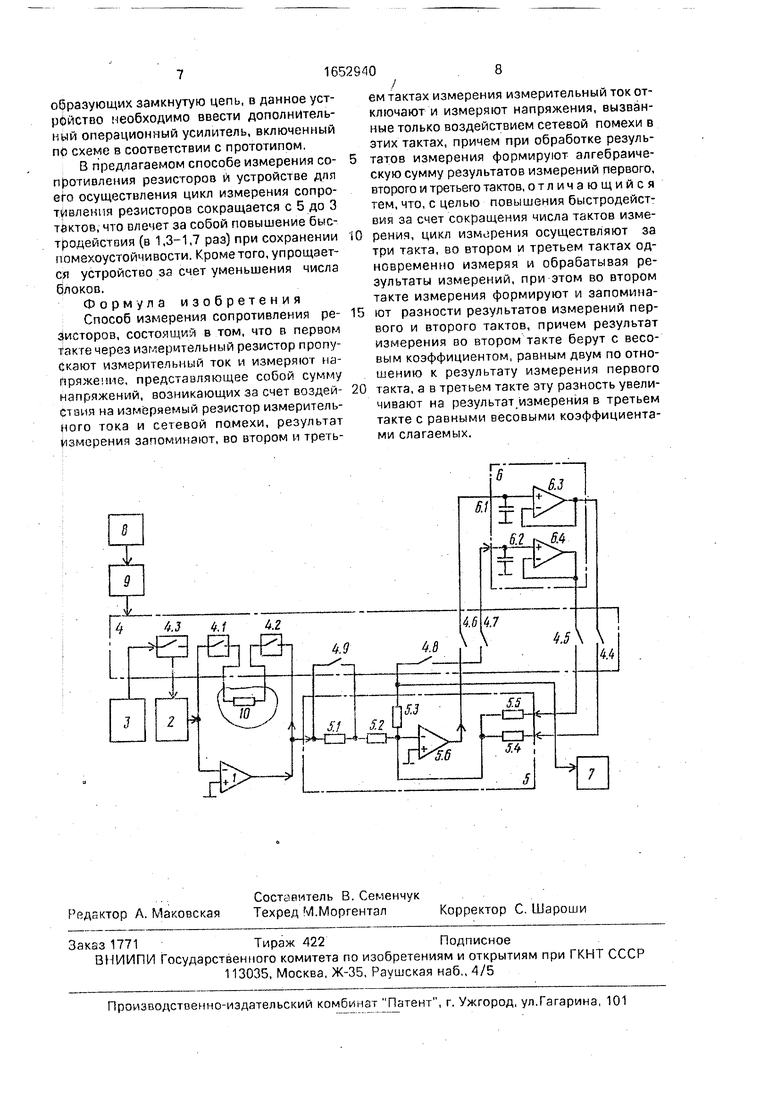

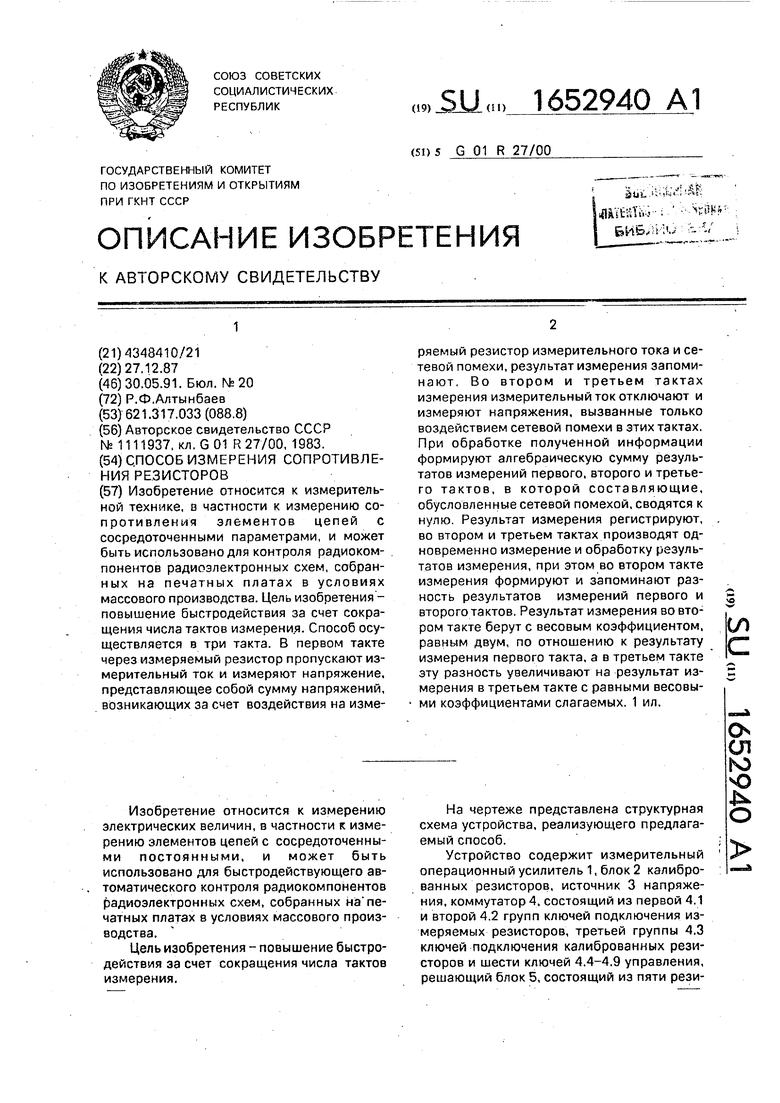

На чертеже представлена структурная схема устройства, реализующего предлагаемый способ.

Устройство содержит измерительный операционный усилитель 1, блок 2 калиброванных резисторов, источник 3 напряжения, коммутатор 4, состоящий из первой 4.1 и второй 4.2 групп ключей подключения измеряемых резисторов, третьей группы 4.3 ключей подключения калиброванных резисторов и шести ключей 4.4-4.9 управления, решающий блок 5, состоящий из пяти резиONСЛ

ГО

ю

4 О

сторов 5.1-Ь,5 и операционного усилителя 5.6, двухканальный блок 6 оперативной памяти (состоящий из конденсаторов б 1 и 6.2 и покорителей 6.3 и 6.4 напряжения), блок 7 регистрации, блок 8 программ, блок 9 уп- раоления; 10 - объект измерения(измеряемый резистор).

Вход и выход измерительного операционного усилителя 1 через первую 4,1 и вторую 42 группы ключей подключения соединены с измзряемым резистором 10, вход измерительного операционного усилителя 1 подключен к выходу блока 2 калиброванных резисторов, вход которого через третью группу 4.3 кпючей подключения коммутатора 4 соединен с выходом источника 3 напряжения.

Выход измерительного операционного усилителя 1 соединен с первым входом решающего блока 5. К второму и третьему водам решающего блока 5 через первый 4.4 и второй 4,5 ключи управления коммутатора 4 соответственно подключены выходы первого и второго каналов двухканального блока 6 оперативной памяти, входы первого и второго каналов которого соответственно через третий 4.6 и четвер(ый 4.7 ключи управления коммутатора 4 соединены с выходом решающего блока 5. Кроме того, выход решающего блока 5 через пятый ключ 4.0 коммутатора 4 соединен с входом блока 7 режстрации. Выход блока 8 программ соединен с входом управления коммутатора 4 через блок 9 управления,

Порзый вход решающего блока 5 соединен с входом операционного усилителя 5.6 через последогптелыю соединенные резисторы 5.1 и 5.2 i; воды резистора 5.1 соединены с выводами ключа 4.9. Такое построение решающего блока 6 позволяет изменять весовые коэффициенты слагаемых по первому входу решающего блока 5 по отношению к слагаемым второго и третьего входов.

Устройство работает следующим образом

Блок 8 программ задает очередность проверки резисторов объекта 10 измерения. Сигналы управления с блока 8 программ поступают на блок 9 управления, который управляет очередностью работы каждого из блоков устройства. При этом сигналы управления с блока 9 управления поступают на коммутатор 4, который подключает измеряемый резистор 10 в цепь отрицательной обратной связи измерительного операционного усилителя 1 с помощью первой 4 1 и второй 4.2 групп ключей подключение.В зависимости от необходимого 1члодел измерения одновременно к входу

измерительного операционного усилителя1 подключается калиброванный резистор из блока 2 калиброванных резисторов с помощью третьей группы 4.3 ключей подклю- чения.

Цикл измерения состоит из трех тактов одинаковой длительности. В первом такте первый 4,4 и третий 4.6 ключи управления замкнуты, а второй 4.5, четвертый 4,7, пятый 4.8 и шестой 4.9 ключи управления разомкнуты. При этом на выходе источника 3 напряжения вырабатывается напряжение UL

На вход измерительного операционно- го усилителя 1 через калиброванный резистор блока 2 поступают напряжение Ui и напряжение 1)2 сетевой помехи, наводимой на соединительных линиях.

Под воздействием этих составляющих (Ui + 1)2) на выходе измерительного операционного усилителя 1 в первом такте возникает напряжение Уз

(u,+u4b (D

где RX - сопротивление измеряемого резистора;

RK сопротивление калиброванного резистора на входе измерительного операци- онногоусилителя 1;

Ui - напряжение на входе измерительного операционного усилителя 1,создаваемое источником 3 напряжения;

U2 - напрчя ение на входе измеритель- ною операционного усилителя 1, создаваемое помехой.

При этом через измеряемый резистор 10 протекает измерительный ток И, равный

U 3 R

и ток 12, вызванный сигналом сетевой помехи,

45

3 { Ч Rk

Напргжение l)V поступает на первый решающего блока 5. Значения сопротивлений резисторов 5.1-5 5 (Rs r Rs s) решающего блока 5 выбраны следующим образом:(2)

.2eT RS,3 R5,5-R

Так как первый ключ 4.4 управления

коммутатора 4 замкнут, а ключи 4.5, 4.8 и 4,9

разомкнуты, то на выходе решающего блока

5 в первом такте получает напряжение LM1,

равное

R

5 ±

R 5 Ч 57

или с учетом соотношений (1) и (2)

u 4-и з

Я,

R,

W

(U. + u,, i- к

Поскольку третий ключ 4.6 управления замкнут, четвертый ключ 4.7 разомкнут, то напряжение U41 поступает на первый канал двухкапального блока 6 оперативной памяти и запоминается гам (до этого напряжения заряжается конденсатор 6 1 блока 6). На этом первый тркт заканчивается.

Во втором такте третий 4.6 и пятый 4,8 ключи управления коммутатора 4 разомкнуты, а первый 4.4, второй 4.5, четвертый 4.7 и шестой 4.9 ключи управления замкнуты. При этом напряжение Ui на выходе источника 3 напряжения равно нупю, в результл- те чего измерительный ток И, протекающий через измеряемый резистор 10, также равен нулю. На входе измерительного операцией- ного усилителя 1 присутствует только напряжение сетевой помехи. Поэтому на выходе измерительного операционного усилителя 1 во втором такте образуется напряжение Уз , равь

Li

Ь

R,

ий + Я),

(4)

где LJ2 - напряжение сетевой помехи в первое такте измерения;

5- приращение помехи во втором такте измерения, обусловленное ее sin-характером.

Напряжение Ua с выхода измерительного операционного усилителя 1 поступает на первый вход решающего блока 5. На второй вход решающего блока 5 поступает напряжение с выхода первого канала блока боперативной памяти через замкнутый первый 4.4 ключ управления коммутатора 4. Величина этого напряжения равна напряжению на накопительном конденсаторе 6.1 блока 6 и определяется по формуле (3). Так как замкнуты также второй 4.5, четвертый 4.7 и шестой 4.9 ключи управления коммута- тора 4, то напряжение Щ на выходе реша- юшего блока 5 во втором такте равно

S.5

IJ4-R

5.5

S 2

5.4

или с учетом соотношений по формулам (2). (3) и (4)

( + Ue)(Ue + ,)55

Напряжение 1Ц2 с выхода решающего блока 5 поступает на вход второго канала двухканального блока 6 оперативной памя

5 10

15 20 ти и запоминается там (до этого напряжения заряжается конденсатор 6.2 второго канала 5покгч г-;. На атом второй такт заканчивается. С третьем такте первый 4.4, третий 4.6, четвертый 4.7 и шестой 4.9 ключи управления коммутатора 4 разомкнуты, а второй 4.5 и пятый 4 8 - замкнуты. При этом напряжение но выход 3 источника 3 напряжения равно нулю. На измерительного операционного усилителя 1 присутствует только напряжение сетевой помехи

. Д f 8t ,

где ( Ц + д ) - напряжение сетевой помехи во втором такте:

д-|- приращение помехи в третьем такте.

На выходе измерительного операционного усилителя 1 образуется напряжение Уз . оавное

(6)

u .

R

Напряжение Уз поступает на первый вход решающего блока 5. На третий вход решающего блока 5 через замкнутый второй ключ 4.5управления коммутатора 4 поступает напряжение с выхода второю канала двухканального блока 6 оперативной памяти, величина которого опеределяется по формуле (5). Поэтому напряжение на выходе решающего блока 5 в третьем такте равно

U43-rR

UsR5,, 4 .3

5., + R5.2

R,

Поставляя значения величин из формул (2), (5) и (6), получаем

uj-r-ftvs-j,). оо

к

Поскольку длительности тактов равны, то приращение помехи во втором такте д можно принять равным приращению помехи в третьем такте di т.е. д 5i и, следов тельно,

R

u. -n-u,

кк

4

Таким образом, влияние помехи на измерение устранено.

Напряжение LM , пропорциональное величине сопротивления измеряемого резистора, через замкнутый пятый ключ 4.8 управления коммутатора 4 поступает на вход блока 7 регистрации.

В данном устройстве измеряемые рези сторы не образуют замкнутую цепь. В случае измерения сопротивления резисторов,

образующих замкнутую цепь, в данное устройство необходимо ввести дополнительный операционный усилитель, включенный по схеме в соответствии с прототипом.

В предлагаемом способе измерения сопротивления резисторов и устройстве длл его осуществления цикл измерения сопротивления резисторов сокращается с 5 до 3 тактов, что олечег за собой повышение быстродействия (в 1,3-1,7 раз) при сохранении помехоустойчивости. Кроме того, упрощается устройство за счет уменьшения числа блоков.

Формула изобретения Способ измерения сопротивления резисторов, состоящий в том, что в первом такге через измерительный резистор пропускают измеритепьный ток и измеряют nd- пряжечие, представляющее собой сумму напряжений, возникающих за счет воздействия на измеряемый резистор измерительного тока и сетевой помехи, результат измерения запоминают, во втором и трегьем тактах измерения измерительный ток отключают и измеряют напряжения, вызванные только воздействием сетевой помехи в этих тактах, причем при обработке результатов измерения формируют алгебраическую сумму результатов измерений первого, второго и третьего тактов, отличающийся тем, что, с целью повышения быстродействия за счет сокращения числа тактов измерения, цикл измерения осуществляют за три такта, во втором и третьем тактах одновременно измеряя и обрабатывая результаты измерений, при этом во втором такте измерения формируют и запоминают разности результатов измерений первого и второго тактов, причем результат измерения во втором такте берут с весовым коэффициентом, равным двум по отношению к результату измерения первого

такта, а в третьем такте эту разность увеличивают на результат измерения в третьем такте с равными весовыми коэффициентами слагаемых.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения сопротивления резисторов,образующих замкнутую цепь | 1983 |

|

SU1118937A1 |

| Аналого-цифровой преобразователь сопротивления | 1983 |

|

SU1108369A1 |

| Устройство для измерения температуры | 1986 |

|

SU1362951A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЭЛЕКТРОКОЖНОГО СОПРОТИВЛЕНИЯ ТОЧЕК АКУПУНКТУРЫ, УСТРОЙСТВО ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА И ЕГО ВАРИАНТЫ | 2001 |

|

RU2268643C2 |

| Устройство для измерения отклонения сопротивления от заданного значения | 1986 |

|

SU1536322A1 |

| Преобразователь толщины в интервал времени | 1987 |

|

SU1441178A1 |

| Устройство для измерения относительной погрешности делителей тока | 1983 |

|

SU1150579A1 |

| Устройство для измерения сопротивления | 1984 |

|

SU1239608A1 |

| Преобразователь сигнала тензомоста в интервал времени | 1987 |

|

SU1580260A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИЗМЕНЕНИЯ СОПРОТИВЛЕНИЯ РЕЗИСТИВНЫХ ДАТЧИКОВ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 2005 |

|

RU2292051C2 |

Изобретение относится к измерительной технике, о частности к измерению со- противленич элементов цепей с сосредоточенными параметрами, и может быть использовано для контроля радиокомпонентов радиоэлектронных схем, собранных на печатных платах в условиях массового производства. Цель изобретения - повышение быстродействия за счет сокра- щенич числа тактов измерения. Способ осуществляется в три такта. В первом такте через измеряемый резистор пропускают измерительный ток и измеряют напряжение, представляющее собой сумму напряжений, возникающих за счет воздействия на измеряемый резистор измерительного тока и сетевой помехи, результат измерения запоми- нают. Во втором и третьем тактах измерения измерительный ток отключают и измеряют напряжения, вызванные только воздействием сетевой помехи в этих тактах. При обработке полученной информации формируют алгебраическую сумму результатов измерений первого, второго и третьего тактов, в которой составляющие, обусловленные сетевой помехой, сводятся к нулю Результат измерения регистрируют, во втором и третьем тактах производят одновременно измерение и обработку результатов измерения, при этом во втором такте измерения формируют и запоминают разность результатов измерений первого и второго тактов Результат измерения во втором такте берут с весовым коэффициентом, равным двум, по отношению к результату измерения первого такта, а в третьем такте эту разность увеличивают на результат измерения в третьем такте с равными весовыми коэффициентами слагаемых. 1 ил. сл С

L.

| Промысловое судно-катамаран | 1983 |

|

SU1111937A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-30—Публикация

1987-12-27—Подача