разряда которого подключен к управляющему входу регистра сдвига и первому входу первого элемента И-НЕ, выход которого подключен к входу установки в ноль триггера, второй выход генератора тактовых импульсов подключен к управляющему входу двоичного счетчика, выход первого разряда которого подключен к второму входу элемента ИЛИ, выход которого подключен к управляющему входу блока памяти, выход триггера подключен к входу обнуления двоичного счетчика, информационный выход которого подключен к информационному входу первого коммутатора, управляющий вход которого подключен к информационному выходу регистра сдвига,инверсный инфор; мащюнный выход которого подключен к первому входу сумматора,выход которого

подключен к адресному входу блока постоянной памяти и информационному вхо- ду регистра, информационный выход которого подключен к второму входу сумматора, третий выход генератора тактовых импульсов подключен к первому входу второго элемента И-НЕ,

второй вход которого соединен с вторым входом первого элемента И-НЕ и подключен к информационному выходу второго коммутатора, информационные входы которого соответственно соединены с выходами k 41 старших разрядов регистра сдвига, инверсный информационный выход которого объединен с информационным выходом второго коммутатора, выходом второго элемента И-НЕ и подключен к управляющему входу второго коммутатора управления, информационный выход которого подключен к первому информационному входу коммутатора режима, второй информационный вход которого подключен к информационному выходу первого коммутатора управления, управляющий вход которого является входом задания формата устройства и соединен с управляющим входом коммутатора и управляющим входом второго коммутатора блока управления, информационньй выход первого коммутатора которого подключен к информационному входу второго коммутатора управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрого преобразования Фурье последовательности с нулевыми элементами | 1983 |

|

SU1119025A1 |

| Многоканальное устройство для быстрого преобразования Фурье с конвейерной обработкой операндов | 1984 |

|

SU1211752A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1982 |

|

SU1056207A1 |

| Устройство для реализации двумерного быстрого преобразования фурье | 1983 |

|

SU1142845A1 |

| Устройство для реализации быстрого преобразования Фурье | 1984 |

|

SU1233166A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

УСТРОЙСТВО ДЛЯ РЕАЛИЗАЦИИ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ ПРИ МНОГОКАНАЛЬНОЙ ОБРАБОТКЕ ИНФОРМАЦИИ, содержащее блок управления, входной коммутатор, информационный нмход которого подключен к информационному входу блока памяти, информационный выход которого подключен к информационному входу арифметического блока, инф рмационный выход которого является информационным выходом устройства и подключен к первому информационноку входу входного коммутатора, второй информационный вход которого является информационным входом устройства, триггер, выход которого подключен к управляющим входам входного коммутатора и коммутатора режима, информационный выход которого подключен к адресному входу блока памяти, счетчик, информационный выход блока по.стрянной памяти подключен к входу задания коэффициента арифметического блока, отлича ющеес я тем. что, с целью расширения области применения за счет пространственной обработки сигналов с переменным числом каналов и переменной длиной выборки, в него введены первый и второй коммутаторы управления, блок стековой памяти, элемент ИЛИ, коммутатор, счетчик стека, блок сравнения и счетчик , информационными выход которого подключен к первому входу блока сравнения, выход которого подключен к первому входу элемента ИЛИ и тактовому входу счетчика стека, информационный выход которого подключен к управляющему входу блока S (Л стековой памяти и первому информационному входу первого коммутатора управления, второй информационный, вход которого подключен к информационному выходу счетчика, выходы k+1 (k - число каналов) старших разрядов которого подключены соответственно к информационным входам коммутатора, информационный выход которого подключен ко входу установки в N9 единицу триггера, тактовый вход счет4 чика соединен с тактовым входом счетиэ чика канапов и является тактовым входом устройства, второй вход блока SD сравнения подключен к информационно му выходу блока стековой памяти,-информационный вход которого является входом задания номеров обрабатываемых каналов устройства, причем блок управления содержит первый и второй элементы И-НЕ, сумматор, регистр, первый и второй коммутаторы, регистр сдвига, двоичный счетчик и генератор тактовых импульсов, первый выход которого подключен к счетному входу двоичного счетчика, выход старшего

Изобретение относится к вычислительной технике, в частности к устройствам для спектрального анализа, и может быть использовано при решении задач прс.странственно-временной обработки сигналов. Известно устройство для реализаци быстрого преобразования Фурье (ВПФ), содержащее оперативную память, арифметический блок, постоянную память и блок управления, первый и второй выходы которого подключены к адресным входам соответственно блоков опе ративной и постоянной памяти, выходы которых подключены соответственно к входам операндов и коэффициентов арифметического блока, третий выход блока управления подключен к входу синхронизации арифметического блока, выход которого подключен к информационному входу блока оперативной памяти 1 j . Недостатком устройства являются ограниченныефункциональные возможности при определении спектров сигналов с неизвестной стационарностью из-за фиксированного числа каналов и объема обрабатываемых массивов. Наиболее близким к предлагаемому по технической сущности является устройство для реализации безизбыточного а лгоритма Б1М, содержащее арифметический блок, блок постоянной памяти, два блока оперативной памяти, блок управления, причем выходы блока постоянной памяти соединены соответственно с вторым и третьим входами арифметического блока, выход которого подключен к второму входу первого блока оперативной памяти, а первый, второй и третий выходы блока управления соединены с первыми входами соответственно блоков оперативной памяти, арифметического блока и блока постоянной памяти, кроме того, выход

второго блока оперативной памяти соединен с вторым входом арифметического блока, выход которого подключен к второму входу второго блока оперативной памяти, первые и третьи входы которого соединены соответственно с шестым и пятым выходами блока управления , четвертый выход которого подключен к тре; ьему входу первого блока оперативной памяти. Данное уст ройство обрабатывает четыре действиГ Т

тельных массива 21 .

Недостатком данного устройства является ограниченная область применения из-за фиксированной длины вход ной выборки и малого числа каналов при обработке многоканальных сигналов с меняющейся стационар нос т ы;р и временем существования, например сигналов по лучам диаграммы направленности антенной решетки.

Цель изобретения - расширение области применения за счет пространственной обработки сигналов с переменным числом каналов и переменной длиной выборки.

Поставленная цель достигается тем что в устройство для реализации быстрого преобразования Фурье при. многоканальной обработке информации, содержащее блок управления, входной коммутатор, информационный выход которого подключен к информационному входу блока памяти, информационный выход которого подключен к информаци онному входу арифметического блока, информационный выход которого является информационным выходом устройства и. подключен к первому информационному входу входного коммутатора, второй информационный вход которого является ннформахщонным входом устройства, триггер, выход которого подклю ген к управлякжим входам входного коммутатора и коммутатора режима, информационный выход которого подклю чен к адресному входу блока памяти, счетчик, информационный выход блока постоянной памяти подключен к входу задания коэффициента арифметического блока, введены первый и второй коммутаторы управления, блок стековой памяти, элемент ИЛИ, коммутатор, счетчик стека, блок сравнения и счетчик каналов, информационный выход котррого подключен к первому входу блока сравнения, выход которого подключен к первому входу элемента ШШ

и тактовому входу счетчика стека, информационный выход которого подключен к управляющему входу блока стековой памяти и первому информационному входу первого кo Iмyтaтopa .управления, второй информационный вход которого подключен к информационному выходу счетчика, выходы k +1(k число каналов) старших разрядов которого подключены соответственно к информационным входам коммутатора, информационный выход которого подключен к входу установки в единицу

триггера, тактовый вход счетчика соединен с тактовым входом счетчика каналов и является тактовым входом устройства, .второй вход блока сравнения подключен к информационному выходу блока стековойпамяти, информационный вход которого является входом задания номеров обрабатываемых каналов устройства, причем блок управления содержит первый и второй элементы И-НЕ, сумматор, регистр, первый и второй коммутаторы, регистр сдвига, двоичный счетчик и генератор тактовых импульсов, 1Тервый выход которого подключен к счетному входу двоичного счетчика, выход старшего разряда которого подключен к управляющему входу регистра сдвига и первому входу первого элемента И-НЕ, выход которого подключен к входу установки в ноль триггера, второй выход генератора тактовых импульсов подключен к управлякидему входу двоичного счетчика, выход первого разряда которого подключен к второму входу элемента ИЛИ, выход которого подключен к управляющему входу блока памяти, выход триггера подключен к входу обнуления двоичного счетчика, информационный выход которого подключен к информационному входу первого коммутатора, управляющий вход которого

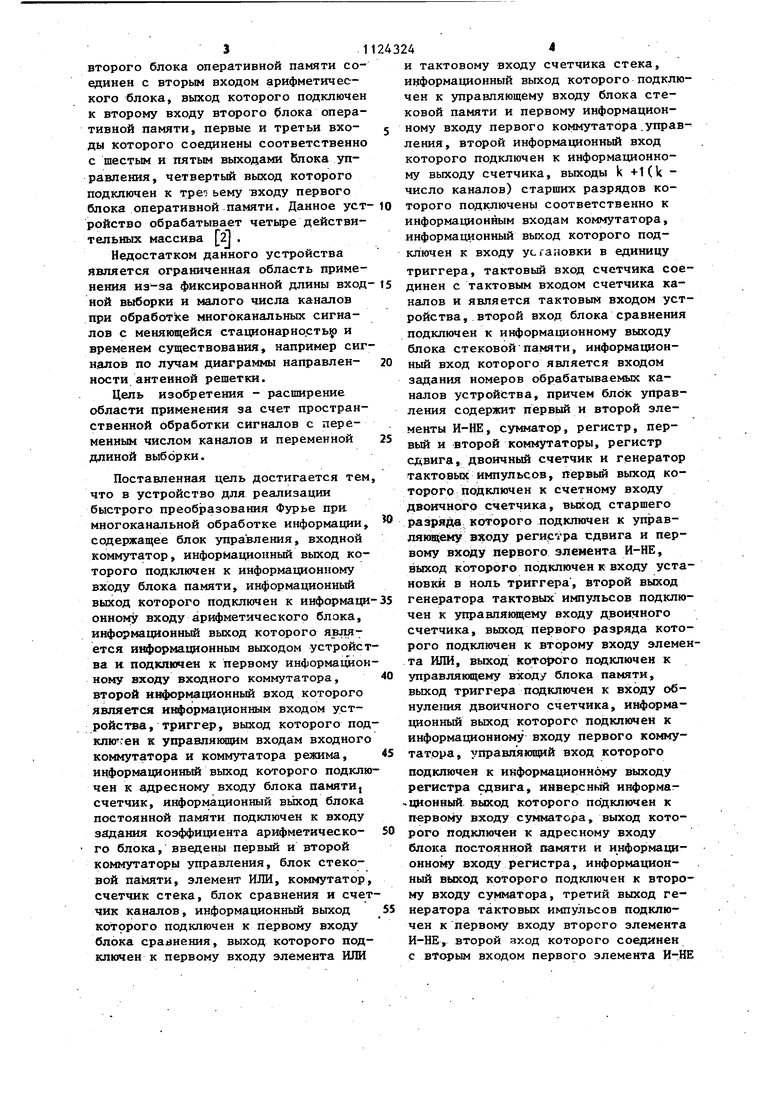

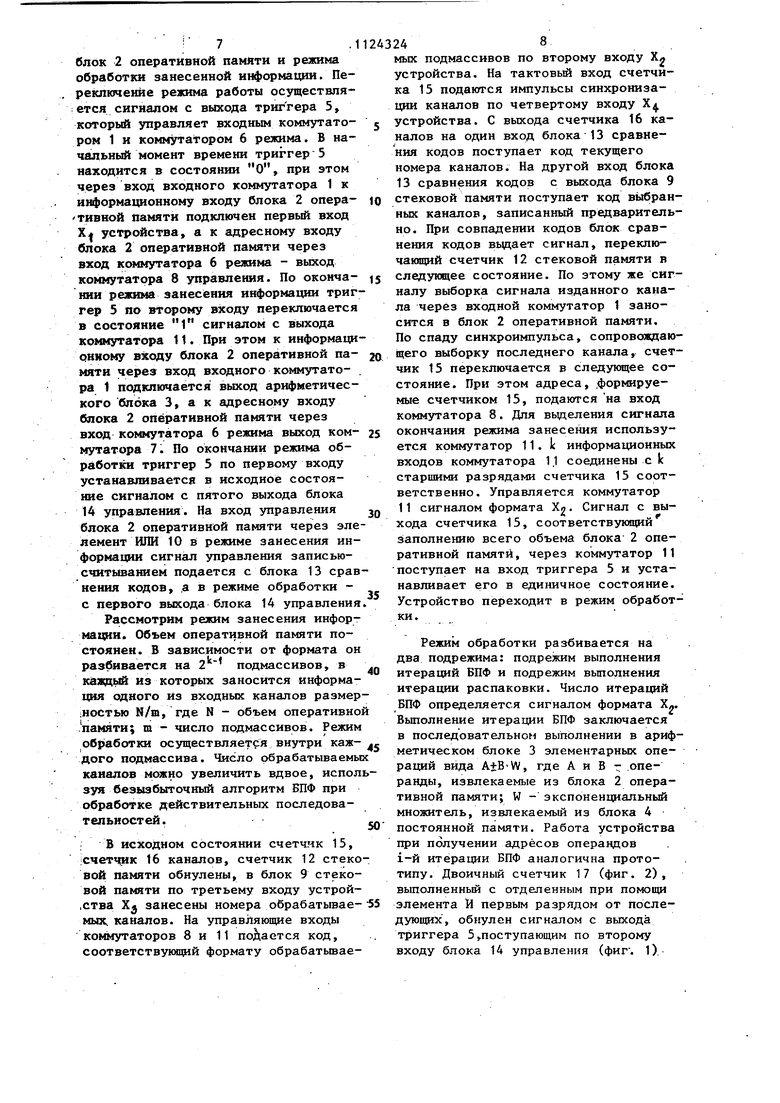

подключен к информационному выходу регистра сдвига, инверснь1й информа-иионный выход которого подключен к п-ервому входу сумматора, выход которого подключен к адресному входу блока постоянной памяти и информационному входу регистра, информационный выход которого подключен к второму входу сумматора, третий выход генератора тактовых импульсов подключен к первому входу второго элемента И-НЕ, второй зход которого соединен с вторым входом первого элемента И-НЕ И подключен к информационному выходу :второго коммутатора, информационные входы которого соответственно соедине ш с выходами k +1 старших разрядов регистра сдвига, инверсный инфор мационный выход которого объединен с информащюнным выходом второго кой мутатора, выходом второго элемента И-НЕ и подключен к управлякяцеь1у вхо;ду второго ко№1 утатора управления, информационный выход которого подклю чен к первому информационному входу коммутатора режима, второй информационнь вход которого подключен к информационному выходу первого комму татора управления, управлякпций вход которого является входом эа цания формата устройства и соеданен с уп- равляющим входом коммутатора и управ ляющим входом второго коммутатора .блока управления, информао ионный выход первого коммутатора которого под ключен к информахщонному входу второ го коммутатора управления. На фиг. 1-4 приведены функциональ ные схемы предлагаемого устройства, блока управления, первого и второго управляемых коммутаторов соответственно. . . Устройство для реализации БПФ при многоканальной обработке информации (фиг. 1) содерлшт входной коммутатор 1., блок 2 оперативной памяти, тический блок 3, блок 4 постоянной памяти, триггер 5, коммутатор 6 ре жима коммутатор 7 управления, комму татор 8 управления, блок 9 стековой памяти, элемент ИЛИ 10, коммутатор 11, счетчик 12 стека, блок . 13 сравне ния кодов, блок 14 зправления, счетчик 15, счётчик 16 каналов. Блок управления (фиг. 2) содержит двоичный счетчик 17, коммутатор 18, генератор 19 тактовых импульсов, :регистр 20 сдвига, сумматор 21, регистр 22, коммутатор 23, два элемента И-НЕ 24 и 25. i bMMyTaTop 8 управления (фиг. 3) выполнен на базе коммутаторов на .k+1 канал, где k - число обрабатывае мых каналов, причем число коммутаторов равно числу разрядов счетчика 15 С помощью коммутатора в зависимости от выбранного числа обрабатываемых каналов входная информация группируется в группу при занесении в блок оперативной памяти, причем внут ри каящой группы информация заносятся в двоично-инв ерсном порядке. Достигается это тем, что адреса, формирующиеся счетчиком 15, передаются на выход коммутатора 8 двоично-инвертированными и сдвинутыми на k разрядов в сторону младших разрядов. На место освободившихся старших разрдцов подключаются k разрядов счетчика стека (фиг. 3). Коммутатор-7 управления (фиг. .4) содержит группу 26 элементов И, группу 27 коммутаторов на два канала, группу 28 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и предназначен для формирования адресов операндов при выполнении итерации распаковки, необходимой для реализации беэызбыточного алгоритма БПФ. По второму входу Ху на первые входы элементов ЖКШЧАЮЩЕЕ ИЛИ группы 28 с второму выхода У} блока 14 управления подаются сдреса. При выполнении итерац §и БШ на вторые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы 28 подается сигнал 1, а на управлянщие входы коммутаторов на два канала группы 27 - сигнал О. При этом осуществляется прямая передача адресов с блока 14 зптравления на вьосод УТ коммутатора. Для формирования адресов операндов при итерации распаковки, являющейся последней, с третьего выхода У блока 14 управления на первый вход У коммутатора 7, представляющий собой вторые входы элементов И, подается сигнал 1. Первые входы элементов И группы 26 подключены к инверсным выходам регистра 20 сдвига от (n-k+1)-ro разряда до (п+1)-го. Число элементов . И группы 26 равно k. В зависимости от выбранного формата массивов обработки веделяется старший разряд . адреса. При выполнении итерации распаковки из одного адреса формируются два: прямой и дополнительный и осуществляется сдвиг старших разрядов адреса, начиная с (п-|{-1)-го до (n-l)-ro в сторону старших разрядов на один разряд. Сдвиг осуществляется к коммутаторами на два канала, управляющими сигналами 1, поступающими с выходов группы 26 элементов на управляющие входы коммутаторо1в На два канала группы 27. Устройство работает следующим образом. Цикл работы состоит из двух режимов: режима занесения информации в

блок 2 оперативной памяти и режима обработки занесенной информации. Переключение режима работы осуществляется сигналом с выхода триггера 5, который управляет входным коммутатором 1 и коммутатором 6 режима. В начальный момент времени триггер 5 находится в состоянии О, при этом через вход входного коммутатора 1 к информационному входу блока 2 оперативной памяти подключен первый вход Х| устройства а к адресному входу блока 2 оперативной памяти через вход коммутатора 6 режима - выход коммутатора 8 управления. По окончаНИИ режима занесения информации триггер 5 по второму входу переключается в состояние 1 сигналом с выхода коммутатора 11. При этом к информационному входу блока 2 оперативной памяти через вход входного коммутатора 1 подключается выход арифметического блока 3, а к адресному входу блока 2 оперативной памяти через вход коммутатора 6 режима выход коммутатора 7. По окончании режима обработки триггер 5 по первому входу устанавливается в исходное состояние сигналом с пятого выхода блока 14 управления. На вход управления блока 2 оперативной памяти через элелемент ШШ 10 в режиме занесения информации сигнал управления записьюсчитыванием подается с блока 13 сравнения кодов, а в режиме обработки с первого выхода блока 14 управления Ра1ссмотрим режим занесения информации. Объем оперативной памяти постоянен. В зависимости от формата он разбивается на 2 подмассивов, в каждый из которых заносится информация одного Из входных каналов размер;ностью N/m, где N - объем оперативно .памяти; ш - число подмассивов. Режим обработки осуществляется внутри каждого подмассива. Число обрабатываемы каналов Можно увеличить вдвое, исползуя беэызбыточный алгоритм БПФ при обработке действительных последовательностей,

; В исходном состоянии счетчик 15, 16 каналов, счетчик 12 стековой памяти обнулены, в блок 9 стековой памяти по третьему входу устройства Х занесены номера обрабатываемых, каналов. На управляющие входы коммутаторов 8 и 11 подается код, соответствующий формату обрабатьтаемых подмассивов по второму входу Хл устройства. На тактовый вход счетчика 15 подаются импульсы синхронизации каналов по четвертому входу Х устройства. С выхода счетчика 16 каналов на один вход блока13 сравнения кодов поступает код текущего номера каналов. На другой вход блока 13 сравнения кодов с выхода блока 9 стековой памяти поступает код выбранных каналов, записанный предварительно. При совпадении кодов блок сравнения кодов выдает сигнал, переключающий счетчик 12 стековой памяти в следующее состояние. По этому же сигналу выборка сигнала изданного канала через входной коммутатор 1 заносится в блок 2 оперативной памяти. По спаду синхроимпульса, сопровождающего выборку последнего канала, счетчик 15 переключается в следующее состояние. При этом адреса, .формируемые счетчиком 15, подаются на вход коммутатора 8. Для выделения сигнала окончания режима занесения используется коммутатор 11. k информационных входов коммутатора 1.1 соединены с k старшими разрядами счетчика 15 соответственно. Управляется коммутатор 11 сигналом формата Xg. Сигнал с выхода счетчика 15, соответствующий заполнению всего объема блока 2 оперативной памяти, через коммутатор 11 поступает на вход триггера 5 и устанавливает его в единичное состояние. Устройство переходит в режим обработки .

Режим обработки разбивается на два подрежима: подрежим выполнения итераций БПФ и подрежим выполнения итерации распаковки. Число итераций БПФ определяется сигналом формата X. Выполнение итерации БПФ заключается в последовательнои выполнении в арифметическом блоке 3 элементарных операций вида A±BW, где А и В г операнды, извлекаемые из блока 2 оперативной памяти; W - зкспоненхщальный множитель, извлекаемый из блока 4 постоянной памяти. Работа устройства при получении адресов операндов i-й итерации БПФ аналогична прототипу. Двоичный счетчик 17 (фиг. 2), выполненный с отделенным при помощи элемента И первым разрядом от последующих, обнулен сигналом с выхода триггера 5 поступающим по второму входу блока 14 управления (фиг. 1). 9 в регистр 20 сдвига (фиг, 2). Во все разряды от 1-го до i-ro занесен потенциал 1, а в остальные от (i+1)го до (n + D-ro - потенциал О. Коммутатор 18 выполнен на базе коммутаторов на три канала. Связи коммутатб ра 18 с двоичным счетчиком 17 и регистром 20 сдвига организованы следукицим образом. Первые информахщонные входы ксжмутаторов соединены с выходом первого разряда двоичного счетчика 17, казедый j-и разряд двоич ного счетчика 17 соединен с вторым информационным входом j-ro коммутатора, каждый третий информационный вход j-ro коммутатора соединен с (j+1)-M разрядом двоичного счетчика Управляющие вхо; -го коммутатора соединены с выходом j-го и (j+1)-ro разряда регистра 20 сдвига. При пода че на управлякнцие входы коммутаторов двух потенциалов О на выход j-го коммутатора передается информация с второго информационного входа, при подаче потенциалов О и 1 информация с первого информационного входа, при подаче потенциалов 1, 1 - информация с третьего входа. На счетный вход двоичного счетчика 17 с генератора 19. тактовых импульсов поступают къшупъсы обращения к блоку 2 оперативной памяти. Сигнал с второго выхода двоичного счетчика 17, представляняций.собой выход стар:шего .разряда счетчика, сдвигает потенциал 1 в регистре 20 сдвига в сторону старпшх разрядов после выполнения очередной итерации ВПФ. Для реализации алгоритма БПФ с заме щением на вход элемента И, отделяющего младший разряд двоичного счетчи ка 17 от старших, с генератора 19 подается сигнал Ввод-вывод. При потенциале О сигнала Вывод элемент И блокирует перенос информации во второй разряд двоичного счетчика 17, при этом на выходе коммутатора 7 формируются адреса операндов, выбираемых из блока 2 оперативной памяти. При потенциале 1 сигнала Ввод элемент И разрешает йеренос информации с младшего разряда двоичного счетчика 17 в следующий разряд При этом на выходе коммутатора 7 формируются адреса занесения результатов вычислений итераций БПФ, которые совпадают с адресами выбранных операндов. 2410 Одновременно с формированием адресов операндов, выбираемых из блока 2 оперативной памяти,.формируются и адреса для выбора коэффициентов из блока 4 постоянной памяти. Для этого предназначен накапливающий сумматор, реализованный на сумматоре 21 и регистре 22 хранения. После вьшолнения последней итерации БПФ осуществляется итерация распаковки, необходимая для реализации безызбыточного алгоритма БПФ. Для вьщеления сигнала конца последней итерации ВПФ предназначен коммутатор 23 с k +1 информационными входами, которые соединены с k +1 старшими разрядами регистра 20 сдвига соответственно. Управляется коммутатор 23 сигналом формата Х. После выполнения последней итерации БПФ сигнал 1 с выхода коммутатора 23 поступает на первый вход элемента И-НЕ 24 и разрешает прохождение синхросигнала по второму входу этого элемента с генератора 19. При состоянии синхросигнала 1 формируются прямые адреса операндов в коммутаторе 7, при состоянии синхросигнала О дополнительные коды для выбора второ го операнда, которые необходимы для выполнения безызбыточногр алгоритма БПФ. Одновременно потенциал 1 с выхода коммз атора 23 подается по входу коммутатора 7 на вторые входы элементов И группы 26 элементов И. В зависимости от сигнала X л переключаются соответствующие коммутаторы на два канала группы 27, при этом происходит распаковка следующего подмассива. Во время выполнения итерации распаковки на вход элемента И-НЕ 25, предназначенного для формирования сигнала окончания итерации распаковки, подается 1, После проведения итерации распаковки сигнал с выхода двоичного счетчика 17 через элемент И-НЕ 25 по первому входу переключает триггер 5 в состояние О . На этом устройство прекращает работу. Предлагаемое устройство позволяет расширить область применения при обработке множества сигналов с неизвестным временем существования за счет возможности изменения числа обрабатываемых каналов и размерности (

II11243242

массивов обрабатываемых выборок сиг- характеристик при наличии движущегося налов. Примером такой обработки источника шума по лучам диаграммы может служить получение спектральных направленности антенной решетки.

иг.1

IPU9,3

Фиг. 2

АдреonepamifВной пасчетчика стека

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для реализации быстрогопРЕОбРАзОВАНия фуРьЕ | 1979 |

|

SU809198A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельств.о СССР | |||

| Устройство для реализации безызбыточного алгоритма быстрого преобразования Фурье | 1981 |

|

SU1056206A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-15—Публикация

1983-07-04—Подача