указанного элемента ИЛИ, а элемент ИЛИ-НЕ н элемент ИЛИ узла логической памяти снабжены третьими входами, причем выход формирователя импульсов перегрузки через последовательно включенные диод и вторую интегрирующую цепь подключен к третьему входу элемента ИЛИ-НЕ, второму входу элемента ИЛИ дополнительного узла повторного включения и первому входу элемента И узла логической памяти, второй вход которого подсоединен к выходу интегрирующей цепи узла логической задержки и первому входу элемента И, второй

вход которого совместно с третьим входом элемента ИЛИ дополнительного узла повторного включения подсоединен к выходу элемента ИЛИ основного узла повторного включения, выход элемента И подсоединен к третьему входу элемента ИЛИ узла логической памяти, второй вход элемента И дополнительного узла повторного; включения соединен с выходом элемента НЕ узла логической задержки, выход элемента -ИЛИ дополнительного узла повторного включения соединен с вторым выводом диода узла логической задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1981 |

|

SU1046870A1 |

| Стабилизированный преобразователь напряжения с защитой | 1984 |

|

SU1201821A2 |

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1980 |

|

SU957380A1 |

| Стабилизированный преобразователь напряжения | 1987 |

|

SU1424106A1 |

| Стабилизированный транзисторный конвертор | 1977 |

|

SU736289A1 |

| Стабилизированный преобразователь постоянного напряжения | 1981 |

|

SU1001366A1 |

| Импульсный стабилизатор постоянного напряжения с программным управлением | 1987 |

|

SU1458865A1 |

| Преобразователь постоянного напряжения | 1981 |

|

SU1056390A1 |

| Источник питания с защитой от перегрузок по току и короткого замыкания | 1984 |

|

SU1191899A1 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ПОТРЕБИТЕЛЯ ОТ ПОВЫШЕННОГО И ПОНИЖЕННОГО НАПРЯЖЕНИЯ В СЕТИ ПЕРЕМЕННОГО ТОКА | 1998 |

|

RU2136097C1 |

СТАБИЖЗИРОВАИШЙ ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ С ЗАЩИТОЙ, содержа1ций генератор тактовых импульсов, подключенный к входу счетного триггера и одному их входов широтноюшульсного модулятора, другой вход которого через узел обратной связи подключен к выходной клемме и выходу выпрямителя с филь-Грюм, входом подсоединенного к выходу усилителя мощности, управляющие входы которого под шючены к выходам двух логических элементов И, при этом первые входы последних подключены к парафаэньм выходам счетного триггера, вторые объединенlOite входы подключены к выходу широтно-ютульсного модулятора, а третьи объединенные входа подсоединены к выходу блока зав(иты, включающего в себя элемент ШШ-НЕ, форьтрователи импульсов перегрузки и перенапряжения, основной узел повторного включения, выполненш) на двухвходовых элементах И и ИЛИ, причем выхо элемента И подключен к первому входу элемента ИЛИ, узел логической памяти, выполненный на двухвходовых элементах И и ИЛИ, причем выход элемента И подключен к первому входу элемента ИЛИ, выход которого подсоединен к его второму входу, узел логической задержки, выполненный на диоде, времязадающей интегрирующей цепи и элементе НЕ, причем первый вывод диода через времязадающую интегрирукицую цепь подсоединен к входу элемента НЕ, и перв5Ш интегрирующзто цепь, причем выход элемента ИЛИ-НЕ подкл1эчен к выходу блока заяциты, вход формирователя импульсов перегрузки подключен к выходу датчика перегрузки выпрямителя с фильтром, вход формирователя .импульсов перенапряжения соединен с выходной клеммой, а его выход через первую интегрирующую цепь подсоединен к второму входу элемента ШШ основного узла повторного включения, выход указанного элемента ИЛИ подклю-. чен к первому входу элемента ИЛИ-НЕ и первому входу элемента И этого же узла, второй вход элемента И подклю чен к выходу элемента НЕ узла логи: :0 ческой задержки, выход элемента ИЛИ узла логической памяти подключен к второму входу элемента ИЛИ-НЕ, о тличающийся тем, что, с целью повышения функциональной надежности, в него введены диод, вторая интегрирующая цепь, двухвходовой элемент И и дополнительный узел« повторирго включения, выполненный на трехвходовом элементе И1Ш и двухвходовом элементе И, причем выход элемента ИЛИ подключен к первому входу элемента И, выходом подключенного к первому входу

Изобретение относится к электротехнике и может быть использовано при разработке вторичных источников питания.

Известен стабилизированньш преобразователь напряжения с защитой, содержащий генератор тактовых импульсов, подключенный к входу счетного триггера и одному из входов ШИМа, другой вход которого через узел обратной связи подключен к выходу выпрямителя фильтром, установленным на выходе усилителя мощности, управляюпще входы которого поДключенЕ-i к выходам двух логических элементов И, при этом первые входы последних подключены к парафазным выходам счетного триггера, вторые объединенные - к выходу ШШа, а третьи объедиренш.1е - к выходу исполнительного элемента блока защиты с узлом логической задержки, и формирователями импульсов перегрузки и перенап ряжения, подключенными к входу узла повторного - включения, соединенного с входом исполнительного элемента О,

Недостатком известного устройства является невозможность при возникновении перенапряжения или перегрузо (к.з.) сразу же после включения преобразователя осуществлять автоматическое повторное включение ввиду необходимости предварительного заряд конденсатора первой интегрирующей цепи, что снижает быстрО7 ействие устройства.

Наиболее близким по технической сущности к изобретению является стабилизированный преобразователь напряжения с защитой, содержащий генератор тактовых импульсов, подключенный к входу счетного триггера и одному из входов ШИМа, другой вход которого через узел обратной , связи подключен к выходу выпрямителя с фильтром, установленным на выходе усилителя моп(ности, управляющие входы которых подключены к выходам двух логических элементов И,, при этом первые входы последних подключены к парафазным выходам счетного триггера, вторые объединенные - к выходу IMMa, а третьи объединенные к выходу исполнител1зного элемента блока защиты с узлом логической задержки и формирователями импульсов перегрузки и перенапряжения, подключенными к первому входу узла повторного включения, выходом соединенного с первым входом исполнительного элемента, при этом выход узла логическо задержки подключен к второму входу узла повторного включения и через введенный логический элемент НЕ к первому входу упомянутого узла/ логической памяти, причем второй вход последнего подключен к выходу узла повторного включения, а выход к второму входу исполнительного элемента 21.

Недостатком известного устройства является малое быстродействие автомагического повторного включения после возникновения перегрузок, что снижает его надежность.

Целью изобретения является повышение функциональной надежности. j

Поставленная цель достигается тем, что стабилизированный преобразователь напряжения с защитой, содержащий генератор тактовых импульсов, подключенный к входу счетного триг- 10 гера и одному из входов ШИМа, другой вход которого через узел обратной связи подключен к выходной клемме и выходу выпрямителя с фильтром, входом подсоединенного к выходу ij усилителя мощности, управляющие входы которого подключены к выходам двух логических элементов И, при этом первые входы последних подключены к парафазным выходам счетного тригге- 20 ра, вторые объединенные входы подключены к выходу ШИМа, а третьи объединенные входы подключены к выходу блока защиты, включающего в себя элемент ИЛИ-НЕ, формирователи им- 25 пульсов перегрузки и перенапряжения, основной узел повторного включения, выполненный на двухвходовых элементах И и ИЛИ, причем выход элемента И подключен к первому входу элемента 30 ИЛИ, узел логической памяти, выполненный на двухвходовых элементах И и ИЛИ, причем выход элемента И подключен к первому входу элемента ИЛИ, выход которого подсоединен к 35 его второму входу, узел логической

задержки, выполненный на диоде, времязадающей интегрирующей цепи и элементе НЕ, причем первый вывод

циода через времязадающую интегрирую- 40 щую цепь подсоединен к входу элемента НЕ, и первую интегрирующую цепь, причем

ыход элемента ИЛИ-НЕ подключен к выходу блока защиты, вход формирователя импульсов перегрузки подключен 45 к выходу датчика.перегрузки выпрямителя с фильтром, вход формирователя импульсов перенапряжения соединен с выходной клеммой, а его выход через первую интегрирующую цепь подсоеди- 50 иен к второму входу элемента ИЛИ основного узла повторного включения, вьпсод указанного элемента ИЛИ подключен к первому входу элемента

ИЛИ-НЕ и первому входу элемента И 55 этого же узла, второй вход элемента И подключен к выходу элемента НЕ узла логической задержки, выход элемента

ИЛИ узла логической памяти подключен к второму входу элемента ИЛИ-НЕ, введены диод, вторая интегрирующая цепь, двухвходовой элемент И и дополнительный узел повторного включения, выполненный на трехвходовом элементе ИЛИ и двухвходовом элементе И, причем выход элемента ИЛИ подключен к первому входу элемента И выходом подключенного к первому входу указанного элемента ИЛИ, а элемент ИЛИ-НЕ и элемент ИЖ узла логической памяти снабжены третьими входами, причем выход формирователя импульсов перегрузки через последовательно включенные диод и вторую интегрирующую цепь подключен к третьему входу элемента ИЛИ-НЕ, второму входу элемента ИЛИ дополнительного узла повторного включения и первому входу элемента И узла логическо памяти, второй вход которого подсоединен к выходу интегрирующей цепи узла логической задержки и первому входу элемента И, второй вход которого совместно с третьим входом элемента ИЛИ дополнительного узла повторного включения подсоединен к выходу элемента ИЛИ основного узла повторного включения, выход элемента И подсоединен к третьему входу элемента ИЛИ узла логической памяти, второй вход элемента И дополнительного узла повторного включения соединен с выходом элемента НЕ узла логическо задержки, выход элемента ИЛИ дополнительного узла повторного включения соединен с вторым выводом диода узла логической задержки.

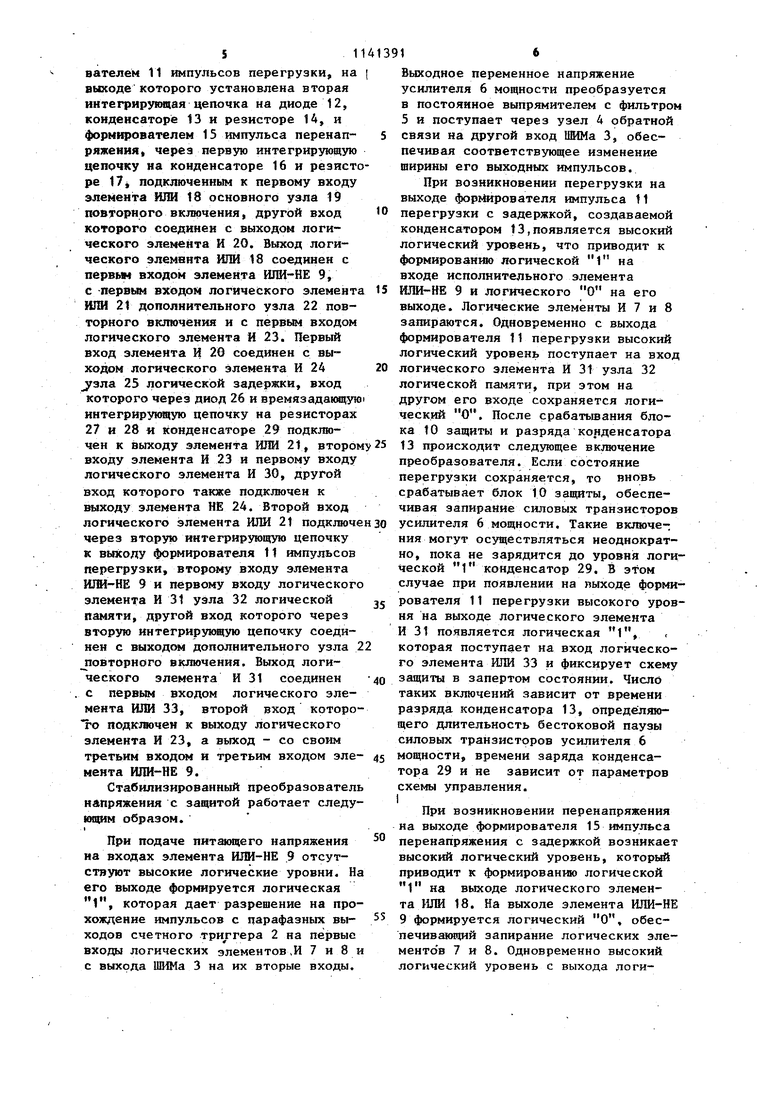

На чертеже показана структурная схема предлагаемого стабилизированного преобразователя напряжения с защитой.

Преобразователь содержит генератор 1 тактовых импульсов, подключен- ньй к входу счетного триггера 2 и входу ШИМа 3, второй вход которого через узел 4 обратной связи подключе к выходу выпрямителя с фильтром 5, установленного на выходе усилителя 6 мощности, управляющие входы которого подключены к выходам двух логических элементов И 7 и 8, первые входы которых подключены выходам счетного триггера 2, вторые объединенные входы - к выходу ШИМа 3, а третьи объединенныё входы - к выходу элемента ШШ-НЕ 9 блока 10 защиты с формирователем 11 датульсов перегрузки, на выходе которого установлена вторая интегрирующая цепочка на диоде 12, конденсаторе 13 и резисторе 14, и формирователем 15 импульса перенапряжения, через первую интегрир тодую цепочку на конденсаторе 16 и резист ре 17j подключенным к первому входу элемента ИЛИ 18 основного узла 19 повторного включения, другой вход которого соединен с выходом логического элемента И 20. Выход логического элемента ИЛИ 18 соединен с первм4 входом элемента ИПИ-НЕ 9, с -первым входом логического элемент ШШ 21 дополнительного узла 22 повторного включения и с первым входом логического элемента И 23. Первый вход элемента И 20 соединен с выходом логического элемента И 24 зла 25 логической задержки, вход которого через диод 26 и времязадающую интегрирунищую цепочку на резисторах 27 и 28 и конденсаторе 29 подкш)чен к выходу элемента ИЛИ 21, второ входу элемента И 23 и первому входу логического элемента И 30, другой вход которого также подключен к выходу элемента НЕ 24. Второй вход логического элемента ИЛИ 21 подкгаоч через вторую интегрирующую цепочку к выходу формирователя 11 импульсов перегрузки, второму входу элемента ШШ-НБ 9 и первому входу логическог элемента И 31 уэла 32 логической памяти, другой вход которого через вторую интегрирующую цепочку соединен с ВЫХОДШ4 дополнительного узла повторного включения. Выход логического элемента И 31 соединен . с входом логического элемента ШШ 33, второй вход которо го подклочен к выходу логического элемента И 23, а выход - со своим третьим входом и третьим входом эле мента ШШ-НЕ 9. Стабилизированный преобразовател напряжения с защитой работает следу юошм образом. При подаче питающего напряжения на входах элемента ИЛИ-НЕ 9 отсутствуют высокие логические уровни. Н его выходе формируется логическая 1, которая дает разрешение на про хождение импульсов с парафазных выходов счетного 2 на первые входы логических элементов И 7 и 8 с выхода ШИМа 3 на их вторые входы. Выходное переменное напряжение усилителя 6 мощности преобразуется в постоянное выпрямителем с фильтром 5 и поступает через узел 4 обратной связи на другой вход ШМа 3, обеспечивая соответствующее изменение ширины его выходных импульсов. При возникновении перегрузки на выходе форь4ирователя импульса 11 перегрузки с задержкой, создаваемой конденсатором 13,появляется высокий логический уровень, что приводит к формированию логической 1 на входе исполнительного элемента ИЛИ-НЕ 9 и логического О на его выходе. Логические элементы И 7 и 8 запираются. Одновременно с выхода формирователя 11 перегрузки высокий логический уровень поступает на вход логического элемента И 31 узла 32 логической памяти, при этом на другом его входе сохраняется логический О. После срабатьшания блока 10 защиты и разряда конденсатора 13 происходит следующее sKjraueHHe преобразователя. Если состояние перегрузки сохраняется, то вновь срабатывает блок 10 защиты, обеспечивая запирание силовых транзисторов усилителя 6 мощности. Такие вкгвочения могут ос тцествляться неоднократно, пока не зарядится до уровня логической 1 конденсатор 29. В этом случае при появлении на пыходе формирователя 11 перегрузки высокого уровня на выходе логического элемента И 31 появляется логическая 1, которая поступает на вход логического элемента ИЛИ 33 и фиксирует схему защиты в запертом состоянии. Число таких включений зависит от времени разряда конденсатора 13, определяющего длительность бестоковой паузы силовых транзисторов усилителя 6 мощности, времени заряда конденсатора 29 и не зависит от параметров схемы управления. I При возникновении перенапряжения на выходе формирователя 15 ш пульса перенапряжения с задержкой возникает высокий логический уровень, который приводит к формированию логической 1 на выходе логического элемента ЦЖ 18. На выходе элемента ШШ-НЕ 9 формируется логический О, обеспечивающий запирание логических элементов 7 и В. Одновременно высокий логический уровень с выхода доги

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Стабилизированный преобразователь постоянного напряжения в постоянное | 1980 |

|

SU957380A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке 3319377/24-07, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-02-23—Публикация

1983-11-11—Подача