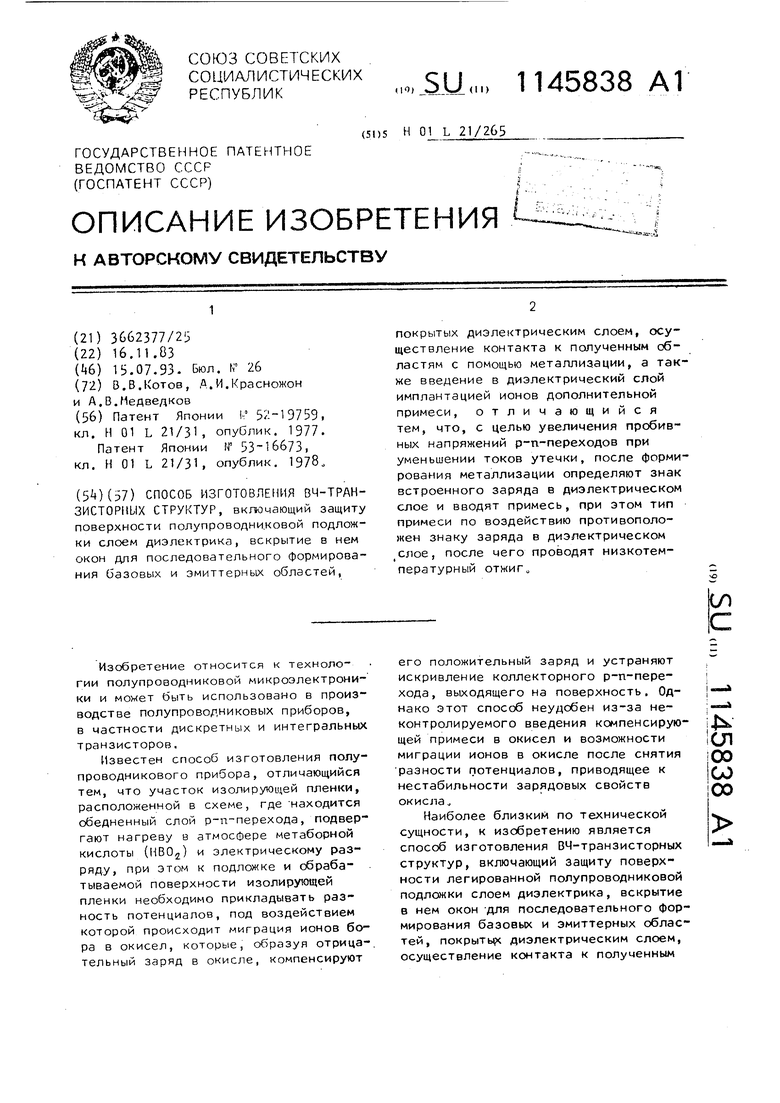

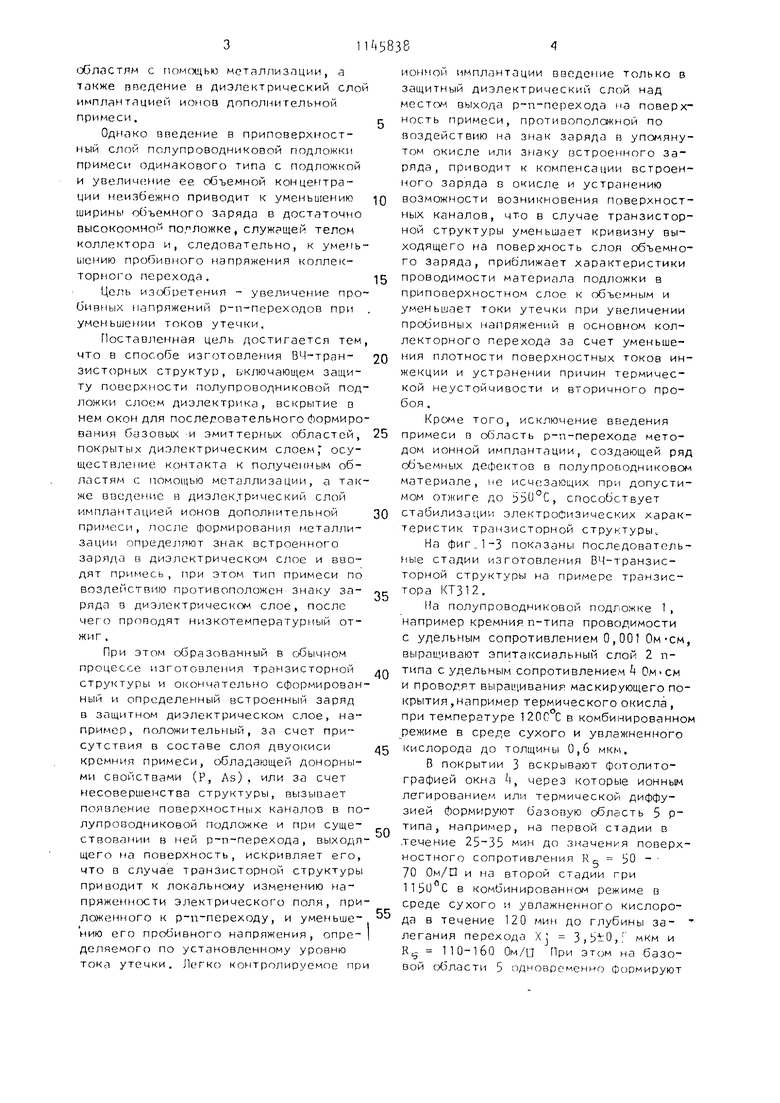

областям с Г1омо(дью металлизации, а также введение в диэлектрический слой имплантацией ионоа дополнительной примеси. Однако введение в приповерхностный слой полупроводниковой подложки примеси одинакового типа с подложкой и уоеличр.ние ее объемной конце(-(тра ции неизбежно приводит к уменьиюнию ширины Ы ъемного заряда в достаточно высокоомной подложке, служащей телом коллектора и, следовательно, к умень июнию пробивного напряжения коллекторного перехода. Цель иэс:1бретения увеличение про бивных напряжений р-п-переходов при уменьшении токов утечки. Поставленная цель достигается тем что в способе изготовления ВЧ-транзисторных структур, ь-ключающем защиту поверхности полупроводниковой под ложки слоем диэлектрика, вскрытие о нем окон для последовательного формиро вания базовых и эмиттерных областей, покрытых диэлектрическим слоем; осуществле)ие контакта к полученным областям с помощью металлизации, а так же введение в диэлектрический слой имплантацией ионов дополнительной примеси, .после формирован|.1я металлизации определяют знак встроенного заряда в диэлектрическом слое и вводят примесь, при этом тип примеси по воздействию противоположен знаку заряда в диэлектрическом слое, после чего проводят низкотемператур1- ый отжиг . При этом образованный в обычном процессе изготовления транзисторной структуры и окончательно сформирован ный и определенный встроенный заряд в защитном диэлектрическом слое, например, положительный, за счет присутствия в составе слоя двуокиси кремния примеси, обладающей донорными свойствами (Р, As), или за счет несовершенства структуры, вызывает появление поверхностных каналов в по лупроводниковой подложке и при существовании в ней р-п-перехода, выходя щего на поверхность, искривляет его что в случае транзисторной структуры приводит к локальноуиу изменению напряженнсхти электрического поля, при ложенного к р-п-переходу, и уменьшеиию его пробивного напряжения, олределяемого по установленному уровню тока утечки. Легко контролируемое пр ионнои имплантации введение только в защитный диэлектрический слой над местам выхода р-п-перехода на поверхность примеси, противоположной по воздействию на знак заряда в упс - янутом окисле или знаку встроенного заряда, приводит к компенсации встроенного заряда в окисле и устранению возможности возникновения поверхностных каналов, что в случае транзисторной структуры уменьшает кривизну выходящего на поверхность слоя объемного заряда, приближает характеристики проводимости материала подложки в приповерхностном слое к объемным и уменьшает токи утечки при увеличении пробивных напряжений в основном коллекторного перехода за счет уменьшения плотности noeepxHocTHbix токов инжекции и устранении причин термической неустойчивости и вторичного пробоя . Кроме того, исключение введения примеси D область р-п-перехода методом ионной имплантации, создающей ряд объемных дефектов в полупроводниковом материале, не исчезающих при допустимом от)1(иге до , способствует стабилизации электрофизических характеристик тра1- зисторной структурьк На фиг „1-3 показаны последовательные стадии изготовления ВЧ-транзисторной структуры на примере транзистора КТ312. На полупроводниковой подложке 1, например кремния п-типа проводимости с удельным сопротивлением 0, 00 Ом-см, выращивают эпитаксиэльный слой 2 птипа с удельным сопротивлением k Ом-см и проводят выращивания маскирующего покрытия ,например термического окисла , при температуре 120С С в комбинированном режиме в среде сухого и увлажненного Кислорода до толщинь1 0,6 мкм, В покрытии 3 вскрывают фотолитографией окна А, через которые ионным легирование- или термической диффузией формируют базовую область 5 Р типа, например, на первой стадии в течение 25-35 мин до значения поверхностного сопротивления Rg 50 - 70 Ом/П и на второй стадии гри 115иС в комбинированном режиме в среде сухого и увлажненного кислорода в течение 120 мин до глубины за- легания перехода X 3,5tO,r мкм и Кц 110-160 Ом/о При этом на базовой области 5 одновременно формируют

5.

маскируюцее покрытие 6 толщиной 0,5 0,7 мкм„ В покрытии 6 фотолитографие вскрывают окна 7, через которые термической диффузией формируют эмиттерную область 8 п-типа, например, на первой стадии из РС1 при lOSOC в среде аргона с добавлением кислорода в течение 15 мин с подпором потока диффузанта в открытой трубе и 5 минутным вытеснением потока диффузанта до. .глубины залегания эмиттерной области X. 1,1 мкм и R 3 Ом/П и на второй стадии при 1050°С в среде кислорода до толщины базовой области liX j 0,6-0,8 мкм. При этом на эииттерной области 8 одновременно формируют защитное покрытие 9 на основе фосфоросиликатного стекла (ФСС) толщиной 0,2-0,25 мкм.

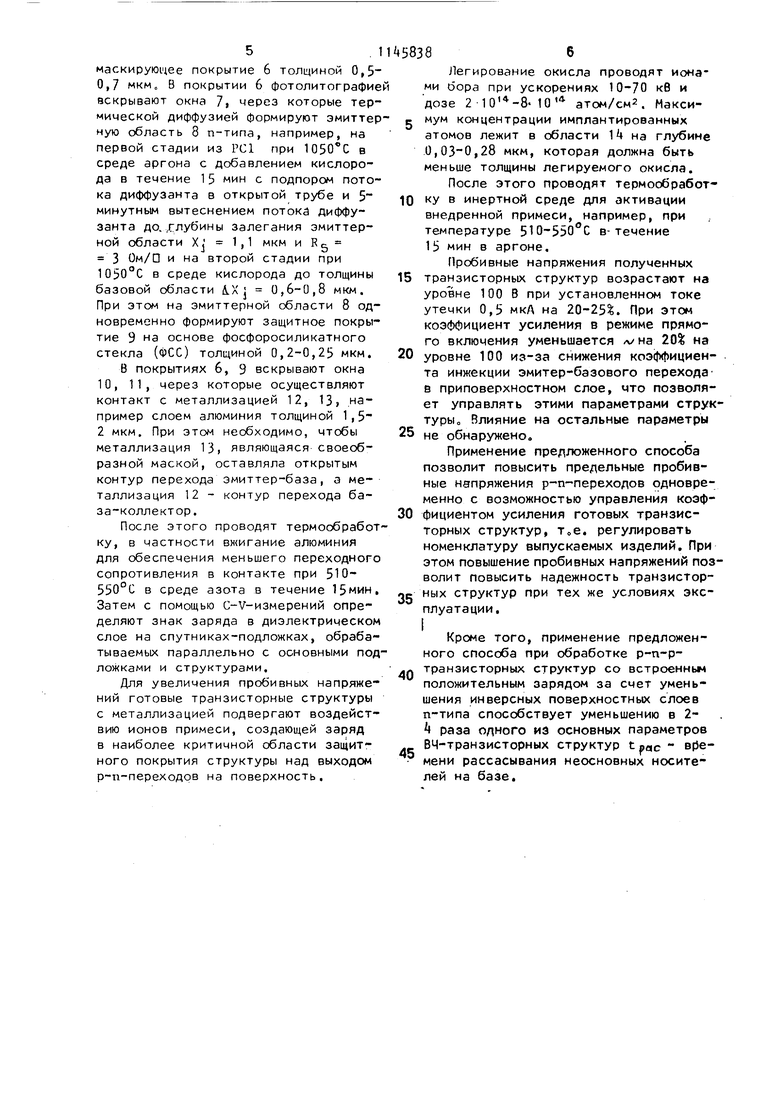

В покрытиях 6, 9 вскрывают окна 10, 11, через которые осуществляют контакт с металлизацией 12, 13 например слоем алюминия толщиной 1,5 2 мкм. При этом необходимо, чтобы металлизация 13, являющаяся своеобразной маской, оставляла открытым контур перехода эмиттер-база, а металлизация 12 - контур перехода база-коллектор.

После этого проводят термообработку, в частности вжигание алюминия для обеспечения меньшего переходного сопротивления в контакте при 510550°С в среде азота в течение 15мин, Затем с помощью C-V-измерений определяют знак заряда в диэлектрическом слое на спутниках-подложках, обрабатываемых параллельно с основными подложками и структурами.

Для увеличения пробивных напряжений готовые транзисторные структуры с металлизацией подвергают воздействию ионов примеси, создающей заряд в наиболее критичной области за1цитного покрытия структуры над выходом р-п-переходрв на поверхность.

58386

Легирование окисла проводят ионами бора при ускорениях 10-70 кв и дозе 2 10 -8-10 атом/см2. Максис мум концентрации имплантированных атомов лежит в области 1 на глубине 0,,28 мкм, которая должна быть меньше толщины легируемого окисла. После этого проводят термообработку в инертной среде для активации внедренной примеси, например, при температуре в-течение 15 мин в аргоне.

Пробивные напряжения полученных

5 транзисторных структур возрастают на уровне 100 В при установленном токе утечки 0,5 мкЛ на 20-25%. При этом коэффициент усиления в режиме прямого включения уменьшается л/ на 20% на

0 уровне 100 из-за снижения коэффициента инжекции эмитер-базового перехода в приповерхностном слое, что позволяет управлять этими параметрами структуры. Влияние на остальные параметры

5 не обнаружено.

Применение предложенного способа позволит повысить предельные пробивные напряжения р-п-переходов одновременно с возможностью управления коэффициентом усиления готовых транзисторных структур, т.е. регулировать номенклатуру выпускаемых изделий. При этом повышение пробивных напряжений позволит повысить надежность транзисторд ных структур при тех же условиях эксплуатации,

I

Кроме того, применение предложенного способа при обработке р-п-рj4 транзисторных структур со встроенньм положительным зарядом за счет уменьшения инверсных поверхностных слоев п-типа способствует уменьшению в 2А раза одного из основных параметров

. ВЧ-транзисторных структур t ас в{3е мени рассасывания неосновных носителей на базе.

| название | год | авторы | номер документа |

|---|---|---|---|

| Планарная транзисторная структура | 1985 |

|

SU1272927A1 |

| Способ изготовления ВЧ транзисторных структур | 1979 |

|

SU766423A1 |

| Способ изготовления мощных ВЧ и СВЧ транзисторов | 1984 |

|

SU1163763A1 |

| Способ изготовления ВЧ и СВЧ кремниевых N - P - N транзисторных структур | 1979 |

|

SU766416A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО ВЫСОКОВОЛЬТНОГО ИНТЕГРАЛЬНОГО ТРАНЗИСТОРА | 2012 |

|

RU2492546C1 |

| Способ изготовления мощных ВЧ транзисторных структур | 1978 |

|

SU705924A1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ВЧ N-P-N-ТРАНЗИСТОРА | 1990 |

|

RU2025824C1 |

| Способ изготовления высокочастотных транзисторных структур | 1983 |

|

SU1114242A1 |

| САМОСОВМЕЩЕННЫЙ ВЫСОКОВОЛЬТНЫЙ ИНТЕГРАЛЬНЫЙ ТРАНЗИСТОР | 2012 |

|

RU2492551C1 |

| ВЫСОКОВОЛЬТНЫЙ САМОСОВМЕЩЕННЫЙ ИНТЕГРАЛЬНЫЙ ДИОД | 2012 |

|

RU2492552C1 |

иг. 1

в 5 /

-5

/

Фаг. 2

. 5

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-07-15—Публикация

1983-11-16—Подача