Областью применения изобретения является полупроводниковая электроника и микроэлектроника, а именно производство интегральных микросхем (ИМС).

Важнейшими параметрами транзисторов любого типа, определяющими возможности их надежной работы той или другой конкретной схеме, являются предельно допустимые пробивные напряжения p-n переходов. В планарных транзисторах электрический пробой p-n переходов имеет свою специфику, обусловленную конструктивно-технологическими особенностями планарных p-n переходов.

Существуют методы повышения пробивных напряжений p-n переходов транзистора. (А. Блихер. Физика силовых биполярных и полевых транзисторов. Пер. с англ.под ред. И.В. Грехова. Ленинград, «Энергоатомиздат», 1986, с.37-50) [1]..

Значительное влияние на снижение напряжение пробоя оказывает искривление p-n перехода. Метод уменьшения этого эффекта заключается в формировании охранного диффузионного кольца с глубиной залегания намного больше глубины базовой области, одинакового типа проводимости с базовой областью и смыкающегося с последней. Увеличение напряжения пробоя достигается увеличением радиуса кривизны охранного диффузионного кольца.

Эффективным способом повышения напряжения пробоя является «метод делительных колец». Делительные кольца формируются при формировании базовой области и располагаются: первое делительное кольцо вокруг базовой области на расстоянии равном границе области пространственного заряда (ОПЗ); второе делительное кольцо на расстоянии, равном области пространственного заряда первого делительного кольца и так далее. Снабдив p-n переход транзистора несколькими делительными кольцами можно получить транзисторную структуру с напряжением пробоя равным напряжению пробоя в плоской части p-n перехода.

Вышеуказанным способам увеличения напряжения пробоя присущи следующие недостатки:

- существенное увеличение площади транзисторной структуры;

- увеличение емкости коллекторной области, приводящее к снижению быстродействия транзистора;

- увеличение сопротивления коллектора, из-за увеличенной области объемного заряда, что также снижает быстродействие транзистора. Известен способ изготовления самосовмещающихся планарных транзисторов, авторское свидетельство СССР N723984 H01L 21/18 [2]. Этот способ включает операции маскирования подложки первого типа проводимости диэлектриком и слоем поликристалличского кремния (СПК), вскрытия в диэлектрике и СПК окна под базовую область, наращивания СПК, легированного примесью противоположного типа проводимости подложке, формирования базовой области и контакта к ней из поликристаллического кремния, локально маскируют диэлектриком, не травящимся в травителях для двуокиси кремния, места будущего эмиттерной области, проводят термообработку для формирования базовой области, удаляют поликристаллический кремний, легированный примесью противоположного типа проводимости подложке, со всей поверхности, за исключением контакта к базе и в местах будущего эмиттера, осуществляют подлегирование базовой области и контакта к ней с выращиванием диокисида кремния, удаляют диэлектрик и СПК на месте будущей эмиттерной области и формируют последнюю примесью второго типа проводимости.

В данном способе самосовмещены базовая и эмиттерная области.

Недостатком этого способа является:

- отсутствует самосовмещение всех областей транзисторной структуры, что снижает их плотность компоновки;

- p-n - переходы областей выходят на поверхность подложки, защищенной диоксидом кремния, что снижает пробивные напряжения последних;

- инжекция основных носителей сферическим и цилиндрическими частями эмиттера способствует уменьшения коэффициента усиления из-за рекомбинации основных носителей в пассивной части базы.

Известен способ изготовления биполярных интегральных транзисторов, авторское свидетельство СССР N1135378 H01L 21/265 [3]. Этот способ включает формирование в полупроводниковой подложке первого типа проводимости скрытого слоя второго типа проводимости, формирование эпитаксиального слоя второго типа проводимости, формирование боковой диэлектрической изоляции, осаждение поликремния, маскирование нитридом кремния области эмиттера, а также области контактов кбазовой и коллекторной областям, формирование пассивной базы ионным легированием примесью первого типа проводимости, термическое окисление поликремния, удаление нитрида кремния, формирование активной базы и эмиттера путем ионного легирования примесями первого и второго типа проводимости с последующей термообработкой, формирование контактов к активным областям транзистора полицидом платины. В этом способе самосовмещены области транзисторной структуры с контактами этих областей.

Недостатком этого способа является:

- отсутствует самосовмещение областей транзисторной структуры с изолирующей областью, что снижает их плотность компоновки;

- p-n - переходы областей выходят на поверхность подложки, защищенной диоксидом кремния, что снижает пробивные напряжения последних;

- инжекция основных носителей сферическим и цилиндрическими частями эмиттера способствует уменьшения коэффициента усиления из-за рекомбинации основных носителей в пассивной части базы;

- присутствие скрытого слоя первого типа проводимости в подложке второго типа проводимости увеличивает емкость коллектор-подложка, что снижает быстродействие.

Наиболее близким аналогом предлагаемого изготовления самосовмещенного высоковольтного интегрального транзистора, принятым нами за прототип, является патент РФ N2 356127 С2 H01L 21/ 762 [4].

Данный способ включает формирование в подложке первого типа проводимости сплошного скрытого слоя второго типа проводимости, осаждение на полупроводниковой подложке эпитаксиального слоя второго типа проводимости, формирование первого диэлектрика на эпитаксиальном слое, вскрытие окон в первом диэлектрике под глубокие и мелкие изолирующие области, под контакт к подложке, формирование экранирующего слоя в окнах под мелкие изолирующие области между базовой областью и коллекторным контактом, одновременное травление щелей под изолирующие области и контакт к подложке, формирование охранных областей первого типа проводимости под глубокими изолирующими областями, заполнение щелей диэлектриком, планаризацию, заполнение щели под контакт к подложке поликремнием, формирование контакта к подложке поликремнием, отличающийся тем, что на месте будущего контакта к прокрытому слою в первом и втором диэлектриках вскрывают окно, на вертикальных стенках окна формируют третий разделительный диэлектрик, в окне формируют экранирующий слой, вскрывают окна в первом и втором диэлектриках под глубокую изолирующую область, травят щель на глубину эпитаксиального, скрытого слоев и частично подложку, а на месте коллекторного контакта - на глубину экранирующего и эпитаксиального слоев формируют разделительный диэлектрик на вертикальных стенках щели, формируют противоканальные области на дне изолирующих щелей, в щелях формируют второй и третий диэлектрики, со дна щели под контакт к подложке и контакт к скрытому слою локально травят диэлектрики и заполняют щели поликремнием, производят планаризацию поликремния и диэлектриков до планарности с подложкой, формируют на подложке диэлектрик, вскрывают в диэлектрике окна под контакты к подложке и к скрытому слою, формируют контакты введением примеси в поликремниевый коллекторный контакт второго типа проводимости и в поликремниевый контакт к подложке первого типа проводимости с последующим термическим отжигом и в изолированной области известными методами формируют базовую и эмиттерную области. В этом способе самосовмещены изолирующая область с контактом к подложке, с контактом к коллекторной области и базовой областью.

Данному способу присущи следующие недостатки:

- n+ скрытый слой коллектора формируется в подложке второго типа проводимости увеличивает емкость коллектор-подложка, что снижает быстродействие;

- инжекция основных носителей сферическим и цилиндрическими частями эмиттера способствует уменьшения коэффициента усиления из-за рекомбинации основных носителей в пассивной части базы;

- отсутствует самосовмещение эмиттерной области с изолирующей областью, коллекторным контактом и контактами к базовой и эмиттерной областями, что снижает плотность компоновки структур.

Задачей изобретения является повышение пробивных напряжений p-n переходов интегрального транзистора, повышения плотности компоновки транзисторных структур и увеличения их быстродействия.

Это решается тем, что способ изготовления самосовмещенного высоковольтного интегрального транзистора, включающий формирование коллекторной области легированием кремниевого слоя, расположенного над диэлектрическим слоем, примесью первого типа проводимости, наращивание эпитаксиального слоя первого типа проводимости, формирование в эпитаксиальном слое области второго типа проводимости легированием примесью, формирование над областью второго типа проводимости первого диэлектрического слоя, вскрытие в нем окна под будущий контакт к коллекторному слою, формирование на вертикальных стенках окна разделительного диэлектрика, формирование в окне экранирующего слоя, вскрытие в первом диэлектрическом слое окна под будущую изолирующую область, формирование на вертикальных стенках окна разделительного диэлектрика, формирование щелей для изолирующей и контакта к коллекторной областям, одновременным травлением кремния в окне под изолирующую область до диэлектрика, расположенного под коллекторной областью и в окне травлением экранирующего слоя и кремния, на месте будущего контакта к коллекторной области, формирование на вертикальных стенках щелей изолирующих диэлектриков, заполнение щелей слоем, планаризацию слоя до первого диэлектрического слоя, удаление слоя в щелях до планарности с подложкой, удаление первого диэлектрического слоя, формирование второго диэлектрического слоя, формирование области первого типа проводимости в области второго типа проводимости, формирование третьего диэлектрического слоя, вскрытие окон во втором и третьем диэлектрических слоях под будущий контакт к области второго типа проводимости, вскрытие в нем окна под будущий контакт к области первого типа проводимости, формирование на вертикальных стенках окон разделительного диэлектрика, формирование в окне экранирующего слоя под будущий контакт к эмиттерному слою, формирование щели травлением кремния в окне под будущий контакт к базовой области, а в окне на месте будущего контакта к эмиттерной области травлением экранирующего слоя и части базового слоя, формирование на стенках щелей изолирующих диэлектриков, заполнение щелей слоем, его планаризацию до третьего диэлектрического слоя, травление слоя в щелях до планарности со слоем в изолирующей области, легирование контакта к базовой области примесью второго типа проводимости под защитой фоторезиста, легирование контакта к эмиттерной области примесью первого типа проводимости под защитой фоторезиста, термический отжиг для формирования эмиттерной области и перераспределения примеси в контактах до областей транзистора, формирование полицида тугоплавких металлов к контактам, формирование металлизированной разводки. Для одновременного формирования щелей под изолирующую область и контакт к коллекторной области, над коллекторным контактом формируется экранирующий слой, который позволяет одновременно формировать щель под изолирующую и под контакт к коллекторной областям для одновременного формирования щелей под контакты к базовой и эмиттерной областям, над эмиттерной областью формируется также экранирующий слой. Контакт к эмиттерной области может формироваться как в щелевом, так и в планарном исполнении.

В планарной транзисторной структуре p-n переходы формируются методом локальной диффузии в окна (прямоугольной формы) вскрытые в диоксиде кремния. Так как диффузия примеси происходит не только в окно, формируя плоскую часть p-n перехода, но и под диоксид кремния у линейного края окна, образуя искривленный участок, который имеет конфигурацию почти цилиндрической формы, а в углах окна под диоксидом кремния образуя еще более искривленный участок сферической формы, которые выходят на поверхность подложки, находящейся под диоксидом кремния. Пробивные напряжения цилиндрических и сферических p-n переходов уменьшают общее пробивное напряжение p-n переходов планарного интегрального транзистора.

Напряжение пробоя снижается также под действием механических напряжений на границе окна кремний - диоксид кремния, особенно в углах окон, вследствие различия коэффициентов расширения кремния и диоксида кремния. Поверхностная концентрация примеси, которая диффундирует под диоксид кремния становится меньше по сравнению с поверхностной концентрацией примеси в окне из-за разных граничных условий диффузии и коэффициента сегрегации примеси в диоксид кремния изменяя таким образом поверхностную проводимость кремния.

Так как p-n переходы выходят на поверхность подложки, защищенную диоксидом кремния, то на напряжения пробоя существенное влияние оказывает условия на поверхности подложки. Наличие на поверхности планарного p-n перехода диоксида кремния влечет за собой два нежелательных фактора, влияющих на снижение напряжение пробоя. Во-первых диоксид кремния, сформированный на подложке, имеет положительный заряд. Во-вторых приповерхностные слои кремния изменяют свою проводимость вследствие перераспределения примеси при термическом окислении. Оба эти фактора снижают пробивные напряжения, сужая область объемного заряда в приповерхностном слое. Сужение области объемного заряда приводит к увеличению напряженности электрического поля в p-n переходе, что приводит к уменьшению пробивных напряжений.

Перераспределение легирующих примесей, например, бора при формировании p-n переходов приводит к обеднению примесью приповерхностных слоев из-за коэффициента сегрегации (m>1), то есть при перераспределении бора с окислением происходит его диффузия как в кремний, так и в диоксид кремния, при диффузии фосфора (m<1) накопление фосфора происходит в приповерхностных слоях. Обедненный слой, возникающий при обратном смещении, будет тем уже, чем низкоомнее материал. В приповерхностной области пробой наступит преждевременно не только из-за влияния кривизны, но и вследствие обогащения фосфором приповерхностного слоя, а в случае диффузии бора в приповерхностной области образуются проводящий канал с низким пробивным напряжением. Это явление еще более усугубляется присутствием положительного заряда в диоксиде кремния.

В предложенном способе изготовления самосовмещенного высоковольтного интегрального транзистора отсутствует искривление p-n - переходов, способствующее повышению напряжения пробоя последних, применение пиролизного диоксида кремния из тетроэтилортосиликата (ТЭОСа) и формирование областей структуры при термоотжиге в инертном газе позволило минимизировать перерасределение примеси, что также способствовало повышению напряжения пробоя p-n - переходов. Присутствие диэлектрика под коллекторной областью способствует уменьшению емкости p-n перехода коллектор-подложка и плоские p-n переходы также уменьшают емкости p-n переходов: эмиттер-база; коллектор-база, что увеличивает быстородействие транзистора. Формирование экранирующих слоев на месте коллекторного и эмиттерного контактов позволяет обеспечить полное самосовмещение структуры, способствующее повышению плотности компоновки транзисторных структур

Данная совокупность признаков позволяет решить поставленную задачу - повышение пробивных напряжений р-n переходов, повышения плотности компоновки транзисторных структур и увеличения их быстродействия. Сущность изобретения поясняется на фиг.1-10.

Суть изобретения состоит в том, что в самосовмещенном высоковольтном интегральном транзисторе р-n переходы являются плоскими и сформированы в объеме полупроводника без выхода на поверхность подложки, формирование экранирующих слоев на месте коллекторного и эмиттерного контактов позволяет обеспечить полное самосовмещение структуры, присутствие диэлектрика под коллекторной областью способствует уменьшению емкости р-n перехода коллектор-подложка и плоские p-n переходы также уменьшают емкости p-n переходов: эмиттер-база; коллектор-база, что увеличивает быстородействие транзистора.

Данная совокупность признаков позволяет решить поставленную задачу - повышение пробивных напряжений p-n переходов, повышения плотности компоновки транзисторных структур и увеличения их быстродействия. Сущность изобретения поясняется на фиг.1-10.

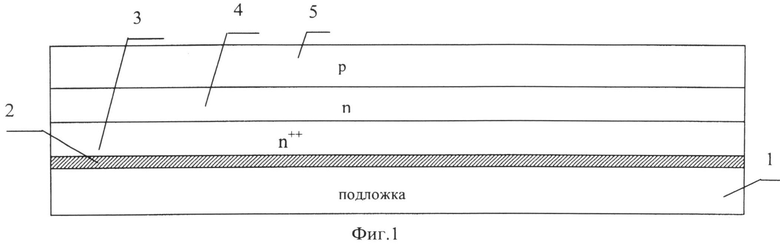

На фиг.1 представлен разрез структуры, где в полупроводниковой подложке 1 сформирован диэлектрический слой 2, над диэлектрическим слоем расположен полупроводниковый сильно легированный слой 3 первого типа проводимости, над которым сформирован эпитаксиальный слабо легированный слой 4 первого типа проводимости, в котором сформирована базовая область 5 второго типа проводимости. Из сильно легированного слоя 3 и слабо легированного слоя 4 формируется коллекторная область.

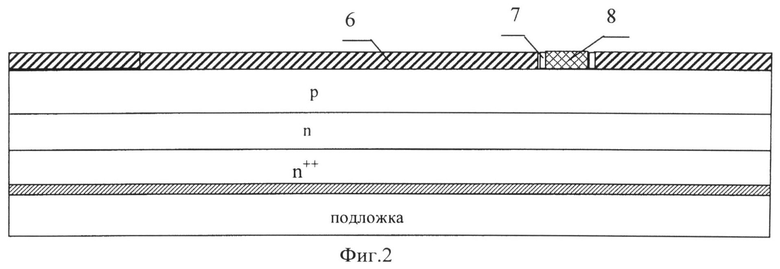

На фиг.2 представлен разрез структуры, на которой сформирован первый диэлектрический слой 6. В диэлектрическом слое вскрыто окно под будущий контакт к коллекторной области, на вертикальных стенках окна сформирован разделительный диэлектрик 7 и в окне сформирован экранирующий слой 8.

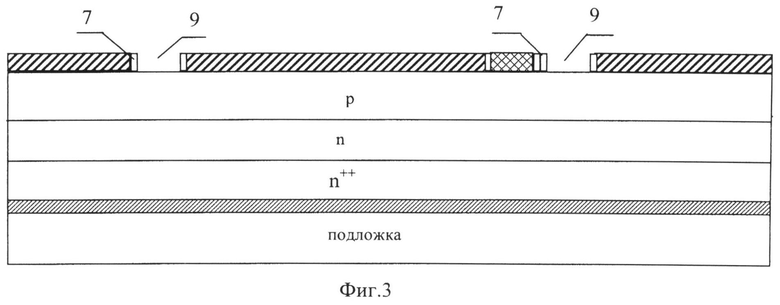

На фиг.3 представлен разрез структуры, где в первом диэлектрическом слое 6 вскрыто окно 9 под будущую изолирующую область, на вертикальных стенках окна сформирован разделительный диэлектрик 7.

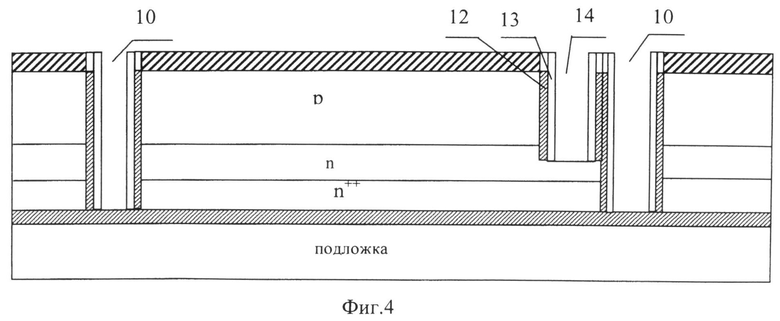

На фиг.4 представлен разрез структуры, где в месте экранирующего слоя 8 (Фиг.2) и в окне 9 (Фиг.3) плазмохическим травлением сформированы щели 10 под изолирующую область и 14 под будущий контакт к коллектору, на вертикальных стенках щелей сформированы изолирующие диэлектрики 12 и 13.

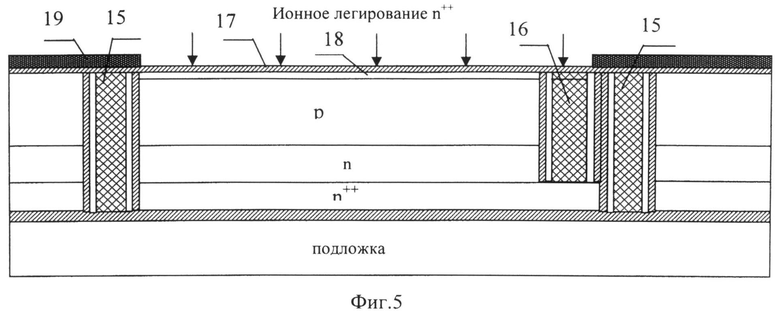

На фиг.5 представлен разрез структуры, где щели с изолирующими диэлектриками 12 и 13 (Фиг.4) заполнены слоем 15 - изолирующая область и 16 - будущий контакт к коллекторной области с последующей планаризацией до первого диэлектрического слоя, подтравлены слои 15 и 16 в щелях до планарности с подложкой, удален первый диэлектрический слой и сформирован второй диэлектрический слой 17 и с помощью маски фоторезиста 19 ионным легированием примеси первого типа проводимости через второй диэлектрический слой 16 сформирована область 18 первого типа проводимости в базовой области и в будущем контакте к коллекторной области.

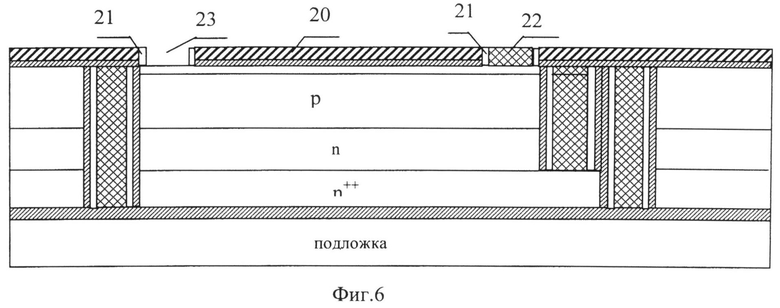

На фиг.6 представлен разрез структуры, где над вторым диэлектрическим слоем 17 сформирован третий диэлектрический слой 20. В диэлектрических слоях 17 и 20 вскрыто окно под контакт к будущей эмиттерной области, на вертикальных стенках окон сформирован разделительный диэлектрик 21 и в окне под контакт к эмиттерной области сформирован экранирующий слой 22. В диэлектрическом слое 17 и 20 вскрыто окно 23 под будущий контакт к базовой области. На вертикальных стенках окна сформирован разделительный диэлектрик 21.

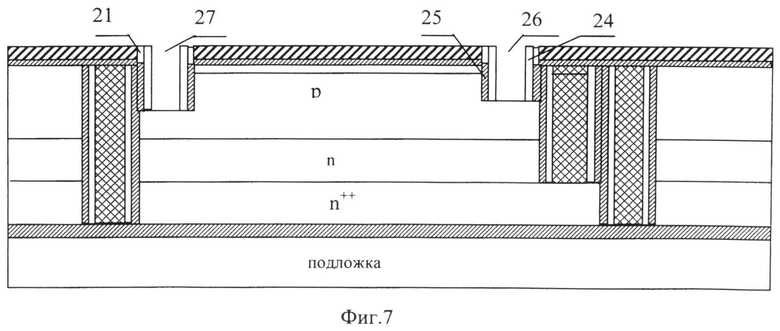

На фиг.7 представлен разрез структуры, где плазмохимическим травлением сформированы щели 27 и 26 под будущие контакты к базовой и будущей эмиттерной областям, соответственно, на вертикальных стенках щелей сформированы изолирующие диэлектрики 24 и 25.

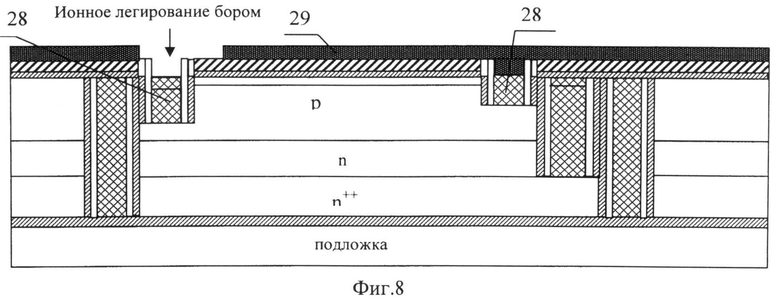

На фиг.8 представлен разрез структуры, где щели 27 и 26 (Фиг.7) заполнены слоем 28, с последующей планаризацией до третьего диэлектрического слоя 20 (фиг.6), подтравлен слой 28 в щелях до планарности с подложкой под контакт к базовой области и под контакт к эмиттерной области. Под защитой фоторезиста 29 ионным легированием введена примесь второго типа проводимости в будущий контакт к базовой области.

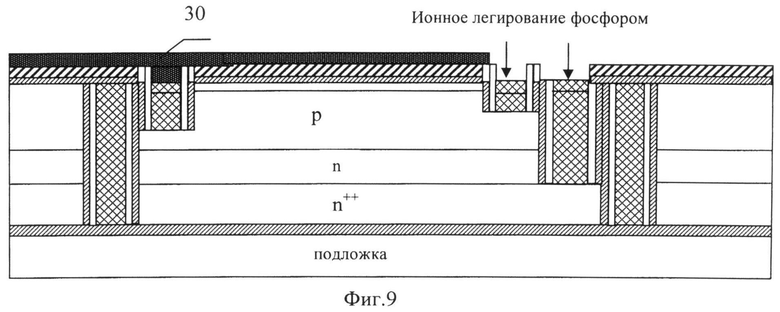

На фиг.9 представлен разрез структуры, где во втором 17 и третьем 20 диэлектрических слоях под защитой фоторезиста 30 вскрыто окна над коллекторным и эмиттерным контактами, ионным легированием введена примесь первого типа проводимости в будущие контакты: 37 к будущей эмиттерной и к коллекторной 34 областям (Фиг.10).

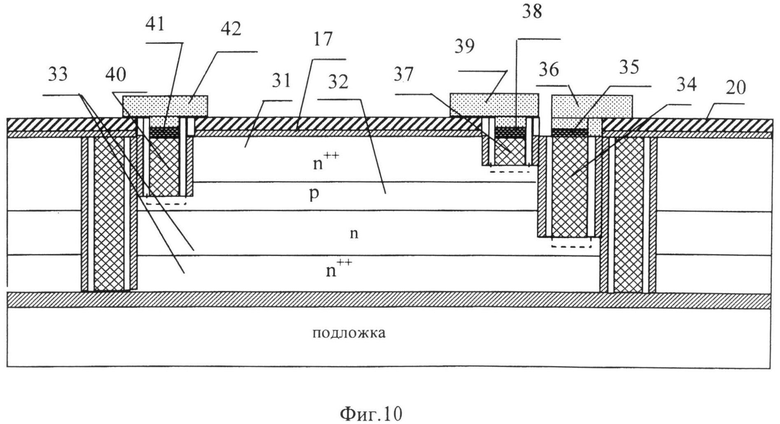

На фиг.10 представлен разрез структуры, где термическим отжигом сформированы: эмиттерная область 31, базовая область 32, коллекторная область 33, сформировано перераспределение примеси в контактах к коллекторной, базовой, эмиттерной областях. На контактах к областям структуры сформирован полицид тугоплавкого металла и сформирована алюминиевая разводка: контакт к базовой области, состоящий из слоя 40, полицида тугоплавкого металла 41 и алюминия 42; контакт к эмиттерной области, состоящий из слоя 37, полицида тугоплавкого металла 38 и алюминия 39; контакт к коллекторной области, состоящий из слоя 34, полицида тугоплавкого металла 35 и алюминия 36.

Пример конкретного выполнения. Исходным материалом является структура кремния на диэлектрике (СКНД).

В полупроводниковой подложке КЭФ-4,5 (100) над диэлектриком сформирован полупроводниковый слой толщиной 1,5-2 мкм того же типа, что и подложка. В полупроводниковом слое формировали n++ слой 3 имплантацией сурьмы с Е=100 кэВ и Д=300 мкКл/см2 с последующим термическим отжигом при Т=1150°С в течение 80 мин. с параметрами ρS=15-20 Ом/□. Наращивали эпитаксиальный слой n-типа проводимости толщиной 2,0-2,5 мкм, ρv=2-3 Ом·см. Эпитаксиальный слой легировали ионной имплантацией бора с Е=40 кэВ и Д=100 мкКл/см2, осаждали первый диэлектрический слой 6 из ТЭОСа при Т=720°С, давлении 80 Па толщиной 1,5-1,6 мкм. Проводили термический отжиг для формирования будущей базовой области при Т=1000°С в течение 90 мин. Получали параметры: ρS=250-300 Ом/□ и глубину Xj=1,2-1,25 мкм. В первом диэлектрическом слое вскрывали окно под будущий контакт к коллекторной области, осаждали нитрид кремния из дихлорсилана+аммиака толщиной 0,1 мкм при давлении 15-20 Па и Т=810°С. Реакционно-ионным травлением нитрида кремния на вертикальных стенках окна формировали разделительный диэлектрик 7. Осаждали поликремний пиролизом моносилана при Т=620°С и давлении 35-40 Па толщиной 1,5-1,6 мкм. Химико-механической полировкой поликремния до планарности с диоксидом кремния 6 формировали экранирующий слой 8. В диоксиде кремния 6 вскрывали окно 9 под будущую изолирующую область, осаждали нитрид кремния из дихлорсилана+аммиака толщиной 0,1 мкм при давлении 15-20 Па и Т=810°С. Реакционно-ионным травлением нитрида кремния на вертикальных стенках окна формировали разделительный диэлектрик 7. Плазмохимическим травлением (ПХТ) в парогазовой смеси SF6+CF3 при давлении 5-7 мм. рт.ст. формировали щели под будущую изолирующую область 10 и будущий контакт 14 к коллекторной области. На вертикальных стеках щели окислением в трихлорэтилене+кислород формировали диоксид кремния 12 толщиной 0,05 мкм при Т=850°С и нитрид кремния 13 толщиной 0,1 мкм (изолирующие диэлектрики). Щели заполняли поликремнием, 15-изолирующая область и 16-контакт к коллекторной области, пиролизом моносилана при Т=620°C и давлении 35-40 Па с последующей планаризацией поликремния до планарности с первым диэлектрическим слоем 6. Плазмохимическим травлением (ПХТ) удаляли разделительные диэлектрики и поликремний в изолирующей области 15 и в контакте к коллекторной области 16 до планарности с подложкой. Удаляли первый диэлектрический слой 6, формировали второй диэлектрический слой 17 толщиной 0,05 мкм в трихлорэтилене с кислородом при Т=800°С. Под защитой фоторезиста 19 ионным легированием фосфора с Е=80 кэВ и Д-1200 мкКл/см2 вводили примесь в будущий коллекторный контакт 16 и в базовую область, слой 18 (Фиг.5). Осаждали третий диэлектрический слой 20 из ТЭОСа при Т=720°С, давлении 80 Па толщиной 0,4-0,45 мкм. Во втором и третьем диэлектрических слоях вскрывали окно под будущий контакт к эмиттерной области, осаждали нитрид кремния из дихлорсилана+аммиака толщиной 0,1 мкм при давлении 15-20 Па и Т=810°С. Реакционно-ионным травлением нитрида кремния на вертикальных стенках окна формировали разделительный диэлектрик 21. Осаждали поликремний пиролизом моносилана при Т=620°С и давлении 35-40 Па толщиной 0,4-0,45 мкм. Химико-механической полировкой поликремния до планарности с третьим диэлектрическим слоем 20 формировали экранирующий слой 22 на месте будущего эмиттерного контакта. Вскрывали в диоксиде кремния 20 и 17 окно 23 под будущий контакт к базовой области, осаждали нитрид кремния из дихлорсилана+аммиака толщиной 0,1 мкм при давлении 15-20 Па и Т=810°С. Реакционно-ионным травлением нитрида кремния на вертикальных стенках окна формировали разделительный диэлектрик 21. ПХТ в парогазовой смеси SF6+CF3 при давлении 5-7 мм. рт.ст. формировали щели 26 и 27 под будущий контакт к базовой и эмиттерной областям, соответственно. На вертикальных стеках щели окислением в трихлорэтилене+кислород формировали диоксид кремния 25 толщиной 0,05 мкм при Т=850°С и нитрид кремния 24 толщиной 0,1 мкм. Щели заполняли поликремнием 27 под контакт к базовой области, 26 под контакт к эмиттерной области, пиролизом моносилана при Т=620°С и давлении 35-40 Па с последующей планаризацией поликремния до планарности с третьим диэлектрическим слоем 20, подтравливали поликремний 26 и 27 в щелях до планарности с подложкой. Вскрывали в фоторезисте 29 окно над контактом к базовой области и легировали его ионной имплантацией бора с Е=80 кэВ и Д=300 мкКл/см2.

Под защитой фоторезиста 30 вскрывали окна над коллекторным и эмиттерным контактами, легировали их ионной имплантацией фосфора с Е=80 кэВ и Д=300 мкКл/см2. Проводили термический отжиг при Т=900°С в течение 60 мин в азоте. Получали следующие параметры: ρSЭ=10-12 Ом/□ и глубину ХJЭ=0,8-0,85 мкм, а ρSKK поликремния коллекторного контакта - (8-10) Ом/□, ρSЭK поликремния эмиттерного контакта - (10-12) Ом/□, ρSЭБ поликремниевого базового контакта- (25-30) Ом/□. Металлизированные контакты формировали напылением никеля толщиной 50 нм с отжигом в вакууме при Т=450°С 30 мин с последующим травлением непрореагировавшего никеля в H2SO4+Н2О2, далее напыляли алюминий толщиной 1 мкм и формировали металлизированные контакты, состоящие из полицида никеля 38 и алюминия 39 над контактом к эмиттерной области, из полицида никеля 41 и алюминия 42 над контактом к базовой области, из полицида никеля 35 и алюминия 36 над контактом к коллекторнойобласти. Обратные пробивные напряжения p-n перехода UKБ=300-350 В, p-n перехода UЭБ=80-90 В (при коэффициенте усиления транзистора 150-160).

Как следует из рассмотренного технического решения самосовмещенном высоковольтном интегральном транзисторе p-n переходы являются плоскими и сформированы в объеме полупроводника без выхода на поверхность подложки, что повышает напряжения пробоя p-n - переходов формирование экранирующих слоев на месте коллекторного и эмиттерного контактов позволяет обеспечить полное самосовмещение структуры, обеспечивающее повышение плотности упаковки транзисторных структур, присутствие диэлектрика под коллекторной областью способствует уменьшению емкости p-n перехода коллектор-подложка и плоские p-n переходы также уменьшают емкости p-n переходов: эмиттер-база; коллектор-база, что увеличивает быстородействие транзистора. Данная совокупность признаков позволяет решить поставленную задачу - повышения плотности компоновки транзисторных структур, увеличения их быстродействия и повышения выхода годных ИС.

Источники информации.

1. А. Блихер. Физика силовых биполярных и полевых транзисторов. Пер. с англ. под ред. И.В. Грехова. Ленинград, «Энергоатомиздат», 1986, с.37-50.

2. Ав. св-во СССР N723984 H01L 21/18.

3. Ав. св-во СССР N1135378 H01L 21/265.

4. Пат. РФ N2 356127 С2 H01L 21/ 762 - прототип.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННЫХ ТРАНЗИСТОРНЫХ СТРУКТУР | 2008 |

|

RU2377691C1 |

| САМОСОВМЕЩЕННЫЙ ВЫСОКОВОЛЬТНЫЙ ИНТЕГРАЛЬНЫЙ ТРАНЗИСТОР | 2012 |

|

RU2492551C1 |

| ВЫСОКОВОЛЬТНЫЙ САМОСОВМЕЩЕННЫЙ ИНТЕГРАЛЬНЫЙ ДИОД | 2012 |

|

RU2492552C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОСОВМЕЩЕННОГО БиКМОП ПРИБОРА | 2005 |

|

RU2295800C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ БИПОЛЯРНОГО ТРАНЗИСТОРА | 2007 |

|

RU2351036C1 |

| СПОСОБ САМОСОВМЕЩЕННОГО ФОРМИРОВАНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ И ПОЛИКРЕМНИЕВЫХ КОНТАКТОВ К ПОДЛОЖКЕ И СКРЫТОМУ СЛОЮ | 2007 |

|

RU2356127C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ САМОМАСШТАБИРОВАННОЙ САМОСОВМЕЩЕННОЙ ТРАНЗИСТОРНОЙ СТРУКТУРЫ | 2009 |

|

RU2408951C2 |

| БиКМОП-ПРИБОР И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2003 |

|

RU2282268C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ КМОП ТРАНЗИСТОРОВ С ПРИПОДНЯТЫМИ ЭЛЕКТРОДАМИ | 2006 |

|

RU2329566C1 |

| СПОСОБ СОЗДАНИЯ ВЕРТИКАЛЬНОГО PNP ТРАНЗИСТОРА В СОСТАВЕ ИС | 1995 |

|

RU2106037C1 |

Использование: микроэлектроника, полупроводниковая электроника, самосовмещенный высоковольтный интегральный транзистор может быть использован в производстве интегральных микросхем. Сущность изобретения: у самосовмещенного, высоковольтного транзистора р-n переходы сформированы в объеме полупроводниковой подложки без выхода на поверхность, а контакты к областям транзистора, изолированные в вертикальной части разделительными диэлектриками от областей транзистора, которые контактируют донной частью к последним. Высоковольтный интегральный транзистор изолирован от подложки диэлектрическим слоем. Самосовмещение в структуре достигается использованием экранирующего слоя над контактом к коллекторной области при формировании щелей под контакт к коллекторной и изолирующей областям и экранирующих слоев над контактами к эмиттерной области при формировании щелей под контакты к базовой и эмиттерной областям. Техническим результатом изобретения является повышение пробивных напряжений р-n переходов интегрального транзистора, повышение плотности компоновки транзисторных структур и увеличение их быстродействия. 2 з.п. ф-лы, 10 ил.

1. Способ изготовления самосовмещенного высоковольтного интегрального транзистора, включающий формирование коллекторной области легированием кремниевого слоя, расположенного над диэлектрическим слоем, примесью первого типа проводимости, наращивание эпитаксиального слоя первого типа проводимости, формирование в эпитаксиальном слое области второго типа проводимости легированием примесью, формирование над областью второго типа проводимости первого диэлектрического слоя, вскрытие в нем окна под будущий контакт к коллекторному слою, формирование на вертикальных стенках окна разделительного диэлектрика, формирование в окне экранирующего слоя, вскрытие в первом диэлектрическом слое окна под будущую изолирующую область, формирование на вертикальных стенках окна разделительного диэлектрика, формирование щелей для изолирующей и контакта к коллекторной областям, одновременным травлением кремния в окне под изолирующую область до диэлектрика, расположенного под коллекторной областью и в окне травлением экранирующего слоя и кремния, на месте будущего контакта к коллекторной области, формирование на вертикальных стенках щелей изолирующих диэлектриков, заполнение щелей слоем, планаризацию слоя до первого диэлектрического слоя, удаление слоя в щелях до планарности с подложкой, удаление первого диэлектрического слоя, формирование второго диэлектрического слоя, формирование области первого типа проводимости в области второго типа проводимости, формирование третьего диэлектрического слоя, вскрытие окон во втором и третьем диэлектрических слоях под будущий контакт к области второго типа проводимости, вскрытие в нем окна под будущий контакт к области первого типа проводимости, формирование на вертикальных стенках окон разделительного диэлектрика, формирование в окне экранирующего слоя под будущий контакт к эмиттерному слою, формирование щели травлением кремния в окне под будущий контакт к базовой области, а в окне на месте будущего контакта к эмиттерной области травлением экранирующего слоя и части базового слоя, формирование на стенках щелей изолирующих диэлектриков, заполнение щелей слоем, его планаризацию до третьего диэлектрического слоя, травление слоя в щелях до планарности со слоем в изолирующей области, легирование контакта к базовой области примесью второго типа проводимости под защитой фоторезиста, легирование контакта к эмиттерной области примесью первого типа проводимости под защитой фоторезиста, термический отжиг для формирования эмиттерной области и перераспределения примеси в контактах до областей транзистора, формирование полицида тугоплавких металлов к контактам, формирование металлизированной разводки.

2. Способ по п.1, отличающийся тем, что толщина экранирующего слоя над контактом к коллекторной области равна n++ легированному слою, расположенному над диэлектрическим слоем, а толщина экранирующего слоя над контактом к эмиттерной области равна половине глубины залегания эмиттерного p-n перехода, а глубина травления щели под контакт к базовой области равна 0,85-0,9 глубины залегания p-n перехода базовой области.

3. Способ по п.1, отличающийся тем, что контакт к эмиттерной области формируется в планарном исполнении.

| СПОСОБ САМОСОВМЕЩЕННОГО ФОРМИРОВАНИЯ ИЗОЛЯЦИИ ЭЛЕМЕНТОВ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ И ПОЛИКРЕМНИЕВЫХ КОНТАКТОВ К ПОДЛОЖКЕ И СКРЫТОМУ СЛОЮ | 2007 |

|

RU2356127C2 |

| БИПОЛЯРНЫЙ ТРАНЗИСТОР ИНТЕГРАЛЬНОЙ СХЕМЫ | 1997 |

|

RU2108640C1 |

| ИНТЕГРАЛЬНЫЙ БИПОЛЯРНЫЙ ТРАНЗИСТОР | 1989 |

|

SU1831966A3 |

| US 6287930 B1, 11.09.2001 | |||

| US 6627972 B1, 30.09.2003 | |||

| US 4829015 A, 09.05.1989 | |||

| US 4745087 A, 17.05.1988. | |||

Авторы

Даты

2013-09-10—Публикация

2012-04-05—Подача