Изобретение относится к радиоэлектронике и может использоваться для управления исполнительными устройствами постоянного и переменного тока в системах автоматического регулирования.

Известен двухтактный усилитель мощности, в котором для исключения сквозных токов, возникающих при переключении выходных транзисторов, вводится задержка включения закрытого транзистора на время заведомо большее, чем время рассасывания неосновных носителей в базе открытого транзистора 1.

В этом усилителе мощности исключение сквозных токов из-за фиксированного времени задержки включения закрытого транзистора не позволяет учитывать частотные свойства конкретных экземпляров выходных транзисторов, что ограничивает быстродействие усилителя мощности.

Наиболее близким к изобретению по технической сущности является усилитель мощност,., содержащий первый и второй входные транзисторы, базы которых объединены, эмиттеры соединены с общей щиной, а коллекторы соответственно через первый и второй резистивные делители, соединены соответственно с первой и второй щинами источника питания, выполненного со средней точкой, к которым также подключены эмиттеры соответственно первого и второго управляющих транзисторов, базы которых подключены к отводам соответственно первого и второго резистивных делителей, а коллекторы - к базам соответственно первого и второго выходных транзисторов, включенных по схеме с общим эмиттером, причем структура второго входного и первых управляющего и выходного транзисторов противоположна структуре первого входного и вторых управляющего и выходного транзисторов, а нагрузка соединена с общим выводом диодов, включенных в коллекторные цепи первого и второго выходных транзисторов 2.

В известном усилителе мощности через диоды, включенные в коллекторные цепи первого и второго выходных транзисторов, протекает ток нагрузки, имеющий значение в мощных усилителях от единиц до десятков ампер, что приводит к дополнительным значительным потерям мощности, примерно равным потерям на первом и втором выходных транзисторах. Быстродействие известного усилителя мощности ограничено верхней рабочей частотой применяемых силовых диодов, что не позволяет использовать частотные свойства современных мощных высокочастотных транзисторов. Это приводит к уменьщению КПД и ухудшению динамических характеристик систем управления, построенных на базе известного усилителя мощности.

Цель изобретения - повышение быстродействия и КПД.

Цель достигается тем, что в усилитель мощности, содержащий первый и второй входные транзисторы, базы которых объединены, эмиттеры соединены с общей шиной, а коллекторы соответственно через первый и второй резистивные делители соединены соответственно с первой и второй шинами источника питания, выполненного со средней точкой, к которым также подключены эмиттеры соответственно первого и вто0 рого управляющих транзисторов, базы которых подключены к отводам соответственно первого и второго резистивных делителей, а коллекторы - к базам соответственно первого и второго выходных транзисторов,

включенных по схеме с общим эмиттером, причем структура второго входного и первых управляющего и выходного транзисторов противоположна структуре первого входного и вторых управляющего и выходного транзисторов, введены первый и второй коммутирующие и лервый и второй дополнительные транзисторы, включенные по схеме с общим эмиттером, первый и второй дополнительные резистивные делители, включенные параллельно соответственно первому и второму резистивным делителям, а также первый и второй резисторы, включенные между базой соответственно первого и второго выходных транзисторов и коллектором соответственно второго и первого коммутирующих транзисторов, базы которых подключены к отводам соответственно второго и первого дополнительных резистивных делителей, а коллекторы первого и второго дополнительных транзисторов подключены к базам соответственно второго и первого дополнительных транзисторов и

отводам соответственно второго и первого резистивных делителей, причем структура первых коммутирующего и дополнительного транзисторов соответствует структуре первого выходного транзистора и противопоQ ложна структуре второго выходного транзистора, коллекторы которых объединены и подключены к нагрузке. ,

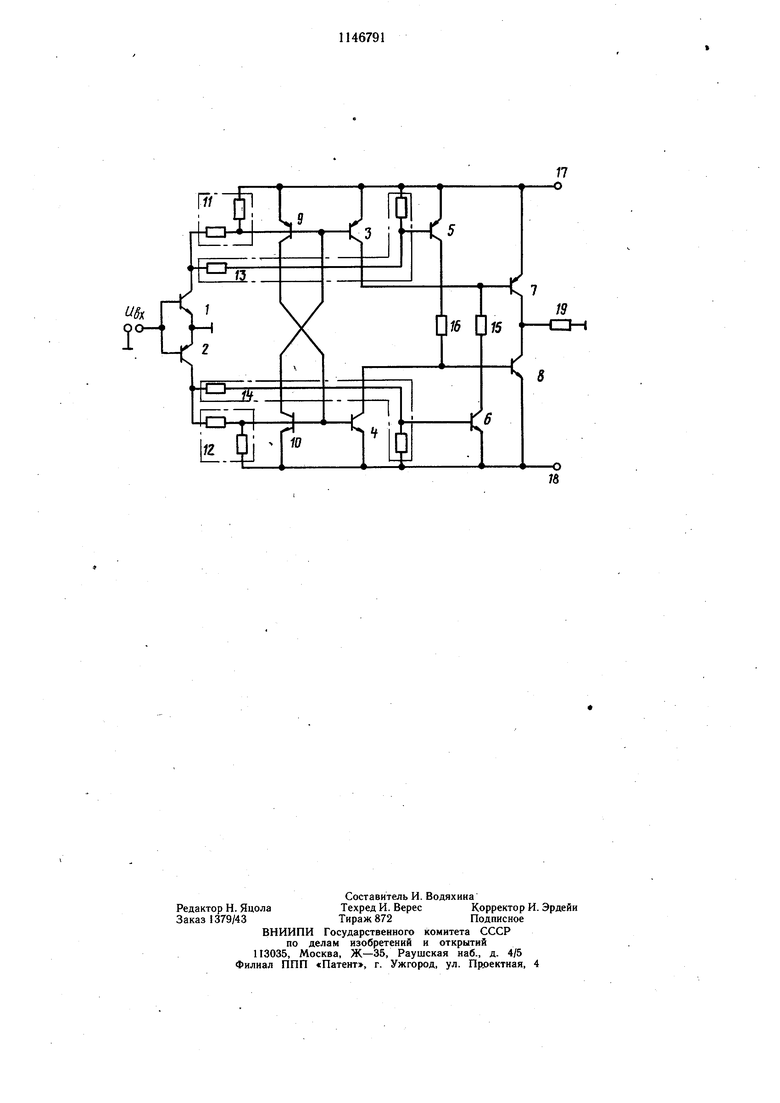

На чертеже представлена принципиальная схема усилителя мощности.

Усилитель мощности -содержит первый и

5 второй входные транзисторы 1 и 2, первый и второй управляющие транзисторы 3 и 4, первый и второй коммутирующие транзисторы 5 и 6, первый и второй выходные транзисторы 7 и 8, первый и второй дополнительные транзисторы 9 и 10, первый и второй резистивные делители 11 и 12, пер- вый и второй дополнительные резистивные делители 13 и 14, первый и второй резисторы 15 и 16, первую и вторую щины 17 и 18 источника питания и нагрузку 19.

5 Усилитель мощности работает следующим образом.

При отрицательно м входном напряжении первые входной управляющий, коммутирующий и дополнительный транзисторы 1, 3, 5

и 9 и второй выходной транзистор 8 закрыты, а второй входной транзистор 2 открыт, потенциал его коллектора примерно равен потенциалу общей точки питания, что обеспечивает положительное смещение на базах вторых управляющего, коммутирующего и дополнительного транзисторов 4, 6 и 10:

Коллекторный ток второго коммутирующего транзистора 6 протекает от первой (плюсовой) шины 17 источника питания через базо-эмиттерный переход первого выходного транзистора 7 и открывает его, обеспечивая ток в нагрузке Ш. С целью уменьщения времени открывания мощности первого выходного транзистора 7, а также уменьщения рассеиваемой мощности, коллекторный ток второго коммутирующего транзистора 6 выбирается из условия обеспечения насыщения первого выходного транзистора 7.

Так как первый коммутирующий транзистор 5 закрыт, а ток обратно смещенного перехода коллектор-база второго выходного транзистора 8 пренебрежимо мал, можно считать, что ток коллектора второго управляющего транзистора 4 равен нулю. Несмотря на то, что через базо-эмиттерньге переходы первых управляющего и дополнительного транзисторов 3 и 9 коллектор второго дополнительного транзистора 10 подключен к первой (плюсовой) шине 17 источника питания и имеет базовое смещение, ток коллектора этого транзистора также равен нулю. Это можно объяснить следующим образом. Вторые управляющий и дополнительный транзисторы 4 и 10 (также как и 3 и 9) образуют связанную симметричную структуру. Напряжения на базо-эмиттерных переходах вторых управляющего и дополнительного транзисторов 4 и 10 равны. В связи с тем, что ток коллектора второго управляющего транзистора 4 равен нулю, его статическое входное сопротивление мало, базоэмиттерное напряжение также мало, весь ток, поступающий от второго входного транзистора 2 в точку включения баз вторых управляющего и дополнительного транзисторов 4 и 10, стекает на вторую (отрицательную) шину 18 источника питания через открытый базо-эмиттерный переход второго управляющего транзистора 4. Наличие напряжения между коллекторо.м и эмиттером второго дополнительного транзистора 10 определяет большее статическое входное сопротивление и более высокий открывающий потенциал базо-эмиттерного перехода по сравнению с вторым управляющим транзистором 4. При этом базо-эмиттерный переход второго дополнительного транзистора 10 и, следовательно, ток его коллектора равен нулю.

При смене полярности входного напряжения второй входной транзистор 2 закрывается, за. ним закрыва ется второй коммутирующий транзистор 6, а первый входной транзистор I открывается, открывая первые управляющий, коммутирующий и дополнительный транзисторы 3, 5 и 9. Через первый управляющий транзистор 3 протекает коллекторный ток рассасывания заряда неосновных носителей из базы первого выходного транзистора 7. Коллекторный ток первого управляющего транзистора 3 обуславливает коллекторный ток первого дополнительного транзистора 9, поэтому остается открытым второй управляющий транзистор 4 шунтирующий базо-эмиттерный переход второго выходного транзистора 8. После завершения рассасывания избыточного заряда в базе первого выходного транзистора 7 и перехода его в режим отсечки, коллекторный ток первого управляюшего транзистора 3 стремится к нулю, что приводит к резкому возрастанию его базового тока. При этом первый дополнительный транзистор 9 закрывается, что свидетельствует о завершении процесса выключения первого выходного транзистора 7. Вслед за первым дополнительным транзистором 9 выключается второй управляюший транзистор 4, коллекторный ток первого коммутирующего транзистора 5 переключается в базу второго выходного транзистора 8.

В предлагаемом усилителе, .мощности мощность, рассеиваемая в первом и втором дополнительных транзисторах 9 и 10 и пер-, вом и. втором управляющих транзистора.ч 3 и 4 в статическом режиме, равна нулю. Мощность, рассеиваемая в этих транзисторах при переключении плеч усилителя мощности, значительно (на два-три порядка) меньше .мощности, рассеиваемой в диодах известного усилителя, что обеспечивает более вь1сокий КПД по сравнению с известным усилителем, предельное быстродействие переключения первого и второго выходных транзисторов 7. и 8 и сохранение высокой надежности, что обусловлено отсутствием сквозных токов.

n

о

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор напряжения | 1989 |

|

SU1756867A1 |

| СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ | 1989 |

|

RU2028657C1 |

| Многоканальный коммутатор | 1979 |

|

SU843236A1 |

| Стабилизирующий источник постоянного напряжения | 1987 |

|

SU1439557A1 |

| Двухтактный усилитель мощности | 1983 |

|

SU1202019A1 |

| Двухтактный усилитель мощности | 1986 |

|

SU1350817A1 |

| Регулятор напряжения для генератора переменного тока | 1983 |

|

SU1109850A1 |

| Коммутатор | 1975 |

|

SU832721A1 |

| МОЩНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 1991 |

|

RU2017322C1 |

| Устройство выборки и хранения | 1980 |

|

SU921087A1 |

УСИЛИТЕЛЬ МОЩНОСТИ, содержащий первый и второй входные транзисторы, базы которых объединены, эмиттеры соединены с общей шиной, а коллекторы соответственно через первый и второй резистивные делители соединены соответственно с первой и второй шинами источника питания, выполненного со средней точкой к которым также подключены эмиттеры соответственно первого и второго управляющих транзисторов, базы которых подключены к отводам соответственно первого и второго резистивных делителей, а коллекторы - к базам соответственно первого и второго выходных транзисторов, включенных по с общим Эмиттером, причем структура второго входного-и первых управляющего и выходного транзисторов противоположна структуре первого входного и вторых управляющего и выходного транзисторов, отличающийся тем, что, с целью повыщения его быстродействия и КПД, в него введены первый и второй коммутирующие и первый и второй дополнительные транзисторы, включенные по схеме с общим эмиттером, первый и второй дополнительные резистивные делители, включенные параллельно соответственно первому и второму резистивным делителям, а также первый и второй резисторы, включенные между базой соответственно первого и второго выходных транзисторов и коллектором соответственно второго и первого коммутирующих транзисторов, базы которых подключены к отводам соответственно второго и первого дополнительных резистивных делителей, а коллекторы пер(Л вого и BTOporq дополнительных транзисторов подключены к базам соответственно второго и первого дополнительных транзисторов и отводам соответственно второго и первого резистивных делителей, причем структура первых коммутирующего и дополнительного транзисторов соответствует структуре первого выходного транзистора и противоположна структуре второго выходО) ного транзистора, коллекторы которых объе динены и подключены к нагрузке. со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Мостовой регулятор мощности | 1979 |

|

SU788099A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Усилитель мощности | 1977 |

|

SU896751A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-03-23—Публикация

1983-06-17—Подача