л

42ь Од 00 N5

Изобретение относится к технике связи и может использоваться в системах связи с различными видами модуляции, особенно в системах с потерей постоянной составляющей при передаче цифровых сигналов.

Известен регенератор цифровых сигналов, содержащий входной усилитель, формирователь выходных информационных импульсов, вьщелитель тактовой частоты и двухполярный детектор ij .

Однако известный регенератор имеет низкую помехоустойчивость.

Цель изобретения - повьшение помехоустойчивости.,

Для достижения цели в регенератор цифровых сигналов, содержащий входной усилитель, формирователь выходных информационных импульсов, вьщелитель тактовой частоты и двухполярньй детектор, введены блок регулирования порога и компаратор, выход которого подключен к входу выделителя тактовой частоты и к первому входу формирователя выходных информа ционных импульсов, второй вход которого соеди-нен с выходом выделителя тактовой частоты, при этом выход входного усилителя подключен к первому входу компаратора и к входу двухполярного дeтeкtopa, выход которого соединен с входом блока регулирования порога, выход которого подключен к второму входу компаратора.

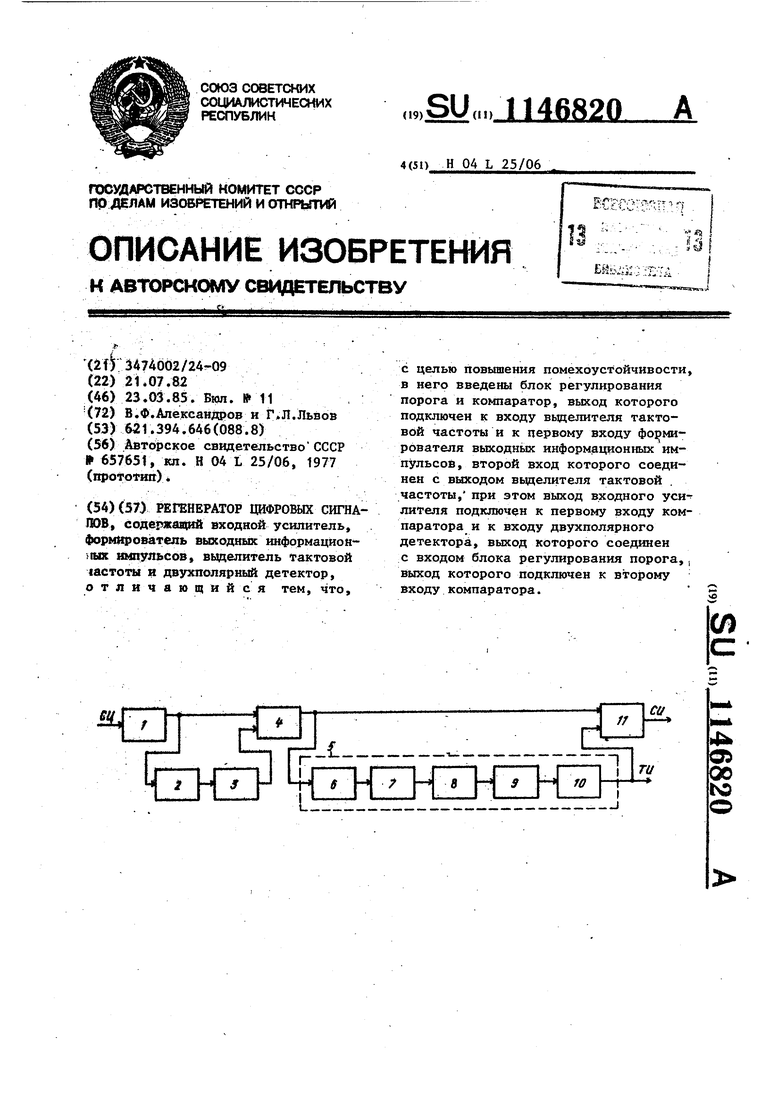

На чертеже представлена структурная электрическая схема предложен- ногр регенератора.

Регенератор цифровых сигналов содержит входной усилитель 1, двухполярный детектор 2, блок 3 регулирования порога, компаратор 4, выделитель 5 тактовой частоты, состоящий из формирователя 6 коротких импульсов, в ысокоизбирательного резонансного блока 7, усилителя 8, решаю блока 9 и элемента задержки 10, формирователь 11 вькодных информационных импульсов.

Регенератор цифровых сигналов работает .следующим образом.

Выходной сигнал поступает на входной усилитель 1, где усиливается до уровня, необходимого для работы двухполярного детектора 2 в линейном режиме, причем диоды Двухполярногодетектора 2 включены последовательно через резистивную нагрузку (не показана) , постоянная времени заряда

Двухполярного детектора не превышает длительности одного бита информации. Выходной сигнал Двухполярного детектора 2 снимается со средней точки резистивной нагрузки и подается на один вход компаратора 4. Такое построение Двухполярного детектора позволяет следить за структурой приходящего сигнала, т.е. при преобладании в нем единиц выходной сигнал смещает порог принятия решения в компараторе 4 в положительную область, а при преобладании нулей1-в отрицательную область, при равновероятном распределении нулей и единиц выходной уровень двухполярного детектора близок к нулю. В моменты изменения уровня входйого сиг- нала синхронно изменяется и порог принятия решения, этим обеспечивается поддержание работы компаратора в оптимальном режиме, которьй первоначально может выставляться блоком 3 регулирования порога на управляющем входе компаратора 4.

Таким образом, данная схема позволяет автоматически независимо от структуры и амплитуды сигнала поддерживать в компараторе 4 оптимальный порог принятия решения. Сигнал о выходе компаратора 4 поступает на вход вьщелителя 5 тактовой частоты, которьй представляет собой.последовательно включенные формирователь 6 коротких импульсов, синхронных по времени с моментами появления переднего и заднего фронтов импульсов с выхода компаратора 4 и поступает на высокоизбирательный резонансный блок.7, где вьщеляется первая гармоника синхронизирующего сигнала, а с его выхода на усилитель 8, в котором производится усиление сигнала до уровня, необходимого для работы решакнцего блока 9, который представляет собой компаратор, управляющий вход которого заземлен, и таким образом на выходе решающего блока 9 появляются сигналы в моменты пересечения нулевого уровня qинxpoнизиpyющeго сигнала с выхода высокоизбирательного, резонансного блока 7. Сигнал с выхода решающего блока 9 через элемент задержки 10 поступает на синхронизирующий вход формир.ователя 11 выходных информационных импульсов, представляющий собой триггер, на второй вход которого подан сигнал с вы311468204

хода компаратора 4. Подбирая времяуправлением уровня принятия решения

задержки элемента задержки 10, доби-уменьшает в 10-100 раз потери достоваются оптимальной точки принятияверности регенерируемой информации

решения по времени.за счет регенератора от воздействия

Применение в цифровых линейныхчто позволяет повысить качество петрактах предложенного регенератораредачи сигнала по цифровому линейноцифровых сигналов с автоматическимму тракту.

5на него дестабилизирующих факторов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Регенератор цифровых сигналов | 1985 |

|

SU1309326A1 |

| Устройство для подавления фазового дрожания | 1983 |

|

SU1218482A1 |

| Устройство для контроля цифрового канала связи | 1985 |

|

SU1358099A1 |

| Многолучевая система радиосвязи | 1980 |

|

SU886275A2 |

| Регенератор цифровых сигналов с квантованной обратной связью | 1987 |

|

SU1434552A1 |

| Регенератор многоуровнего цифрового биполярного сигнала | 1981 |

|

SU1012453A1 |

| Многоуровневый регенератор биполярных сигналов | 1986 |

|

SU1405120A1 |

| Устройство для воспроизведения цифрового сигнала с носителя магнитной записи | 1987 |

|

SU1510002A1 |

| Регенератор цифровых сигналов с квантованной обратной связью | 1986 |

|

SU1406804A2 |

| Многоуровневый регенератор биполярных сигналов | 1983 |

|

SU1172030A1 |

РЕГЕНЕРАТОР 1ЩФРОИЛХ СИГНАЛОВ, входной усилитель, формирователь выходных информационяьк юшуяьсов, вьщелитель тактовой fастоты и двухполярный детектор, отличающийся тем, что. с целью повышения помехоустойчивости, в него введены блок регулирования порога и компаратор, выход которого подключен к входу вьщелителя тактовой частоты и к первому входу формирователя выходных информационных импульсов, второй вход которого соединен с выходом выделителя тактовой частоты, при этом выход входного усилителя подключен к первому входу компаратора и к входу двухполярного детектора, выход которого соединен с входом блока регулирования порога,, Выход которого подключен к второму Входу компаратора.

| Регенератор цифровых сигналов с автоматической регулировкой усиления | 1977 |

|

SU657651A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-03-23—Публикация

1982-07-21—Подача