« Изобретение относится к телемеханике и предназначено для выполнения функций многоточечного контроля датчиков с примерно равной частотой сигналов датчиков.

По основному авт.св.№ 841007 известно устройство, содержащее последовательно соединенные тактовый генерат.ор, распределитель, коммутатор, анализатор, блок памяти, первый и второй блоки сравнения и блок запи си информации, выход которого соединен с вторым входом блока памяти, , вьЕход анализатора соединен Также с вторым входом второго блока сравнения, а второй выход анализатора соединен с первым входом блока выдачи сигналов об отклонении, второй вход которого соединен с выходом блока контроля, на вход которого подключен второй выход распределителя, второй выход блока контроля соединен с вторым входом анализатора, третий вход которого соединен с вторым выходом первого блока сравнения, второй вход которого соединен с третьим входом блока контроля.

В устройстве-прототипе реализован дифференциальный контроль частоты сигналов датчиков друг относительно друга, который существенно улучшает характеристики традиционных устройств, осуществляющих контроль частоты сигналов датчиков относительно постоянно за:данного значения частоты J.

Однако в устройстве возможно нарушение контроля при случайном сбое в блоке памяти. Например, если при кратковременном пропадании напряжения питанияустройства в блоке памяти устанавливается значение частоты, относительно которой сигналы датчиков с номинальной частотой воспринимаются как аномальные, то формируется сигнал отклонения частоты и осуществляется запрет на перезапись в блоке памяти до срабатывания блока контроля, который срабатывает один раз на несколько циклов контроля, при этом во внешние цепи выдается ложный сигнал отклонения, что снижает достоверность контроля.

Цель изобретения - повышение достоверности контроля.

Поставленная цель достигается тем, что в устройство для многоканального контроля введены блок под53337J

тверждения сигналов отклонения и элемент ИЛИ,выход и первый вход элемента ИЛИ подключены соттветственно между входом блока записи информации и первым выходом первого блока сравнения, между вторым выходом которого и третьим входом анализатора подключены соответственно первый вход и первый выход блока подтверждения сиг0 налов отклонения, второй вход и второй выход которого подключены соответственно к второму выходу распределителя и второму входу элемента ИЛИ,

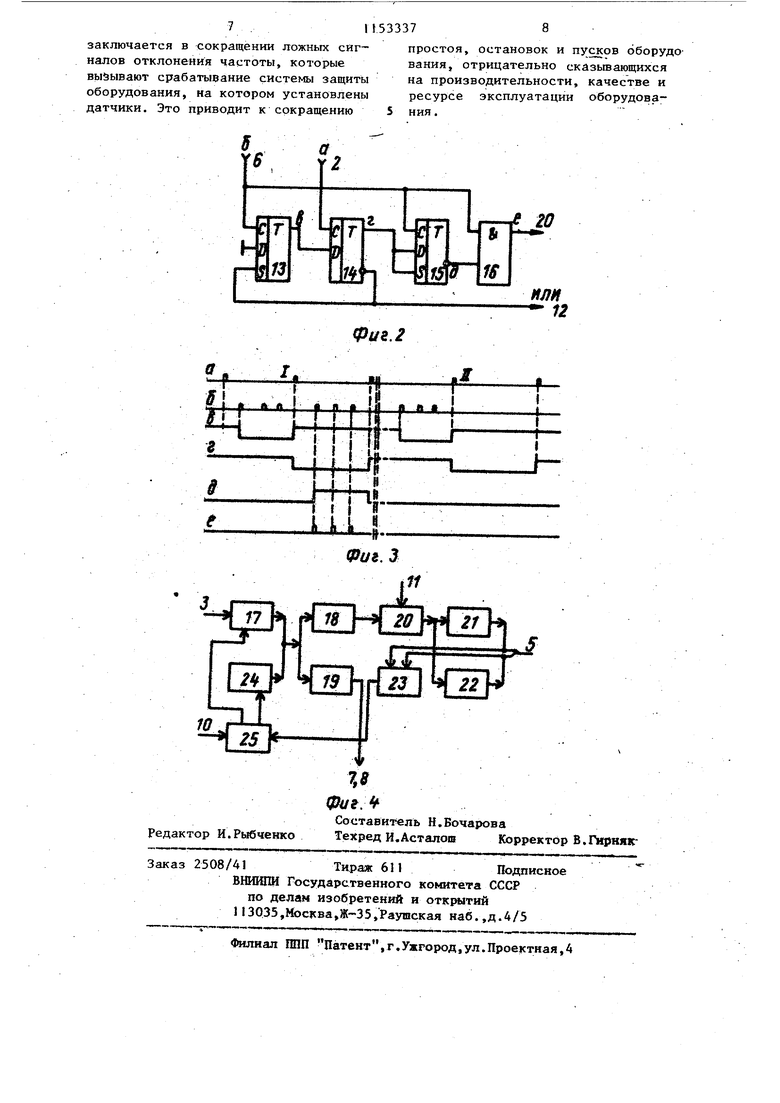

Кроме того, блок подтверждения

сигналов отклонения вьтолнен на триггерах и элементе И, прямой выход первого триггера соединен с 3)-входом второго триггера , прямой выход

которого соединен с объединенными D,- и S -входами третьего триггера, инверсный выход которого соединен с первым входом элемента И, П-вход первого триггера подключен кшине нулевого

потенциала, объединенные С-входы первого и третьего триггеров и второй вход элемента И, и С-вход второго триггера являются соответстведио первым и вторым входами блока подтверж)

дения сигналов отклонения, ;выход . элемента И и объединенные инверсный выход второго триггера и 5-вход первого триггера являются соответственно первым и вторым выходами блока

подтверждения сигналов отклонения.

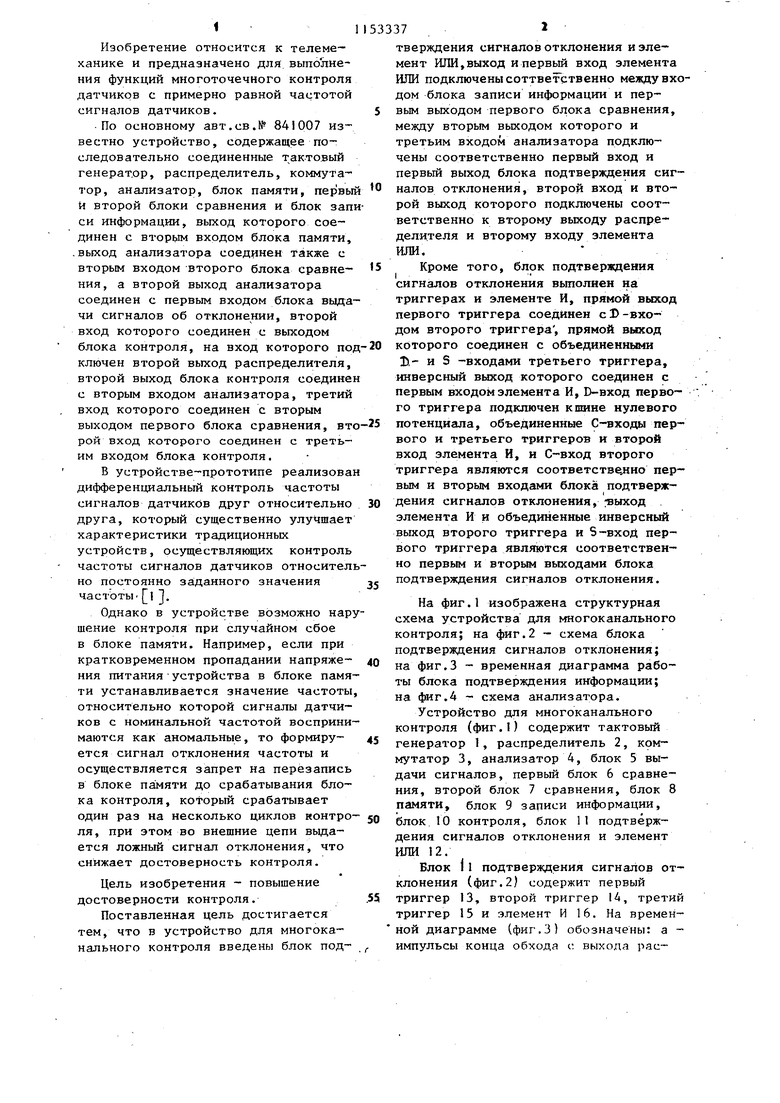

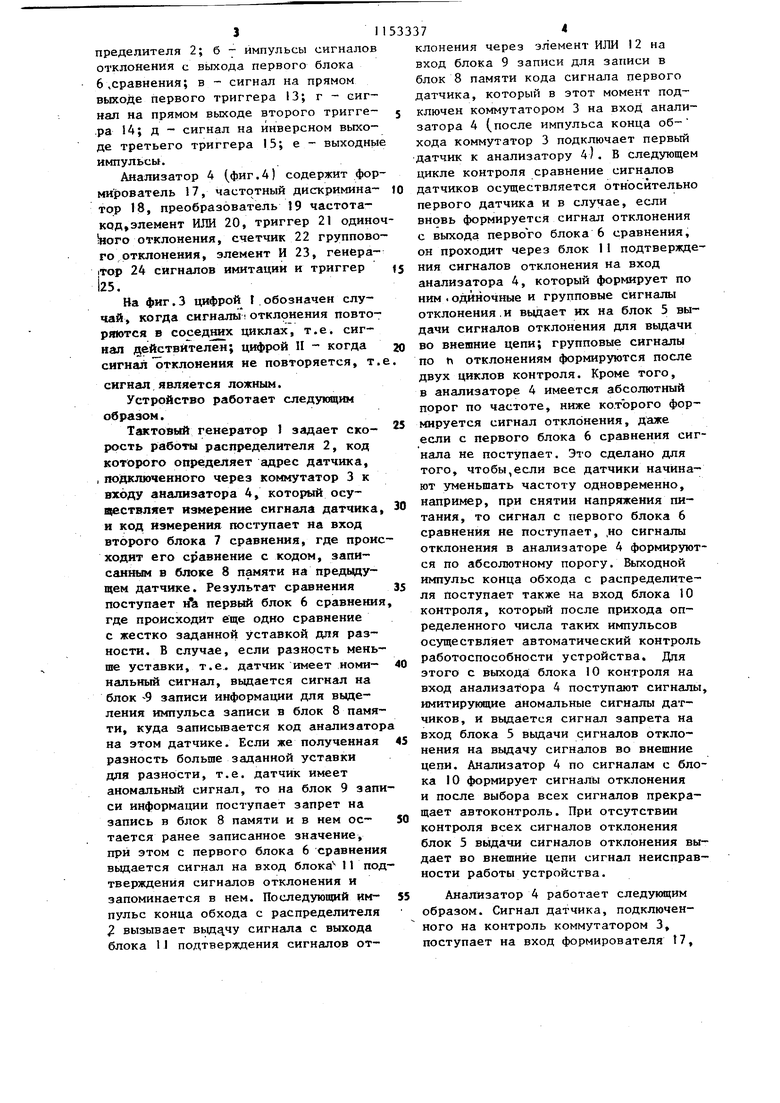

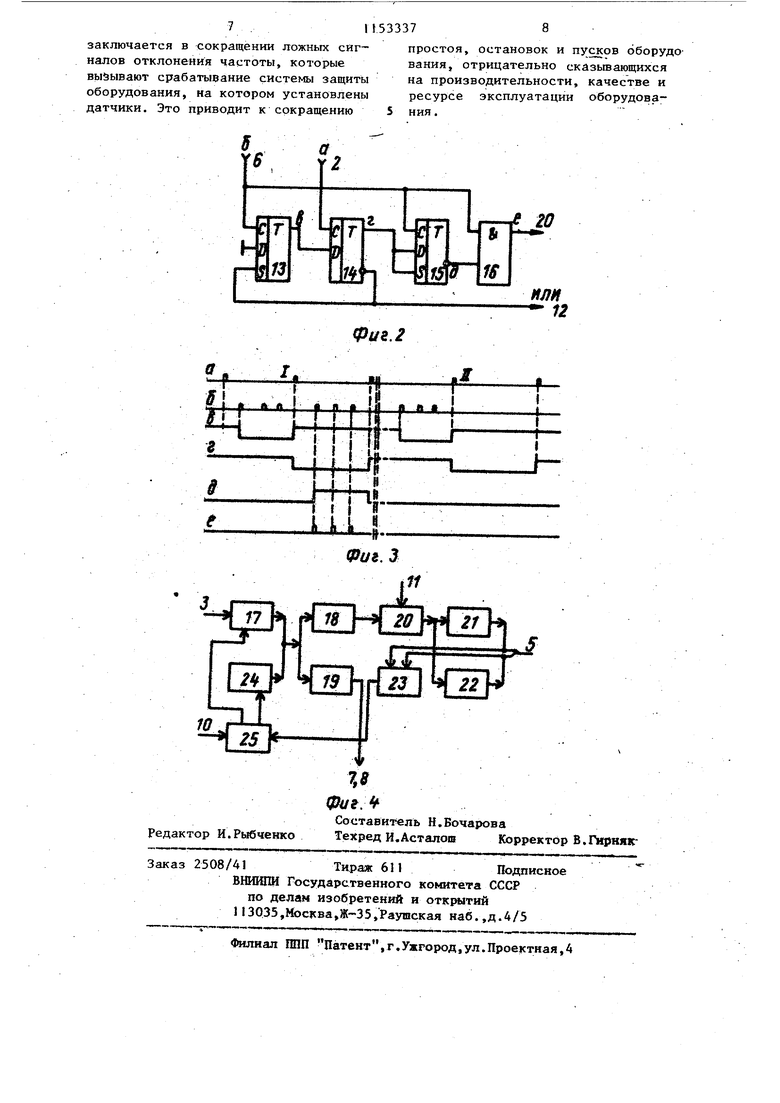

На фиг.1 изображена структурная схема устройства для многоканального контроля; на фиг.2 - схема блока подтверждения сигналов отклонения;

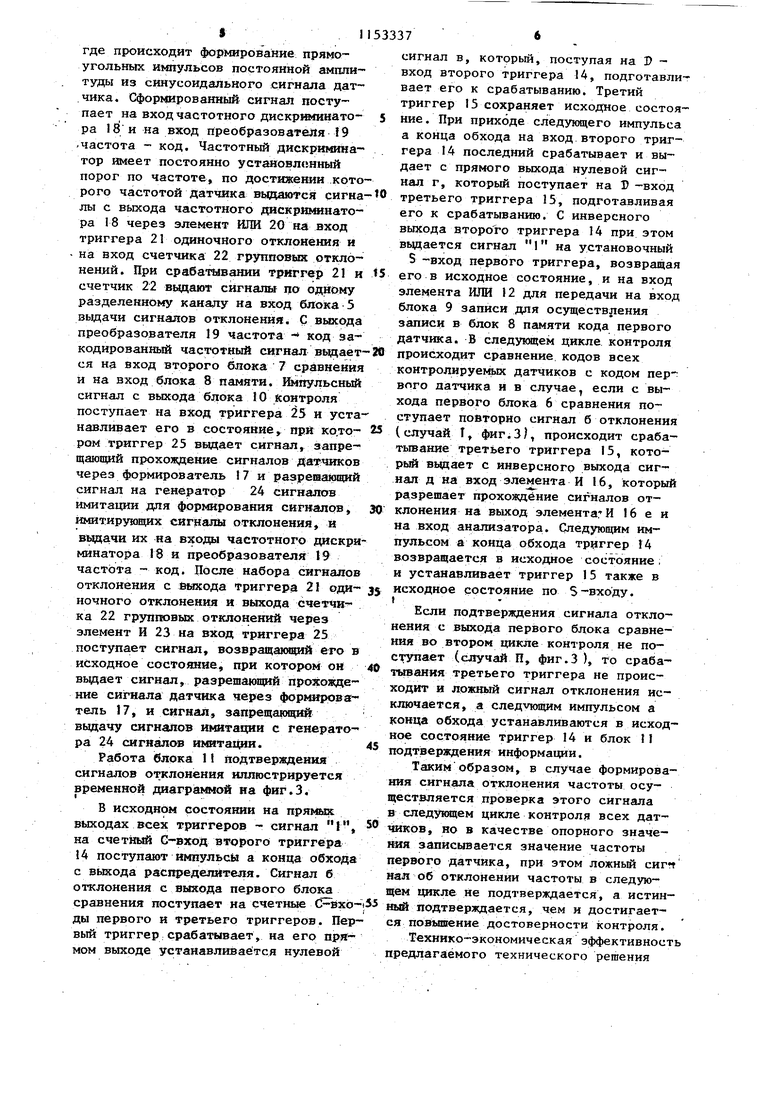

на фиг.З - временная диаграмма работы блока подтверждения информации; на фиг.4 - схема анализатора.

Устройство для многоканального контроля (фиг.I) содержит тактовый

генератор 1, распределитель 2, крммутатор 3, анализатор 4, блок 5 выдачи сигналов, первый блок 6 сравнения, второй блок 7 сравнения, блок 8 памяти, блок 9 записи информации,

блок.10 контроля, блок 11 подтверждения сигналов отклонения и элемент ИЛИ 12.

Блок I1 подтверждения сигналов отклонения (фиг.2) содержит первый

триггер 13, второй триггер 14, третий

триггер 15 и элемент И 16. На нремен ной диаграмме (фиг.З) обозначены: а импульсы конца обхода с. выхода распределителя 2; б - импульсы сигналов отклонения с выхода первого блока 6;сравнения; в - сигнал на прямом выходе первого триггера 13; г - сигнал на прямом выходе второго тригге.ра 14; д - сигнал на инверсном выходе третьего триггера 15; е - выходны импульсы.

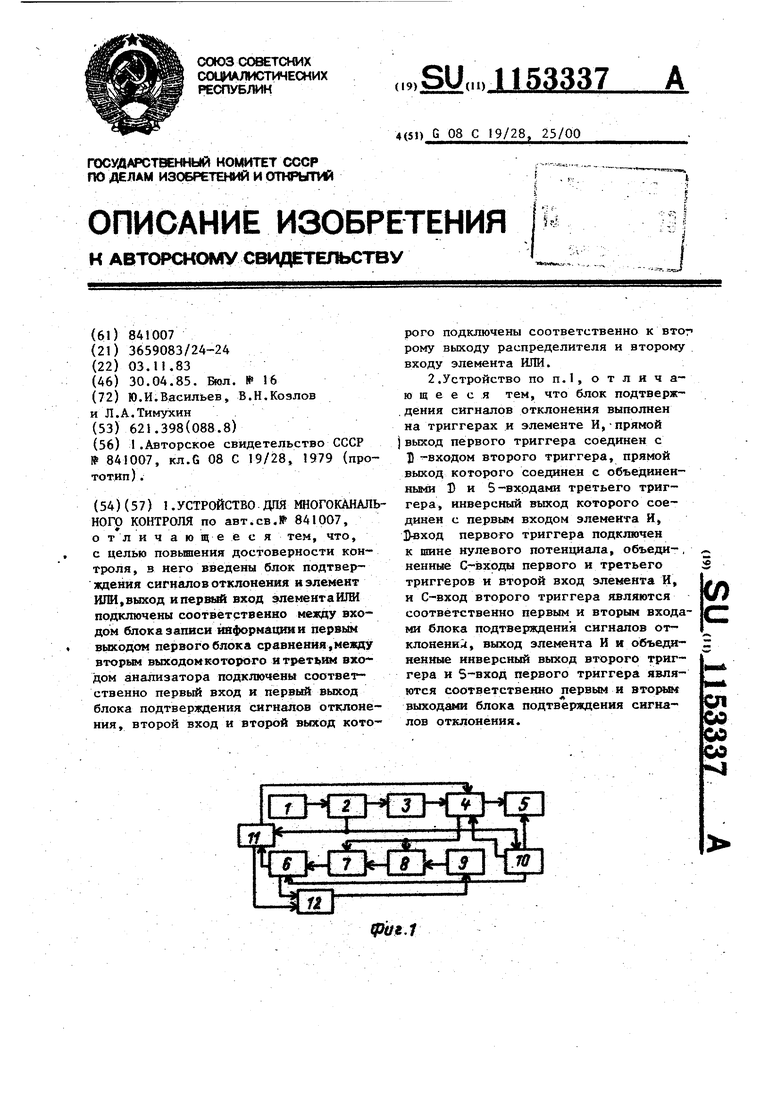

Анализатор 4 (фиг.4) содержит формирователь 17, частотный дискриминатор 18, преобразователь 19 частотакод,элемент ИЛИ 20, триггер 21 одино1ного отклонения, счетчик 22 группового отклонения, элемент И 23, генераiTop 24 сигналов имитации и триггер 125.

На фиг.3 цифрой обозиачен случай, когда сигналы отклонения повторяются в соседних циклах, т.е. сигнал действителен; цифрой II - когда сигнал Отклонения не повторяется, т.

сигнал является ложным.

Устройство работает следукяцим образом.

Тактовый генератор 1 задает скорость работы распределителя 2, код которого определяет адрес датчика, , подключенного через коммутатор 3 к входу анализатора 4, который осув ствляет измерение сигнала датчика, и код измерения поступает на вход второго блока 7 сравнения, где происходит его сравнение с кодом, записанным в блоке 8 памяти на предыдущем датчике. Результат сравнения поступает ifa первый блок 6 сравнения где происходит еще одно сравнение с жестко заданной уставкой для разности. В случае, если разность меньше уставки, т.е,. датчик имеет номи- нальный сигнал, выдается сигнал на блок 9 записи информации для выделения импульса записи в блок 8 памяти, куда записьшается код анализатор на этом датчике. Если же полученная разность больше заданной уставки для разности, т.е. датчик имеет аномальный сигнал, то на блок 9 записи информации поступает запрет на запись в блок 8 памяти и в нем ос- тается ранее записанное значение, при этом с первого блока 6 сравнения выдается сигнал на вход блока 11 подтверждения сигналов отклонения и запоминается в нем. Последующий импульс конца обхода с распределителя 2 вызывает сигнала с выхода блока 11 подтверждения сигналов отклонения через элемент ИЛИ 12 на вход блока 9 записи для записи в блок 8 памяти кода сигнала первого датчика, который в этот момент подключен коммутатором 3 на вход анализатора 4 (после импульса конца обхода коммутатор 3 подключает первый датчик к анализатору 4). В следующем цикле контроля сравнение сигналов датчиков осуществляется относительно первого датчика н в случае, если вновь формируется сигнал отклонения с выхода первого блока 6 сравнения, он проходит через блок 11 подтверждения сигналов отклонения на вход анализатора 4, который формирует по ним .одиночные и групповые сигналы отклонения.и выдает их на блок 5 выдачи сигналов отклонения для выдачи во внешние цепи; групповые сигналы по г отклонениям формируются после двух циклов контроля. Кроме того, в анализаторе 4 имеется абсолютный порог по частоте, ниже которого формируется сигнал отклонения, даже если с первого блока 6 сравнения сигнала не поступает. Это сделано для того, чтобы,если все датчики начинают уменьшать частоту одновременно, например, при снятии напряжения питания, то сигнал с первого блока 6 сравнения не поступает, ,но сигналы отклонения в анализаторе 4 формируются по абсолютному порогу. Выходной импульс конца обхода с распределителя поступает также на вход блока 10 контроля, которьтй после прихода определенного числа таких импульсов осуществляет автоматический контроль работоспособности устройства. Для этого с выхода блока 10 контроля на вход анализатора 4 поступают сигналы имитнрующие аномальные сигналы датчиков, и выдается сигнал запрета на вход блока 5 выдачи сигналов отклонения на выдачу сигналов во внешние цепи. Анализатор 4 по сигналам с блока 10 формирует сигналы отклонения и после выбора всех сигналов прекращает автоконтроль. При отсутствии контроля всех сигналов отклонения блок 5 выдачи сигналов отклонения выдает во внешние цепи сигнал неисправности работы устройства.

Анализатор 4 работает следующим образом. Сигнал датчика, подключенного на контроль коммутатором 3, поступает на вход формирователя 17,

где происходит формирование прямоугольных импульсов постоянной амплитуды из синусоидального сигнала датчика. Сформированный сигнал поступает на вход частотного дискриминато- 5 ра le и на вход преобразоватеяя 19

частота - код. Частотный дискриминатор ittieeT постоянно установлонный порог по частоте, по достижении которого частотой датчика выиаются сигна-О лы с выхода частотного дискриминатора 18 через элемент ИЛИ 20 нй вход триггера 21 одиночного отклонения и

на вход счетчика 22 групповых отклонений. При срабатывании триггер 21 и 15 счетчик 22 вццают сигналы по одному разделенному каналу на вход блока 5 вьщачи сигналов отклонения. С выхода преобразоватеяя 19 частота - код закодированный частотный сигнал вьвдается на вход второго блока 7 сравнения и на вход блока 8 памяти. Шпульсный сигнал с выхода блока 10 Контроля поступает на вход триггера 25 и устанавливает его в состояние, при ко.тором триггер 25 видает сигнал, запрещающий прохождение сигналов датчиков через формирователь 17 и разрешающий сигнал на генератор 24 сигналов имитации для формирования сигналов, имитирующих сягнааш отклонения, и их на входы частотного дискри минатора 18 и преобразователя 19 частота - код. После набора сигналов отклонения с выхода Триггер1а 21 одиночного отклонения и выхода счетчика 22 групгазвых отклонений через элемент И 23 на вход триггера 25 поступает сигнал, возвращающий его в исходное состояние, при котором он выдает сигнал, разрешающий прохождение си1Ряала датчика через формирователь 17, и сигнал, залрещакиций выдачу сигналов и мтации с генератора 24 сигналов имитахщи. Работа блока 1 подтверждения сигналов отклонения иллюстрируется временной дидгра о4ой на фиг.З. В исходном состоянии на прягфк выходах всех триггеров - сигнал I, на счетный С-вхоД второго триггера 14 поступают импульсы а конца обхода с вьБсода распределителя. Сигнал б отклонения с выхода первого блока сравнения поступает на счетные С-вх6ды первого и третьего триггеров. Пер вый триггер срабатывает, на его прямом выходе устанавливае тся нулевой

сигнал в, который, поступая на D вход второго триггера 14, подготавливает его к срабатыванию. Третий триггер 15 сохраняет исходное состояние. При приходе следующего импульса а конца обхода на вход второго триггера 14 последний срабатывает и выдает с прямого выхода нулевой сигнал г, который поступает на Г -вход третьего триггера 15, подготавливая его к срабатывашш. С инверсного выхода второго триггера 14 при этом вьщается сигнал 1 на установочный

S -вход первого триггера, возвращая его в исходное состояние, и на вход элемента ИЛИ 12 для передачи на вход блока 9 записи для осуществления записи в блок 8 памяти кода первого датчшса. В следукяцем дикле контроля происходит сравнение кодов всех контролируемьк датчиков с кодом пер вого датчика и в случае, если с выхода первого блока 6 сравнения поступает повторно сигнал б отклонения (случай I, фиг.З), происходит срабатывание третьего триггера 15, которьй выдает с инверсного выхода сигнал д на вход элемента И 16, который разрешает прохождение сигналов отклонения на выход элемента: И 16 е и на вход анализатора. Следующим импульсом а конца обхода триггер 14 возвращается в исходное состояние; и устанавливает триггер 15 также в исходное состояние по 5-входу. Если подтверждения сигнала отклонения с выхода первого блока сравнения во втором цикле контроля не поступает (случай П, фиг.З), то срабатывания третьего триггера не происходит и ложный сигнал отклонения исключается, а cлeдvющим импульсом а конца обхода устанавливаются в исходное состояние триггер 14 и блок П подтверждения информации. Таким образом, в случае формирования сигнала отклонения частоты осуществляется проверка этого сигнала в следующем цикле контроля всех датков, но в качестве опорного значения записывается значение частоты первого датчика, при этом ложный сиггт нал об отклонении частоты в следующем цикле Не подтверждается, а истинЩ1й подтверждается, чем и достигаетсяпов1ышеиие достоверности контроля, Технико-экономическая эффективность предлага:ёмого технического решения 7 . заключается в сокращении ложных

налов отклонения частоты, которые вызывают срабатывание системы защиты оборудования, на котором установлены датчики. Это приводит к сокращению

г

L.n

LMJ

вания, отрицательно сказьгоающихся на производительности, качестве и ресурсе эксплуатации оборудования.

СЛ

20

Т:

h -s

НЛП 12

Фаг. 2 сиг- простоя, остановок и пусков оборудо И 533378

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для многоканального контроля | 1983 |

|

SU1110313A2 |

| Устройство для многоканального контроля | 1979 |

|

SU841007A1 |

| Устройство для многоканального контроля | 1983 |

|

SU1119054A1 |

| Устройство для многоканальногоКОНТРОля | 1979 |

|

SU840814A1 |

| Устройство для моногоканального контроля | 1975 |

|

SU566193A2 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| Устройство для автоматического контроля межстанционных участков телеграфной сети связи | 1984 |

|

SU1228294A1 |

| Устройство для многоканального контроля | 1977 |

|

SU714461A2 |

| Многоканальное устройство для контроля параметров | 1987 |

|

SU1444714A1 |

| Устройство для многоканального контроля | 1986 |

|

SU1332351A1 |

1.УСТРОЙСТВО ДОЯ МНОГОКАНАЛЬНОГО КОНТРОЛЯ по авт.св.№ 841007, отличающееся тем, что, с целью повьшения достоверности контроля, в иего введены блок подтверждения сигналов отклонения к элемент ИЛИ.вьясод иперв вход элементаШШ подключены соответственно между входом блок а записи информации и первым выходом первого блока сравнения,между вторым выходом которого и третьим входом анализатора подключены соответственно первый вход и первый выход блока подтверждения сигналов отклонения, второй вход и второй выход которого подключены соответственно к втот рому выходу распределителя и второму входу элемента ИЛИ. 2.Устройство по п.1, о т л и ч аю щ е е с я тем, что блок подтверждения сигналов отклонения выполнен на триггерах и элементе И,-прямой выход первого триггера соединен с } -входом второго триггера, прямой выход которого соединен с объединеншфш D и 5-входами третьего триггера, инверсный выход которого соединен с первым входом элемента И, 1МХОД первого триггера подключен к шине нулевого потенциала, объеди-, ненные С-входы первого и третьего триггеров и второй вход элемента И, W и С-вход второго триггера являются соответственно первым и вторым входами блока подтверждения сигналов отклонений , выход элемента И и объединенные инверсный выход второго триггера и 5-вход первого триггера являются соответственно первым и вторым О1 ш гходами блока подтверждения сигна00 00 О9 лов отклонения.

| Устройство для многоканального контроля | 1979 |

|

SU841007A1 |

Авторы

Даты

1985-04-30—Публикация

1983-11-03—Подача